Eelmised osad:

RISC-arhitektuuri ehitamine

Nagu korduvalt mainitud, oli kõigil 1980ndatel välja antud x86 protsessoritel, Motorola lahendustel ja valdaval enamusel kiipidest CISC (Complex Instruction Set Computing) arhitektuur. Kõikide omaduste kombinatsioon on viinud selleni, et kiibid ei ole muutunud mitte ainult keeruliseks ja kalliks tootmiseks, vaid on jõudnud ka oma jõudluse ülemmäära. Kiiruse edasiseks suurendamiseks oli vaja suurendada transistoride arvu, kuid valdatud tehnoloogilised standardid ei võimaldanud keerukamaid lahendusi luua. Intel puutus sellega kokku i486 perekonna väljalaskmisel. Jõudluse parandamiseks muutsid nad protsessori arhitektuuri, lisades vahemälu, kordajaid ja torujuhtmeid. Ühesõnaga, 486. "kivid" said mõned RISC-arhitektuuri "kiibid". Küll aga RISC platvormi loomiseks Ameerika firma pole mingit seost. Arhitektuur võlgneb oma loomise Ameerika insenerile David Pattersonile, kes juhtis Berkeley RISC projekti aastatel 1980–1984.

David Patterson – RISCi isa

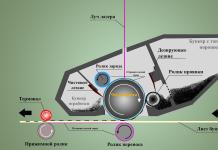

Esialgne idee, mis siis nii mastaapses Berkeley RISC projektis kehastus, oli Motorola 68000 töö uurimine. Vaatluste käigus selgus, et programmid lihtsalt ei kasutanud valdavat enamust sisseehitatud juhistest. protsessor. Näiteks Unixi süsteem kasutas kompileerimisel vaid 30% käskudest. Seetõttu plaaniti Berkeley RISC projekti raames luua protsessor, mis sisaldaks vaid kõige vajalikumaid juhiseid.

Pärast mitmeaastast uurimis- ja arendustegevust ilmus mitu protsessorite näidist, mille nimi andis nime kogu arhitektuurile. Lühend RISC ise tähistab Restricted (Reduced) Instruction Set Computer, mis tõlkes tähendab "vähendatud käsukomplektiga arvutit". "Vähendatud käskude kogum" ei tähenda, et käskude arv on väiksem kui CISC kiipidel olevate käskude arv. Erinevus seisneb selles, et iga RISC-platvormi käsk on lihtne ja täidetakse ühe taktitsükli jooksul (vähemalt peaks täitma), samas kui RISC-käsu täitmine võib võtta mitukümmend taktitsüklit. Sel juhul on käsu pikkus fikseeritud. Näiteks 32 bitti. Ka RISC-l on palju rohkem registreid Üldine otstarve. Lisaks iseloomustab seda arhitektuuri torujuhtmete ühendamine. Just selle kasutamine (koos lihtsustatud käskudega) võimaldab tõhusalt suurendada RISC-protsessorite taktsagedust.

Berkeley RISC projektimeeskond

Debüütlahendused olid RISC I ja RISC II – Pattersoni ja Berkeley RISC projekti idee. Esimene sisaldas üle 44 000 transistori ja töötas sagedusel 4 MHz. Selline protsessor oli väikeste programmide täitmisel keskmiselt kaks korda kiirem kui VAX 11/780 ja umbes neli korda kiirem kui Zilog Z8000 "kivi". RISC II erines oma eelkäijast suure hulga juhiste poolest: 39 versus 32. See oli kiirem. Selle eelis VAX-protsessori ees ulatus 200%-ni, samas kui Motorola 68000 oli mõnes programmis umbes neli korda aeglasem.

Tuleb märkida, et Berkeley RISC oli osa suuremast projektist nimega VLSI. See hõlmas ka Stanfordi ülikooli MIPS-i projekti, mis sai alguse 1981. aastal.

MIPS protsessorid

MIPS-projekti juht oli Stanfordi ülikooli teadlane John Hannessy. Nagu Berkeley RISC puhul, oli ka käivitusettevõtte eesmärk uurida ja ehitada protsessor, mis kasutaks torujuhet ja vähendatud juhiste komplekti. MIPS-lahenduste arhitektuur nägi ette ka abiplokkide olemasolu kristallis: näiteks moodulid mäluga töötamiseks, täisarv ALU (aritmeetiline loogikaüksus) ja käsudekooderid. Erinevus MIPS-plaani ja Berkeley RISC-i vahel oli laiendatud konveieri kasutamine. RISC-arhitektuur hõlmab põhimõtteliselt konveieri kasutamist, kuid Hannessy läks kaugemale ja tegi ettepaneku protsessoris olevat torujuhet nii palju kui võimalik pikendada, st ühe toimingu täitmist veelgi "tükeldada". Selline lähenemine avas ehitamiseks veelgi rohkem ruumi kella sagedus. Samas võimaldas konveieri pikendamine käskude täitmise tõhusamat paralleelsust. Sel ajal oli paralleelsus RISC-arhitektuuri tunnuseks, kuna ükski CISC-protsessor ei rakendanud seda funktsiooni enne torujuhtmete tulekut. Näiteks MIPS-is ja ka RISC-is ei saanud ühe käsu täitmist veel lõpule viia, kui hakati täitma teist. CISC protsessorites oli ühe käsu täitmise alustamiseks vaja teise käsu töötlemine lõpetada.

John Hannessy - MIPS-i arhitektuuri looja ja praegune Stanfordi ülikooli president

Algne MIPS-protsessorite spetsifikatsioon ei toetanud elementaarseid toiminguid, nagu korrutamine ja jagamine. Seda tehti meelega. Seega soovisid arendajad vabaneda vajadusest kasutada nn torujuhtme lukke. Blokeerimine ise kujutas endast torujuhtme peatamist juhtudel, kui torujuhtme teatud etapis ei saanud toimingut ühe tsükliga lõpule viia. MIPS-i arhitektuuri varased juurutused töötasid aga lukkudega ning toetasid isegi korrutamist ja jagamist. Läks veidi aega, enne kui esialgne idee protsessorites teoks sai.

1984. aastal lahkus Hannessy Stanfordi ülikoolist ja asutas ettevõtte MIPS Computer Systems, mis hakkas tootma sama arhitektuuriga protsessoreid. Aasta hiljem ilmus ettevõtte esimene toode - 32-bitine "kivi" R2000. Sellest sai ajaloo esimene kaubanduslikult saadaolev RISC-mudel. 1988. aastal ilmus järgmise põlvkonna protsessor nimega R3000. Võrreldes R2000-ga sai see multitöötluse toe ning käskude ja andmete vahemälu. 3000. osutus äriliselt edukaks. Protsessorit kasutati selliste ettevõtete serverisüsteemides ja tööjaamades nagu Silicon Graphics, DEC, Seiko Epson ja paljud teised. Lisaks on R3000-st saanud Sony PlayStationi mängukonsooli süda.

MIPS R3000 protsessor

Järgmise põlvkonna MIPS-protsessorite väljatöötamiseks kulus kolm aastat. R4000 protsessor tutvustati 1991. aastal. See sai 64-bitise arhitektuuri, sisseehitatud kaasprotsessori ja töötas kõrgemal taktsagedusel kui tema eelkäijad. Seega oli R4000 minimaalne sagedus 100 MHz. Käskude ja andmete vahemälu suurus oli kumbki 8 KB. Kaks aastat hiljem esitleti protsessori muudetud versiooni R4400 indeksiga. Uuel stantsil oli kaks korda suurem vahemälu ja see toetas suuremat L2 vahemälu. Lisaks on 64-bitises režiimis töötades parandatud arvukalt vigu.

Üllataval kombel oli MIPS vaatamata oma protsessorite ärilisele edule finantsraskustes ja lõpuks ostis SGI selle ära ja nimetas ümber MIPS Technologiesiks. Pärast seda hakati kolmandatele ettevõtetele kloonide tootmise litsentse väljastama. Näiteks lõi QED (Quantum Effects Devices) odavaid MIPS-protsessoreid, mida kasutati Cisco ruuterid. Ja NEC tegeles "kivi" VR4300 tootmisega, mis "registreeriti" Nintendo 64 mängukonsoolis.

Nintendo 64-s kasutatav NEC VR4300 protsessor

1994. aastal ilmus R8000 protsessor. Sellest sai esimene superskalaarse arhitektuuriga MIPS-lahendus, mis eeldab käskude paralleelset täitmist eeldusel, et ühe käsu täitmine ei sõltu teise tulemusest. Näiteks R8000 suudab ühe kella kohta töödelda kuni nelja käsku.

1996. aasta jaanuaris tutvustas MIPS järgmise põlvkonna protsessorit nimega R10000. "Kümnetuhandik" kasutas sama superskalaarset arhitektuuri nagu R8000 ja tegelikult oli see oma eelkäija muudetud versioon. Samuti oli protsessoril käskude ja andmete vahemälu 32 KB ning see töötas sagedusel 175 MHz või 195 MHz. 1997. aastal ilmus kiibist isegi 250 MHz versioon. Kuid isegi 195 MHz juures oli R10000 üks tolle aja kiiremaid protsessoreid.

Toshiba toodetud R10000 protsessor

Kahjuks loobus SGI pärast R10000 turuletoomist MIPS-i arhitektuurist. Kõik järgnevad kristallid põhinesid "kümnetuhandiku" tuumal ja neil ei olnud sellega võrreldes põhimõttelisi erinevusi. Näiteks 1998. aastal turule toodud protsessor R12000 sai uue etapi ja täiustas tööd käsujärjekordadega. Selle taktsagedus oli 270 MHz, 300 MHz või 360 MHz. Peale R12000 tulid välja veel kaks põlvkonda MIPS protsessoreid: R14000 ja R16000. Nad said tuge kiiremate süsteemisiinide, suurenenud sageduste ja suurema vahemälu jaoks. Näiteks R16000 võiks töötada sagedusel 700 MHz ja toetada 64 KB käsu- ja andmevahemälu.

Pärast seda hakkas MIPS müüma litsentse 32-bitise ja 64-bitise MIPS32 ja MIPS64 arhitektuuri jaoks.

SPARC protsessorid

Sun Microsystems otsustas välja töötada ka arhitektuuri – SPARC (Scalable Processor ARChitecture). Niisiis ammutasid insenerid inspiratsiooni Berkeley RISC projektist. Ja David Patterson ise osales projektis isegi konsultandina. Kuid selle tulemusena nägi SPARC välja rohkem MIPS-i arhitektuuri moodi. Näiteks platvormi käskude komplektis puudusid ka korrutamise ja jagamise juhised. SPARC arhitektuuri eripäraks oli registriakna kasutamine, mille abil muudeti veidi programmides funktsioonide kutsumise protsessi. Tavaliselt jättis protsessor programmide helistamisel oma oleku meelde (st mõne üld- ja eriotstarbeline), jätkas funktsiooni täitmist ja naasis seejärel algsesse olekusse enne funktsiooni kutsumist. Ja SPARC protsessorites kirjutati funktsiooni kutsumisel vajalikud andmed registri akna lõppu ja registri aken ise liikus failis nii, et andmed olid akna alguses. See lähenemine andis teoreetiliselt rohkem suur kiirus tööd.

Fujitsu toodetud SPARC V7 protsessor

Arhitektuuri esimene versioon kandis nime SPARC V7. Sellel põhinevat samanimelist protsessorit toodeti kuni 1992. aastani. Siis tuli arhitektuuri järgmine põlvkond – SPARC V8. Suuri muutusi ta läbi teinud ei ole. Peamised erinevused oli korrutamise ja jagamise operatsioonide lisamine, samuti ujukomaaritmeetika täiustatud jõudlus. Sarnaselt SPARC V7-le jäi SPARC V8 32-bitiseks arhitektuuriks, millel microSPARC protsessor põhines. See kuulus madala hinnaga segmenti ja seda kasutati väikestes tööjaamades ja manussüsteemides. Ettevõtted Texas Instruments ja Fujitsu andis välja ka täiustatud kloonid. Tootlikum lahendus oli SuperSPARC protsessor.

SPARC Arhitektuurikomitee, kuhu lisaks Sunile kuulusid sellised ettevõtted nagu Texas Instruments, Fujitsu, Philips ja paljud teised, tegeles juba SPARC V9 nime kandva arhitektuuri järgmise põlvkonna loomisega. Platvormi laiendati 64-bitiseks ja see oli 9-astmelise torujuhtmega superskalaarne. SPARC V9 võimaldas kasutada esimese taseme vahemälu, mis on jagatud 16 KB suurusteks juhisteks ja andmeteks, samuti teist taset mahuga 512–4096 KB. Arhitektuuri teostus oli UltraSPARC protsessor sagedusega 143-200 MHz.

UltraSPARC II protsessor

UltraSPARC polnud ainus SPARC V9 arhitektuuriprotsessor. 1997. aastal tutvustati UltraSPARC II.

ARM protsessorid

Nüüd populaarsete ARM-protsessorite või õigemini ARM-i arhitektuuri enda ajalugu algab Acorn Computersi ja selle BBC Micro arvutiga. See kasutas "kivi" MOS Technology 6502, kuid selle jõudlusest ei piisanud järgmise põlvkonna töölaua loomiseks. Erinevatel põhjustel ei vastanud Acorni nõuetele ka teised saadaolevad protsessorid, mistõttu mõtles ettevõte oma kiibi loomisele. Pärast erinevate arhitektuuride uurimist võtsid Acorni insenerid aluseks RISC protsessorid ja sama MOS Technology 6502 kiibi.

BBC Micro arvuti

Näiteks MOS-protsessor laenas oma mälu juurdepääsu arhitektuuri ja juhiste komplekti. Iga käsku on täiendatud spetsiaalse neljabitise tingimuskoodiga. Sõltuvalt koodi väärtusest (tõene või väär) võib käsk olla täidetud või mitte. See võimaldas meil vähendada konveieri arhitektuuri jõudlust negatiivselt mõjutanud toimingute ajal üleminekute arvu. Arendajad kaasasid ka meeskonnad, kes viisid arhitektuuri esialgsesse versiooni läbi mitmeid elementaarseid toiminguid. Ühesõnaga kaldusime RISCi reeglitest veidi kõrvale. Pikemas perspektiivis parandas see aga ainult protsessori jõudlust.

Arhitektuuriarendus viidi lõpule 1985. aastal koos loomisega ARM protsessor. Esimesed kommertsversioonid ilmusid 1986. aastal ja kandsid nime ARM2. Võrreldes CISC protsessoritega oli ARM2 väga lihtne – see sisaldas vaid 30 000 transistorit. Samas kulutas see väga vähe energiat ja oli samas üsna produktiivne. Veidi hiljem ilmusid ARM protsessorid, millesse lisati 4 KB vahemälu, mis tõstis kristallide jõudlust veelgi.

ARM2 protsessor

1980. aastate lõpuks ei olnud Acorn ARM-arhitektuuri arendamisel enam üksi; Apple ühines sellega. Sellega seoses muudeti otse ARM-protsessoritega tegelev divisjon eraldi ettevõtteks - Advanced RISC Machines. Uue ettevõtte esimene toode oli ARM6 protsessorituum ja ARM610 protsessor, mida kasutati ühes maailma esimestest Apple Newtoni pihuarvutitest.

ARM-protsessorid ei suutnud aga enam jõudluse poolest CISC-lahendustega konkureerida ning RISC-segmendis domineerisid MIPS-i arhitektuuriga protsessorid. Siis läks ARM teist teed. Ettevõte hakkas positsioneerima ARM6 manustatud tuumana, mida kõik kolmanda osapoole tootjad saaksid oma protsessorites väikese raha eest kasutada. See poliitika tasus end ära ja ARM-i tuum sai väga populaarseks ning ettevõte ise sai äriliselt edukaks.

Koos DEC-ga töötati välja suurema jõudlusega ARM-lahenduste arhitektuur nimega StrongARM, mis oli klassikaline 5-astmelise torujuhtmega skalaararhitektuur. Arhitektuuril olid mäluhaldusüksused ning toetatud käsu- ja andmevahemälud mahuga 16 KB.

Esimene StrongARM-il põhinev protsessor SA-110 tutvustati 1996. aasta veebruaris. See töötas 100 MHz, 160 MHz või 200 MHz taktsagedustel. "Stone" kasutati Apple MessagePad 2000, samuti Acorn Computer Risc PC ja Eidos Optima süsteemides. Kogu 1996. aasta jooksul oli SA-110 kõrgeima jõudlusega mobiilne protsessor.

Apple MessagePad 2000 kasutas SA-110 protsessorit

1997. aastal müüdi StrongARM-i arhitektuuri õigused Intelile, kes töötas välja platvormi järgmise põlvkonna. Aastal 2000 seda esitleti, kuid arhitektuur (õigemini arhitektuuri teostus) kandis teist nime - Xscale. Platvorm on saanud palju muudatusi. Näiteks on konveieri pikkust suurendatud 8 astmeni. Vahemälu maht nii juhiste kui ka andmete jaoks on kasvanud 32 KB-ni. XScale'i on kasutatud sellistes seadmetes nagu RIM Blackberry, Dell Axim, Motorola A780 mobiiltelefon ja muud seadmed.

PowerPC protsessorid

Kui täpne olla, siis esimene ettevõte, kes RISC-arhitektuuri arendama hakkas, oli IBM. Veel 1974. aastal alustati IBM 801 protsessori väljatöötamist, mis pani sellele platvormile esimesed aluse. Ja Berkeley RISC projekt kujundas lõpuks arhitektuuri.

80ndate alguses kasutasid mõned IBMi sisseehitatud protsessorid arhitektuuri 801. Sellel põhinev protsessor "registreerus" ka arvutisse IBM 9370.

1985. aastal alustas IBM järgmise põlvkonna RISC-arhitektuuri arendamist. Projekt sai nimeks America Project. Protsessori ja selle juhiste komplekti arendamine lõppes 1990. aastal. Kristall ise kandis nime POWER1 ja seda kasutati IBMi serverites ja tööjaamades. Sellel oli üsna kõrge jõudlus, kuid sellel oli mitme kiibi paigutus ja see koosnes 11 erinevast mikroskeemist. 1992. aastal tutvustas IBM POWER1 protsessori odavat versiooni, mis mahub ühele kiibile.

Protsessor POWER1. Isegi pigem kiibistik

1993. aastal tutvustati POWER2 arhitektuuri teist põlvkonda. Sellele lisati üks lisaplokk aritmeetika-loogilised tehted ja ujukomaarvutused. Laiendati ka juhiste komplekti: lisati näiteks arvu ruutjuure arvutamise operatsioon riistvara tasemel. Protsessori taktsagedus varieerus 55 MHz kuni 71 MHz ning andmete ja käskude vahemälu oli vastavalt 256 KB ja 32 KB. Nagu eelkäijagi uus protsessor oli mitme kiibi paigutusega. Kuid 1994. aasta mais ilmus ka ühe kiibiga versioon.

Kuid juba enne POWER2 väljaandmist moodustas IBM koos Apple'i ja Motorolaga AIM-i liidu ja nõustus looma POWERil põhineva täiustatud arhitektuuri. Kasu said kõik kolm ettevõtet, kuna neil oli üks kiiremaid RISC-protsessoreid turul. Ühiselt arendatud arhitektuur sai nimeks PowerPC. Lisaks POWER platvormi põhifunktsioonide komplektile kahe režiimi tugi (big-endian ja little-endian), uued juhised ujukomaarvutusteks ja tagasiühilduvus 32-bitise töörežiimiga arhitektuuri 64-bitise versiooni jaoks.

1. põlvkonna PowerPC protsessor

Erinevalt teistest RISC-arhitektuuridest, mis hõivasid kitsaid turunišše, positsioneeriti PowerPC konkureeriva x86 platvormina. Selle peamine eesmärk oli personaalarvutid. Seega on PowerPC-põhist protsessorit arvutites kasutatud juba mõnda aega. Apple Macintosh- kuni 2006. aastani.

Arhitektuur konkureeris kuni 2001. aastani x86-ga, kuid pärast seda ei suutnud see Inteli ja AMD protsessoritega sammu pidada. Vaatamata sellele kasutati Sony PlayStation 3 ja Microsoft Xbox 360 videomängukonsoolides PowerPC-põhiseid protsessoreid.

Sony PlayStation 3 ja Microsoft Xbox 360 konsoolide toiteallikaks on PowerPC protsessor

90ndatel õnnestus IBMil välja anda kolmanda põlvkonna protsessorid nimega POWER3, millest sai tegelikult 64-bitise PowerPC arhitektuuri teostus. Kiip loodi silmas pidades kasutamiseks serverites ja tööjaamades, kuid lõpuks oli selle põhirakenduseks IBM RS / 6000 süsteemid.

DEC Alpha protsessorid

DEC VAX arhitektuur oli lootusetult vananenud ja 90ndate alguses mõtles ettevõte oma RISC platvormi väljatöötamisele. Temast sai Alpha, mis ilmus 1994. aastal. Esimene protsessor oli Alpha 21064, koodnimega EV4. See on 64-bitine konveierarhitektuuriga superskalaarne kristall. See tähendab, et sellel oli klassikaline RISC disain. DEC-protsessorit eristas soodsalt kõigi selle plokkide tõrgeteta töö. Nii näitas EV4 teiste "kividega" võrdsel sagedusel kõrgemat jõudlust. Protsessori väline siin oli 128-bitine. Sellel oli 16 KB andmete ja juhiste vahemälu ning see oli toodetud CMOS-4 tehnoloogia abil. EV4 taktsagedus oli 150 MHz või 200 MHz. Mõnevõrra hiljem ilmus modifikatsioon nimega 21064A, mis suutis töötada kiirustel kuni 300 MHz, mis andis kristallile tolleaegse kiireima protsessori tiitli. EV4 peamiseks rakenduseks said serverid ja tööjaamad.

Protsessor Alpha 21064

Alpha 21064A jäi DEC-i tippmudeliks kuni järgmise põlvkonna protsessorite – 21164 (EV5) – ilmumiseni. Sellel oli kaks täisarvu ühikut ja kaks ujukomaühikut. EV5-s oli vahemälu juba kolm taset: kaks asusid otse protsessoris ja kolmas oli väline. Esimese taseme vahemälu jagunes kaheks osaks: andmevahemälu ja juhiste vahemälu, igaüks 8 KB. Teise taseme vahemälu maht oli 96 KB. Protsessori taktsagedus varieerus 266 MHz kuni 333 MHz. Alpha 21164 võttis üle Alpha 21064A-lt ja oli kiireim protsessor kuni Pentium Pro väljalaskmiseni. DEC-i vastust ei tulnud aga kaua oodata – ettevõte avaldas rohkem produktiivne protsessor Alpha 21164A töötab kõrgemal taktsagedusel (kuni 666 MHz). Protsessorit kasutati selliste ettevõtete tööjaamades ja serveriarvutites nagu Digital, Network Appliance ja Cray Research.

Protsessor Alpha 21264

1996. aastal tutvustati järgmise põlvkonna DEC-protsessoreid Alpha 21264 (EV6). Kiip sai varasemate mudelitega võrreldes mitmeid olulisi muudatusi. Näiteks toetas see juhiste täitmist, mis tõi kaasa tuuma täieliku ümberkorraldamise. Täisarvuplokid ja laadimis-/salvestusplokid ühendati üheks Eboxi mooduliks ning ujukomaplokid eraldati Fboxi mooduliks. Lisaks plokkidele endile sisaldasid need üksused ka registrifaile. Vahemälu struktuur muutus taas kahetasandiliseks - see asendas Alpha 21164 vahemälu kolmetasandilise korralduse. Esimese taseme vahemälu säilitas jaotuse mällu juhiste ja andmete jaoks. Iga osa maht oli 64 KB. Mis puudutab teise taseme vahemälu, siis selle maht võiks olla 1 MB kuni 16 MB. Lisaks sai protsessor haru ennustamise tuge. Aja jooksul ilmus Alpha 21264 protsessorite uusi versioone, milles ennekõike suurendati taktsagedust. Viimane modifikatsioon oli Alpha 21264E, mis töötas sagedusel 1250 MHz.

Paraku oli Alpha 21264 protsessorite sari "sõltumatu" DEC ajaloos viimane. 1998. aasta alguses kuulutati välja DEC pankrot ja Compaq võttis selle üle.

Intel P5 arhitektuur

RISC-arhitektuuriga protsessorid hõivasid enamasti oma spetsialiseeritud niši, kuid lauaarvutisüsteemides kasutati endiselt x86 arhitektuuriga kristalle. Nende areng jätkus, kuigi mõningate muudatustega.

Hoolimata asjaolust, et Intel sisenes RISC protsessorite turule oma i860 ja i960 lahendustega, panustas ettevõte ikkagi x86 kiipidega. Järgmise põlvkonna "kivid" olid tuntud P5 arhitektuuril põhinevad Pentiumid, mis ilmusid 1993. aastal.

Palju tööd on tehtud. Esiteks on P5 muutunud superskalaarseks. Arhitektuur töötas kahe torujuhtmega, millest igaüks võis teha kaks toimingut tsükli kohta. Teiseks sai andmesiinist 64-bitine, mis võimaldas tsükli kohta üle kanda kaks korda rohkem andmeid. Kolmandaks jagati andmete ja juhiste vahemälu kaheks eraldi plokkiks, igaüks 8 KB. Lisaks on protsessorisse lisatud harude ennustamise plokk ning ujukomaarvutusmoodul on muutunud tootlikumaks.

Esimesed Pentiumi protsessorid töötasid sagedusel 60 MHz või 66 MHz. Samal ajal vajasid nad tööks 5 V pinget, nii et läksid väga kuumaks. Samuti said esimesed "kännud" kuulsaks ujukomaarvutusühiku vale töö tõttu, mis andis arvude jagamisel kohati vale tulemuse. Seetõttu tõi Intel peagi turule parandatud P54C arhitektuuriga protsessorid.

Intel Pentium protsessor

P54C-st on saanud omamoodi vigade kallal töötamine. Uute protsessorite tootmine viidi üle 0,6-mikronilisele protsessitehnoloogiale. Kristallid ise töötasid nüüd 3,3 V pingega, mis lahendas ülekuumenemise probleemi. Mis puudutab muudatusi arhitektuuri tasemel, siis P54C-le lisandus poolteist kordaja - edaspidi töötasid protsessorid rohkem kõrgsagedus kui süsteemisiin. Protsessorite kiirus oli 75 MHz, 90 MHz või 100 MHz. P54C-d paigaldati ka pesadesse Socket 5 või Socket 7. Erinevalt P5-st, mis toetas ainult Socket 4. P54C arhitektuur ise sai uue uuenduse 1995. aastal, kui see viidi üle 350 nm protsessitehnoloogiale. See võimaldas taas vähendada kristallide energiatarbimist, samuti tõsta nende taktsagedust 200 MHz-ni.

1.1 Peamised erinevused CISC- ja RISC-arhitektuuride vahel

Kaks peamist käsukomplekti arhitektuuri, mida arvutitööstus praeguses arvutitehnoloogia arendamise etapis kasutab (vastavalt sellele), on CISC ja RISC arhitektuurid. CISC-arhitektuuri rajajaks võib pidada IBM-i oma /360 baasarhitektuuriga, mille tuum on kasutusel alates 1964. aastast ja on säilinud tänapäevani näiteks sellistes kaasaegsetes suurarvutites nagu IBM ES / 9000. mikroprotsessorite arendamine c täiskomplekt käske (CISC – Complete Instruction Set Computer) peetakse Inteliks oma x86 ja Pentium seeriaga. See arhitektuur on mikroarvutite turu praktiline standard. CISC protsessoreid iseloomustavad: suhteliselt väike arvüldotstarbelised registrid; suur hulk masinakäske, millest osa laaditakse semantiliselt sarnaselt operaatoritega kõrgetasemelised keeled programmeerimine ja neid teostatakse paljudes tsüklites; suur hulk adresseerimismeetodeid; suur hulk erineva bitisügavusega käsuvorminguid; kahe aadressiga käsuvormingu domineerimine; registrimälu tüüpi töötlemisjuhiste olemasolu.

Kaasaegsete tööjaamade ja serverite arhitektuuri aluseks on vähendatud käsustikuga arvutiarhitektuur (RISC – Reduced Instruction Set Computer). Selle arhitektuuri algus ulatub tagasi CDC6600 arvutitesse, mille arendajad (Thornton, Cray jt) mõistsid, kui oluline on kiireks ehitamiseks juhiste komplekti lihtsustada. arvutid. S. Cray rakendas edukalt seda arhitektuuri lihtsustamise traditsiooni Cray Researchi tuntud superarvutite seeria loomisel. RISC-i kontseptsioon selle tänapäevases tähenduses kujunes aga lõpuks välja kolme arvutite uurimisprojekti põhjal: IBM 801 protsessor, Berkeley ülikooli RISC protsessor ja Stanfordi ülikooli MIPS protsessor.

Muudeks RISC-arhitektuuride funktsioonideks on üsna suure registrifaili olemasolu (tüüpilistes RISC-protsessorites on realiseeritud 32 või enam registrit võrreldes 8-16 registriga CISC-arhitektuurides), mis võimaldab protsessorikiibil asuvates registrites salvestada rohkem andmeid. aega ja lihtsustab kompilaatori tööd muutujate jaoks registrite eraldamisel.

Töötlemiseks kasutatakse reeglina kolme aadressiga käske, mis lisaks dekrüpteerimise lihtsustamisele võimaldab salvestada registritesse suurema hulga muutujaid ilma nende hilisema ümberlaadimiseta.

RISC-arhitektuuri arengu määras suuresti edusammud optimeerivate kompilaatorite loomise vallas. Just kaasaegsed kompileerimistehnikad võimaldavad tõhusalt ära kasutada suuremat registrifaili, konveierkorraldust ja kiiremat käskude täitmist. Kaasaegsed kompilaatorid kasutavad ära ka teist RISC-protsessorites tavapäraselt kasutatavat jõudluse optimeerimise tehnikat: viivitatud harude rakendamist ja superskalaarset töötlemist, mis võimaldab korraga väljastada mitu käsku.

Tuleb märkida, et nii Inteli (tähendab Pentium ja Pentium Pro), kui ka tema järeltulijate-konkurentide (AMD R5, Cyrix M1, NexGen Nx586 jne) viimastes arendustes kasutatakse laialdaselt RISC mikroprotsessorites rakendatud ideid, nii et et paljud erinevused CISC ja RISC vahel hägustuvad. Kuid x86 arhitektuuri ja juhiste komplekti keerukus jääb püsima ja on põhiliseks sellel põhinevate protsessorite jõudlust piiravaks teguriks.

Hewlett Packardi PA-RISC arhitektuuri eelised ja puudused

Kaasaegsete Hewlett-Packardi toodete arendamise aluseks on PA-RISC arhitektuur. Ettevõte töötas selle välja 1986. aastal ja sellest ajast alates on see integreeritud tehnoloogia edusammude tõttu mitmekiibilisest ühe kiibi täitmiseni läbinud mitu arenguetappi. Septembris 1992 kuulutas Hewlett-Packard välja oma superskalaarprotsessori PA-7100, millest on saanud aluseks HP 9000 seeria 700 tööjaamade perekonna ja HP 9000 seeria 800 äriserveriperekonna loomisel. Praegu on sagedusega 33, 50 - ja 99 MHz PA-7100 kristalli rakendamine. Lisaks on muudetud, mitmes mõttes täiustatud PA-7100LC kristallid taktsagedusega 64, 80 ja 100 MHz ning PA-7150 taktsagedusega 125 MHz, samuti PA-7200 taktsagedusega 90 MHz. ja 100 MHz, vabastati. Ettevõte arendab aktiivselt järgmise põlvkonna HP 8000 protsessorit, mis töötab sagedusel 200 MHz ja pakub 360 SPECint92 ja 550 SPECfp92 ühikut. Selle kristalli ilmumist on oodata 1996. aastal. Lisaks plaanib Hewlett-Packard koostöös Inteliga luua uue protsessori väga pika juhissõnaga (VLIW arhitektuur), mis ühildub mõlemaga. Inteli perekond x86 ja PA-RISC perekond. Selle protsessori väljalaskmine on kavandatud 1998. aastaks.

1.3 PA-RISC arhitektuuril põhinevate protsessorite omadused

1.3.1 PA 7100 protsessori omadused ja omadused

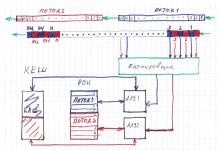

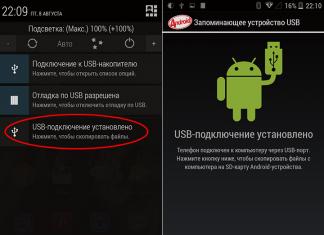

PA-RISC arhitektuuri eripäraks on vahemälu kiibiväline realiseerimine, mis võimaldab realiseerida erineva mahuga vahemälu ja optimeerida disaini olenevalt rakenduse tingimustest (joonis 1.3.1). Juhised ja andmed salvestatakse eraldi vahemäludesse ning protsessor on nendega ühendatud kiirete 64-bitiste siinide abil. Vahemälu on realiseeritud kiiretel staatilistel mälukiipidel (SRAM), mis sünkroniseeritakse otse protsessori taktsagedusega. Sagedusel 100 MHz on iga vahemälu ribalaius lugemiseks 800 MB/s ja kirjutamiseks 400 MB/s. Mikroprotsessor toetab riistvaras erinevas mahus vahemälu: käskude vahemälu võib olla 4 KB kuni 1 MB, andmevahemälu - 4 KB kuni 2 MB.

Puuduste määra vähendamiseks kasutatakse aadressi räsimise mehhanismi. Mõlemad vahemälud kasutavad töökindluse parandamiseks täiendavaid kontrollbitte ja juhiste vahemälu vead parandab riistvara.

joonis 1.3.1 PA 7100 protsessori plokkskeem

Protsessor on sünkroonsiini kaudu ühendatud mälu ja I/O alamsüsteemiga. Protsessor võib sõltuvalt välise siini sagedusest töötada kolme erineva sisemise ja välise taktsageduse suhtega: 1:1, 3:2 ja 2:1. See võimaldab süsteemides kasutada erineva kiirusega mälukiipe.

Struktuurselt sisaldab PA-7100 kiip: täisarvulist protsessorit, ujukomaarvude töötlemise protsessorit, vahemälu juhtimisseadet, ühtset TLB puhvrit, juhtseadet ja mitmeid liideseahelaid. Täisarvuprotsessor sisaldab ALU-d, nihutit, hüppekäsu lisajat, seisundikoodi kontrollimise ahelaid, möödaviiguahelaid, universaalset registrifaili, juhtregistreid ja aadressikonveieri registreid. Vahemäluhaldur sisaldab registreid, mis laadivad vahelejäämise korral vahemälu uuesti ja kontrollivad mälu koherentset olekut. See seade sisaldab ka segmendi aadressiregistreid, TLB aadressi tõlkepuhvrit ja räsiriistvara, mis juhib TLB uuesti laadimist. Ujukomaprotsessor sisaldab korrutamisühikut, aritmeetilise loogika ühikut, jagamis- ja ruutjuurühikut, registrifaili ja ahelaid tulemuse "lühistamiseks". Liideseseadmed sisaldavad kõiki vajalikke lülitusi käsu- ja andmevahemälu ning andmesiiniga suhtlemiseks. Üldistatud TLB sisaldab 120 fikseeritud suurusega assotsiatiivset mälurida ja 16 muutuva suurusega assotsiatiivset mälurida.

Ujukoma ühik rakendab ühe- ja kahekordse täppisaritmeetikat standardis IEEE 754. Selle korrutusühikut kasutatakse ka täisarvude korrutamistehingute tegemiseks. Jaotuse ja ruutjuure ühikud töötavad kaks korda suurema protsessori kiirusega. Aritmeetiline loogikaüksus teostab andmevormingute liitmise, lahutamise ja teisendamise toiminguid. Registrifail koosneb 28 64-bitisest registrist, millest igaühte saab kasutada kahe 32-bitise registrina, et sooritada ühe täpsusega ujukomaoperatsioone. Registrifailil on viis lugemisporti ja kolm kirjutusporti, mis võimaldavad üheaegselt teha korrutamist, liitmist ja laadimis-/kirjutusoperatsioone.

Konveier oli mõeldud maksimaalne suurendus aeg, mis kulub välise andmevahemälu SRAM-kiipide lugemiseks. See võimaldab teil maksimeerida protsessori sagedust antud SRAM-i kiiruse jaoks. Kõik laadimisjuhised (LOAD) täidetakse ühe tsükliga ja nõuavad ainult ühte andmevahemälu ribalaiuse tsüklit. Kuna käsu- ja andmevahemälu asuvad erinevatel siinidel, ei esine andmevahemälu ja käskude vahemälu juurdepääsude konfliktidest tulenevaid kadusid.

Protsessor saab anda ühe täisarvu käsu ja ühe ujukoma käsu taktitsükli kohta. Käskude vahemälu ribalaius on piisav, et toetada kahe käsu pidevat väljastamist igas taktitsüklis. Koos täidetavate käskude paari joondamisele või järjestusele pole piiranguid. Lisaks ei kaasne kella kadu kahe käsu täitmiselt ühe käsu täitmisele üleminekuga.

Erilist tähelepanu on pööratud sellele, et kahe käsu väljastamine samas taktitsüklis ei tooks kaasa taktsageduse piiranguid. Selle saavutamiseks rakendati käskude vahemällu spetsiaalne eeldekodeeritav bitt, et eraldada täisarvu seadmekäsud ujukomaseadme käskudest. See käsu eeldekodeerimise bitt minimeerib käskude õigeks eraldamiseks kuluvat aega.

Andme- ja juhtimissõltuvustega seotud üldkulud on selles torujuhtmes minimaalsed. Laadimiskäsud täidetakse ühe taktitsükli jooksul, välja arvatud juhul, kui järgnev käsk kasutab LOAD käsu sihtregistrit. Reeglina võimaldab kompilaator ühe tsükli sarnastest kadudest mööda minna. Tingimuslike harukäskudega kaasnevate kadude vähendamiseks kasutab protsessor juhtimise ülekandmise suuna ennustamise algoritmi. Jõudluse optimeerimiseks ennustatakse tsüklite edasi-tagasi juhtimist läbi programmi teostamata hüpetena ja tagasiliikumist läbi programmi ennustatakse sooritatud hüpetena. Õigesti ennustatud tingimushüpped sooritatakse ühe taktitsükli jooksul.

STORE käsuga sõna või topeltsõna kirjutamiseks vajalike tsüklite arv on vähenenud kolmelt tsüklilt kahele. PA-RISC arhitektuuri varasemates rakendustes oli tabamuse tagamiseks vaja ühte lisatsüklit vahemälu märgendi lugemiseks ja ka vanade andmevahemälu rea andmete ühendamiseks kirjutatavate andmetega. PA 7100 kasutab eraldi aadressisildi siini, et ajastada sildi lugemist eelmise STORE käsu andmete kirjutamisega. Lisaks välistab vahemälurea iga sõna jaoks eraldi kirjutamise lubamise signaalide olemasolu vajaduse ühendada vanu andmeid uute andmetega, mis pärinevad sõna- või kahesõnalistest kirjutamiskäskudest. See algoritm nõuab, et SRAM-kiipidele kirjutamine toimuks alles pärast seda, kui on kindlaks tehtud, et kirjutamisega kaasneb vahemälu tabamus ja see ei põhjusta katkestust. See nõuab täiendavat konveieri etappi märgendi lugemise ja andmete kirjutamise vahel. See konveier ei too kaasa täiendavaid taktikaod, kuna protsessoril on spetsiaalsed möödaviiguahelad, mis võimaldavad suunata kirjutamiskäsu ootel olevad andmed järgmistele laadimiskäskudele või STORE käskudele, mis kirjutavad ainult osa sõnast. Antud protsessori puhul tühistatakse konveieri kadu sõna- või kahesõnalise kirjutamiskäsu korral, välja arvatud juhul, kui vahetult järgnev käsk on laadimis- või kirjutamiskäsk. Vastasel juhul on kaotus võrdne ühe tsükliga. Kaod sõnaosa kirjutamisel võivad olla nullist kahe tsüklini. Simulatsioon näitab, et valdav enamus kirjutamiskäskudest töötab tegelikult ühe sõna või kahe sõna vormingus.

Kõik ujukomaoperatsioonid, välja arvatud jagamise ja ruutjuure käsud, on täielikult konveierdatud ja neil on tõuke-tõmbe latentsus nii ühe- kui ka topelttäppisrežiimis. Protsessor võib kadude puudumisel väljastada sõltumatuid ujukomakäske täitmiseks igas taktitsüklis. Registrisõltuvustega järjestikused toimingud põhjustavad ühe tsükli kadumise. Jagamise ja ruutjuure juhised võtavad ühe täpsuse jaoks 8 tsüklit ja topelttäpsuse jaoks 15 tsüklit. Käsu täitmist ei peata jaga/ruutjuure käsk enne, kui on vaja tulemusregistrit või väljastatakse järgmine jagamise/ruutjuure käsk.

Protsessor suudab paralleelselt täita üht täisarvukäsku ja ühte ujukomakäsku. Sel juhul loetakse ujukomaregistrite laadimise ja kirjutamise juhiseid ka "täisarvulisteks käskudeks" ning "ujukomajuhised" sisaldavad käske FMPYADD ja FMPYSUB. Need viimased juhised ühendavad korrutustehte vastavalt liitmise või lahutamise toiminguga, mida tehakse paralleelselt. Maksimaalne läbilaskevõime on 200 MFLOPS-i FMPYADD-käskude jada jaoks, kui külgnevad käsud on tõstu- ja suurtähtedest sõltumatud.

Kaod ujukomaoperatsioonidel kasutades eellaadimine LOAD-käsu operandiks on üks kell, kui laadimis- ja ujumiskäsud on kõrvuti, ja kaks kella, kui need antakse täitmiseks välja samal ajal. Kirjutamiskäsu puhul, mis kasutab ujukomatehte tulemust, ei kaasne kadu, isegi kui neid täidetakse paralleelselt.

Andmevahemälu vahelejäämisest tulenevad kaod on viidud miinimumini nelja erineva tehnika rakendamisega: Laadimis- ja STORE-käskluste "hit on miss", andmevahemälu voogedastus, kirjutamiskäskude spetsiaalne kodeerimine, et vältida puuduva rea kopeerimist, ja semafori toimingud vahemälus. Esimene atribuut võimaldab andmevahemälu puudujäägi töötlemise ajal täita mis tahes muud tüüpi käske. Laadimiskäsu täitmisel ilmnevate möödalaskmiste korral võib järgmiste käskude töötlemine jätkuda seni, kuni LOAD-käsu tulemuste registrit on vaja teise käsu operandiregistrina. Kompilaator saab seda atribuuti kasutada vajalike andmete eellaadimiseks vahemällu ammu enne, kui neid tegelikult vaja läheb. STORE-käsu täitmisel ilmnevate vahelejäämiste korral jätkub järgmiste laadimiskäskude või sama sõna osade kirjutamistoimingute töötlemine, kuni pääsete juurde reale, kus möödalaskmine toimus. Kompilaator saab seda atribuuti kasutada käskude täitmiseks eelmiste arvutuste tulemuste salvestamisel. Käsitlemise viivituse ajal saab muid andmevahemällu sattunud LOAD ja STORE käske täita nagu teisi täisarvu ja ujukomakäske. Kuni STORE puudujääki töödeldakse, võivad samale vahemälureale muud kirjutused toimuda ilma täiendava ajakadudeta. Protsessoril on vahemälurea iga sõna jaoks spetsiaalne indikaatorbitt, mis takistab neid rea sõnu, mis on STORE juhiste abil kirjutatud, mälust kopeerimast. See võimalus kehtib täisarvude ja ujukoma LOAD ja STORE operatsioonide puhul.

Käsu täitmine peatatakse, kui valesti täitva LOAD-käsu sihtregistrit on vaja teise käsu operandiks. "Treadability" omadus võimaldab täitmist jätkata niipea, kui soovitud sõna või topeltsõna on mälust tagastatud. Seega saab käskude täitmine jätkuda nii möödalaskmise töötlemisega seotud viivituse ajal kui ka möödalaskmise korral vastava rea täitmise ajal.

Andmete plokkkoopia tegemisel teab kompilaator mõnel juhul ette, et kirjutamine tuleks läbi viia täielik rida vahemälu. Selliste olukordade haldamise optimeerimiseks määratleb PA-RISC 1.1 arhitektuur kirjutamisjuhistele spetsiaalse kodeeringu ("ploki koopia"), mis näitab, et riistvara ei pea tõmbama mälust rida, mis võib põhjustada vahemälu puudumist. Sel juhul on andmevahemälu juurdepääsuaeg aja summa, mis kulub vana vahemälu rea samale vahemäluaadressile kopeerimiseks (kui see on määrdunud) ja uue vahemälusildi kirjutamiseks kuluva aja summa. PA 7100 protsessoris on see funktsioon rakendatud nii privilegeeritud kui ka mitteprivilegeeritud juhiste jaoks.

Andmevahemälu haldamise viimane täiustus on "load-and-zero" semaforoperatsioonide rakendamine otse vahemälus. Kui semaforoperatsioon sooritatakse vahemälus, siis ajakadu selle täitmise ajal ei ületa tavaliste kirjutamistoimingute kadu. See mitte ainult ei vähenda torujuhtme kadusid, vaid vähendab ka mälusiini liiklust. PA-RISC 1.1 arhitektuur pakub ka teist tüüpi spetsiaalset juhiste kodeeringut, mis eemaldab nõude sünkroonida semafori toiminguid I/O-seadmetega.

Käskude vahemälu haldamine võimaldab möödalaskmise korral jätkata käskude täitmist kohe pärast vahemälust puuduva käsu mälust saabumist. Käskude vahemäluplokkide täitmiseks kasutatav 64-bitine andmetee vastab välise mälu siini maksimaalsele ribalaiusele 400 MB/s sagedusel 100 MHz.

Protsessor pakub ka mitmeid meetmeid, et minimeerida kadusid, mis on seotud virtuaalaadresside teisendamisega füüsilisteks aadressideks.

Protsessori disain pakub mitmeprotsessoriliste süsteemide ehitamiseks kahte võimalust. Esimese meetodi puhul on iga protsessor ühendatud liidese kiibiga, mis jälgib kõiki põhimälusiini tehinguid. Sellises süsteemis on kõik vahemälu koherentse oleku säilitamise funktsioonid määratud liidese kristallile, mis saadab vastavad tehingud protsessorile. Andmevahemälu on üles ehitatud viivitatud kopeerimise põhimõtetele ja iga vahemälu ploki jaoks säilitatakse olekubitid "privaatne" (privaatne), "määrdunud" (määrdunud) ja "usaldusväärne" (kehtiv), väärtused mis muutuvad vastavalt töötleja poolt väljastatud või saadud tehingutele.

Teine viis mitmeprotsessorilise süsteemi korraldamiseks võimaldab ühendada kaks protsessorit ning mälu ja I/O kontrolleri samale kohalikule mälusiinile. See konfiguratsioon ei vaja täiendavaid liidese kiipe ja ühildub olemasolevate mälusüsteemidega. Vahemälu sidususe tagab kohaliku mälusiini jälgimine. Vahemälu vahelised liiniülekanded tehakse ilma mälukontrolleri ja I / O osaluseta. See konfiguratsioon võimaldab ehitada väga odavaid suure jõudlusega multiprotsessorsüsteeme.

Protsessor toetab mitmeid toiminguid, mis on vajalikud 700. seeria tööjaamade graafika jõudluse parandamiseks: plokkide edastused, Z-puhverdamine, värvide interpoleerimine ja ujukoma andmeedastusjuhised sisend-/väljundruumiga vahetamiseks.

Protsessor on ehitatud 0,8 mikronise CMOS protsessitehnoloogia baasil, mis tagab 100 MHz taktsageduse.

1.3.2 PA 7200 protsessori omadused ja omadused

PA 7200 protsessoril on PA 7100-ga võrreldes mitmeid arhitektuurilisi täiustusi, millest peamised on teise täisarvu torujuhtme lisamine, kiibil oleva lisaandmete vahemälu ehitamine ja uue 64-bitise mälusiini liidese rakendamine. .

Protsessor PA 7200, nagu ka tema eelkäija, pakub superskalaarset töörežiimi koos ühe taktitsükli jooksul kuni kahe käsu samaaegse väljastamisega. Kõik protsessori käsud võib jagada kolme rühma: täisarvulised toimingud, laadimis-/kirjutustoimingud ja ujukomaoperatsioonid. PA 7200 suudab samaaegselt väljastada kahte erinevatesse rühmadesse kuuluvat käsku või kahte täisarvu käsku (tänu teise täisarvu konveieri olemasolule koos ALU-ga ja täiendavate lugemis- ja kirjutamisportidega registrifailis). Hüppekäsud täidetakse täisarvulises konveieris ja neid hüppeid saab siduda nii, et need väljastatakse üheaegselt täitmiseks ainult eelmise käsuga.

Protsessori taktsageduse suurendamine nõuab käskude dekodeerimise lihtsustamist väljastamise etapis. Selleks viiakse vahemälu laadimise etapis läbi käsuvoo esialgne dekrüpteerimine. Iga topeltsõna jaoks sisaldab käskude vahemälu 6 täiendavat bitti, mis sisaldavad teavet andmete sõltuvuste ja ressursikonfliktide olemasolu kohta, mis lihtsustab oluliselt juhiste väljastamist superskalaarrežiimis.

PA 7200 protsessor rakendab tõhus algoritm käskude eellaadimine, mis töötab hästi programmide lineaarsetes osades.

Sarnaselt PA 7100-ga liidestub protsessor välise andmevahemäluga, mis töötab protsessori taktsagedusel ühe tsükli latentsusajaga. Väline andmevahemälu põhineb otsese kaardistamise põhimõttel. Lisaks on protsessori kiibil tõhususe suurendamiseks rakendatud väike lisavahemälu, mille maht on 64 rida. Moodustamine, aadresside tõlkimine ning juurdepääs põhi- ja abiandmete vahemällu teostatakse konveieri kahes etapis. Tabamuse tuvastamise maksimaalne viivitus on üks kell.

Täiendav sisemine vahemälu sisaldab 64 32-baidist rida. Vahemälu juurde pääsemisel kontrollitakse 65 silti: 64 lisavahemälu silti ja ühte välist andmevahemälu silti. Sobivuse leidmisel saadetakse andmed vajalikule funktsionaalsele üksusele.

Kui vajalikku rida vahemälus pole, laaditakse see põhimälust. Sel juhul siseneb rida lisavahemällu, mis mõnel juhul vähendab välise vahemälu uuesti laadimiste arvu, mis on korraldatud vastavalt otsese kaardistamise põhimõttele. Uue protsessori laadimis-/kirjutuskäskude arhitektuur tagab kohaliku andmete asukoha erimärgi kodeerimise ("ainult ruumiline asukoht"). Selle lipuga tähistatud laadimiskäskude täitmisel täidetakse abivahemälu rida tavapäraselt. Järgmine rida kirjutatakse aga otse põhimällu, välisest andmevahemälust mööda minnes, mis tõstab oluliselt töö efektiivsust suurte andmemassiividega, mille jaoks ei piisa otseselt kaardistatud vahemälu rea suurusest.

Protsessori juhiste laiendatud komplekt võimaldab teil rakendada automaatse indekseerimise tööriistu, et parandada massiividega töötamise tõhusust, samuti eellaadida juhiseid, mis on paigutatud täiendavasse sisemisse vahemällu. See lisavahemälu laiendab dünaamiliselt peamise otsekaardistatud vahemälu assotsiatiivsuse astet ja on lihtsam alternatiiv mitme assotsiatiivse organisatsiooni jaoks.

PA 7200 protsessor sisaldab uut 64-bitist multipleksliidest süsteemisiin Runway, mis rakendab tehingute jagamist ja toetab mälu sidususe protokolli. See liides sisaldab tehingupuhvreid, arbitraažiahelaid ja väliseid/sisemisi taktsageduse juhtahelaid.

1.3.3 Superskalaarprotsessori PA 8000 omadused

Protsessor PA-8000 kuulutati välja märtsis 1995 konverentsil COMPCON 95. Teatati, et selle jõudlusnäitajad jõuavad vastavalt 8,6 ühikuni SPECint95 ja 15 SPECfp95 ühikuni täisarvuliste ja reaalaritmeetiliste tehtete puhul. Praegu kinnitavad seda väga kõrget jõudlust selle protsessori baasil ehitatud tööjaamade ja serverite testid.

PA-8000 protsessor on integreerinud kõike tuntud meetodid kiirendada käsu täitmist. See põhineb "intelligentse täitmise" kontseptsioonil, mis põhineb käskude ebakorrapärase täitmise põhimõttel. See omadus võimaldab PA-8000-l saavutada maksimaalse superskalaarse jõudluse tänu laialdast kasutamist mehhanismid andmete ja riistvarahalduse konfliktide automaatseks lahendamiseks. Need tööriistad täiendavad hästi teisi kristallstruktuuri sisseehitatud arhitektuurseid komponente: suur hulk juhtivaid funktsionaalseid üksusi, tööriistu üleminekute suuna ennustamiseks ja juhiste täitmiseks eeldusel, vahemälu optimeeritud korraldust ja suure jõudlusega siiniliidest. .

PA-8000 kõrge jõudluse määrab suures osas suure hulga funktsionaalsete seadmete olemasolu, mis sisaldavad 10 täitevseadmed: kaks aritmeetilist loogikaühikut (ALU) täisarvuliste toimingute tegemiseks, kaks ühikut andmete nihutamise/ühendamise toimingute tegemiseks, kaks ühikut ujukomaarvude korrutamiseks/liitmiseks, kaks jagamis-/ruutjuureühikut ja kaks ühikut laadimis-/laadimistoimingute kirjete jaoks .

PA-8000 protsessori ebakorrapärane täitmine tagab konveieri laadimise riistvaralise ajastamise ja funktsionaalsete üksuste parema kasutamise. Igas tsüklis saab täitmiseks väljastada kuni neli käsku, mis sisenevad 56-realisse ümberkorralduspuhvrisse. See puhver võimaldab funktsionaalseid üksusi hõivatud hoida ja vähendab tõhusalt ressursside konkurentsi. ressursside konfliktid. Crystal suudab analüüsida kõiki 56 käsuread samal ajal ja andke igas tsüklis funktsionaalsetele seadmetele täitmiseks valmis 4 käsku. See võimaldab protsessoril automaatselt tuvastada käsutaseme paralleelsust.

Superskalaarprotsessor PA-8000 pakub täielikku 64-bitiste toimingute komplekti, sealhulgas aadressi aritmeetikat, fikseeritud punkti ja ujukoma aritmeetikat. Samal ajal jääb kristall täielikult ühilduvaks 32-bitiste rakendustega. See on esimene protsessor, mis rakendab 64-bitist PA-RISC arhitektuuri. See säilitab täieliku ühilduvuse eelmiste ja tulevaste PA-RISC rakendustega.

Matriit on valmistatud 0,5-mikronilise CMOS-tehnoloogia abil, mille toitepinge on 3,3 V ning tulevikus on oodata elementide edasist vähendamist.

2. PARISC ARHITEKTUURIGA PROTSESSORITEL PÕHINEVATE HEWLETT-PACKARDI SERVERI FUNKTSIOONID

Hewlett-Packard Company asutati Californias 1938. aastal, et luua elektroonilisi katse- ja mõõteseadmeid. Ettevõte arendab, toodab, turustab ja teenindab praegu süsteeme kaubanduslikud rakendused, tootmisprotsesside automatiseerimine, arendus-, testimis- ja mõõtmisprotsessid, samuti analüütilised ja meditsiinilised instrumendid ja süsteemid, perifeeriaseadmed, kalkulaatorid ja komponendid kasutamiseks paljudes tööstusharudes. See müüb üle 4500 toote, mida kasutatakse tööstuses, äris, teaduses, hariduses, meditsiinis ja inseneritöös.

Kaasaegsete Hewlett-Packardi arvutite arendamise aluseks on PA-RISC arhitektuur. Ettevõte töötas selle välja 1986. aastal ja sellest ajast alates on see tänu integreeritud tehnoloogia edule läbinud mitmeid arenguetappe alates mitmekiibilisest kuni ühe kiibi täitmiseni. PA-RISC arhitektuur töötati välja, võttes arvesse võimalust ehitada üles mitme protsessoriga süsteeme, mida rakendatakse vanemates serverimudelites.

2.1 HP9000 klassi D serverid

Töörühmaserverite turul on HP-l üsna lai valik HP9000 klassi D süsteeme. Tegemist on suhteliselt odava süsteemiseeriaga, mis konkureerib PC-põhiste serveritega. Need süsteemid põhinevad PA-RISC protsessori arhitektuuril (75 ja 100 MHz PA-7100LC, 100 ja 120 MHz PA-7200 ja 160 MHz PA-8000) ja töötavad operatsioonisüsteem HP UNIX.

Mudelid D200, D210 ja D310 on (vastavalt) ühe protsessoriga süsteemid. Mudeleid D250, D260, D270 ja D350 saab varustada kas ühe või kahe protsessoriga. Oma D3XX mudelitega rõhutab HP kõrget käideldavusfunktsiooni, nagu kuumvahetusega sisemised kõvakettad, RAID-võimekus ja katkematu toiteallikas. Nendel mudelitel on ka täiustatud võimalused RAM-i ja I / O alamsüsteemi suurendamiseks.

D2XX mudelitel on 5 I/O laienduspesa ja 2 SCSI-2 kõvakettasahtlit. D3XX mudelid suurendavad I/O laienduspesade arvu 8-ni ja 5 pesa mahutavad kiireid/laia SCSI-2 kõvakettaid, mida saab kiirvahetusega vahetada.

Seeria vanemad mudelid pakuvad võimalust laiendada ECC RAM-i kuni 1,5 GB-ni, samas kui komplekti koefitsient võib suureneda kuni 12-ni. kettaruum väliste kettamassiivide kasutamisel võib see ulatuda 5,0 TB-ni.

2.2 HP9000 klassi K serverid

HP9000 K-klassi serverid on keskklassi süsteemid, mis toetavad sümmeetrilist multitöötlust (kuni 4 protsessorit). Lisaks klassi D süsteemidele põhinevad need PA-RISC arhitektuuril (120 MHz PA-7200 koos 256/256 KB või 1/1 MB L1 käsu/andmevahemäluga ning 160 ja 180 MHz PA-8000 koos käskude/andmetega esimese taseme mälu 1/1 MB, töötab protsessori taktsagedusel).

K-klassi serverid on loodud pakkuma suurt süsteemi läbilaskevõimet. Kõrge jõudluse säilitamise peamised komponendid on süsteemisiin, mille maksimaalne ribalaius on 960 MB / s, suur RAM ühe veakontrolli ja -parandusega (ECC) mahuga kuni 4 GB 32-kordse triibuga, mitme kanaliga I / O alamsüsteem ribalaiusega kuni 288 MB /s, standardne kiire Fast/Wide Differential SCSI-2 siin, samuti lisavõimalused kiirete võrkude ja kanalite nagu FDDI, ATM ja Fibre Channel ühendamiseks.

Serveri disain pakub 4 lahtrit kettaseadmete paigaldamiseks ja spetsiaalsete riiulite (kappide) abil laiendamiseks. kettasalvestus süsteemi saab suurendada 8,3 TB-ni.

2.3 HP9000 klassi T sümmeetrilised mitmeprotsessorilised serverid

HP kõige võimsam ja laiendatav UNIX-põhiste ettevõtteserverite sari on T-klassi perekond HP9000. See on järgmise põlvkonna serverid, mille ettevõte töötas välja pärast HP9000 mudelit 870. Esialgu ilmusid turule HP9000 T500 süsteemid, mis võimaldasid 12 PA7100 protsessorile, teatas HP seejärel 14 protsessoriga T520 süsteemidest, mis põhinevad 120 MHz PA7150 protsessoril. PA-8000 protsessoril põhinevad 12 protsessoriga süsteemid T600 on nüüdseks välja kuulutatud ja peaksid hakkama tarnima 1997. aastal. Olemasolevad süsteemid(T500 ja T520) võimaldavad asendada vanad protsessorid PA-8000 protsessoritega.

T-klassi serverite arhitektuuri iseloomulik tunnus on suur vahemälu maht käskude (1 MB) ja andmete (1 MB) jaoks süsteemi iga protsessori jaoks. T-klassi serverid kasutavad 64-bitist jagatud tehingusiini, mis toetab kuni 14 protsessorit, mis töötavad sagedusel 120 MHz. Selle siini, nagu ka Runway siini, tõhusus on 80%, pakkudes 768 MB/s püsiseisundi läbilaskevõimet tippvõimsusega 960 MB/s.

T-klassi serverid võivad toetada kuni 8 HP-PB (HP Precision Bus) linki, mis töötavad kiirusega 32 MB/s, kuid süsteemi põhireck toetab ainult ühte HP-PB linki. I / O alamsüsteemi täieliku konfiguratsiooni tagamiseks on vaja paigaldada 7 laiendusriiulit, mis hõivavad üsna suure ala. Maksimaalne I/O ribalaius täielikult konfigureeritud 8-rack-süsteemis on 256 MB/s, mis on väiksem kui K-klassi serverite I/O ribalaius.Kuid RAID-massiivide kasutamisel on ketta maksimaalne salvestusmaht 20 TB .

See kahetasandiline serveri siini struktuur tagab optimaalse tasakaalu protsessori ja I/O nõuete vahel, tagades süsteemi suure läbilaskevõime isegi suure töökoormuse korral. Protsessorid võimaldavad juurdepääsu põhimälule võimsa protsessori-mälu süsteemisiini kaudu, mis säilitab kogu süsteemi vahemälu ühtse oleku. Tulevaste süsteemide jaoks on kavandatud I/O alamsüsteemi ribalaiuse neli korda suurendamine.

2.4 HP9000 ettevõtte paralleelserveri perekond

Üks HP uusimaid tooteid on paralleelsüsteemide perekond, mida praegu esindavad kaks mudelit ESP21 ja ESP30. Nende süsteemide põhikontseptsioon on üsna lihtne. See seisneb kombineeritud struktuuri loomises, mis ühendab võimalused ja tugevused aja testitud, suure jõudlusega sümmeetriline multitöötlus praktiliselt piiramatu jõudluse ja skaleeritavuse potentsiaaliga, mida on võimalik saavutada paralleelse arhitektuuriga. Selle kombinatsiooni tulemuseks on suure jõudlusega arhitektuur, mis tagab erakordselt kõrge paralleelse andmetöötluse taseme.

Erinevalt mõnest teisest paralleelarhitektuurist, mis kasutavad lõdvalt ühendatud ühe protsessori sõlme, kasutab ESP21 ja ESP30 serverite paralleelarhitektuur skaleeritavate ehitusplokkidena suure jõudlusega SMP-tehnoloogiat. Selle lähenemisviisi eeliseks on rakendussüsteemide kasutamine arvutusvõimsus ja mitme tihedalt ühendatud protsessori võimalused SMP infrastruktuuris ning tagavad tõhusalt parima võimaliku rakenduse jõudluse. Vajadusel saab süsteemile lisada täiendavaid SMP-mooduleid, et suurendada paralleelsuse astet, et skaleerida süsteemi üldist jõudlust, mahtu, I/O ribalaiust vms. süsteemi ressursse nii põhi- kui ka kettamälu.

Selle seeria tooted on mõeldud peamiselt mastaapsuse tagamiseks tavapärasest SMP-arhitektuurist suuremahuliste otsustussüsteemide, veebipõhiste tehingute töötlemise süsteemide ja andmehoidlate jaoks veebis. Enamiku rakenduste puhul pakuvad ESP mudelid jõudlust peaaegu lineaarselt. See saavutatakse ESP-sõlmede suure jõudlusega SMP siini arhitektuuri kasutamisega koos võimalusega installida täiendavaid SMP-sõlmi, kasutades HP Fibre Channel Enterprise Switchi. Kõikide süsteemiressursside haldamine toimub ühest halduskonsoolist.

Kui on vaja kõrget kättesaadavust, toetavad ESP-süsteemid spetsiaalset MC/ServiceGuardi tarkvarakihti. Need tööriistad pakuvad tõhusat kombinatsiooni suurest jõudlusest, skaleeritavusest ja kõrgest saadavusest ning lisaks standardsetele RAS-i (Usaldusväärsus, Kättesaadavus ja Teenindatavus) võimalustele võimaldavad sõlmede kuumavahetust.

Tegelikult pakub EPS-seeria vahendeid klassi K (EPS21) ja T (EPS30) mudelite ühendamiseks üheks süsteemiks. 16-kanaliline Fibre Channeli lüliti võimaldab mudelil EPS21 kuni 64 protsessorit (tulevikus kuni 256 protsessorit) ja mudelis EPS30 kuni 224 protsessorit (tulevikus kuni 768 protsessorit). Süsteemide maksimaalne läbilaskevõime võib ulatuda 15 GB / s tasemeni.

Sissejuhatus

Peal see etapp Teaduse ja tehnoloogia arengu tõttu on riistvaraplatvormi ja süsteemi konfiguratsiooni valimine äärmiselt keeruline ülesanne. See on tingitud eelkõige loodusest rakendatud süsteemid, mis võib suuresti määrata arvutuskompleksi kui terviku töökoormuse. Tihti osutub aga koormuse enda piisava täpsusega ennustamine lihtsalt keeruliseks, eriti kui süsteem peab teenindama mitut oma vajadustelt heterogeenset kasutajagruppi. Tuleb märkida, et konkreetse riistvaraplatvormi ja konfiguratsiooni valiku määravad ka mitmed üldised nõuded, mis kehtivad tänapäevaste arvutisüsteemide omadustele. Nende hulka kuuluvad: kulu/jõudluse suhe, töökindlus ja tõrketaluvus, mastaapsus, ühilduvus ja tarkvara kaasaskantavus. Peamiseks väljakutseks kogu PA-RISC süsteemimudelite valiku kujundamisel oli luua arhitektuur, mis oleks kasutaja seisukohalt ühesugune kõikidele süsteemimudelitele, sõltumata nende igaühe hinnast ja jõudlusest. Selle lähenemisviisi tohutuid eeliseid, mis võimaldab teil uutele mudelitele üleminekul hoida olemasolevat tarkvara mahajäämust, hindasid kiiresti nii arvutitootjad kui ka kasutajad ning sellest ajast alates on peaaegu kõik arvutiseadmete müüjad need põhimõtted kasutusele võtnud, pakkudes ühilduvate arvutite seeriat.

Probleemi sõnastamine

Selle kursuseprojekti käigus on vaja arvestada olemasolevate protsessorite arhitektuuritüüpidega, iseloomustada nende eeliseid ja puudusi. Üksikasjalikult tuleb läbi mõelda igasugune arhitektuur (antud juhul on see Hewlett Packardi PA-RISC arhitektuur), samuti kaaluda valitud arhitektuuriga protsessorite kasutusvaldkondi (PA-RISC-l põhinevate Hewlett Packardi serverite omadused protsessorid). Samuti on vaja välja töötada draiveriprogramm teabe edastamiseks kohtvõrgu tööjaamade vahel.

Järeldus

Selles kursuse projektis käsitletakse põhiprotsessorite arhitektuure. Hewlett Packardi PA-RISC arhitektuuri käsitletakse üksikasjalikult, analüüsitakse selle arhitektuuri eeliseid ja puudusi. Samuti käsitletakse PA-RISC arhitektuuriga protsessorite rakendusvaldkondi (PA-RISC protsessoritel põhinevate Hewlett Packardi serverite omadused). Rakendus sisaldab programmi, mis tagab teabeedastuse kohtvõrgu tööjaamade vahel.

Käsuarhitektuuri kiht sisaldab masinakäskude komplekti, mida täidab tõlgi püsivara või riistvara.

Kaks peamist arvutitööstuses kasutatavat käsukomplekti arhitektuuri on tänapäeval CISC ja RISC arhitektuurid.

- Täielik juhiskomplekt (CISC-arhitektuur, mikroprotsessoril arvuti koos täieliku juhistega)

– vähendatud käsukomplektiga arvuti (RISC-arhitektuur, vähendatud käsukomplektiga arvuti)

| CISC | RISC | |

| asutaja, modell | IBM, IBM/360 | CDC6600 (Cray) |

| Tänane juht | x86 | Alpha, PowerPC, SPARC |

| Turg | Personaalarvutid(ühilduvuse tõttu odava tarkvaraga, mille kogumaksumus - 90ndate alguses - oli mitu miljardit USA dollarit) | Suure jõudlusega arvutid (tarkvara hind ei ole nii märkimisväärne) |

| Rakendamine | Püsivara (tõlgendus) | Riistvara |

| Üldotstarbeliste registrite arv | väike | suur |

| Käsuvorming | suur hulk erineva bitipikkusega käsuvorminguid | fikseeritud pikkusega ja fikseeritud vormingu käsud |

| Adresseerimine | suur hulk adresseerimismeetodeid, kaheaadressilise käsuvormingu ülekaal | lihtsad adresseerimismeetodid, kolme aadressiga käsuvorming |

asutaja, modell

Esimese protsessori mudelite - i8086/8088 - korraldamise eesmärk oli eelkõige vähendada tolleaegsete süsteemide jaoks kriitilise tähtsusega programmide hulka, mida eristasid väikesed RAM. Käsusüsteemi rakendatavate toimingute ulatuse laiendamine võimaldas vähendada programmide suurust, aga ka nende kirjutamise ja silumise töömahukust. Käskude arvu suurenemine muutis aga nende topoloogiliste ja püsivara rakenduste arendamise keerukamaks. Viimane väljendus nii CISC protsessorite arendusaja pikenemises kui ka avaldumises erinevaid vigu nende töös.

Need puudused tingisid vajaduse välja töötada alternatiivne arhitektuur - RISC, mille eesmärk oli eelkõige vähendada käskude voo ebakorrapärasust, vähendades nende koguarvu.

Tänane juht

Inteli protsessorid alates 486-st sisaldavad RISC-tuuma, mis täidab kõige lihtsamad (ja tavaliselt kõige tavalisemad) käsud ühes andmeteetsüklis ja tavapärane tehnoloogia Keerulisemaid käske tõlgendab CISC. Selle tulemusena täidetakse tavalised käsud kiiresti, samas kui keerukamad ja harvemad käsud on aeglased. Kuigi see "hübriidne" lähenemine ei tööta nii kiiresti kui RISC, on sellel arhitektuuril mitmeid eeliseid, kuna see võimaldab vana tarkvara ilma muudatusteta kasutada.

Esimene mudel Inteli protsessor, mis lähenes arhitektuurile RISC– PentiumPRO (täpne RISC-organisatsioon – täielik RISC-arhitektuur).

Rakendamine

Tõlgenduskihi kõrvaldamine tagab enamiku käskude kiire täitmise. CISC-arvutites saab keerukamad käsud jagada mitmeks osaks, mis seejärel täidetakse mikrokäskude jadana. See lisatoiming vähendab masina kiirust, kuid seda saab kasutada käskude jaoks, mida harva kohtab.

Registrite arv

RISC-arhitektuuri arengu määras suuresti edusammud optimeerivate kompilaatorite loomise vallas. Just kaasaegne kompileerimistehnika võimaldab efektiivselt ära kasutada suurema arvu registrite, konveierkorralduse ja käskude kiirema täitmise eeliseid.

Registrite suur arv võimaldab protsessorikiibil registritesse rohkem andmeid salvestada pikema aja jooksul ja muudab kompilaatoril muutujate jaoks registrite jaotamise lihtsamaks.

Käsuvorming

Käske peaks olema lihtne dekodeerida. Ühe sekundi jooksul kutsutavate käskude arvu piirang sõltub üksikute käskude dekodeerimisprotsessist. Käsud dekodeeritakse, et määrata, milliseid ressursse nad vajavad ja milliseid toiminguid teha. Kõik vahendid, mis aitavad seda protsessi lihtsustada, on kasulikud. Näiteks kasutatakse neid tavalised meeskonnad fikseeritud pikkusega ja väikese arvu väljadega. Vähem erinevad vormingud käske, seda parem.

Adresseerimine

Lihtsad adresseerimismeetodid võimaldavad käskude dekodeerimist oluliselt lihtsustada. Registristruktuuri korraldus on RISC peamine eelis ja põhiprobleem. Peaaegu igas RISC-arhitektuuri teostuses kasutatakse kolmekohalisi töötlusoperatsioone, mille puhul on tulemusel ja kahel operandil sõltumatu adresseerimine - R1:= R2, R3. See võimaldab teil ilma märkimisväärse ajakuluta valida adresseeritavate operandide hulgast operandid. tegevusregistrid ja kirjutage toimingu tulemus registrisse. Lisaks annavad ternaartehted kompilaatorile rohkem paindlikkust kui tavalised CISC 2-kohalised registrist-mällu toimingud. Koos kiire aritmeetikaga muutuvad registritevahelised RISC-toimingud väga võimsaks viisiks protsessori jõudluse suurendamiseks.

Sissejuhatus

RISC (Reduced Instruction Set Computer) on vähendatud käsukomplektiga arvuti. RISC-i iseloomustavad järgmised omadused:

· Masinakäskude fikseeritud pikkus (nt 32 bitti) ja lihtne käsuformaat.

· Spetsiaalsed käsud mälutoiminguteks – lugemine või kirjutamine. Loe-muuda-kirjutamisoperatsioone pole. Kõik "muutmistoimingud" tehakse ainult registrite sisuga (laadimise ja salvestamise arhitektuur).

· Suur hulk üldotstarbelisi registreid (32 või enam).

· Puudub tugi sellistele operatsioonidele nagu lühendatud andmetüüpide muutmine – bait, 16-bitine sõna. Näiteks sisaldas DEC Alpha käsusüsteem ainult toiminguid 64-bitiste sõnadega ning nõudis protseduuride väljatöötamist ja järgnevat väljakutsumist, et sooritada toiminguid baitidega, 16- ja 32-bitiste sõnadega.

· Püsivara puudumine protsessori enda sees. See, mida mikroprogrammid CISC-protsessoris käivitavad, täidetakse RISC-protsessoris tavalise (ehkki spetsiaalsesse salvestusruumi paigutatud) masinkoodina, mis ei erine põhimõtteliselt OS-i tuuma ja rakenduste koodist.

Tüüpilised RISC-lahendused:

· Spekulatiivne hukkamine. Kui protsessor puutub kokku tingimusliku harukäsuga, täidab protsessor (või vähemalt loeb käskude vahemällu) mõlemad harud korraga, kuni haru juhtavaldist hinnatakse. Võimaldab vältida torujuhtme seisakuid tingimuslike hüpete ajal.

· Registreeri ümbernimetamine. Iga protsessori register on tegelikult mitu paralleelset registrit, mis sisaldavad väärtuse mitut versiooni. Kasutatakse spekulatiivse hukkamise rakendamiseks.

RISC protsessoril on suurenenud jõudlus lihtsustades juhiseid, et nende dekodeerimine oleks lihtsam ja täitmisaeg lühem. Esimestel RISC-protsessoritel polnud isegi korrutamise ja jagamise juhiseid. See muudab ka kiirendamise lihtsamaks ja muudab superskalaarse (käskude paralleelsus mitme täitmisüksuse vahel) tõhusamaks.

Esimeste RISC-arhitektuuride puhul on enamik dekodeerimise lihtsustamise juhiseid ühepikkused ja sarnane struktuur, aritmeetilised tehted töötada ainult registritega ja töö mäluga läbib laadimise (laadimise) ja salvestamise (salvestamise) eraldi juhised. Need omadused on võimaldanud paremini tasakaalustada torujuhtmete ühendamise etappe, muutes torujuhtmed RISC-is palju tõhusamaks ja võimaldades tõsta taktsagedust.

Lihtsatele juhistele keskendumine viib RISC-arhitektuurini, mille eesmärk on muuta käsud nii lihtsaks, et neid saab hõlpsasti konveierdada ja et need ei võtaks kõrgetel sagedustel rohkem kui ühte taktitsüklit konveieri sammu kohta.

Hiljem märgiti, et RISC-i kõige olulisem omadus on andmetöötluse ja mälule juurdepääsu käskude eraldamine – juurdepääs mälule käib ainult laadimis- ja salvestamiskäskude kaudu ning kõik muud käsud piirduvad sisemiste registritega. See lihtsustas protsessorite arhitektuuri: võimaldas fikseeritud pikkusega käske, lihtsustas torujuhtmeid ja isoleeritud loogikat, mis käsitleb mälu juurdepääsu viivitusi vaid kahes käsus. Sellest tulenevalt on RISC-arhitektuure hakatud nimetama ka laadimis/salvestamise arhitektuurideks.

"Vähendatud käsustik" on valesti mõistetud kui käskude arvu minimeerimine käsukomplektis. Tegelikult on paljudel RISC-protsessoritel rohkem juhiseid kui CISC-protsessoritel. Tegelikult väheneb iga üksiku juhise töö maht (ja aeg) - maksimaalselt ühe mälupöördustsükli võrra. CISC-protsessorite keerukate käskude täitmiseks võib vaja minna sadu juurdepääsutsükleid mälule.

Esimene süsteem, mida võib nimetada RISC-süsteemiks, on CDC 6600 superarvuti, mille lõi 1964. aastal Seymour Creme. Hiljem ilmus nali, et termin RISC tähistab tegelikult "Seymour Cray poolt tõesti leiutatud" ("Really leiutas Seymour Cray").

Esimene katse luua RISC-protsessor kiibil tehti IBM-is aastal 1975. Selle töö tulemusel loodi IBM 801 protsessoriperekond, mis ilmus kiibi kujul ROMP nime all aastal 1981. ROMP tähendab Research OPD ( Office Product Division) Mikroprotsessor, siis on olemas "Research MP". Järgnesid mitmed uurimisprojektid, millest ühe tulemuseks oli POWER-süsteem.

Pärast seda, kui x86 arhitektuuriga protsessorid muudeti superskalaarseks RISC-arhitektuuriks, võib öelda, et valdav enamus praegustest protsessoritest põhinevad RISC-arhitektuuril.

RISC-arhitektuur on vähendatud juhiste komplektiga arvuti. See on teatud tüüpi mikroprotsessori arhitektuur, mis kasutab väikest optimeeritud juhiste kogumit, erinevalt varasematest arhitektuuritüüpidest, millel on suur hulk algoritmilisi andmeid. Mõiste RISC võttis kasutusele David Patterson Berkeley RISC projektist.

Definitsioon

Piiratud käsukomplekti arvuti on seade, mille käsustikuarhitektuuril (ISA) on atribuutide komplekt, mis võimaldab sellel olla väiksemaid tsükleid käsu kohta (CPI) kui komplekskäsukomplektil arvuti kohta (CISC). RISC-i üldkontseptsioon on arvuti kontseptsioon, mis sisaldab väikest komplekti lihtsaid ja üldisi algoritme, kuid mitte keerukate ja spetsiifiliste jadade laiendatud komplekti. Teine RISC-i levinud omadus on laadimis-/salvestamise arhitektuur, kus mälule pääseb ligi ainult kindlate juhistega.

Ajalugu ja areng

Esimesed RISC-projektid pärinesid IBM-ist, Stanfordist ja UC-Berkeleyst 70ndatel ja 80ndatel. XX sajand. IBM 801, Stanford MIPS ja Berkeley RISC I ja II disainiti sarnase filosoofiaga, mis sai tuntuks kui RISC. Mõned disainifunktsioonid olid enamikule RISC-protsessoritele ühised:

Kui mitmed 1960. ja 70. aastate arvutid olid RISCi eelkäijad, siis praegune kontseptsioon pärineb 1980. aastatest. Eelkõige suurendavad seda kaks projekti Stanfordis ja California ülikoolis kontseptuaalne idee. Stanfordi MIPS-ist saaks äriliselt edukas mudel, samas kui UC Berkeley andis kogu kontseptsioonile nime, mida turustati kui SPARC. Teine selle ajastu edu oli IBMi jõupingutused, mis lõpuks viisid Power Architecture'i. Kuna need arengud arenesid 1980ndate lõpus ja eriti 1990ndate alguses, õitsesid paljud sellised projektid, mis esindasid Unixi tööjaamade turul olulist jõudu, samuti manustatud protsessoreid. laserprinterid, ruuterid ja sarnased tooted.

RISC-arhitektuuri plussid ja miinused

Lihtsaim viis RISC arhitektuuri eeliste ja haavatavuste uurimiseks on võrrelda seda eelmise CISC arhitektuuriga. CISC-arhitektuuri põhieesmärk on täita ülesanne vähemate koosteliinidega. See saavutatakse töötlemisriistvara loomisega, mis on võimeline mõistma ja sooritama mitmeid toiminguid. Selle jaoks konkreetne ülesanne CISC-protsessoriga on kaasas spetsiifiline juhis (MULT). Täitmisel laadib see käsk kaks väärtust eraldi registritesse, korrutab täitmisüksuses olevad operandid ja salvestab seejärel toote vastavasse registrisse. Seega saab kogu kahe arvu korrutamise ülesande täita ühe juhisega: MULT 2:3, 5:2.

MULT on nn kompleksjuhend. Käsk töötab otse arvuti mälupankades ja ei nõua programmeerijalt ühegi laadimis- või salvestamisfunktsiooni selgesõnalist väljakutsumist. See on väga sarnane kõrgema taseme keele käsuga. Näiteks kui eeldame, et a tähistab väärtust 2:3 ja b tähistab väärtust 5:2, siis on see käsk avaldisega identne C a = a * b.

Selle süsteemi üks peamisi eeliseid on see, et kompilaator peab tegema minimaalselt tööd, et tõlkida kõrgetasemeline keeleavaldus assambleesse. Kuna koodi pikkus on suhteliselt lühike, on juhiste salvestamiseks vaja väga vähe RAM-i. CISC ja RISC protsessorite arhitektuuride võrdlevas analüüsis on rõhk keeruliste käskude rakendamisel otse riistvaras.

RISC-lähenemine

RISC-protsessorid kasutavad ainult elementaarseid käske, mis täidetakse ühe taktitsükli jooksul. Seega saab ülalkirjeldatud käsu MULT jagada kolmeks eraldi käsuks: LOAD, mis liigutab andmed mälupangast PROD registrisse, mis leiab kahe registri sees paikneva operandi korrutise ja STORE, mis liigutab andmeid registrist. mälupankadesse. CISC-meetodis kirjeldatud täpsete sammude seeria järgimiseks peab programmeerija kodeerima neli koosterida:

KOORMUS A, 2:3.

KOORMUS B, 5:2.

PROD A, B.

KAUPLUS 2:3, A.

Alguses võib see tunduda palju vähem tõhus viis toimingu lõpuleviimine, sest koostetaseme juhiste salvestamiseks on rohkem koodiridu ja rohkem RAM-i. Samuti peab koostaja rohkem tööd tegema, et tõlkida kõrgetasemeline keeleavaldus selle vormi koodiks.

CISC ja RISC võrdlus

Allpool on CISC ja RISC arhitektuuri võrdlus:

- Rõhk riistvarale.

- Sisaldab mitu tundi keerulisi juhiseid.

- Väikesed koodisuurused, suured tsüklid sekundis.

- Transistorid, mida kasutatakse keerukate juhiste salvestamiseks.

- Rõhk tarkvaral.

- Lühendatud juhend, mis ei nõua palju aega.

- Madalad tsüklid sekundis, suured koodisuurused.

- Kulutab rohkem transistore mäluregistritele.

RISC-strateegia toob kaasa väga olulisi eeliseid. Kuna iga käsu täitmiseks on vaja ainult ühte tsüklit, töötab kogu programm umbes sama aja jooksul kui mitmesilindriline MULT-käsk. Need RISC-i "vähendatud juhised" nõuavad vähem riistvararuumi transistore kui keerukad juhised, jättes rohkem ruumi tavalistele registritele. Kuna kõik käsud täidetakse korraga (näiteks üks takttsükkel), on konveierid võimalik.

Protsessi omadused

Käskude LOAD ja STORE eraldamine vähendab tegelikult arvuti töömahtu. Pärast CISC-stiilis MULT käsu täitmist kustutab protsessor registrid automaatselt. Kui mõnda operandit on vaja kasutada muuks arvutuseks, peab protsessor andmed mälupangast uuesti registrisse laadima. RISC-is jääb operand registrisse seni, kuni sellele laaditakse mõni muu väärtus.

CISC-lähenemine püüab minimeerida iga programmi käskude arvu, ohverdades tsüklite arvu käsu kohta. RISC, vastupidi, vähendab tsüklite arvu iga programmi juhiste arvelt.

Kaubandusliku rakendamise raskused

Vaatamata RISC-põhise töötlemise eelistele kulus aastakümneid, enne kui RISK-kiibid kaubanduslikult kättesaadavaks said. See oli suuresti tingitud tarkvara toe puudumisest.

Kui Apple'i Power Macintoshi sari, mis kasutas RISC- ja Windows NT-põhiseid kiipe, on RISC-ühilduv, loodi Windows 3.1 ja Windows 95 CISC-protsessoreid silmas pidades. Paljud ettevõtted ei tahtnud riskida tärkava RISC-tehnoloogiaga. Ilma ärihuvita ei ole protsessorite arendajad suutnud toota RISC-kiipe piisavalt suurtes kogustes, et muuta nende hind konkurentsivõimeliseks.

Teine suur takistus oli Inteli olemasolu. Kuigi nende CISC-kiibid muutusid üha mahukamaks ja raskemini kujundatavaks, oli Intelil ressursse võimsate protsessorite arendamiseks. Kuigi RISC-kiibid võisid teatud valdkondades Inteli jõupingutusi ületada, ei olnud erinevused piisavalt suured, et veenda ostjaid tehnoloogiat vahetama.

RISC üldine eelis

Tänapäeval on Intel x86 ainus kiip, mis säilitab CISC arhitektuuri. Selle põhjuseks on eelkõige edusammud teistes valdkondades. arvutitehnoloogia. RAM-i hind on järsult langenud. 1977. aastal maksis 1 MB DRAM-i umbes 5000 dollarit. 1994. aastaks maksab sama palju mälu vaid 6 dollarit (inflatsiooni järgi). Ka kompilaatoritehnoloogia on muutunud keerukamaks, seega on RISC RAM-i kasutamine ja tarkvarale keskendumine muutunud ideaalseks.

Juhendikomplekti filosoofia

RISKi definitsiooni väärarusaam seisneb selles, et protseduurid elimineeritakse, mille tulemusena väheneb algoritmide kogum. Aastate jooksul on RISC-rutiinid suurenenud ja tänapäeval on paljudel neist laiem funktsioonide komplekt kui CISC-protsessoritel.

Mõiste "vähendatud protseduuride komplekt" viitab asjaolule, et iga käsuga tehtava töö maht väheneb (mitte rohkem kui üks mälutsükkel) võrreldes keerukamate CISC protseduuridega, mis nõuavad ühe käsu täitmiseks kümneid tsükleid. RISC-arhitektuuril on tavaliselt eraldi sisend- ja andmetöötlusalgoritmid.

Juhise vorming

Enamikul RISC-arhitektuuridel on fikseeritud pikkusega juhised (tavaliselt 32 bitti) ja lihtne kodeerimine, mis lihtsustab oluliselt toomise, dekodeerimise ja väljastamise loogikat. Üks 32-bitiste käskude puudusi on kooditiheduse vähendamine, mis on tööjaamades ja serverites manustatud andmetöötluse jaoks ebasoodne tegur. RISC-arhitektuurid olid algselt mõeldud teeninduseks. Selle probleemi lahendamiseks on mitmel arhitektuuril, nagu ARM, Power ISA, MIPS, RISC-V ja Adipteva Epiphany, valikuline lühike, lühendatud juhiste vorming või käskude tihendamise funktsioon. SH5 järgib ka seda mustrit, kuigi see on pikema lisamisega vastupidises suunas arenenud multimeediumijuhised algsele 16-bitisele kodeeringule.

Seadmete kasutamine

Mis tahes üldise jõudluse taseme jaoks on RISC-kiibil tavaliselt palju vähem põhiloogikale pühendatud transistore, mis algselt võimaldas disaineritel registri suurust ja sisemist paralleelsust suurendada.

Muud funktsioonid, mida RISC-arhitektuurides tavaliselt leidub, on järgmised:

- Protsessori keskmine jõudlus läheneb ühele käsule tsükli kohta.

- Üksikjuhisevorming – kasutab üht sõna opkoodiga samades kohtades, et hõlbustada dekodeerimist.

- Kõiki üldotstarbelisi registreid saab kõigis käskudes kasutada allika/sihtkohana, lihtsustades kompilaatorite arendamist (ujukomaregistrid salvestatakse sageli eraldi).

- Lihtsad režiimid keeruka adresseerimisega, mis täidetakse käsujadadega.

- Riistvaras mitu andmetüüpi (nt baidistring või BCD).

RISC-i disainilahendused tutvustavad ka Harvardi mälumudelit, kus juhised ja andmed on kontseptuaalselt eraldatud. See tähendab, et koodi salvestamise mälu muutmine ei pruugi mõjutada protsessori poolt täidetavaid käske (kuna CPU-l on eraldi käsud ja andmete vahemälu) kuni spetsiaalse sünkroonimisjuhise väljastamiseni. Teisest küljest võimaldab see samaaegset juurdepääsu vahemäludele, mis sageli parandab jõudlust.

RISC-arhitektuuri omadused

Arvutitööstuse algusaegadel tehti programmeerimine mõlemas masinkoodis, mis soodustas võimsate ja lihtsalt kasutatavate juhiste kasutamist. Seetõttu püüdsid CPU disainerid kavandada algoritme, mis suudaksid teha võimalikult palju tööd. Kõrgema taseme keelte tulekuga hakkasid arhitektid looma erijuhised teatud kesksete mehhanismide otseseks rakendamiseks. Teine üldine eesmärk oli pakkuda iga algoritmi jaoks kõiki võimalikke adresseerimisrežiime, mida nimetatakse ortogonaalsuseks, et hõlbustada kompilaatori rakendamist.

Suhtumine selleks ajaks oli selline, et disain riistvara oli küpsem kui kompilaatori disain, seega on see iseenesest põhjus ka osa funktsionaalsuse rakendamiseks riistvaras või mikrokoodis, mitte ainult mälupiiranguga kompilaatoris (või selle genereeritud koodis). Pärast RISC-i tulekut hakati seda lähenemist nimetama Complex Instruction Set Computing ehk CISC-ks.

Ka protsessoritel oli suhteliselt vähe registreid mitmel põhjusel:

Praktiline kasutamine

RISC-protsessorarhitektuure kasutatakse nüüd paljudel platvormidel, alates nutitelefonidest ja tahvelarvutitest kuni mõne kõige võimsama superarvutini, nagu K-arvuti (2011. aasta 500 parima edetabelis).

21. sajandi alguseks on enamik madala profiiliga ja mobiilsed süsteemid põhineb RISC arhitektuuril. Näited:

- domineerib väikese võimsusega ja odavate manussüsteemide turul (2014. aastal 200–1800 MHz). Seda kasutatakse paljudes enamikes Android-süsteemides, Apple iPhone'is ja iPadis, Microsoft Windows telefon ( endine Windows Mobiil), RIM-seadmed (topic.risc.architecture), Nintendo Game Boy Advance, DS/3DS ja Switch.

- MIPS-liin (kasutatakse ühel hetkel paljudes SGI-arvutites) ja nüüd PlayStationis, PlayStation 2-s, Nintendo 64-s (ipb.risc.architecture), PlayStation Portable mängukonsoolides ja koduväravates, nagu Linksys WRT54G.

- Sega Super 32X-is, Saturnis ja Dreamcastis (viewtopic.php.risc.architecture) kasutatav Hitachi SuperH on nüüd välja töötatud ja müüdud Renesase poolt SH4-na.

- Atmel AVR-i kasutatakse paljudes tootesarjades alates Xboxi pihuarvutitest kuni BMW sõidukiteni.

- RISC-V (vbulletin.risc.architecture), viies avatud lähtekoodiga Berkeley RISC ISA, millel on 32-bitine aadressiruum, väike täisarvuline käsukomplekti tuum, eksperimentaalne "tihendatud" ISA kooditiheduse jaoks ning mõeldud standard- ja kohandatud jaoks laiendused.

- Tööjaamad, serverid ja superarvutid.

- MIPS (powered.by.smf.risc.architecture), Silicon Graphics (lõpetas MIPS-põhiste süsteemide ehitamise 2006. aastal).

- SPARC, Oracle (endine Sun Microsystems) ja Fujitsu (phorum.risc.architecture).

- IBM Power Architecture on leitud enamikus IBMi superarvutites, keskmistes serverites ja terminalijaamades.

- Hewlett-Packardi PA-RISC (phpbb.risc.architecture), mida nimetatakse ka HP-PA-ks (aegunud 2008. aasta lõpus).

- Alpha, mida kasutatakse Digital Equipment Corporationi, Compaqi ja HP tööjaamades, serverites ja superarvutites (lõpetatud alates 2007. aastast).

- RISC-V (powered.by.phpbb.risc.architecture), viies Berkeley RISC ISA, avatud lähtekoodiga 64- või 128-bitiste aadressiruumide ja terve tuum, mis on laiendatud ujukoma, pihustamise ja vektortöötlusega ning mõeldud laienduste jaoks koos juhistega võrkude, I / O, andmetöötluse jaoks. Rocketi 64-bitine superskalaarne disain on allalaadimiseks saadaval.

Võrdlus teiste arhitektuuridega

Mõned protsessorid on spetsiaalselt loodud väga väikeste käsukomplektidega, kuid need kujundused erinevad oluliselt traditsioonilistest RISC-arhitektuuridest, seega on neile antud muid andmeid, nagu minimaalne käsukomplekt (MISC) või transpordi algatatud arhitektuur (TTA).

RISC-arhitektuuridel on traditsiooniliselt olnud vähe edu lauaarvutite ja kaubaserverite turgudel, kus x86-põhised platvormid jäävad domineerivaks protsessori arhitektuuriks. See võib aga muutuda, kuna ARM-põhised protsessorid töötatakse välja suurema jõudlusega süsteemide jaoks. Tootjad, sealhulgas Cavium, AMD ja Qualcomm, on välja andnud ARM-i arhitektuuri alusel. ARM tegi 2017. aastal koostööd ka Crayga, et ehitada ARM-i arhitektuuril põhinev superarvuti. Arvutitööstuse liider Microsoft teatas, et teeb 2017. aastal Qualcommiga koostööd, et toetada Windows PC versioonid 10 Qualcomm Snapdragoni seadmetes. Need seadmed toetavad x86-põhist Win32 tarkvara, kasutades x86 protsessori emulaatorit.

Kuid lisaks töölauaareenile kasutatakse ARM RISC arhitektuuri laialdaselt nutitelefonides, tahvelarvutites ja paljudes manustatud seadmetes. Ka Intel Pentium Pro (P6) kasutab oma protsessorite jaoks sisemist RISC-protsessori tuuma.

Kui RISC-protsessorite arhitektuuri esialgsed kujundused erinesid oluliselt uuenduslikest CISC-disainidest, siis 2000. aastaks olid RISC-sarja suurima jõudlusega protsessorid peaaegu eristamatud CISC-sarja suurima jõudlusega protsessoritest.