Kus kasutatakse mittesüttivaid kangaid www.algo-textile.ru. Sääsevõrkude tarvikud sääsevõrkudele 2-sklad.ru.

PCI ja PCI-X

PCI ja PCI-X siinid

Sissejuhatus

PCI ja PCI-X siinid on tänapäevaste arvutite peamised sisend-/väljundlaiendussiinid; videoadapterite ühendamiseks täiendab neid AGP-port. I/O laiendussiinid (Expansion Bus) on süsteemitasemel ühenduvus: need võimaldavad adapteritel ja välisseadmete kontrolleritel otse kasutada arvutisüsteemi ressursse – mälu ja I/O aadressiruumi, katkestusi, otsejuurdepääsu mälule. Laiendussiinidega ühendatud seadmed saavad ise neid siine juhtida, pääsedes ligi teistele arvutiressurssidele. Laiendussiinid on mehaaniliselt teostatud pesade (pesakonnektorite) või tihvtidega; Neid iseloomustab juhtmete lühike pikkus, see tähendab, et need on puhtalt lokaalsed, mis võimaldab neil saavutada suuri töökiirusi. Neid siine ei pruugita konnektoritesse väljastada, vaid neid kasutatakse integreeritud emaplaatide seadmete ühendamiseks.

Alguses tutvustati PCI siini laiendusena (mezzanine siin) ISA siiniga süsteemidele. See töötati välja Pentiumi protsessoreid silmas pidades, kuid töötas hästi ka i486 protsessoritega. Hiljem sai PCI-st mõneks ajaks kesksiin: see ühendati protsessori siiniga suure jõudlusega sillaga (“põhjasild”), mis oli osa emaplaadi kiibistikust. Ülejäänud I/O laiendussiinid (ISA/EISA või MCA), samuti kohalik ISA-laadne X-BUS siin ja LPC liides, millega on ühendatud emaplaadi kiibid (ROM BIOS, katkestuskontrollerid, klaviatuurid, DMA , COM- ja LPT-pordid, HDD ja muud pisiasjad), mis on ühendatud PCI siiniga "lõunasilla" kaudu. Kaasaegsetes “jaoturi” arhitektuuriga emaplaatides on PCI siini perifeeriasse viidud, ilma et see kahjustaks selle sidekanali mahtu protsessori ja mäluga, aga ka laadimata seadmeid teistele transiitliiklusega siinidele.

PCI-siin on sünkroonne – kõik signaalid püütakse kinni CLK signaali positiivse servaga (servaga). Nominaalseks sünkroniseerimissageduseks loetakse 33,3 MHz, vajadusel saab seda alandada. Alates versioonist PCI 2.1 on võimalik sagedust tõsta 66,6 MHz-ni, kui kõik siinis olevad seadmed “nõustuvad”. PCI-X-is võib sagedus ulatuda 133 MHz-ni.

PCI kasutab paralleelselt multipleksitud aadressi/andmeside (AD) siini, mille tüüpiline laius on 32 bitti. Spetsifikatsioon määratleb võimaluse laiendada bitisügavust 64 bitini; PCI-X versioon 2.0 määratleb ka 16-bitise siini valiku. Siini sagedusel 33 MHz ulatub teoreetiline läbilaskevõime 32-bitise siini puhul 132 MB/s ja 64-bitise siini puhul 264 MB/s; sünkroniseerimissagedusel 66 MHz - vastavalt 264 MB/s ja 528 MB/s. Kuid need tippväärtused saavutatakse ainult pakettülekande ajal: protokolli ülekoormuse tõttu on siini tegelik keskmine läbilaskevõime madalam.

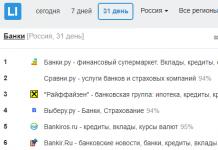

PCI ja PCI-X siinide ning arvutiga ühilduvate arvutite teiste laiendussiinide võrdlusomadused on toodud tabelis. 1.1. ISA-siin lahkub lauaarvutitest, kuid säilitab oma positsiooni tööstuslikes ja sisseehitatud arvutites, nii traditsioonilises pesaversioonis kui ka "sandwich" PC/104 versioonis. Sülearvutites kasutatakse laialdaselt PCMCIA pesasid koos PC-kaardi ja kaardibussi siinidega. LPC siin on kaasaegne ja odav vahend mitteressursimahukate seadmete ühendamiseks emaplaadiga.

| Rehv | Tippvõimsus MB/s | DMA kanalid | Bussimeister | ACFG | Andmete laius | Aadressi suurus | Sagedus MHz |

| ISA-8 | 4 | 3 | - | - | 8 | 20 | 8 |

| ISA-16 | 8 |

7 |

+ |

- |

16 |

24 |

8 |

| LPC | 6,7 |

7 |

+ |

- |

8/16/32 |

32 |

33 |

| EISA |

33,3 | 7 | + |

+ |

32 |

32 |

8,33 |

| MCA-16 |

16 |

- |

+ |

+ |

16 |

24 |

10 |

| MCA-32 |

20 |

- |

+ |

+ |

32 |

32 |

10 |

| VLB |

132 |

- |

(+) |

- |

32/64 |

32 |

33-50(66) |

| PCI |

133-533 |

- |

+ |

+ |

32/64 |

32/64 |

33/66 |

| PCI-X |

533-4256 |

- |

+ |

+ |

16/32/64 |

32/64 |

66-133 |

| PCI Express |

496-15872 |

- |

+ |

+ |

1/2/4/8/12/16/32 |

32/64 |

2,5 GHz |

| AGP 1x/2x/4x/8x |

266/533/1066/2132 |

- |

+ |

+ |

32 |

32/64 |

66 |

| PCMCIA |

10/22 |

+ |

- |

+ |

8/16 |

26 |

10 |

| Kaardibuss | 132 | - | + | + | 32 | 32 | 33 |

ACFG1- Toetab automaatset konfigureerimist. ISA jaoks on PnP hiline lisand, mida rakendavad adapterid ja tarkvara.

PCI ja PCI-X siini signaalimisprotokoll

Infovahetus PCI ja PCI-X siinil on korraldatud tehingutena – loogiliselt sooritatud vahetusoperatsioonidena. Tüüpiline tehing hõlmab kahte seadet: vahetusinitsiaatorit, mida tuntakse ka ülemseadmena, ja sihtseadet, mida nimetatakse ka alamseadmeks. Nende seadmete vahelise suhtluse reeglid määrab PCI siini protokoll. Seade suudab jälgida siinis toimuvaid tehinguid ilma osalejaks olemata (signaale sisestamata); Termin Snooping vastab jälgimisrežiimile. On olemas spetsiaalne tehingutüüp (Special Cycle) - leviedastus, mille käigus algataja ei suhtle protokolli järgi ühegi seadmega. Iga tehing täidab ühe käsu, mis tavaliselt loeb või kirjutab andmeid määratud aadressile. Tehing algab aadressifaasiga, milles algataja määrab käsu ja sihtaadressi. Järgneda võivad andmefaasid, kus üks seade (andmeallikas) paneb andmed siinile ja teine (valamu) loeb neid. Tehinguid, millel on mitu andmefaasi, nimetatakse paketttehinguteks. On ka üksikuid tehinguid (ühe andmefaasiga). Tehingu saab lõpule viia ilma andmefaasideta, kui sihtseade (või algataja) ei ole vahetuseks valmis. PCI-X siinile on lisatud atribuudi faas, mille käigus edastatakse tehingu kohta lisateavet.

PCI ja PCI-X siini signaalimisprotokoll

Siiniliidese signaalide koostis ja eesmärk on toodud allolevas tabelis. Kõikide signaaliliinide olekuid tajub positiivne serv CLK ja neid momente on edasises kirjelduses mõeldud siinitsüklitena (joonistel tähistatud vertikaalsete punktiirjoontega). Erinevatel aegadel juhivad samu signaaliliine erinevad siiniseadmed ning korrektseks (konfliktivabaks) “volituste üleandmiseks” on vajalik ajavahemik, mille jooksul ükski seade liini ei juhi. Ajadiagrammidel tähistab seda sündmust - niinimetatud "piruetti" (pööret) - paar poolringikujulist noolt.

Tabel. PCI siini signaalid

| Signaal |

Eesmärk |

| AD | Aadress/andmed – multipleksitud aadress/andmesiin. Tehingu alguses edastatakse aadress, järgnevates tsüklites - andmed |

| C/B# | Command/Byte Enable – käsk/luba baitidele juurde pääseda. Järgmise siinitsükli tüübi määrav käsk määratakse aadressifaasis neljabitise koodiga |

| RAAM # |

Raam. Signaali sissetoomine tähistab tehingu algust (aadressifaasi), signaali eemaldamine näitab, et järgnev andmeedastuse tsükkel on tehingus viimane |

| DEVSEL# |

Seadme valimine - seade on valitud (juhtimiskeskuse vastus sellele adresseeritud tehingule) |

| IRDY# |

Initiator Ready – põhiseadme valmisolek andmevahetuseks |

| TRDY# |

Target Ready – juhtimiskeskuse valmisolek andmevahetuseks |

| STOP# |

CPU-lt taotlus ülemseadmele praeguse tehingu peatamiseks |

| LUKKU# |

Siini lukustussignaal katkematu töö tagamiseks. Kasutatakse silla poolt, mis nõuab ühe toimingu sooritamiseks mitut PCI tehingut |

| REQ# |

Taotlus – peaseadme taotlus siini arestimiseks |

| GNT# |

Grant - siini juhtimise andmine kaptenile |

| PAR |

Paarsus – ühine paarsusbitt AD ja C/BE# ridade jaoks |

| PERR# |

Parity Error — paarsusvea signaal (kõikide tsüklite jaoks, välja arvatud eritsüklid). Loob mis tahes seade, mis tuvastab vea |

| PME# |

Toitehalduse sündmus - signaal sündmuste kohta, mis põhjustavad muutusi tarbimisrežiimis (PCI 2.2-s kasutusele võetud lisasignaal) |

| CLKRUN# |

Kell töötab – siin töötab nominaalsel taktsagedusel. Signaali eemaldamine tähendab tarbimise vähendamiseks sünkroonimise aeglustumist või peatamist (mobiilirakenduste puhul) |

| PRSN# |

Olevik – plaadi kohaloleku indikaatorid, mis kodeerivad energiatarbimise päringu. Laienduskaardil on GND siiniga ühendatud üks või kaks LED-liini, mida tajub emaplaat |

| RST# |

Lähtesta - lähtestage kõik registrid nende algolekusse (klõpsake nuppu "Lähtesta". ja taaskäivitamisel) |

| IDSEL |

Initialization Device Select – seadme valik konfiguratsiooni lugemis- ja kirjutamistsüklites; Nendele tsüklitele reageerib seade, mis tuvastab sellel liinil kõrge signaalitaseme |

| SERR# |

Süsteemi viga – süsteemiviga. Aadressi või andmepaarsuse viga spetsiaalses kaadris või muu seadme tuvastatud katastroofiline viga. Aktiveerib mis tahes PCI-seade ja kutsub NMI-d |

| REQ64# |

64-bitise taotlus – 64-bitise vahetuse taotlus. Signaali sisestab 64-bitine initsiaator; see langeb ajaliselt kokku FRAME# signaaliga. Lähtestamise lõpetamise ajal (RST# signaal) annab 64-bitisele seadmele signaali, et see on ühendatud 64-bitise siiniga. Kui 64-bitine seade seda signaali ei tuvasta, peab see konfigureerima end ümber 32-bitisele režiimile, keelates suurebaidilised puhverahelad |

| ACK64# |

64-bitise vahetuse kinnitus. Signaali sisestab 64-bitine protsessor, mis on oma aadressi ära tundnud, samaaegselt koodiga DEVSEL#. Kui seda kinnitust ei esitata, sunnib algataja vahetust teostama 32-bitisel tasemel |

| INTA#, INTB#, INTC#, INTD# |

Katkestus A, B, C, D - katkestuspäringu read, taseme tundlikkus, aktiivne tase - madal, mis võimaldab ridade eraldamist (jagamist) |

| CLK |

Kell — siini taktsagedus. Peaks jääma vahemikku 20-33 MHz, alates PCI 2.1-st võib see olla kuni 66 MHz, PCI-X-is kuni 100 ja 133 MHz |

| M66EN |

66MHz Luba - taktsageduse eraldusvõime kuni 66 MHz (kaartidel 33 MHz on maandatud, 66 MHz puhul tasuta) |

| PCIXCAP (38B) |

PCI-X võimalused: PCI-plaatidel - maandatud, PCI-X133-l ühendatud maandusega läbi 0,01 µF kondensaatori, PCI-X66 puhul - paralleelse RC-ahelaga 10 kOhm, 0,01 µF. |

| SDONE |

Snoop Done – annab märku, et praeguse tehingu snoop-tsükkel on lõppenud. Madal tase näitab, et mälu ja vahemälu sidususe jälgimise tsükkel on mittetäielik. Valikuline signaal, mida kasutavad ainult vahemäluga siiniseadmed. PCI 2.2 seisuga aegunud |

| SBO# |

Snoop Backoff - praegune juurdepääs siini abonendi mälule jõuab muudetud vahemälu reale. Valikuline signaal, mida kasutavad tagasikirjutusalgoritmi ajal ainult vahemäluga siiniabonendid. PCI 2.2 seisuga aegunud |

| SMBCLK |

SMBus Clock - SMBus siini kellasignaal (I2C liides). Kasutusele võetud alates PCI 2.3 versioonist |

| SMBDAT |

SMBus Data - SMBus siini jadaandmed (I2C liides). Kasutusele võetud alates PCI 2.3 versioonist |

| TCK |

Test Clock – JTAG testliidese sünkroonimine |

| TDI |

Test Data Input – JTAG testliidese sisendandmed |

| TDO |

Test Data Output – JTAG testliidese väljundandmed |

| TMS |

Test Mode Select – valige JTAG testliidese režiim |

| TRST |

Test Logic Reset – lähtestage testloogika |

Igal ajahetkel saab siini juhtida ainult ühe peaseadmega, mis on saanud selleks õiguse vahekohtunikult. Igal ülemseadmel on paar signaali – REQ# siini juhtimise taotlemiseks ja GNT# siini juhtimise lubamise kinnitamiseks. Seade saab tehingut alustada (FRAME# signaali seadistada) ainult siis, kui see võtab vastu aktiivse GNT# signaali ja ootab, kuni siini tegevust ei toimu. Pange tähele, et puhkeaega oodates võib kohtunik "mõtet muuta" ja anda bussi juhtimise teisele kõrgema prioriteediga seadmele. GNT# signaali eemaldamine takistab seadmel järgmise tehingu alustamist ning teatud tingimustel (vt allpool) võib sundida seda käimasolevat tehingut lõpetama. Bussi kasutamise taotluste arbitraaži tegeleb spetsiaalne sõlm - vahekohtunik, mis on osa seda bussi keskusega ühendavast sillast. Prioriteediskeem (fikseeritud, ring-robin, kombineeritud) määratakse vahekohtuniku programmeerimisega.

Aadresside ja andmete jaoks kasutatakse ühiseid multipleksitud AD-liine. Neli multipleksitud C/BE liini tagavad juhiste kodeerimise aadressifaasis ja baitide eraldusvõime andmefaasis. Kirjutamistoimingutes võimaldavad C/BE read kasutada andmebaite samaaegselt nende olemasoluga AD siinil, lugemistehingute puhul viitavad need signaalid järgmise andmefaasi baitidele. Aadressifaasis (transaction start) aktiveerib juht FRAME# signaali, edastab sihtaadressi AD siinil ja edastab C/BE# liinidel informatsiooni tehingu tüübi (käskluse) kohta. Adresseeritud sihtseade vastab DEVSEL# signaaliga. Peaseade näitab oma valmisolekut andmete vahetamiseks IRDY# signaaliga; seda valmisolekut saab seadistada enne DEVSEL# vastuvõtmist. Kui sihtseade on andmete vahetamiseks valmis, seab see signaali TRDY#. Andmeid edastatakse AD siinil ainult siis, kui signaalid IRDY# ja TRDY# on samaaegselt olemas. Neid signaale kasutades koordineerivad juht- ja sihtseadmed oma kiirusi ooteolekute sisseviimisega. Alloleval joonisel on kujutatud vahetuse ajastusskeem, kus nii ülem- kui ka sihtseade sisestavad ootekellasid. Kui mõlemad sisestaksid valmis signaalid aadressifaasi lõpus ja ei eemaldaks neid enne vahetuse lõppu, siis edastataks igas aadressifaasi järgses taktitsüklis 32 bitti andmeid, mis tagaks vahetuse maksimaalse jõudluse. Lugemistehingutes on pärast aadressifaasi vaja pirueti jaoks lisakell, mille jooksul algataja lõpetab AD liini juhtimise; Sihtseade suudab AD siini juhtimise üle võtta alles järgmises taktitsüklis. Kirjutamistehingus pole piruetti vaja, sest algataja edastab andmed.

PCI siinis käsitletakse kõiki tehinguid pakettidena: iga tehing algab aadressifaasiga, millele võib järgneda üks või mitu andmefaasi. Andmefaaside arv paketis ei ole otseselt näidatud, kuid viimase andmefaasi taktitsüklis eemaldab ülemseade IRDY# signaali sisestamisel signaali FRAME#. Üksikute tehingute puhul on FRAME# signaal aktiivne ainult ühe taktitsükli jooksul. Kui seade ei toeta alamrežiimis paketttehingut, peab ta taotlema paketttehingu lõpetamist esimese andmefaasi ajal (kehtides STOP# signaali samaaegselt TRDY#-ga). Vastuseks sellele viib ülem antud tehingu lõpule ja jätkab järgneva tehingu vahetamist järgmise aadressiväärtusega. Pärast viimast andmefaasi eemaldab juhtseade IRDY# signaali ja siin läheb jõudeolekusse (Idle) – mõlemad signaalid: FRAME# ja IRDY# on passiivses olekus.

Algataja saab alustada järgmist tehingut ilma puhkeperioodita, määrates FRAME# samaaegselt IRDY# eemaldamisega. Selliseid kiireid külgnevaid tehinguid (Fast Back-to-Back) saab adresseerida kas ühele või erinevatele sihtseadmetele. Esimest tüüpi kiireid külgnevaid tehinguid toetavad kõik sihtseadmena töötavad PCI-seadmed. Teist tüüpi külgnevate tehingute tugi (selline tugi on valikuline) on tähistatud olekuregistri bitiga 7. Algataja saab (võimaluse korral) kasutada kiireid külgnevaid tehinguid erinevate seadmetega (loa määrab käsuregistri bitt 9) ainult siis, kui kõik siiniagendid lubavad kiireid kõnesid. Andmete vahetamisel PCI-X režiimis ei ole kiired külgnevad tehingud lubatud.

Siiniprotokoll tagab vahetuse töökindluse – ülemseade saab alati infot sihtseadme tehingu töötlemise kohta. Vahetuse töökindluse suurendamise vahendiks on paarsuskontrolli kasutamine: AD ja C/BE# read nii aadressifaasis kui ka andmefaasis on kaitstud paarsusbitiga PAR (nende ridade seatud bittide arv, kaasa arvatud PAR, peab olema paaris). Tegelik PAR-väärtus ilmub siinile ühe taktitsükli viivitusega liinide AD ja C/BE# suhtes. Kui tuvastatakse viga, genereerib seade PERR# signaali (nihutatakse ühe kella võrra pärast kehtiva paarsusbiti ilmumist siinile). Pariteedi arvutamisel andmeedastuse ajal võetakse arvesse kõiki baite, sealhulgas kehtetuid baite (märgitud kõrge C/BEx# signaaliga). Biti olek peab isegi kehtetute andmebaitide korral jääma andmefaasi ajal stabiilseks.

Iga tehing siinis peab olema plaanipäraselt lõpule viidud või katkestatud ning buss peab minema puhkeolekusse (signaalid FRAME# ja IRDY# on passiivsed). Tehingu lõpuleviimise algatab põhiseade või sihtseade.

Kapten saab tehingu lõpule viia ühel järgmistest viisidest:

- lõpetamine – tavaline lõpetamine andmevahetuse lõppedes;

- time-out — lõpetamine ajalõpu järgi. Tekib siis, kui peamise siini juhtseade eemaldatakse tehingu ajal (eemaldades GNT# signaali) ja selle latentsustaimer aegub. See võib juhtuda, kui adresseeritud sihtseade on ootamatult aeglane või tehing on ajastatud liiga pikaks. Lühikesed tehingud (ühe või kahe andmefaasiga), isegi kui GNT# signaal eemaldatakse ja taimer käivitatakse, lõpetatakse normaalselt;

- master-Abort – Tehingu katkestamine, kui juhtseade ei saa sihtseadmelt vastust (signaal DEVSEL#) määratud aja jooksul.

Tehingu saab lõpetada sihtseadme algatusel; Selleks võib see sisestada STOP# signaali. Võimalik on kolme tüüpi tehingu lõpetamine:

- uuesti proovimine - kordamine, STOP# signaali sisseviimine passiivse TRDY# signaaliga enne esimest andmefaasi. See olukord tekib siis, kui sihtseadmel ei ole sisemise hõivatuse tõttu aega esimesi andmeid õigeaegselt toota (16 taktitsüklit). Korduskatse katkestamine on juhis juhtseadmele sama tehingu taaskäivitamiseks;

- disconnect - lahtiühendamine, STOP# signaali sisseviimine esimese andmefaasi ajal või pärast seda. Kui STOP# signaal sisestatakse siis, kui järgmise andmefaasi TRDY# signaal on aktiivne, siis need andmed edastatakse ja tehing lõpetatakse. Kui STOP# signaal on seatud siis, kui signaal TRDY# on passiivne, siis sooritatakse tehing ilma järgmise faasi andmeid edastamata. Ühenduse katkestamine toimub siis, kui sihtseade ei suuda õigeaegselt väljastada ega vastu võtta järgmist pakettandmete osa. Ühenduse katkestamine on juhis ülemale selle tehingu taaskäivitamiseks, kuid muudetud algusaadressiga;

- target-abort - rike, STOP# signaali sisseviimine samaaegselt signaali DEVSEL# eemaldamisega (varasematel juhtudel oli STOP# signaali ilmumisel DEVSEL# signaal aktiivne). Pärast seda andmeid enam ei edastata. Keeldumine toimub siis, kui sihtseade tuvastab saatusliku vea või muud tingimused, mille tõttu ta ei saa enam antud päringut teenindada (sealhulgas toetamata käsk).

Kolme tüüpi tehingute lõpetamise kasutamine ei ole kõigi sihtseadmete jaoks vajalik, kuid iga peaseade peaks olema valmis tehingute lõpetamiseks mis tahes nimetatud põhjustel.

Katse lõpetamise tüüpi kasutatakse hilinenud tehingute korraldamiseks. Edasilükatud tehinguid kasutavad ainult aeglased sihtseadmed ja PCI-sillad tehingute teisele siinile tõlkimisel. Katkestades (algataja jaoks) uuesti proovimise tingimusega tehingu, täidab sihtseade tehingu sisemiselt. Kui algataja kordab seda tehingut (annab andmefaasis sama käsu sama aadressiga ja sama C/BE# signaalide komplektiga), on sihtseadmel (või sillal) tulemus juba valmis (andmete lugemine või kirjutamise edenemine olek), et see naaseb kiiresti algatajale. Antud seadme poolt sooritatud poolelioleva tehingu tulemus peab seade või sild salvestama seni, kuni algataja tulemusi küsib. Ta võib aga tehingut korrata "unustada" (mõnede ebanormaalsete olukordade tõttu). Tulemuste salvestuspuhvri ületäitumise vältimiseks peab seade need tulemused ära viskama. Kukkumist saab teha ilma kõrvalmõjudeta, kui tehing lükati eellaadimist võimaldavasse mällu (atribuudiga prefetchable, vt allpool). Üldjuhul ei saa teist tüüpi tehingutest karistamatult loobuda (võib rikkuda andmete terviklikkust), nende puhul on kasutuselt kõrvaldamine lubatud alles pärast 215 siinitsükli edutut korduse ootamist (kui käivitub kasutuselt kõrvaldamise taimer). Seade saab sellest erandist teatada oma draiverile (või kogu süsteemile).

Tehingu algataja võib taotleda PCI siini eksklusiivset kasutamist vahetusoperatsiooni kestel, mis nõuab mitut siinitehingut. Näiteks kui CPU täidab PCI-seadmele kuuluvas mäluelemendis andmete muutmise käsu, peab ta lugema seadmest andmeid, muutma neid oma ALU-s ja tagastama tulemuse seadmele. Selleks, et teiste algatajate tehingud ei segaks seda toimingut (mis võib põhjustada andmete terviklikkuse rikkumisi), teostab põhisild seda blokeeritud toiminguna – LOCK# siini signaal edastatakse kogu toimingu ajaks. Tavalised PCI-seadmed (mitte sillad) ei kasuta (ega tooda) seda signaali mingil viisil; seda kasutavad vaid sillad vahekohtu kontrollimiseks.

Riistvarakatkestused arvutiga ühilduvates arvutites

PCI-seadmetel on võimalus asünkroonsetest sündmustest katkestuste abil signaali anda. PCI siinil on saadaval nelja tüüpi katkestuste signaalimine:

- traditsiooniline juhtmega signaalimine INTx liinide kaudu;

- energiajuhtimise sündmuste juhtmega signaalimine PME# liini kaudu;

- signaalimine sõnumite abil - MSI;

- andes märku saatuslikust veast liinil SERR#.

See peatükk hõlmab kõiki neid signalisatsioonitüüpe, samuti üldist pilti riistvarakatkestuse toest arvutiga ühilduvates arvutites.

Riistvarakatkestused arvutiga ühilduvates arvutites

Riistvarakatkestused annavad protsessori vastuse sündmustele, mis toimuvad käivitava programmikoodi suhtes asünkroonselt. Tuletame meelde, et riistvaralised katkestused jagunevad maskeeritavateks ja mittemaskeeritavateks. Katkestussignaali korral peatab x86 protsessor jooksva käsuvoo täitmise, salvestades virna oleku (lipud ja tagastusaadress) ning teostab katkestuste käsitlemise protseduuri. Konkreetne töötlemisprotseduur valitakse katkestuste tabelist katkestusvektoriga - selles tabelis oleva elemendi ühebaidise numbriga. Katkestuste vektor tuuakse protsessorisse erineval viisil: mittemaskeeritavate katkestuste puhul on see fikseeritud, maskeeritavate katkestuste puhul teatab spetsiaalne katkestuste kontroller. Lisaks riistvaralistele katkestustele on x86 protsessoritel ka sisemised katkestused – erandid, mis on seotud käskude täitmise erijuhtudega ja tarkvara katkestustega. Erandite puhul määrab vektori eritingimus ise ja Intel jätab esimesed 32 vektorit (0-31 või 00-1Fh) erandite jaoks. Tarkvarakatkestuste puhul sisaldub vektori number käsus endas (tarkvarakatkestused on vaid spetsiifiline viis protseduuride numbri järgi kutsumiseks, kusjuures lipuregister salvestatakse kõigepealt virna). Kõik need katkestused kasutavad sama 256 võimalikust vektorist koosnevat komplekti. Ajalooliselt kattuvad riistvarakatkestuste vektorid, välja arvatud BIOS-i ja DOS-i teenusekõnede jaoks kasutatud tarkvarakatkestuste vektorid ja vektorid. Seega peab mitme vektornumbri puhul katkestustabelis viidatud protseduur sisaldama esmalt programmikoodi, mis määrab, miks see välja kutsuti: erandi, riistvarakatkestuse või mõne süsteemiteenuse kutsumise tõttu. Seega kutsutakse protseduur, mis tegelikult tagab protsessori reageerimise samale asünkroonsele sündmusele, alles pärast katkestuse allika tuvastamiseks tehtud toiminguid. Samuti märgime siinkohal ära, et sama katkestusvektorit saavad kasutada mitmed välisseadmed – see on nn katkestuste jagatud kasutamine, millest on allpool üksikasjalikult juttu.

Katkestusteenuse rutiini kutsumine protsessori reaalsetes ja kaitstud režiimides on oluliselt erinev:

- reaalrežiimis sisaldab katkestustabel 4-baidiseid kaugosutajaid (segment ja nihe) vastavatele protseduuridele, mis kutsutakse välja kaugkõnega (Call Far koos eelsalvestatud lippudega). Tabeli suurus (256 × 4 baiti) ja asukoht (alates aadressist 0) on fikseeritud;

- Kaitstud režiimis (ja konkreetsel juhul V86 režiimis) sisaldab tabel 8-baidiseid katkestuste deskriptoreid, milleks võivad olla katkestusväravad, lõksväravad või ülesannete väravad. Tabeli suurust saab vähendada (maksimaalselt - 256 × 8 baiti), tabeli asukohta saab muuta (määrab protsessori IDT registri sisu). Katkestuse töötleja kood peab olema vähemalt sama privilegeeritud kui katkestatud ülesande kood (vastasel juhul käivitatakse turvaerand). Sel põhjusel peavad katkestuste töötlejad töötama OS-i kerneli tasemel (nullõiguste tasemel). Õiguste taseme muutmine töötleja kutsumisel toob kaasa lisaaega, mis kulub virna uuesti määratlemisele. Katkestused, mis põhjustavad ülesannete vahetamist (Task Gate'i kaudu), kulutavad märkimisväärselt aega konteksti vahetamisele - protsessoriregistrite mahalaadimisele vana ülesande olekusegmenti ja uue ülesande olekusegmendist laadimisele.

Kaitstud režiimiga operatsioonisüsteemide riistvarakatkestuste jaoks kasutatavad vektornumbrid erinevad reaalrežiimi operatsioonisüsteemides kasutatavatest, et need ei oleks vastuolus protsessori erandite jaoks kasutatavate vektoritega.

Protsessor reageerib alati mittemaskeeritavale katkestusele (NMI) (kui eelmise NMI teenindus on lõpetatud); See katkestus vastab fikseeritud vektorile 2. Mittemaskeeritavaid katkestusi kasutatakse personaalarvutites surmavatest riistvaravigadest märku andmiseks. NMI liini signaal tuleb mälu juhtimisahelatelt (paarsus või ECC), ISA siini juhtliinidelt (IOCHK) ja PCI siinilt (SERR#). NMI-signaal blokeeritakse enne protsessorisse sisenemist, määrates pordi 070h biti 7 väärtusele 1, üksikud allikad on lubatud ja identifitseeritud pordi 061h bittide järgi:

- bitt 2 R/W - ERP - luba juhtida RAM-i ja PCI siini SERR# signaali;

- bitt 3 R/W - EIC - ISA siini juhtimise lubamine;

- bitt 6 R - IOCHK - juhtimisviga ISA siinil (IOCHK# signaal);

- bitt 7 R - PCK - RAM-i paarsusviga või SERR# signaal PCI siinil.

Protsessori reaktsiooni maskeeritavatele katkestustele saab edasi lükata, lähtestades selle sisemise IF-lipu (CLI-käsk keelab katkestused, STI-käsk lubab). Maskeeritavaid katkestusi kasutatakse seadmete sündmustest signaalimiseks. Kui toimub sündmus, mis nõuab vastust, genereerib seadme adapter (kontroller) katkestusnõude, mis saadetakse katkestuskontrolleri sisendisse. Katkestuste kontrolleri ülesandeks on tuua katkestusnõue protsessorisse ja edastada vektor, mille järgi tarkvara katkestuste käsitlemise protseduur on valitud.

Seadme katkestamise rutiin peab seadme teenindamiseks tegema toiminguid, sealhulgas lähtestama selle päringu, et see saaks vastata järgmistele sündmustele, ja saatma katkestuskontrollerile lõpetamiskäske. Töötlemisrutiini kutsumisel salvestab protsessor automaatselt kõigi virna lippude väärtused ja lähtestab IF-lipu, mis keelab maskeeritavad katkestused. Sellest protseduurist naastes (kasutades IRET-i käsku) taastab protsessor salvestatud lipud, sealhulgas seatud (enne katkestust) IF-i, mis võimaldab taas katkestusi. Kui katkestuste käitleja töötamise ajal on vaja reageerida teistele katkestustele (kõrgema prioriteediga), siis peab STI käsk käitlejas olemas olema. See kehtib eriti pikkade käitlejate kohta; siin tuleks STI juhis sisestada võimalikult vara, kohe pärast kriitilist (mittekatkestatavat) sektsiooni. Katkestuste kontroller teenindab järgnevaid sama või madalama prioriteediga katkestusi alles pärast EOI (End Of Interrupt) käsu saamist.

IBM PC-ühilduvad arvutid kasutavad kahte peamist tüüpi katkestuskontrollereid:

- PIC (Peripheral Interrupt Controller) on välisseadmete katkestuskontroller, tarkvara, mis ühildub "ajaloolise" 8259A kontrolleriga, mida kasutati esimestes IBM PC mudelites. Alates IBM PC/AT ajast on kasutatud paari kaskaad-PIC-i, mis võimaldab teenindada kuni 15 katkestuspäringu rida;

- APIC (Advanced Peripheral Interrupt Controller) on täiustatud välisseadmete katkestuskontroller, mis on kasutusele võetud mitme protsessori süsteemide toetamiseks arvutites, mis põhinevad 4-5 põlvkonna protsessoritel (486 ja Pentium) ning seda kasutatakse ka tänapäeval hilisemate protsessorimudelite jaoks. Lisaks mitmeprotsessori konfiguratsioonide toetamisele võimaldab kaasaegne APIC suurendada saadaolevate katkestusliinide arvu ja käsitleda sõnumimootori (MSI) kaudu saadetud PCI-seadmete katkestustaotlusi. APIC-kontrolleriga varustatud arvuti peab suutma töötada standardse PIC-paariga ühilduvas režiimis. Selle režiimi aktiveerib riistvara lähtestamine (ja sisselülitamine), mis võimaldab kasutada vanu OS-i ja MS DOS-i rakendusi, mis ei tunne APIC-d ja multitöötlust.

Traditsiooniline skeem katkestustaotluste genereerimiseks paari PIC-i abil on näidatud alloleval joonisel.

Katkestuskontrolleri sisendid võtavad vastu päringuid süsteemiseadmetelt (klaviatuur, süsteemitaimer, CMOS-taimer, kaasprotsessor), emaplaadi välisseadmete kontrolleritelt ja laienduskaartidelt. Traditsiooniliselt on kõik päringuliinid, mida loetletud seadmed ei hõivata, kõigis ISA/EISA siini pesades. Need read on tähistatud IRQx-ga ja neil on ühine eesmärk (vt allolevat tabelit). Mõned neist liinidest on eraldatud PCI siinile. Tabelis on näidatud ka katkestuste prioriteedid – päringud on järjestatud kahanevas järjekorras. Kontrolleri päringuridadele, prioriteetsüsteemile ja mõnele muule parameetrile vastavate vektorite arvud määratakse kontrollerite lähtestamise ajal programmiliselt. Need põhisätted jäävad tarkvara ühilduvuse osas traditsioonilisteks, kuid erinevad reaal- ja kaitstud režiimis OS-ide vahel. Näiteks Windows OS-is on põhi- ja alamkontrollerite baasvektorid vastavalt 50h ja 58h.

| Nimi (number 1) | Vektor 2 | Vektor 3 | Kontroller/mask | Kirjeldus |

| NMI | 02h | |||

| IRQ0 | 08h | 50h |

#1/1h |

Kanali juhtimine, mälupaarsus (XT-s - kaasprotsessor) |

| IRQ1 | 09h | 51h |

#1/2h |

Klaviatuur |

| IRQ2 | 0 Ah | 52h |

#1/4h |

XT - reserv, AT - pole saadaval (IRQ8-IRQ15 kaskaad on ühendatud) |

| IRQ8 | 70h |

58h |

#2/1h |

CMOS RTC – reaalajas kell |

| IRQ9 | 71h |

59h |

#2/2h |

Reserv |

| IRQ10 | 72h |

5 Ah |

#2/4h |

Reserv |

| IRQ11 | 73h |

5 Bh |

#2/8h |

Reserv |

| IRQ12 | 74h |

5Ch |

#2/10h |

PS/2-Mouse (reserv) |

| IRQ13 | 75h |

5Dh |

#2/20h |

Matemaatika kaasprotsessor |

| IRQ14 | 76h |

5 Eh |

#2/40h |

HDC - HDD kontroller |

| IRQ15 | 77h |

5Fh |

#2/80h |

Reserv |

| IRQ3 | 0Bh |

52h |

#1/4h |

COM2, COM4 |

| IRQ4 | 0Ch |

53h |

#1/10h |

COM1, COM3 |

| IRQ5I | 0Dh |

54h |

#1/20h |

XT – HDC, AT – LPT2, heli (reserv) |

| IRQ6 | 0 Eh |

55h |

#1/40h |

FDC - ujuvajami kontroller |

| IRQ7 | 0Fh |

56h |

#1/80h |

LPT1 - printer |

*1 Katkestustaotlusi 0, 1, 8 ja 13 ei väljastata laiendussiinidele.

*2 Reaalprotsessori režiimis töötamisel kuvatakse vektornumbrid.

*3 Windows OS-is töötades kuvatakse vektornumbrid.

Igale seadmele, mis vajab oma töö toetamiseks katkestusi, tuleb määrata oma katkestuse number. Katkestuste numbrite määramine toimub kahelt poolt: esiteks tuleb katkestusi vajav adapter konfigureerida kasutama kindlat siiniliini (kas hüppajate või tarkvara abil). Teiseks tuleb adapterit toetavale tarkvarale teada anda kasutatavast vektorinumbrist. ISA- ja PCI-siinide PnP-süsteem saab osaleda katkestuste määramise protsessis; päringuliinide siinide vahel jagamiseks kasutatakse spetsiaalseid CMOS-i seadistusparameetreid. Kaasaegsetel operatsioonisüsteemidel on võimalus muuta CMOS-i häälestuse kaudu tehtud jaotamise päringute määramist.

Pärast katkestussüsteemi konfigureerimist (katkestuskontrolleri initsialiseerimist, päringuliinide määramist seadmetele ja töötlemisprotseduuride viidate seadistamist) töödeldakse maskeeritavaid riistvarakatkestusi järgmiselt:

- katkestuse sündmuse korral ergastab seade talle määratud katkestusnõude rea;

- kontroller võtab vastu katkestuse allikatest päringu signaale (IRQx signaalid) ja maskeerimata päringu olemasolul saadab x86 protsessorile üldise katkestuse taotluse signaali (INTR signaal);

- päringule vastates (kui IF-lipuga katkestused on lubatud) salvestab protsessor pinusse lipuregistri sisu ja tagastusaadressi, misjärel genereerib INTA (Interrupt Acknowledge) siinitsükli, mis edastatakse katkestuse kontroller;

- INTA signaali vastuvõtmise hetkel salvestab katkestuskontroller oma päringu sisendite oleku - selleks hetkeks võis nende olek muutuda: võivad ilmuda uued päringud või kaduda "kannatamatu" seadme päring. Kontroller analüüsib sissetulevaid päringuid vastavalt programmeeritud prioriteetskeemile ja saadab protsessorile katkestusvektori, mis vastab kõrgeima prioriteediga maskeerimata päringule, mis on kontrolleri sisendis INTA siini käsu andmise ajal. Samal ajal teostab vastutav töötleja ka mõningaid toiminguid vastavalt kehtestatud prioriteedipoliitikale, võttes arvesse, milline vektor saadeti (milline päringutest läks teenusesse);

- Pärast katkestusvektori vastuvõtmist kutsub protsessor oma numbri abil välja vastava katkestuste käsitlemise protseduuri. Kui antud katkestusvektorit ei kasutata mitte ainult riistvaraliste katkestuste, vaid ka erandite ja/või tarkvara katkestuste jaoks, siis peab rutiin esmalt kindlaks määrama, millise neist tüüpidest sündmus on. Selleks saab protseduur ühendust võtta PIC-kontrolleriga (lugeda ISR-registrit) ja analüüsida protsessoriregistrite seisu. Täiendavaid samme kaalutakse juhul, kui tuvastatakse riistvarakatkestus;

- Katkestuse käsitlemise protseduur peab tuvastama katkestuse allika – määrama selle põhjustanud seadme. Kui antud päringunumbrit (ja seega ka vektorit) kasutavad ühiselt mitu seadet, saab katkestuse allika tuvastada ainult järjestikuse juurdepääsu kaudu iga seadme registritele. Sel juhul tuleks arvestada võimalusega saada päringuid mitmelt seadmelt samaaegselt või ühe katkestuse töötlemise ajal;

- protseduur peab teenindama katkestuse allika seadet - tegema "kasulikke" toiminguid, mis on seotud sündmusega, millest seade märku andis. See teenus peaks tagama ka selle seadme katkestuse taotluse signaali eemaldamise. Jagatud katkestuste korral võib allikaid olla mitu ja kõik need vajavad hooldust;

- kui katkestuse töötlemine võtab palju aega, mille jooksul süsteem peab vastama kõrgema prioriteediga päringutele, siis pärast kriitilist osa lisatakse töötlejasse STI käsk, mis määrab protsessoris katkestuse lubamise lipu (IF). . Sellest hetkest alates on võimalikud pesastatud katkestused, mis katkestavad antud töötleja töö mõne teise, kõrgema prioriteediga protseduuriga;

- Katkestuste käsitlemise protseduur peab saatma kontrollerile käskluse katkestamise töötlemise lõpetamiseks EOI (End Of Interrupt), mille abil kontroller võimaldab järgnevalt signaali vastu võtta teenindatavast sisendist ja madalama prioriteediga sisenditest. Seda tuleb teha pärast katkestussignaali eemaldamist hooldatavatelt seadmetelt, vastasel juhul saadab kontroller pärast EOI-d teise päringu. Katkestuste töötleja, mille kohta päring on tulnud alamkontrollerilt, peab saatma EOI nii alam- kui ka ülemkontrollerile. Käsitleja osa, mis algab EOI käsu andmisest kuni lõpetamiseni (IRET käsk), peab olema katkematu ehk see on kriitiline lõik. Kui töötleja lubas pesastatud katkestusi, peab enne EOI käsu andmist olema katkestusi keelav CLI käsk;

- katkestustöötlus lõpetatakse IRET-käsuga, millega protsessor naaseb katkestatud käsuvoo täitmise juurde, olles eelnevalt pinust välja otsinud lippude registri sisu. Sel juhul lubatakse riistvarakatkestused uuesti.

Seda järjestust kirjeldatakse seoses tavalise katkestuskontrolleriga (PIC), APIC-ga süsteemid muudavad katkestuste vektori kontrollerilt protsessorisse edastamise viisi ja MSI katkestused muudavad signaali edastamise viisi seadmest APIC-kontrollerisse. . Neid nüansse kirjeldatakse järgmistes osades.

Üldine informatsioon

PCI sillad (PCI Bridge) on spetsiaalne riistvara PCI (ja PCI-X) siinide omavaheliseks ja teiste siinidega ühendamiseks. Host Bridge'i kasutatakse PCI ühendamiseks arvuti keskosaga (süsteemimälu ja protsessor). Peasilla "auväärne kohustus" on genereerida kõnesid keskprotsessori kontrolli all olevasse konfiguratsiooniruumi, mis võimaldab hostil (keskprotsessoril) konfigureerida kogu PCI siini alamsüsteemi. Süsteemil võib olla ka mitu põhisilda, mis võimaldab pakkuda kõrgjõudlusega sidet keskusega suuremale hulgale seadmetele (seadmete arv ühel siinil on piiratud). Neist bussidest üks on tinglikult määratud põhibussiks (buss 0).

Täiendavate PCI siinide ühendamiseks kasutatakse PCI peer sildu (PeertoPeer Bridge). Need sillad lisavad alati täiendavat andmeedastust, nii et seadme ja jaoturi vahelise side tõhus jõudlus väheneb iga takistava sillaga.

PCMCIA, CardBus, MCA, ISA/EISA, X-Bus ja LPC siinide ühendamiseks kasutatakse spetsiaalseid sildu, mis sisalduvad emaplaadi kiibikomplektides või on eraldi PCI seadmed (kiibid). Need sillad teisendavad ühendatud siinide liideseid, sünkroonivad ja puhverdavad andmevahetust.

Iga sild on programmeeritav – talle on antud aadressivahemikud mälus ja seadmetele eraldatud sisend/väljundruumid selle siinidel. Kui praeguse tehingu CPU aadress silla ühel siinil (küljel) viitab vastaspoole siinile, tõlgib sild tehingu vastavale siinile ja tagab siini protokolli läbirääkimise. Seega teostab PCI-sildade kogum päringute marsruutimist mööda seotud siine. Kui süsteemil on mitu peasilda, siis ei pruugi erinevate siinide peal olevate seadmete vaheline ots-ots-marsruutimine olla võimalik: põhisillad võivad olla omavahel ühendatud ainult mälukontrolleri magistraalteede kaudu. Igat tüüpi PCI-tehingute tõlkimise toetamine peamiste sildade kaudu osutub sel juhul liiga keeruliseks ja seetõttu pole PCI spetsifikatsioonis seda rangelt nõutud. Seega pääsevad süsteemimälu juurde kõik aktiivsed seadmed kõikidel PCI siinidel, kuid peer-to-peer side võimalus võib sõltuda sellest, kas need seadmed kuuluvad ühte või teise PCI siini.

PCI-sildade kasutamine pakub selliseid võimalusi nagu:

- võimaliku ühendatud seadmete arvu suurendamine, siini elektriliste spetsifikatsioonide piirangute ületamine;

- PCI seadmete jaotus segmentideks - PCI siinid - erinevate omadustega bitisügavus (32/64 bitti), taktsagedus (33/66/100/133 MHz), protokoll (PCI, PC-X Mode 1, PCI-X Mode 2, PCI Express). Igal siinil on kõik abonendid võrdsed nõrgima osalejaga; seadmete õige paigutus siinidel võimaldab maksimaalse efektiivsusega kasutada seadmete ja emaplaadi võimalusi;

- segmentide organiseerimine seadmete "kuum" ühendamise/lahtiühendamisega;

- erinevatel bussidel asuvatelt algatajatelt tehingute samaaegse paralleelse täitmise korraldamine.

Iga PCI sild ühendab ainult kahte siini: esmase siini, mis asub hierarhia tipule lähemal, sekundaarse siiniga; Sillaliideseid, mille kaudu see on nende siinidega ühendatud, nimetatakse vastavalt primaarseks ja sekundaarseks. Lubatud on ainult puhtalt puutaoline konfiguratsioon, see tähendab, et kaks siini on omavahel ühendatud ainult ühe sillaga ja sildade “aasusid” pole. Antud silla sekundaarse liidesega teiste sildade kaudu ühendatud siine nimetatakse allutatud siinideks. PCI-sillad moodustavad PCI-siinide hierarhia, mille ülaosas on põhisillaga ühendatud põhisiin, nummerdatud null. Kui peasildasid on mitu, siis nende bussidest (mis on võrdsed) on peamine see, millel on nullnumber.

Sild peab täitma mitmeid kohustuslikke funktsioone:

- teenindada selle sekundaarse liidesega ühendatud siini:

- teostab arbitraaži - REQx# päringu signaalide vastuvõtmine siiniülematelt ja neile õiguse andmine siini juhtimiseks GNTx# signaalidega

- parkige siin - saatke mõnele seadmele GNTx# signaal, kui siini juhtimine pole ühegi masteri poolt nõutav;

- genereerida 0-tüüpi konfiguratsioonitsükleid üksikute IDSEL-signaalide moodustamisega adresseeritavale PCI-seadmele;

- "tõmba" juhtsignaalid kõrgele tasemele;

- määrata ühendatud seadmete võimalused ja valida neid rahuldav siini töörežiim (sagedus, bitisügavus, protokoll);

- genereerida riistvara lähtestamine (RST#), lähtestades esmasest liidesest ja käsuga, teatades valitud režiimist spetsiaalse häirega.

- pidama silla vastaskülgedel asuvate ressursside kaarte;

- reageerima sihtseadme varjus tehingutele, mille juht on algatanud ühes liideses ja adresseeritud teises liideses asuvale ressursile; edastada need tehingud teisele liidesele, mis toimib peaseadmena, ja edastada nende tulemused tõelisele algatajale.

Neid funktsioone täitvaid sildu nimetatakse läbipaistvateks sildadeks; Selliste sildade taga asuvate seadmetega töötamiseks pole vaja täiendavaid silladraivereid. Just neid sildu on kirjeldatud PCI Bridge 1.1 spetsifikatsioonis ja neile kui PCI-seadmetele on eriklass (06). Sel juhul eeldatakse ressursi adresseerimismudelit (mälu ja I/O): igal seadmel on antud süsteemis (arvutis) kordumatud (teistega mitte ristuvad) aadressid.

Samuti on olemas läbipaistmatud sillad (mittepaistev sild), mis võimaldavad korraldada eraldi segmente oma kohalike aadressiruumidega. Läbipaistmatu sild teostab aadressi translatsiooni (teisendamise) tehingute jaoks, mille algataja ja sihtseade asuvad silla vastaskülgedel. Kõik vastaspoole ressursid (aadressivahemikud) ei pruugi olla sellise silla kaudu kättesaadavad. Läbipaistmatuid sildu kasutatakse näiteks siis, kui arvutil on “intelligentne sisend/väljund” (I20) alamsüsteem, millel on oma I/O protsessor ja kohalik aadressiruum.

Üldine informatsioon

PCI siinil on algselt võimalus süsteemiressursse automaatselt konfigureerida (mälu- ja I/O-ruumid ning katkestusnõude read). Seadme automaatset seadistamist (aadresside ja katkestuste valik) toetavad BIOS ja OS-i tööriistad; see on keskendunud PnP-tehnoloogiale. PCI-standard määrab iga funktsiooni jaoks konfiguratsiooniruumi kuni 256 registrist (8-bitist), mis ei ole määratud ei mälu- ega sisend-väljundruumile. Nendele pääseb juurde spetsiaalsete siinikäskude abil Configuration Read ja Configuration Write, mis on loodud ühe allpool kirjeldatud riist- ja tarkvaramehhanismi abil. Selles ruumis on alad, mis on vajalikud kõigi ja konkreetsete seadmete jaoks. Antud seadmel ei pruugi olla registreid kõigil aadressidel, kuid see peab toetama neile suunatud toimingute tavapärast lõpetamist. Sel juhul peaks olematute registrite lugemine tagastama nullid ja kirjutamine peaks toimuma tühikäigu toiminguna.

Funktsiooni konfiguratsiooniruum algab standardse päisega, mis sisaldab tootja, seadme ja selle klassi identifikaatoreid ning vajalike ja hõivatud süsteemiressursside kirjeldust. Päise struktuur on standardiseeritud tavaseadmetele (tüüp 0), PCI-PCI sildadele (tüüp 1), PCI-CardBus sildadele (tüüp 2). Päise tüüp määrab hästi tuntud registrite asukoha ja nende bittide eesmärgi. Päise järel võivad olla seadmepõhised registrid. Seadmete standardiseeritud võimaluste (võimekuse) jaoks (näiteks energiahaldus) on konfiguratsiooniruumis teadaoleva otstarbega registrite plokid. Need plokid on organiseeritud ahelateks, esimesele sellisele plokile viidatakse standardpäises (CAP_PTR); ploki esimeses registris on link järgmisele plokile (või 0, kui see plokk on viimane). Seega saab konfiguratsioonitarkvara ketti skaneerides loendi kõigist saadaolevatest seadme omadustest ja nende asukohtadest funktsioonide konfiguratsiooniruumis. PCI 2.3 määratleb järgmised CAP_ID-d, millest mõnda me vaatame:

- 01 - energiamajandus;

- 02 - AGP port;

- 03 - VPD (Vital Product Data), andmed, mis annavad põhjaliku kirjelduse seadmete riistvara (võimalik, et ka tarkvara) omadustest;

- 04 — pesade ja šassii nummerdamine;

- 05 - MSI katkestab;

- 06 - Hot Swap, kuum ühendus kompaktse PCI jaoks;

- 07 - PCI-X protokolli laiendused;

- 08 - reserveeritud AMD jaoks;

- 09 - tootja äranägemisel (Vendor Specific);

- 0Ah — silumisport (Debug Port);

- 0Bh - PCI Hot Plug, "hot plug" standardvarustus.

PCI-X režiimi 2 seadmete jaoks on konfiguratsiooniruum laiendatud 4096 baidini; laiendatud ruumis võivad olla laiendatud kinnisvarakirjeldused.

Pärast kõva lähtestamist (või sisselülitamist) ei reageeri PCI-seadmed mälu- ja sisend-/väljundruumi juurdepääsudele ning on saadaval ainult konfiguratsiooni lugemiseks ja kirjutamiseks. Nendes toimingutes valitakse seadmed individuaalsete IDSEL-signaalide abil ning registreid lugedes õpib konfiguratsioonitarkvara tundma ressursinõudeid ja seadme võimalikke konfiguratsioonivõimalusi. Pärast seda, kui konfiguratsiooniprogramm on ressursside eraldanud (POST-i või OS-i alglaadimise ajal), kirjutatakse konfiguratsiooniparameetrid (baasaadressid) seadme konfiguratsiooniregistritesse. Alles pärast seda seatakse seadmed (täpsemalt funktsioonid) bittideks, mis võimaldavad neil vastata käskudele juurdepääsuks mälule ja I/O portidele ning juhtida siini ise. Selleks, et alati oleks võimalik leida toimiv konfiguratsioon, peavad kõik kaartide hõivatud ressursid olema oma ruumis teisaldatavad. Multifunktsionaalsete seadmete puhul peab igal funktsioonil olema oma konfiguratsiooniruum. Seade suudab samad registrid kaardistada nii mälu kui ka I/O ruumiga. Sel juhul peavad mõlemad deskriptorid olema nende konfiguratsiooniregistrites, kuid draiver peab kasutama ainult ühte juurdepääsumeetodit (eelistatavalt mälu kaudu).

Konfiguratsiooniruumi päis kirjeldab kolme tüüpi aadresside vajadusi.

- registreerib I/O ruumis);

- I/O registrid on mällu vastendatud (Memory Mapped I/O). See on mäluala, millele tuleb juurde pääseda rangelt vastavalt sellele, mida vahetuse algataja nõuab. Juurdepääs nendele registritele võib muuta välisseadmete sisemist olekut;

- mälu, mis võimaldab eellaaditavat mälu. See on mäluala, kus "lisa" lugemine (kasutamata tulemustega) ei too kaasa kõrvalmõjusid, kõiki baite loetakse sõltumatult BE# signaalidest ja üksikute baitide kirjutamist saab sildada (st see on mälu kõige puhtamal kujul).

Aadressinõuded on näidatud baasaadressiregistrites - BAR (Base Address Register). Konfiguratsiooniprogramm suudab määrata ka vajalike alade suuruse. Selleks peab see pärast riistvara lähtestamist lugema ja salvestama baasaadresside väärtused (need on vaikeaadressid), kirjutama igasse registrisse FFFFFFFFh ja lugema nende väärtuse uuesti. Vastuvõetud sõnades peate lähtestama tüübi dekodeerimisbitid (bitid mälu jaoks ja bitid I/O jaoks), inverteerima ja suurendama saadud 32-bitist sõna - tulemuseks on ala pikkus (ignoreeri portide bitte ). Meetod eeldab, et piirkonna pikkus on väljendatud kui 2n ja piirkond on loomulikult joondatud. Standardpäis mahutab kuni 6 baasaadressiregistrit, kuid 64-bitise adresseerimise kasutamisel väheneb kirjeldatud plokkide arv. Kasutamata BAR-registrid peaksid lugemisel alati nullid tagastama.

PCI toetab pärandseadmeid (VGA, IDE), mis deklareerivad end sellistena päises oleva klassikoodi järgi. Nende traditsioonilisi (fikseeritud) pordiaadresse ei deklareerita konfiguratsiooniruumis, kuid kui pordi juurdepääsu lubamise bitt on määratud, lubatakse seadmetel vastata ka neile aadressidele.

Inteli ja tema partnerite välja töötatud PCI Expressi jadasiin on mõeldud paralleelse PCI siini ja selle laiendatud ja spetsialiseeritud variandi AGP asendamiseks. Vaatamata sarnastele nimedele on PCI ja PCI Express siinidel vähe ühist. PCI-s kasutatav paralleelne andmeedastusprotokoll seab piirangud siini ribalaiusele ja sagedusele; PCI Expressis kasutatav jadaandmeedastus tagab skaleeritavuse (spetsifikatsioonid kirjeldavad PCI Expressi 1x, 2x, 4x, 8x, 16x ja 32x rakendusi). Hetkel on siini praegune versioon indeksiga 3.0

Inteli ja tema partnerite välja töötatud PCI Expressi jadasiin on mõeldud paralleelse PCI siini ja selle laiendatud ja spetsialiseeritud variandi AGP asendamiseks. Vaatamata sarnastele nimedele on PCI ja PCI Express siinidel vähe ühist. PCI-s kasutatav paralleelne andmeedastusprotokoll seab piirangud siini ribalaiusele ja sagedusele; PCI Expressis kasutatav jadaandmeedastus tagab skaleeritavuse (spetsifikatsioonid kirjeldavad PCI Expressi 1x, 2x, 4x, 8x, 16x ja 32x rakendusi). Hetkel on siini praegune versioon indeksiga 3.0

PCI-E 3.0

2010. aasta novembris teatas PCI Expressi tehnoloogiat standardiv PCI-SIG organisatsioon PCIe Base 3.0 spetsifikatsiooni kasutuselevõtust.

Peamiseks erinevuseks kahest eelmisest PCIe versioonist võib pidada modifitseeritud kodeerimisskeemi – nüüd saab edastatud 10 bitist (8b/10b) kasuliku teabe 8 biti asemel edastada 128 bitti kasulikku teavet saadetud 130 bitist. bussi kaudu, st. Kasuliku koormuse koefitsient on peaaegu 100% lähedal. Lisaks on andmeedastuskiirus kasvanud 8 GT/s-ni. Meenutagem, et PCIe 1.x puhul oli see väärtus 2,5 GT/s ja PCIe 2.x puhul 5 GT/s.

Kõik ülaltoodud muudatused viisid siini ribalaiuse kahekordistumiseni võrreldes PCI-E 2.x siiniga. See tähendab, et kogu PCIe 3.0 siini ribalaius 16x konfiguratsioonis jõuab 32 Gb/s. Esimesed protsessorid, mis varustati PCIe 3.0 kontrolleriga, olid Ivy Bridge'i mikroarhitektuuril põhinevad Inteli protsessorid.

Vaatamata PCI-E 3.0 enam kui kolmekordsele läbilaskevõimele võrreldes PCI-E 1.1-ga, ei erine samade videokaartide jõudlus erinevate liideste kasutamisel palju. Allolev tabel näitab GeForce GTX 980 testitulemusi erinevates testides. Mõõtmised viidi läbi samade graafikaseadetega, samas konfiguratsioonis.PCI-E siini versiooni muudeti BIOS-i seadistustes.

PCI Express 3.0 on jätkuvalt tagasiühilduv PCIe eelmiste versioonidega.

PCI-E 2.0

2007. aastal võeti kasutusele uus PCI Expressi siini spetsifikatsioon 2.0, mille peamine erinevus on iga ülekandeliini kahekordne ribalaius igas suunas, s.o. videokaartides kasutatava PCI-E 16x populaarseima versiooni puhul on läbilaskevõime kummaski suunas 8 Gb/sek. Esimene PCI-E 2.0 toetav kiibistik oli Intel X38.

PCI-E 2.0 on täielikult tagasiühilduv PCI-E 1.0-ga, st. Kõik olemasolevad PCI-E 1.0 seadmed võivad töötada PCI-E 2.0 pesades ja vastupidi.

PCI-E 1.1

PCI Expressi liidese esimene versioon, mis ilmus 2002. aastal. Tagas läbilaskevõime 500 MB/s liini kohta.

Erinevate PCI-E põlvkondade töökiiruste võrdlus

PCI-siin töötab sagedusel 33 või 66 MHz ja annab 133 või 266 MB/sek ribalaiust, kuid see ribalaius jagatakse kõigi PCI-seadmete vahel. PCI Expressi siini töösagedus on 1,1–2,5 GHz, mis annab läbilaskevõimeks 2500 MHz / 10 * 8 = 250 * 8 Mbps = 250 Mbps (8-bitise andmeedastuse üleliigse kodeerimise tõttu on tegelikult 10 bitti edastatud teave) iga PCI Express 1.1 x1 seadme jaoks ühes suunas. Kui rida on mitu, tuleb läbilaskevõime arvutamiseks väärtus 250 Mb/s korrutada ridade arvuga ja 2-ga, sest PCI Express on kahesuunaline siin.

| PCI Express 1.1 radade arv | Ühesuunaline läbilaskevõime | Kogu läbilaskevõime |

| 1 | 250 MB/sek | 500 MB/sek |

| 2 | 500 Mb/sek | 1 GB/s |

| 4 | 1 GB/s | 2 GB/s |

| 8 | 2 GB/s | 4 GB/s |

| 16 | 4 GB/s | 8 GB/sek |

| 32 | 8 GB/sek | 16 GB/sek |

Märge! Ärge proovige installida PCI Expressi kaarti PCI pesasse ja vastupidi, PCI-kaarte ei installita PCI Expressi pesadesse. Siiski saab paigaldada näiteks PCI Express 1x kaardi ja suure tõenäosusega töötab see normaalselt PCI Express 8x või 16x pesas, aga mitte vastupidi: PCI Express 16x kaart ei mahu PCI Express 1x pesasse. .

PCI siini

32-bitine PCI-pistik emaplaadil

64-bitine PCI pesa Power Macintosh G4-s

PCI siini standard määratleb:

- füüsilised parameetrid (näiteks pistikud ja signaalijuhtmestik);

- elektrilised parameetrid (näiteks pinge);

- loogiline mudel (nt siinitsükli tüübid, siini adresseerimine).

PCI standardi on välja töötanud PCI Special Interest Group.

Loomise ajalugu

Vaadake, mis on "PCI buss" teistes sõnaraamatutes:

PCI-X siini- 64-bitine siin, PCI siiniga tagasiühilduv. Infotehnoloogia teemad üldiselt ET PCI X ... Tehniline tõlkija juhend

Fotol on 4 PCI Expressi pesa: x4, x16, x1, jälle x16, allpool on standardne 32-bitine PCI pesa, DFI LanParty nForce4 SLI DR PCI Express või PCIe või PCI E emaplaadil, (tuntud ka kui 3GIO 3. põlvkonna I/O jaoks, mitte segi ajada PCI-ga... Wikipedia

PCI E PCI Express PCI Expressi logo Avastamise aasta: 2002 (1.0) 15. jaanuar 2007 (2.0) november 2010 (Spetsifikatsiooni versioon 3.0) Arendaja: Intel, PCI Special Interest Group Mida see siin asendas: AGP, PCI X, PCI .. Vikipeedia

PCI (Peripheral Component Interconnect) arvutisiin. PCI DSS standard kaardimaksesüsteemide andmeturbe jaoks (Payment Card Industry Data Security Standard), mida kasutatakse sageli lühendina PCI. PCI... ... Vikipeedia

Sellel terminil on ka teisi tähendusi, vt PCI (tähendused) ... Wikipedia

See artikkel tuleb täielikult ümber kirjutada. Jutulehel võib olla selgitusi... Vikipeedia

PCI Express (väliskomponentide ühendamise ekspress)- 3. põlvkonna süsteemisisend/väljundsiin, varem kandis nime 3GIO (3rd Generation I/O), mis asendas standardse PCI siini ja sai peamiseks liideseks arvutisiseste komponentide ühendamiseks. PCI Express siin toetab ühilduvust... Samsungi kodu- ja arvutiseadmete terminite sõnastik

PCI - Ekspress (PCIePCI -E)– esmakordselt avalikustati seeria-, universaalbuss 22. juuli 2002 aasta.

On üldine, ühendav siini kõigi emaplaadi sõlmede jaoks, milles eksisteerivad koos kõik sellega ühendatud seadmed. Tuli vananenud rehvi vahetama PCI ja selle variatsioonid AGP, mis on tingitud suurenenud nõuetest siini läbilaskevõimele ja suutmatusest parandada viimase kiirust mõistlike kuludega.

Rehv toimib nagu lüliti, saates lihtsalt signaali ühest punktist teise ilma seda muutmata. See võimaldab ilma ilmse kiiruse kaotamiseta minimaalsete muudatuste ja vigadega signaali edastada ja vastu võtta.

Andmed bussi kohta lähevad simpleks(täisdupleks), see tähendab samaaegselt mõlemas suunas sama kiirusega ja signaal mööda jooni voolab pidevalt, isegi kui seade on välja lülitatud (alalisvooluna või nullide bitisignaalina).

Sünkroonimine ehitatud üleliigsel meetodil. See tähendab, et selle asemel 8 bitine teave edastatakse 10 bitti, millest kaks on ametnik (20% ) ja serveeri kindlas järjestuses majakad Sest sünkroonimine kella generaatorid või vigade tuvastamine. Seetõttu on deklareeritud kiirus ühe rea kohta 2,5 Gbps, on tegelikult võrdne ligikaudu 2,0 Gbps päris.

Toitumine iga seade siinis, valitud eraldi ja reguleeritud tehnoloogia abil ASPM (Aktiivne oleku toitehaldus). See võimaldab, kui seade on jõude (ilma signaali saatmata) alandage oma kella generaatorit ja pange buss režiimi vähenenud energiatarbimine. Kui mõne mikrosekundi jooksul signaali vastu ei võeta, siis seade peetakse passiivseks ja lülitub režiimi ootustele(aeg sõltub seadme tüübist).

Kiirusomadused kahes suunas PCI - Express 1.0 :*

1 x PCI-E~ 500 Mbps

4x PCI-E~ 2 Gbps

8 x PCI-E~ 4 Gbps

16x PCI-E~ 8 Gbps

32x PCI-E~ 16 Gbps

*Andmeedastuskiirus ühes suunas on nendest näitajatest 2 korda väiksem

15. jaanuar 2007 PCI-SIG andis välja uuendatud spetsifikatsiooni nimega PCI-Express 2.0

Peamine paranemine toimus 2 korda suurenenud kiirus andmeedastus ( 5,0 GHz, vastu 2,5 GHz vanas versioonis). Samuti paranenud punkt-punkti sideprotokoll(punktist punktini), muudetud tarkvara komponent ja lisatud süsteem tarkvara jälgimine vastavalt rehvi kiirusele. Samal ajal see säilis ühilduvus protokolli versioonidega PCI-E 1.x

Standardi uues versioonis ( PCI -Express 3.0 ), on peamine uuendus muudetud kodeerimissüsteem Ja sünkroonimine. Selle asemel 10 bitti süsteemid ( 8 bitine teave, 2 bitti ametnik), kohaldatakse 130 bitti (128 bitti teave, 2 bitti ametnik). See vähendab kaotused kiiruses 20% kuni ~1,5%. Samuti kujundatakse ümber sünkroniseerimisalgoritm saatja ja vastuvõtja, täiustatud PLL(faasilukuga silmus).Edastamise kiirus eeldatavasti suureneb 2 korda(võrreldes PCI-E 2.0), kus ühilduvus jääb alles eelmiste versioonidega PCI-Express.

Praegu käib keerulise elektroonika vallas aktiivne ja kiire uute tehnoloogiate juurutamine, mille tulemusena võivad osa süsteemi komponendid vananeda ja neid ei saa uuendada jne.

Sellega seoses on vaja nendega ühendada erinevad lisandmoodulid ja tarvikud, mis sageli nõuavad teatud adaptereid.

Selles artiklis vaatleme pci-e pci-adapterit, selle toimimist ja funktsioone.

Definitsioon

Mis seade see on ja milleks see on? Rangelt võttes on see sisend- ja väljundsiin, mis ühendub personaalarvutiga.

Selle siiniga, st adapteriga, saate ühendada teatud arvu väliseid välisseadmeid (mis sõltub konfiguratsioonist).

Jadaühendust kasutades ühendatakse need välisseadmed arvutiga.

Sellise seadme peamine omadus on selle läbilaskevõime.

Just see iseloomustab (üldiselt) töö kvaliteeti, selle kiirust ning arvuti ja sel viisil ühendatud elementide jõudlust.

Läbilaskevõimet väljendatakse ühendusliinide arvus (1 kuni 32).

Sõltuvalt sellest peamisest omadusest võib selle seadme hind oluliselt erineda. See tähendab, et mida parem on see omadus (mida kõrgem on indikaator), seda suurem on sellise seadme maksumus. Lisaks sõltub palju tootja staatusest, seadmete töökindlusest ja vastupidavusest. Keskmiselt algab hind 250–500 rubla (madala ribalaiusega Aasia toodete puhul), kuni 2000 rubla (suure ribalaiusega Euroopa ja Jaapani seadmete puhul).

Tehnilised andmed

Tehnilisest küljest selline seade sisaldab kolme komponenti:

Eespool on kirjutatud seadme läbilaskevõime erakordsest tähtsusest selle normaalseks toimimiseks.

Mis on läbilaskevõime? Sellele küsimusele vastamiseks peate mõistma sellise adapteri tööpõhimõtet.

See on võimeline samaaegselt kahesuunaliseks (kaardilt välisseadmesse ja välisseadmest kaardile) seadmete ühendamiseks.

Sellisel juhul võib andmeedastus toimuda ühe või mitme rea kaudu.

Mida rohkem selliseid liine, seda stabiilsemalt seade töötab, seda suurem on selle läbilaskevõime ja seda kiirem on välisseadmed.

Tähtis! Olenevalt liinide arvust võib seadmel olla erinev konfiguratsioon: x1, x2, x4, x8, x12, x16, x32. Number näitab otseselt kahesuunalise samaaegse teabeedastuse radade arvu. Igaüks neist ribadest koosneb kahest juhtmepaarist (edastuseks kahes suunas).

Nagu kirjeldusest näha, mõjutab see konfiguratsioon oluliselt seadme maksumust.

Aga mis praktiline tähendus sellel on?Kas tõesti on mõtet seadme ostmisel lisakulutusi teha?

See sõltub otseselt sellest, kui palju kavatsete emaplaadiga ühendada - mida rohkem neid on, seda suuremat ribalaiust seade vajab arvuti stabiilse töö tagamiseks.

Krüpteerimine

Sellise teabeedastussüsteemi puhul kasutatakse selle kaitsmiseks moonutamise ja kadumise eest kindlat süsteemi.

See kaitsemeetod on tähistatud 8V/10V.

Asi on selles, et 8 biti vajaliku teabe edastamiseks tuleb kasutada 2 täiendavat teenindusbitti, et tagada turvalisus ja kaitse moonutuste eest.

Sellise adapteri töökorras edastatakse 20% teenindusinfost pidevalt arvutisse, mis ei kanna koormust ja mida kasutaja ei vaja. Kuid just see tagab siini ja välisseadmete stabiilsuse, kuigi see koormab (samas väga kergelt).

Lugu

2000. aastate alguses kasutati aktiivselt AGP laienduspesa ja just selle abiga .

Kuid mingil hetkel saavutati maksimaalne tehniliselt võimalik jõudlus ja tekkis vajadus luua uut tüüpi adapter.

Ja varsti ilmus PCI-E - see oli 2002.

Kohe tekkis vajadus adapteri järele, mis võimaldaks paigaldada uusi graafikalahendusi vananenud laienduspesasse või vastupidi.

Seetõttu hakkasid paljud arendajad ja tootjad 2002. aastal tõsiselt sellist adapterit looma.

Sel ajal oli seadmel üks oluline omadus - arvuti uuendamise võimalus, kulutades sellele minimaalselt, sest emaplaadi väljavahetamise asemel piisas suhteliselt odavast adapterist.

Kuid arendus ei olnud edukas, kuna sel ajal maksid need peaaegu sama palju kui esimesed adapterid ja seetõttu oli vaja välja töötada lihtsam adapteri konfiguratsioon.

Huvitaval kombel on tootjad ka selliste seadmete läbilaskevõimet järjekindlalt suurendanud. Kui esimeste konfiguratsioonide puhul ei olnud see enam kui 8 Gb/s, siis teise puhul juba 16 Gb/s ja kolmanda puhul 64 Gb/s. See vastas välisseadmete moderniseerimisest tulenevatele kasvavatele töömahtudele.

Samal ajal ühilduvad erineva edastuskiirusega pesad kõigi madalama "kiire" taseme seadmetega.

See tähendab, et kui ühendate teise või esimese põlvkonna graafikaplatvormi kolmanda põlvkonna pesaga, lülitub pesa automaatselt ühendatud seadmele vastavale erinevale kiirusrežiimile.

Erinevused PCI ja PCI-E vahel

Millised konkreetsed erinevused neil kahel konfiguratsioonil on?

Oma tehniliste ja tööomaduste poolest sarnaneb PCI AGP-ga, samas kui PCI-E on põhimõtteliselt uus arendus.

Kui PCI pakub paralleelset infoedastust, siis PCI-E jadaedastust, saavutades seeläbi oluliselt suurema infoedastuskiiruse ja jõudluse, isegi kui arvestada adapteri kasutamist.

Miks seda vaja on?

Milleks sellist adapterit vaja on ja milleks seda kasutada?Kas ilma selleta saab hakkama?

Peate mõistma, et enamik kasutajaid saab ilma selle seadmeta hakkama, kuna see pole vajalik isegi vanades arvutites, mis on olulisel määral kulunud.

See on lisavarustus, mis mõnel juhul parandab teie arvuti funktsionaalsust, kuid milleta tavakasutaja saab hõlpsasti hakkama.

Tegelikult annab sellise adapteri kasutamine ainult ühe peamise eelise – võimaluse ühendada mälukaardiga teatud arv välisseadmeid, samas kui nii paljusid neist otse ühendada on võimatu. Näiteks saate sel viisil ühendada diskreetse video või lisaks peamisele.

Samuti on üsna mugav võimalus vajadusel kõik välisseadmed korraga kiiresti välja lülitada.

Näiteks juhul, kui arvuti jõudlus väheneb või muudel põhjustel. Sel juhul ei pea kasutaja komponente pikka aega programmiliselt keelama.