Мало кто знает, но у истоков создания самого известного в мире процессора Intel Pentium были и советские специалисты и инженеры. В свое время СССР добился достаточно серьезных достижений в создании компьютерной техники. Примером этому может служить серия советских суперкомпьютеров «Эльбрус», которые были созданы в Институте точной механики и вычислительной техники (ИТМиВТ) в 1970-1990-х годах прошлого века, это же название носит серия микропроцессоров и систем, созданных на их основе и выпускаемых сегодня ЗАО МЦСТ (Московский центр SPARC-технологий).

История компании «-Эльбрус МСЦТ»- началась в 1992 году, когда Бабаян со своими коллегами и при участии Дэвида Дицеля, в то время работавшего в компании Sun Microsystems, организовали «-Московский центр SPARC-технологий»-. Позднее при участии Бабаяна были созданы еще несколько компаний: «-Эльбрус 2000″-, «-Эльбрус Интернейшнл»-, которые и образуют «-Эльбрус МЦСТ»-.

Компания работала как по заказам зарубежных компаний: Sun, Transmeta (именно в эту компанию перебрался со временем Дэвид Дицель), а также выполняла работы по заказам правительства России. Прежде всего, это используемые в российской армии вычислительные комплексы «-Эльбрус 90-микро»- на базе собственных процессоров серии МЦСТ R. За их создание Бабаян и его коллеги в своё время получили государственные награды.

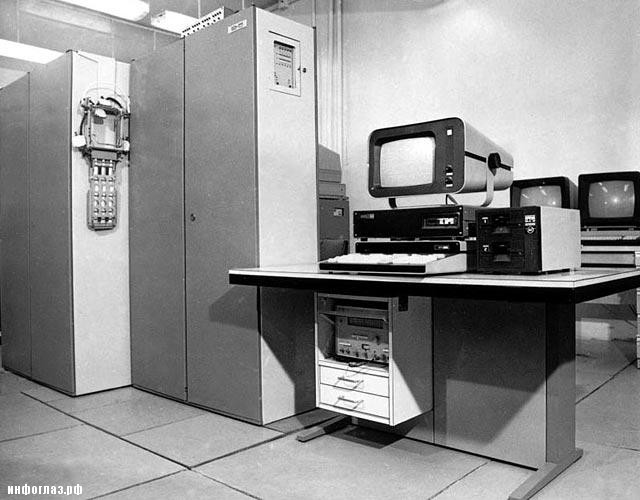

Однако история самого »-Эльбруса»- куда длиннее. Первый компьютер с таким названием был создан еще в 1978 году в ИТМиВТ им. С.А. Лебедева АН СССР под руководством Б.С. Бурцева и при участии Бориса Бабаяна, который был одним из заместителей главного конструктора. Основными заказчиками компьютеров «-Эльбрус»-были, конечно, военные.

Первый компьютер «Эльбрус» обладал модульной архитектурой и мог включать в себя от 1 до 10 процессоров на базе схем средней интеграции. Быстродействие данной машины достигало 15 миллионов операций в секунду. Объем оперативной памяти, которая была общей для всех 10 процессоров, составлял до 2 в 20 степени машинных слов или, если применять принятые сейчас обозначения, 64 Мб. Однако самым интересным в «Эльбрусе-1» была именно его архитектура. Созданный в СССР суперкомпьютер стал первой в мире коммерческой ЭВМ, которая применяла суперскалярную архитектуру. Ее массовое применение за рубежом началось только в 90-х годах прошлого века с появлением на рынке доступных процессоров Intel Pentium.

Как выяснилось позднее, подобные разработки существовали и до «-Эльбруса»- в корпорации IBM, однако работы эти были закрытыми и так и не привели к созданию коммерческого продукта. Правда, в ряде публикаций появлялись сведения, что при проектировании «-Эльбруса»- в основу были положены разработки зарубежных фирм. Однако участники создания советского суперкомпьютера с такой позицией не согласны. В одном из интервью В.С. Бурцев, главный конструктор «-Эльбруса»-, отметил, что при создании компьютера конструкторы старались использовать передовой опыт как отечественных, так и зарубежных разработчиков. И на архитектуру «-Эльбрусов»- оказали влияние не только компьютеры фирмы Burroughs, но и разработки таких фирм, как Hewlett-Packard, а также опыт создателей БЭСМ-6.

При этом немалая часть разработок была оригинальной, к ним относится и суперскалярная архитектура. Кроме этого для организации передачи потоков данных между периферийными устройствами и оперативной памятью в компьютере могли применяться специальные процессоры ввода-вывода. Таких процессоров в составе системы могло быть до 4-х штук, они работали параллельно с центральным процессором и обладали своей собственной памятью.

Следующим этапом работ явилось создание компьютера «Эльбрус-2». Эти ЭВМ отправились в серийное производство в 1985 году. По своей внутренней архитектуре они не сильно отличались от «Эльбрус-1», но применяли новую элементную базу, что позволило увеличить максимальную производительность до 125 млн. операций в секунду. Объем оперативной памяти компьютера увеличился до 16 млн. 72-разрядных слов или 144 Мб. Максимальная пропускная способность каналов ввода-вывода «Эльбруса-2» составляла 120 Мбайт/с.

Данные компьютеры активно применялись в СССР в областях, которые требовали большого количества вычислений, в первую очередь в оборонной отрасли. ЭВМ «Эльбрус-2» эксплуатировались в ядерных исследовательских центрах в Челябинске-70 и в Арзамасе-16 в ЦУПе, наконец, именно этот комплекс, начиная с 1991 года, применялся в системе ПРО А-135, а также на других военных объектах страны.

Помимо двух перечисленных выше компьютеров, также выпускался ЭВМ общего назначения «Эльбрус 1-КБ», создание данного компьютера было окончено в 1988 году. До 1992 года было произведено 60 таких ЭВМ. Они были основаны на технологиях «Эльбруса-2» и применялись для замены устаревших машин БЭСМ-6. При этом между «Эльбрус 1-КБ» и БЭСМ-6 существовала полная обратная программная совместимость, которая была дополнена новыми режимами работы с увеличенной разрядностью чисел и адресов.

Создание компьютеров «Эльбрус» было по достоинству оценено руководством Советского Союза. За разработку «Эльбруса-1» многие инженеры были награждены орденами и медалями. Борис Бабаян был награжден Орденом Октябрьской революции, его коллега В.В. Бардиж – орденом Ленина. За разработку «Эльбруса-2» Бабаян с рядом своих коллег был удостоен Ленинской премии, а генеральный конструктор В.С. Бурцев и ряд других специалистов – Государственной премии.

После завершения работ над ЭВМ «Эльбрус-2» в ИТМиВТ взялись за разработку ЭВМ на базе принципиально новой процессорной архитектуры. Проект, который был назван достаточно просто – «Эльбрус-3», также значительно опередил аналогичные разработки на Западе. В «Эльбрусе-3» впервые был реализован подход, который Борис Бабаян называет «постсуперскалярным». Именно такой архитектурой в будущем обладали процессоры Intel Itanium, а также чипы компании Transmeta. Стоит отметить, что в СССР работы над данной технологией были начаты в 1986 году, а Intel, Transmeta и HP приступили к реализации работ в этом направлении лишь в середине 1990-х годов.

К сожалению, «Эльбрус-3» так никогда и не был запущен в серийное производство. Его единственный работающий экземпляр был построен в 1994 году, но в это время он был никому не нужен. Логическим продолжением работ над данным компьютером стало появление процессора «Эльбрус-2000», известного также как E2K.

По словам Бориса Арташесовича Бабаяна, главного архитектора суперкомпьютеров линии Эльбрус, суперскалярная архитектура была изобретена в России: «-В 1978-ом году мы сделали первую суперскалярную машину, Эльбрус-1. Сейчас на Западе делают суперскаляры только такой архитектуры. Первый суперскаляр на Западе появился в 92-ом году, наш в 78-ом. Причем тот вариант суперскаляра, который сделали мы, аналогичен Pentium Pro, который Intel сделал в 95-ом году «-.

Подтверждают историческое первенство Эльбрус и в Америке. В той же статье из Microprocessor Report Кит Дифендорфф, разработчик Motorola 88110, одного из первых западных суперскалярных процессоров, пишет: «-В 1978 году, почти на 15 лет раньше, чем появились первые западные суперскалярные процессоры, в Эльбрус-1 использовался процессор, с выдачей двух команд за один такт, изменением порядка исполнения команд, переименованием регистров и исполнением по предположению «-.

В 1991г в Эльбрус (тогда еще ИТМиВТ) побывал г-н Розенбладт (Peter Rosenbladt) из фирмы Hewlett-Packard, и получил исчерпывающую документацию на Эльбрус-3. Позже выяснилось, что именно тогда HP начала проект, приведший к совместной с Intel разработке EPIC-процессора Merced. Его архитектура очень схожа с Эльбрус-3, а отличия в основном связаны с упрощениями сделанными в микропроцессоре от Intel.

По словам Б.А. Бабаяна, Петер Розенбладт предлагал сотрудничество с HP. Но Бабаян выбрал Sun (первая встреча с руководством Sun состоялась еще в 1989г). И в 1991г с Sun был заключен контракт. От официальных представителей Sun известно, что Эльбрус принимал участие в разработке микропроцессора UltraSPARC, оптимизирующих компиляторов, операционных систем (в том числе Solaris), инструментария Java, библиотек мультимедиа.

Первоначально проект E2k финансировался фирмой Sun. Сейчас проект полностью независим, вся интеллектуальная собственность на него принадлежит Эльбрус и защищена примерно 70-ю патентами США. Б.А. Бабаян поясняет «-Если бы мы и дальше работали с Sun в этой области, то все принадлежало бы Sun. Хотя 90% работы было выполнено еще до появления Sun «-.

В Sun с 1992 по 1995 Эльбрус работал вместе с известным микропроцессорным архитектором Дэйвом Дитцелом. Как рассказывает Б.А. Бабаян, «-Потом Дэйв образовал собственную фирму - Transmeta и начал работать над машиной, очень похожей на нашу. Мы по-прежнему поддерживаем с Дитцелом тесные контакты. Да и он очень хочет с нами сотрудничать «-. Про будущий продукт Transmeta пока известно мало. Известно, что это VLIW/EPIC микропроцессор с низким энергопотреблением, двоичная совместимость с x86 обеспечивается динамической трансляцией объектного кода.

Е2К против Itanium

64-битный процессор Intel Itanium не оправдал надежд и на бумаге сильно уступал «Эльбрус-2000».

С 1994 по 1998 годы о работе команды Бориса Бабаяна ничего не было слышно - русские готовили сенсацию. В 1998 году без особой шумихи Бабаян и Ко (порядка 400 сотрудников) переименовались в компанию «Эльбрус».

Тем временем зарубежные конкуренты не спали. В 1989 году Intel и Hewlett-Packard объединили свои силы для создания процессора нового поколения - Itanium (кодовое имя - Merced). Itanium должен был вобрать в себя все самые современные наработки и стать венцом процессоростроения. Многие ожидали, что новый процессор будет доминировать на рынке серверов, рабочих станций и, возможно, настольных компьютеров, вытеснив все остальные. Проектная частота Merced равнялась 800 МГц, уровень тепловыделения - 60 Вт, а объем кэш-памяти третьего уровня - от 2 до 4 Мбайт. При этом процессор должен был стать 64-битным.

Совершенно реальный процессор R500 от МЦСТ был блеклым отголоском многообещающего «Эльбрус-2000».

День Х настал 25 февраля 1999 года, когда на конференции Microprocessor Forum к трибуне поднялся лично Борис Бабаян и громко заявил, что его компания разработала микропроцессор «Эльбрус-2000» (Е2К), сильно опережающий хваленый Merced по всем характеристикам. Вся компьютерная общественность застыла в ожидании. Вместо запланированных двух часов Бабаян выступал четыре часа. Прозвучали ответы на вопросы относительно конкуренции со стороны западных компаний и перспектив выхода на рынок микропроцессора и компьютеров на его основе. В какой-то момент Борис Бабаян шокировал публику, заявив, что сумма для выпуска пробной партии процессоров «Эльбрус-2000» нужно $60 млн. Такая цифра отпугнула всех потенциальных инвесторов. Еще бы, ведь все обещания Бабаяна были чистой теорией - никаких инженерных сэмплов и прототипов показано не было.

Легенда компьютерного мира Гордон Бэлл (Gordon Bell), который, работая в DEC, создавал компьютеры линий PDP и VAX, а сейчас возглавляет исследовательское подразделение Microsoft (Telepresence Research Group), популяризирует проект Эльбрус E2k на международных конференциях.

Его лекция с названием «-Следующее десятилетие супервычислений»- (The Next Ten Years in Supercomputing) 26 мая 1999 г открывала Международный Симпозиум по Высокопроизводительным Вычислениям (International Symposium on High Performance Computing) в Японии, а 10 июня - четырнадцатую Манхеймовскую Конференцию по Суперкомпьютерам (Mannheim Supercomputer Conference) в Германии. Оба раза доктор Бэлл часть лекции посвятил рассказу о E2k. В слайде под названием «-Russian Elbrus E2K»- он приводит таблицу, где оценивает E2k и Merced. Причем сравнение свидетельствует явно не в пользу детища Intel.

Ниже приведена таблица из доклада Гордона Бэлла.

| Микропроцессор | E2K | Merced |

|---|---|---|

| Тактовая частота, ГГц | 1.2 | 0.8 |

| Производительность, SPECint95 / SPECfp95 | 135 / 350 | 45 / 70 |

| Размер кристалла, мм2 | 126 | 300 |

| Энергопотребление, Ватт | 35 | 60 |

| Пропускная способность шины, Гбайт/сек | 15 | н/д |

| Кэши (Кбайт) | 64 / 256 | н/д |

| Пиковая производительность, GFLOPS | 10.2 | н/д |

| Планируемое время начала поставок | 4-ый квартал 2001г | н/д |

Семейство процессоров Intel Pentium

- P54CS

- Tillamook

Pentium (произносится Пе́нтиум ) - торговая марка нескольких поколений микропроцессоров семейства x86 , выпускаемых корпорацией Intel с 22 марта 1993 года . Pentium является процессором Intel пятого поколения и пришёл на смену Intel 80486 (который часто называют просто 486).

История

Модели

Первоначально (22 марта 1993 года) было представлено только две модели, основанные на ядре P5 с частотами 60 и 66 МГц. Позже были выпущены и более производительные процессоры Pentium, основанные на усовершенствованных ядрах. Кроме того, были представлены мобильные версии процессоров и процессоры Pentium OverDrive.

| Кодовое имя ядра | P5 | P54C | P54CS | P55C | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Техпроцесс, нм | 800 | 600 | 350 | ||||||||||

| Тактовая частота ядра, МГц | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 166 | 200 | 233 |

| Анонсирован | 23 марта 1993 | 10 октября 1993 | 7 марта 1994 | 27 марта 1995 | 12 июня 1995 | 4 января 1996 | 10 июня 1996 | 8 января 1997 | 2 июня 1997 | ||||

P5

Единственные две модели процессоров Pentium первого поколения, с тактовой частотой ядра 60 и 66 МГц, были анонсированы 23 марта 1993 года.

Процессор выпускался в 273-контактном корпусе CPGA , на материнскую плату устанавливался в процессорный разъём Socket 4 и требовал питание напряжением 5 В. Частота системной шины (FSB) была равна частоте ядра, то есть множитель ядра был равен 1,0.

Все процессоры Pentium относятся к классу SL Enhanced - это значит, что в них предусмотрена система SMM , обеспечивающая снижение энергопотребления. Кэш второго уровня размещался на материнской плате и мог иметь размер до 1 Мб. Ранние варианты процессоров, с частотами 60-100 МГц (ядра P5 и P54C), имели ошибку в модуле математического сопроцессора , которая в редких случаях приводила к уменьшению точности операции деления. Этот дефект был обнаружен в 1994 году и стал известен как «Pentium FDIV баг ».

Процессоры на ядре P5 изготавливались с использованием 800-нанометрового техпроцесса , по биполярной BiCMOS -технологии. Процессор содержит 3,1 млн транзисторов, а размер кристалла ядра составляет 294 мм². Pentium 66 потребляет ток в 3,2 А и имеет мощность 16 Вт, что потребовало установки дополнительного вентилятора. Производство таких процессоров оказалось очень сложным и процент выхода годных кристаллов оказался слишком мал. Многие специалисты, указывая на многочисленные недостатки (см.: F0 0f c7 c8) процессоров Pentium первого поколения, не советовали покупать данные модели. Производство на время пришлось остановить. Однако вскоре началось производство усовершенствованных процессоров, основанных на ядре P54C.

P54C

В процессорах Pentium второго поколения используется умножение тактовой частоты, он работает быстрее системной шины. Для указания, во сколько раз тактовая частота ядра процессора больше частоты системной шины, используется множитель. Во всех процессорах, основанных на ядре P54C, множитель равен 1,5.

P54CS

Первые процессоры, основанные на данном ядре, были выпущены 27 марта 1995 года . По сути, это ядро представляет собой ядро P54C, изготовленное с использованием 350-нанометровой биполярной BiCMOS-технологии, что позволило уменьшить размер кристалла ядра до 91 мм² (процессоры Pentium 120 и 133), однако вскоре, в результате оптимизации ядра, его размер удалось уменьшить до 83 мм² при том же количестве транзисторов. При этом Pentium 200 потреблял ток в 4,6 А, а его максимальная рассеиваемая энергия (тепловыделение) составляло 15,5 Вт.

P55C

8 января 1997 года были выпущены процессоры Pentium, основанные на ядре P5 третьего поколения (P55C). Центром разработок и исследований Intel в Хайфе (Израиль) в ядро P55C был добавлен новый набор инструкций, названный MMX (MultiMedia eXtension), существенно увеличивающий (от 10 до 60 %, в зависимости от оптимизации) производительность компьютера в мультимедиа-приложениях. В результате, эти процессоры именуются Pentium w/MMX technology (обычно сокращается до Pentium MMX). Новый процессор включает в себя устройство MMX с конвейерной обработкой команд, кэш L1 увеличен до 32 Кб (16 Кб для данных и 16 Кб для инструкций). Состоит новый процессор из 4,5 млн транзисторов и производится по усовершенствованной 280-нанометровой CMOS -технологии с использованием кремниевых полупроводников, работает на напряжении 2,8 В. Максимальный потребляемый ток равен 6,5 А, тепловыделение равно 17 Вт (для Pentium 233 MMX). Площадь кристалла у процессоров Pentium MMX равна 141 мм². Процессоры выпускались в 296-контактном корпусе типа CPGA или PPGA для Socket 7.

Pentium OverDrive

Было выпущено несколько поколений Pentium OverDrive.

- В 1995 году вышел первый Pentium OverDrive (на ядре P24T). Он был предназначен для установки в гнёзда типа Socket 2 или Socket 3 и работал с напряжением питания 5 В, то есть служил для модернизации систем, использующих процессор 486 без замены материнской платы. При этом данный процессор обладал всеми функциями процессора Pentium первого поколения (на ядре P5). Было выпущено две модели, работающие на частотах 63 и 83 МГц, старшая потребляла ток в 2,8 А и обладала рассеиваемой мощностью 14 Вт. Из-за высокой стоимости данный процессор ушёл, не успев появиться. И хотя через некоторое время (4 марта 1996 года) на смену этим процессорам пришли Pentium ODP5V с частотами 120 и 133 МГц, основанные на ядре P5T (по сути, представляет собой ядро P54CS), они также не стали популярны.

- 4 марта 1996 года выходит следующая версия Pentium OverDrive - Pentium ODP3V - на ядре P54CT. Данное ядро основано на ядре P54CS. Процессор выпускался в 320-контактном корпусе CPGA для Socket 5 или Socket 7.

- 3 марта 1997 года выходят две модели Pentium ODPMT (с частотами 150 и 166 МГц), построенные на ядре P54CTB (аналог P55C). Позже, 4 августа 1997 года, выходят ещё две модели на том же ядре (с частотами 180 и 200 МГц). Они выпускались в 320-контактных корпусах CPGA и были предназначены для Socket 5 или Socket 7 (Pentium ODPMT-200 MMX - только для Socket 7).

Tillamook

Процессоры, основанные на данном ядре, предназначались для портативных компьютеров, использовались в т. н. «мобильном модуле» MMC-1 Mobile Module Connector с 280 пинами работали вместе с чипсетом Intel 430 TX и имея при этом 512 КБ кэш-памяти на системной плате. Ядро Tillamook (названо в честь города в штате Орегон , США), представляет собой ядро P55C с пониженным напряжением питания - модель с частотой 300 МГц работала с напряжением 2,0 В, потребляя при этом ток в 4,5 А и обладала тепловыделением в 8,4 Вт. Старшие модели (с частотой 233, 266 и 300 МГц) выпускались с использованием 250-нм техпроцесса и имели кристалл площадью 90 мм², также существовали версии со 166 МГц частотой ядра Модели 200 и 233 выпускались с августа 1997 г., модель 266 с января 1998, а старшая в линейке модель была представлена в январе 1999 г.

Pentium (произносится Пентиум) - торговая марка нескольких поколений микропроцессоров семейства x86, выпускаемых корпорацией Intel с 22 марта 1993 года. Pentium является процессором Intel пятого поколения и пришёл на смену Intel 80486 (который часто называют просто 486).

Отличия от i3(4)86:

- адресная память в стравнении с предыдущей моделью не изменилась;

- шана данных 64 бита (если Pentium 32 бита);

- впервые 2 конвейера самостоятельно считывает и обрабатывает потоки;

- впервые появилось спекулятивное исполнение команд;

- впервые используется такая технология, как автоматическое переупорядочивание команд:

Измененный порядок ни на что не влияет. НО проблема - условный переход.

ADD AX,BX ADD CX,AX YZ M1 MOV DX, 5h

Решение: предпологается, что переход выполнился, следовательно, произошло считывание команды в конвейер; если выясняется, что все правильно - продолжается выполнение, иначе - происходит сброс конвейера и перезагрузка с места перехода.

Основания для предположения:

- статистика переходов (если много, кратный цикл);

- блок предстказаний использует статистику: если переход условный, указывает назад, то с большой вероятностью выполнится. (Пример: repeat until). А если вперед, то большая вероятность, что не будет выполняться.

Впервые аппаратная поддержка мультипроцессорности (соединение с помощью специальной шины/спец интерфейса)

{Шина данных 32 ----> 64, так как 2 конвеера}

Тактовая частота Pentium: 60-150 МГц Тактовая частота MMX: 200 МГц

Существуют дополнительные регистры, отвечающие за прошедшее с начала кода число тактов.

Существует команда CPUID - идентификатор CPU.

Всевозможные регистры.

Архитектурная особенность

(до этого CISC) Существует внутренний перекодировщик преобразования CISC команд во внутренний код RISC в оболочке CISC.

Прерывание: ранее --> PIC (программный контроллер прерывания).

Ранее источник прерывающий сигнал на ножке процессора, и адрес перехода.

APIC: источник - сообщение, приходящее по специальной шине.

Процессор Intel Pentium P6200

Intel Pentium P6200 - процессор начального уровня, предназначенный для ноутбуков. Он работает на частоте 2.13 ГГц, но, к сожалению, не поддерживает технологию TurboBoost для автоматического разгона. Кроме того, отсутствует функция шифрования AES и поддержка многопоточности. CPU поддерживает технологию Enhanced Speedstep, которая позволяет снизить энергопотребление во время низкой нагрузки на процессор, но другие энергосберегающие технологии в данном процессоре отключены (также как и в серии Penryn Pentium).

P6200 основан на микроархитектуре Arrandale, следовательно, имеет встроенный контроллер памяти и графическую карту Intel HD Graphics (оба произведены по 45 нм технологическому процессу, а CPU по 32 нм). Встроенная видеокарта GMA HD работает на частоте 500 МГц и способна разгоняться до 667 МГц благодаря технологии Turbo Boost.

Производительность данного процессора немного ограничена из-за низкой тактовой частоты и отсутствия Turbo Boost и Hyperthreading. Если судить по показателю частоты в ГГц, то процессор Pentium P6200 должен быть чуть лучше, чем Core 2 Duo с аналогичной тактовой частотой, из-за встроенного контроллера памяти и небольших улучшений в ядре.

*Указанные тактовые частоты могут быть изменены производителемИстория появления Pentium процессора

Одним обычным тихим воскресным утром 10 мая 1992 года,четыре инженера фирмы INTEL прибыли в аэропорт San Jose International. Установив видеоаппаратуру, Анджела Чанг, Эрик Деваннайн, Автар Саини и Сухель Заатри нервозно прохаживались по залу, ожидая с минуты на минуту самолета из Орегона.

Когда Марк Хопман, спустя несколько минут после приземления самолета, вышел из коридора, держа в руках маленький голубой чемодан, вся встречающая группа направилась к нему. Все внимание было приковано к чемодану, в котором находился продукт разработчиков 5 Орегонской фабрики. Трудно было поверить, что в этом чемодане находился результат трехлетнего труда многих людей, воплощенный в маленький чип. Так началась жизнь Pentium процессора, который формально был представлен 22 марта 1993 года.

В то время, когда Винод Дэм делал первые наброски, начав в июне 1989 года разработку Pentium процессора, он и не подозревал, что именно этот продукт будет одним из главных достижений фирмы INTEL. С появлением Pentium процессора рынок компьютеров сразу изменился и начался новый этап конкуренции. San Microsistems, MIPS и другие продавцы RISC процессоров, разрабатывающие супербыстрые чипы, безоговорочно признали, что новый процессор фирмы INTEL станет стандартом для новых настольных PC.

Процесс рождения Pentium процессора был нелегким

По теории, создавая процессор, команда разработчиков создает концепцию проекта, в котором определяются его основные свойства и нововведения. Далее инженеры проектируют логику,которая затем воплощается в конкретные схемы. Как только заканчивается схемотехническое проектирование, проектировщики топологии прорисовывают каждый транзистор. В результате их труда создается конечный шаблон.Реально же все было иначе. Традиционный процесс проектирования был кардинально переработан, поскольку требовались ускоренные темпы реализации проекта.

Как только команда разработчиков выполняла локальную задачу, мененджеры перераспределяли ресурсы. Каждый инженер решал персональную задачу. Командный дух постоянно подвергался таким испытаниям, как задержки и трудности, однако временной план выполнения проекта от этого не зависел. Для выполнения всех задач использовались самые последние достижения автоматизированного проектирования. Очень пригодился опыт, накопленный при проектировании и решении аналогичных проблем в 286, Intel386 и Intel486 процессорах.

Как только выполнялся очередной этап проекта, сразу начинался процесс всеобъемлющего тестирования. Было желание не повторить проблемы, возникшие в свое время с Intel486, задержавшие его запуск в производство. Каждая ошибка трассировалась в обратном порядке и устранялись ее причины. Остальные инженеры выполняли сотни тестирований для проверки логики, архитектуры и общей конструкции. Они выполнили более, чем 5000 уточняющих тестирований, прежде, чем Pentium процессор обрел свою архитектуру. Для тестирования была разработана специальная технология, позволившая имитировать функционирование Pentium процессора с использованием программируемых устройств, объединенных на 14 платах с помощью кабелей. Только когда были обнаружены все ошибки, процессор смог работать в реальной системе. В дополнение ко всему, в процессе разработки и тестирования Pentium процессора принимали активное участие все основные разработчики персональных компьютеров и программного обеспечения, что немало способствовало общему успеху проекта.

В конце 1991 года, когда была завершен макет процессора, инженеры смогли запустить на нем программное обеспечение. Проекировщики начали изучать под микроскопом разводку и прохождение сигналов по подложке с целью оптимизации топологии и повышения эффективности работы. Проектирование в основном было завершено в феврале 1992 года. Началось всеобъемлющее тестирование опытной партии процессоров, в течение которого испытаниям подвергались все блоки и узлы. В апреле 1992 года было принято решение, что пора начинать промышленное освоение Pentium процессора. В качестве основной промышленной базы была выбрана 5 Орегонская фабрика.

Более 3 миллионов транзисторов были окончательно перенесены на шаблоны. Началось промышленное освоение производства и доводка технических характеристик, завершившиеся через 10 месяцев, 22 марта 1993 года широкой презентацией Pentium процессора.

Современная микропроцессорная технология фирмы INTEL

Достижения фирмы INTEL в искусстве проектирования и производства полупроводников делают возможным производить мощные микропроцессоры в все более малых корпусах. Разработчики микропроцессоров в настоящее время работают с комплементарным технологическим процесом металоксид полупроводник (CMOS) с разрешением менее, чем микрон.

Использование субмикронной технологии позволяет разработчикам фирмы INTEL располагать больше транзисторов на каждой подложке. Это сделало возможным увеличение количества транзисторов для семейства X86 от 29,000 в 8086 процессоре до 1,2 миллионов в процессоре Intel486 DX2, с наивысшим достижением в Pentium процессоре. Выполненный по 0.8 микронной BiCMOS технологии, он содержит 3.1 миллиона транзисторов. Технология BiCMOS объединяет преимущества двух технологий: биполярной (скорость) и CMOS (малое энергопотребление). С помощью более, чем в два раза большего количества транзисторов Pentium процессора по сравнению с Intel486, разработчики поместили на подложке компоненты, ранее располагавшимися снаружи процессора. Наличие компонентов внутри уменьшает время доступа, что существенно увеличивает производительность. 0.8 микронная технология фирмы INTEL использует трехслойный метал и имеет уровень, более высокий по сравнению с оригинальной 1.0 микронной технологией двухслойного металла, используемой в процессоре Intel486.

Фирма INTEL использовала самые последние достижения технологии проектирования микропроцессоров для достижения преимуществ, сравнимых с альтернативными архитектурами, используемыми в научных и инженерных рабочих станциях, обеспечив при этом совместимость с програмным обеспечение стоимостью $50 миллиардов, наработанного для семейства микропроцессоров серии X86.

Да и само программное обеспечение для Pentium процессора разрабатывалось по новой технологии. Еше на этапе проектирования аппаратных средств процессора к проекту стали привлекаться эксперты из всех основных компаний, разрабатывающих операционные системы и компиляторы - Microsoft, IBM, NeXT, Borland, Watcom, MetaWare и др. Это позволило на аппаратном уровне поддержать новые технологии программирования с учетом фирменного стиля поставщиков стандартного программного обеспечения. С другой стороны, еще до рождения нового процессора использовались методы классической и специльной оптимизации, раскрывающие специфические достоинства архитектуры X86, например, использование команд загрузки-записи, мощных режимов адрессации, удаление инвариантных участков кода из циклов и т.д. Теперь, только за счет перекомпиляции традиционных приложений удается повысить их производительность на новом процессоре еще вдвое. Такого в настоящее время не может предложить не один из конкурентов фирмы INTEL.

Новое поколение процессоров фирмы INTEL

Объединяя более, чем 3.1 миллион транзисторов на одной кремниевой подложке, 32-разрядный Pentium процессор характеризуется высокой производительностью с тактовой частотой 60 и 66 МГц. Его суперскалярная архитектура использует усовершенствованные способы проектирования, которые позволяют выполнять более, чем одну команду за один период тактовой частоты, в результате чего Pentium в состоянии выполнять огромное количество PC-совместимого программного обеспечения быстрее, чем любой другой микропроцессор. Кроме существуюших наработок программного обеспечения, высокопроизводительный арифметический блок с плавающей запятой Pentium проессора обеспечивает увеличение вычислительной мощности до необходимой для использования недоступных ранее технических и научных приложений, первоначально предназначенных для платформ рабочих станций. Также, как локальные и глобальные сети продолжают вытеснять устаревшие иерархические сети, управляемые большими ЭВМ, преимущества мультипроцессорности и гибкость операционной системы Pentium процессора - идеал для Хост-компьютера для современных приложений клиент-серверов, применяемых в промышленности.

Поскольку Pentium процессор способен достигать уровня производительности равного или более высокого, чем современные рабочие станции высокого уровня, он обладает преимуществми, которых лишены обычные рабочие станции: полная совместимость с более, чем 50 000 программных приложений со стоимостью миллиарды долларов, которые были написаны под ахитектуру фирмы INTEL. В дополнение, Pentium процессор позволяет использовать все основные операционные системы, которые доступны современным настольным персональным компьютерам, рабочим станциям и серверам, включая UNIX, Windows-NT, OS/2, Solaris и NEXTstep.

Pentium процессор. Технические нововведения

Многочисленные нововведения - характерная особенность Pentium процессора в виде уникального сочетания высокой производительности, совместимости, интеграции данных и наращиваемости. Это включает:

- Суперскалярную архитектуру;

- Раздельное кэширование программного кода и данных;

- Блок предсказания правильного адреса перехода;

- Высокопроизводительный блок вычислений с плавающей запятой;

- Расширенную 64-битовую шину данных;

- Поддержку многопроцессорного режима работы;

- Средства задания размера страницы памяти;

- Средства обнаружения ошибок и функциональной избыточности;

- Управление производительностью;

- Наращиваемость с помощью Intel OverDrive процессора.

Архитектура Pentium процессора

1 - 64-битовый шинный интерфейс;

2 - Средства кэширования программного кода;

3 - Буферы выборки с упреждением;

4 - 32-битовый целочисленный блок АЛУ;

5 - 32-битовый целочисленный блок АЛУ;

6 - Набор регистров;

7 - Средства кэширования данных;

8 - Блок предсказания правильного адреса перехода;

9 - Блок конвеерных вычислений с плавающей запятой.

Суперскалярная архитектура

Суперскалярная архитектура Pentium процессора представляет собой совместимую только с INTEL двухконвеерную индустриальную архитектуру, позволяющую процессору достигать новых уровней производительности посредством выполнения более, чем одной команды за один период тактовой частоты. Термин "суперскалярная" обозначает микропроцессорную архитектуру, которая содержит более одного вычислительного блока. Эти вычислительные блоки, или конвееры, являются узлами, где происходят все основные процессы обработки данных и команд.

Появление суперскалярной архитектуры Pentium процессора представляет собой естественное развитие предыдущего семейства процессоров с 32-битовой архитектурой фирмы INTEL. Например, процессор Intel486 способен выполнять несколько своих команд за один период тактовой частоты, однако предыдущие семейства процессоров фирмы INTEL требовали множество циклов тактовой частоты для выполнения одной команды.

Возможность выполнять множество команд за один период тактовой частоты существует благодаря тому, что Pentium процессор имеет два конвеера, которые могут выполнять две инструкции одновременно. Так же, как и Intel486 с одним конвеером, двойной конвеер Pentium процессора выполняет простую команду за пять этапов: предварительная подготовка, первое декодирование (декодирование команды), второе декодирование (генерация адреса), выполнение и обратная выгрузка. Это позволяет нескольким командам находиться в различных стадиях выполнения, увеличивая тем самым вычислительную производительность.

Каждый конвеер имеет свое арифметическо-логическое устройство (ALU), совокупность устройств генерации адреса и интерфейс кэширования данных. Так же как и процессор Intel486, Pentium процессор использует аппаратное выполнение команд, заменяющее множество микрокоманд, используемых в предыдуших семействах микропроцессоров. Эти инструкции включают загрузки, запоминания и простые операции АЛУ, которые могут выполняться аппаратными средствами процессора, без использования микрокода. Это повышает производительность без затрагивания совместимости. В случае выполнения более сложных команд, для дополнительного ускорения производительности выполнения расширенного микрокода Pentium процессора для выполнения команд используются оба конвеера суперскалярной архитектуры.

В результате этих архитектурных нововведений, по сравнению с предыдущими микропроцессорами, значительно большее количество команд может быть выполнено за одно и то же время.

Раздельное кэширование программного кода и данных

Другое важнейшее революционное усовершенствование, реализованное в Pentium процессоре, это введение раздельного кэширования. Кэширование увеличивает производительность посредством активизации места временного хранения для часто используемого программного кода и данных, получаемых из быстрой памяти, заменяя по возможности обращение ко внешней системной памяти для некоторых команд. Процессор Intel486, например, содержит один 8-KB блок встроенной кэш-памяти, используемой одновременно для кэширования программного кода и данных.

Проектировщики фирмы INTEL обошли это ограничение использованием дополнительного контура, выполненного на 3.1 миллионах транзисторов Pentium процессора (для сравнения, Intel486 содержит 1.2 миллиона транзисторов) создающих раздельное внутреннее кэширование программного кода и данных. Это улучшает производительность посредством исключения конфликтов на шине и делает двойное кэширование доступным чаще, чем это было возможно ранее. Например, во время фазы предварительной подготовки, используется код команды, полученный из кэша команд. В случае наличия одного блока кэш-памяти, возможен конфликт между процессом предварительной подготовки команды и доступом к данным. Выполнение раздельного кэширования для команд и данных исключает такие конфликты, давая возможность обеим командам выполняться одновременно. Кэш-память программного кода и данных Pentium процессора содержит по 8 KB информации каждая, и каждая организована как набор двухканального ассоциативного кэша - предназначенная для записи только предварительно просмотренного специфицированного 32-байтного сегмента, причем быстрее, чем внешний кэш. Все эти особенности расширения производительности потребовали использования 64-битовой внутренней шины данных, которая обеспечивает возможность двойного кэширования и суперскалярной конвеерной обработки одновременно с загрузкой следующих данных. Кэш данных имеет два интерфейса, по одному для каждого из конвееров, что позволяет ему обеспечивать данными две отдельные инструкции в течение одного машинного цикла. После того, как данные достаются из кэша, они записываются в главную память в режиме обратной записи. Такая техника кэширования дает лучшую производительность, чем простое кэширование с непосредственной записью, при котором процессор записывает данные одновременно в кэш и основную память. Тем не менне, Pentium процессор способен динамически конфигурироваться для поддержки кэширования с непосредственной записью.

Таким образом, кэширование данных использует два различных великолепных решения: кэш с обратной записью и алгоритм, названный MESI (модификация, исключение, распределение, освобождение) протокол. Кэш с обратной записью позволяет записывать в кэш без обращения к основной памяти в отличие от используемого до этого непосредственного простого кэширования.

Эти решения увеличивают производитльность посредством использования преобразованной шины и предупредительного исключения самого узкого места в системе. В свою очередь MESI-протокол позволяет данным в кэш-памяти и внешней памяти совпадать - великолепное решение в усовершенствованных мультипроцессорных системах, где различные процессоры могут использовать для работы одни и те же данные.

Высокопроизводительный блок вычислений с плавающей запятой

Нарастающая волна 32-разрядных программных приложений включает много интенсивно вычисляющих, графически ориентиро-программ, которые занимают много процессорных ресурсов на выполнение операций с плавающей запятой, обеспечивающих математические вычисления. Поскольку требования к персональным компьютерам со стороны программного обеспечения по вычислениям с плавающей запятой постоянно возрастают, удовлетворить эти потребности могут усовершенствования в микропроцессорной технологии. Процессор Intel486 DX, например, был первым микропроцессором, интегрированным на одной подложке с математическим сопроцессором. Предыдущие семейства процессоров фирмы INTEL, при необходимости использования вычислений с плавающей запятой, использовали внешний математический сопроцессор.

Pentium процессор позволяет выполнять математические вычисления на более высоком уровне благодаря использованию усовершенствованного встроенного блока вычислений с плавающей запятой, который включает восьмитактовый конвеер и аппаратно реализованные основные математические функции. Четырехтактовые конвеерные команды вычислений с плавающей запятой дополняют четырехтактовую целочисленную конвееризацмю. Большая часть команд вычислений с плавающей запятой могут выполняться в одном целочисленном конвеере, после чего подаются в конвеер вычислений с плавающей запятой. Обычные функции вычислений с плавающей запятой, такие как сложение, умножение и деление, реализованы аппаратно с целью ускорения вычислений.

В результате этих инноваций, Pentium процессор выполняет команды вычислений с плавающей запятой в пять раз быстрее, чем 33-МГц Intel486 DX, оптимизируя их для высокоскоростных численных вычислений, являющихся неотъемлемой частью таких усовершенствованных видеоприложений, как CAD и 3D-графика.

Pentium процессор на тактовой частоте 66 МГц работает как "числодробилка" с рейтингом 64.5 по тесту SPECint92, практически не уступая RISC-процессору Alpha компании Digital, но с тактовой частотой вдвое более высокой.

Общая производительность Pentium процессора превосходит в 6 раз 25 МГц Intel486 SX и в 2.6 раз - 66 МГц Intel486 DX2. Индекс по рейтингу iCOMP для 66 МГц Pentium процессора, который выполняет 112 миллионов операций в секунду, составляет 567. Индекс по iCOMP (Intel COmparative Microprocessor Peformance) выполняет относительное сравнение производительности 32-битовых процессоров фирмы INTEL.

Расширенная 64-битовая шина данных

Pentium процессор снаружи представляет собой 32-битовое устройство. Внешняя шина данных к памяти является 64-битовой, удваивая количество данных, передаваемых в течение одного шинного цикла. Pentium процессор поддерживает несколько типов шинных циклов, включая пакетный режим, в течение которого происходит порция данных из 256 бит в кэш данных и в течение одного шинного цикла.

Шина данных является главной магистралью, которая передает информацию между процессором и подсистемой памяти. Благодаря этой 64-битовой шине данных, Pentium процессор существенно повышает скорость передачи по сравнению с процессором Intel486 DX - 528 MB/сек для 66 МГц, по сравнению со 160 MB/сек для 50 МГц процессора Intel486 DX. Эта расширенная шина данных способствует высокоскоростным вычислениям благодаря поддержке одновременной подпитки командами и данными процессорного блока суперскалярных вычислений, благодаря чему достигается еще большая общая производительность Pentium процессора по сравнению с процессором Intel486 DX.

В общем, имея более широкую шину данных, Pentium процессор обеспечивает конвееризацию шинных циклов, что способствует увеличению пропускной способности шины. Конвееризация шинных циклов позволяет второму циклу стартовать ранше завершения выполнения первого цикла. Это дает подсистеме памяти больше времени для декодирования адреса, что позволяет использовать более медленные и менее дорогостоящие компоненты памяти, уменьшая в результате общую стоимость системы. Ускорение процессов чтения и записи, параллелилизм адреса и данных, а также декодирование в течение одного цикла - все вместе позволяет улучшить пропускную способность и повышает возможности системы.

Мультипроцессорность

Pentium процессор - это идеал для наростающей волны мультипроцессорных систем, а также высочайший уровень производительности и вычислительной мощности в области современных вычислительных средств. Мультипроцессорные приложения, которые соединяют два или более Pentium процессоров - хорошо обслуживаются посредством усовершенствованной архитектуры кристаллов, раздельным встроенным кэшированием программного кода и данных, а также наборами микросхем для управления внешней кэш-памятью и утонченными средствами контроля целостности данных.

Как обсуждалось ранее, Pentium процессор поддерживает упорядоченный кэш с его MESI протоколом. Когда один процессор получает доступ к данным, которые кэшируются в другом процессоре, он имеет возможность приема правильных данных. И если данные модифицировались, все процессоры получают возможность доступа к приему данных в модифицированном виде. Новейший Pentium процессор фирмы INTEL также определяет, какие команды распознаются системой в соответствии с ипользуемым способом программирования. Это строго определенно подсказывает, каким образом программному обеспечению, разработанному для однопроцессорной системы, корректно работать в многопроцессорном окружении.

Средства разделения памяти на страницы

Pentium процессор предлагает опции поддержки любой из традиционных размеров страниц памяти - 4 KB или более широкие, 4 MB страницы. Эта опция позволяет производить вычисление частоты свопинга страниц в комплексных графических приложениях, буферах фреймов, а также ядер операционных систем, где увеличенный размер страницы сейчас позволяет пользователям перепланировать шире первоначально громоздкие объекты. Увеличение страниц дает результат в виде повышения производительности, причем все это отражается на прикладном программном обеспечении.

Определение ошибок и функциональная избыточность

Хорошая защита данных и обеспечение их целостности посредством внутренних средств становится крайне важным в приложениях, критичным к потерям данных благодаря распространению современного окружения клиент-серверов. Pentium процессор содержит два усовершенствования, традиционно присущих проектированию класса больших ЭВМ - внутреннее определение ошибок и контроль за счет функциональной избыточности (FCR) - это помогает обеспечить целостность данных развивающихся сегодня систем, базирующихся на настольных компьютерах.

Внутреннее определение ошибок дополняет битом четности внутренний код и кэширование данных, сдвиговую ассоциативную таблицу страниц, микрокод, а также целевой буфер перехода, помогая определять ошибки таким образом, что это остается незаметным и для пользователя, и для системы. В то же время контроль с помощью функциональной избыточности оптимизирован для приложений, критических к потерям данных, где Pentium процессор может работать в конфигурации основной/контролирующий. Если между двумя процессорами обнаруживаются разногласия, система извещается об ошибке. В результате происходит обнаружение более, чем 99% ошибок.

Кроме того, на подложке процессора расположено устройство встроенного тестирования. Самотестирование охватывает более 70% узлов Pentium процессора, не требует выполнения сброса кристалла и представляет собой процедуру, обычно используемую при диагностике систем. Другими встроенными решениями является реализация стандарта IEEE 1149.1, позволяющая тестировать внешние соединения проессора и отладочный режим, дающий возможность программному обеспечению просматривать регистры и состояние процессора.

Управление производительностью

Управление производительностью - особенность Pentium процессора, что позволяет разработчикам систем и прикладных расширений оптимизировать свои аппаратные и программные средства посредством определения потенциально узкого места для программного кода. а работчики могут наблюдать и считать такты для внутренних событий процессора, таких, как производительность чтения и записи данных, кэширование совпадений и выпадений, прерываний и использования шины. Это позволяет им измерять эффективность, которую имеет код в двойной архитектуре Pentium процессора и в своих продуктах и выполнять тонкую настройку своих приложений или систем для достижения оптимальной производительности. Выгода для конечных пользователей - это более высокие достоинства и высшая производительность, и все это благодаря хорошему взаимодействию с Pentium процессором, пользовательской системой и прикладным программным обеспечением.

Давая возможность разработчикам проектировать системы с управлением энергопотреблением, защитой и другими свойствами, Pentium процессор поддерживаем режим управления системой (SMM), подобный режиму архитектуры Intel SL.

Наращиваемость

Вместе со всем, что сделано нового для 32-битовой микропроцессорной архитектуры фирмы INTEL, Pentium процессор сконструирован для легкой наращиваемости с использованием архитектуры наращивания фирмы INTEL. Эти нововведения защищают инвестиции пользователей посредством наращивания производительности, которая помагает поддерживать уровень продуктивности систем, основанных на архитектуре процессоров фирмы INTEL, больше, чем продолжительность жизни отдельных компонентов. Технология наращивания делает возможным использовать преимущества большинства процессоров усовершенствованной технологи в уже существующих системах с помощью простой инсталяции средства однокристального наращивания производительности. Например, первое средство наращивания - это OverDrive процессор, разработанный для процессоров Intel486 SX и Intel486 DX, использующий технологию простого удвоения тактовой частоты, использованную при разработке микропроцессоров Intel486 DX2.

Посредством наращивания одного из этих дополнительных процессоров в сокет, расположенный возле центрального микропроцессора на большинстве материнских платах Intel486, пользователи могут увеличить общую производительность системы более, чем на 70% практически для всех программных приложений.

Технология наращивания с помощью OverDrive процессоров возможна и для систем, основанных на семействе Pentium процессора, посредством простой установки в будущем процессора, выполненного по усовершенствованной технологии. В свою очередь, технология Pentium процессора является основой дополнительного процессора, разрабатываемого для систем, базируемых на Intel486 DX2.

Процессоры Pentium фирмы Intel представляют пятое поколение процессоров семейства х86. По базовой регистровой архитектуре и системе команд они совместимы с вышеописанными 32-битными процессорами, но имеют 64-битную шину данных, благодаря чему их иногда ошибочно называют 64-разрядными. По сравнению с предыдущими поколениями процессоры Pentium имеют следующие качественные отличия:

- Суперскалярная архитектура: процессор имеет два параллельно работающих конвейера обработки (U-конвейер с полным набором инструкций и V-конвейер с несколько ограниченным набором), благодаря чему он способен одновременно выполнять две инструкции. Однако преимущества этой архитектуры полностью реализуются только при специальном режиме компиляции ПО.

- Применение технологии динамического предсказания ветвлений совместно с выделенным внутренним кэшем команд объемом 8 Кбайт, обеспечивает максимальную загрузку конвейеров.

- Внутренний (Level 1) кэш данных объемом к Кбайт в отличие от 486-го работает с отложенной (до освобождения внешней шины) записью и настраивается на режим сквозной или обратной записи, поддерживая протокол

- Внешняя шина данных ради повышения производительности имеет разрядность 64 бит, что требует соответствующей организации памяти.

- Встроенный сопроцессор за счет архитектурных улучшений (конвейеризации) в 2-10 раз превосходит FPU-486 по производительности.

- Введено несколько новых инструкций, в том числе распознавание семейства и модели CPU.

- Применено выявление ошибок внутренних устройств (внутренний контроль паритета) и внешнего интерфейса шины, контролируется паритет шины адреса.

- Введена возможность построения функционально-избыточной двухпроцессорной системы.

- Реализован интерфейс построения двухпроцессорных систем с симметричной архитектурой (начиная со второго поколения Pentium).

- Введены средства управления энергопотреблением.

- Применена конвейерная адресация шинных циклов.

- Сокращено время (число тактов) выполнения инструкций.

- Введена трассировка инструкций и мониторинг производительности.

- Расширены возможности виртуального режима - введена виртуализация флага прерываний.

- Введена возможность оперирования страницами размером 4 Мб в режиме страничной переадресации (Paging).

Все Pentium-процессоры имеют средства SMM, возможности которых расширялись по мере появления новых моделей. Средства тестирования включают возможность выполнения встроенного теста BIST (Built-In Self Test), обеспечивающего выявление ошибок микрокодов, программируемых логических матриц, тестирование командной кэш-памяти, кэш-памяти хранения данных, буфера быстрой переадресации и ROM. Все процессоры имеют стандартный тестовый порт IEEE 1149.1, позволяющий тестировать процессор с помощью интерфейса JTAG.

В процессорах реализованы новые дополнительные средства отладки:

- зондовый режим (Probe Mode), обеспечивающий доступ к внутренним регистрам и пространствам ввода-вывода системной памяти процессора Pentium. Этот режим позволяет проверять и изменять состояние CPU, обеспечивая средства для отладки программ с возможностями, подобными внутрисхемным эмуляторам;

- расширения отладки DE (Debug Extensions), позволяющие ставить контрольные точки по адресам ввода-вывода;

- внутренние счетчики, используемые для текущего контроля производительности и учета числа событий;

- пошаговое исполнение с помощью команды CPUID.

Процессоры Pentium первого поколения (Р5) с тактовой частотой 60 и 66 МГц имели напряжение питания 5 В, что приводило к большому тепловыделению (на частоте 66 МГц - 16 Вт). Они выпускались в корпусах PGA-273 (матрица 21x21), для установки этих процессоров предназначен сокет 4.

Первые модели процессоров имели ошибку в FPU (floating point flaw), выражавшуюся в потере точности при выполнении деления с некоторыми сочетаниями операндов. Ошибка могла появляться от 4-го до 19-го разряда после десятичной точки. С начала 1995 года процессоры выпускались уже без ошибок. Статистические исследования показывают, что ошибка может проявляться раз в несколько лет. Тем не менее фирма Intel до сих пор обеспечивает бесплатную замену уже проданных процессоров с ошибкой на исправленные версии, но без «апгрейда» на более современные модели. Процессоры с ошибкой могут быть выявлены с помощью утилиты CPUIDF.EXE, которую можно получить на Web-сервере компании.

Pentium Overdrive 120 и 133 МГц (Overdrive for Pentium) - вариант процессора Pentium второго поколения (с пониженным энергопотреблением и удвоением частоты), предназначенный для замены процессоров Pentium 1-го поколения. Он имеет корпус PGA-273, устанавливаемый в сокет 4. Эти процессоры дороже обычных Pentium 120 или 133, их применение имеет смысл только тогда, когда по каким-либо причинам нет возможности заменить старую системную плату, а производительности Pentium 60 или 66 Мгц недостаточно. Но более мощный процессор в такую плату все равно уже не поставить.

Процессоры Pentium второго поколения (Р54) имеют напряжение питания 3,3 В и менее, что существенно снижает рассеиваемую мощность. При этом их входные и выходные сигналы остаются совместимыми с ТТЛ, однако для входов допустимый уровень сигнала ограничен на уровне 3,3 В (кроме тактовых входов CLC и PICCLC, допускающих уровень до 5 В). Более совершенные модели второго поколения используют технологию снижения напряжения питания VRT (Voltage Reduction Technology). При этом напряжение питания VCC для интерфейсных схем остается равным 3,3 В, а для питания ядра, потребляющего около 90% мощности, VCC снижено до 2,9 В, что уменьшает рассеиваемую мощность.

Процессоры изготавливаются в корпусах SPGA-296 с шахматным расположением выводов, для их установки предназначены сокеты 5 и 7. Сокет 7 имеет две шины питания: VCC2 для питания ядра процессора и VCC3 для питания интерфейсных схем - и допускает установку процессоров с VRT-технологией.

В процессорах второго поколения применяется внутреннее умножение частоты, при этом интерфейсные схемы внешней системной шины работают на частотах 50, 60 или 66,66 МГц, а ядро процессора работает на более высокой частоте (75, 90, 100, 120, 133, 150, 166, 180 и 200 МГц). Разделение частот позволяет реализовать достижения технологии изготовления процессоров, существенно опережающие возможности повышения производительности памяти и других традиционных компонентов компьютера. Коэффициент умножения (1,5, 2, 2,5 или 3) задается комбинацией уровней сигналов на входах BF0, BF1 в пределах, разрешенных спецификацией тактовой частоты процессора. Независимость установки внешней частоты и коэффициента умножения позволяет одну и ту же внутреннюю частоту задавать разными способами. Например, 100 МГц можно получить и как 50x2, и как 66,66x1,5. Последний вариант в общем случае предпочтительнее, поскольку при этом шина PCI будет работать на частоте 33 МГц, а не 25 МГц. Однако бывают и исключения: если установленная память при частоте 66 МГц потребует больше тактов ожидания, чем при 50 МГц, то предпочтительнее скорее всего будет частота 50 МГц.

Процессоры с различающимися значениями тактовых частот, указанных в маркировке на корпусе, выполняются по одним и тем же шаблонам (схемам) в пределах одной группы степпинга (см. ниже). Маркировка частоты наносится после жестких отбраковочных испытаний в зависимости от частоты, на которой он полностью прошел выходной контроль. Это открывает возможности для «разгона» процессоров, включая и пиратскую перемаркировку, когда на процессор наносится новое обозначение завышенной тактовой частоты. Против перемаркировки в некоторых моделях процессоров устанавливали специальные схемы, не допускающие разгона.

Pentium OverDrive 125, 150 и 166 МГц - вариант процессоров 2-го поколения для замены Pentium 75, 90 и 100 МГц. От обычных в основном отличаются фиксированным (установленным внутри корпуса) коэффициентом умножения частоты. Предназначены для установки в сокет 5 или 7.

Процессоры Pentium MMX (Р55С) - новое поколение процессоров, основанное на MMX-технологии, ориентированной на мультимедийное, 2D- и 3D- графическое и коммуникационное применение. В архитектуру Pentium введены восемь 64-битных регистров (точнее, появилась возможность иного использования регистров FPU), 4 новых типа данных и 57 дополнительных мнемоник инструкций для одновременной обработки нескольких единиц данных (SIMD - Single Instruction Multiple Data). Одновременно обрабатываемое 64-битное слово может содержать как одну единицу обработки, так и восемь однобайтных, четыре двухбайтных, или два четырехбайтных операнда. В остальных командах обеспечивается совместимость с Pentium.

Кроме MMX-расширения, в архитектуре Pentium MMX имеется ряд усовершенствований, повышающих его производительность и на обычных операциях. Более эффективный способ предсказания ветвлений позаимствован у Pentium Pro, удвоено число буферов записи (их стало четыре) и удвоен объем обеих частей кэша L1 (теперь 16+16 Кб), увеличено число ступеней конвейеров, улучшена возможность параллельных вычислений (процессор способен выполнять две SIMD-инструкции с 16-битными данными за 1 такт).

В двухпроцессорных системах Pentium MMX поддерживает только симметричную архитектуру, возможность функционально-избыточного контроля (FRC) изъята.

Применено раздельное питание ядра (напряжение 2,7-2,9 В, номинал 2,8 В) и интерфейсных схем (3,135 - 3,6 В, номинал 3,3 В). Процессор совместим по выводам с Pentium второго поколения с технологией VRT и устанавливается в сокет 7 (установка в сокет 5 механически возможна, но электрически недопустима).

Процессоры Pentium для мобильных применений имеют пониженное энергопотребление, обеспеченное снижением напряжения питания ядра процессора. Кроме того, из этих процессоров изъяты средства поддержки двухпроцессорных систем, APIC и соответствующие им внешние выводы. Процессоры этого класса исполняются в корпусах SPGA, а также в корпусах TCP, имеющих выводы, расположенные по периметру корпуса.

Интерфейс шины процессоров Pentium

По интерфейсу шина процессора Pentium напоминает шину i486, но имеет заметные отличия. Новые особенности направлены на поддержку политики обратной записи кэша, повышение производительности и обеспечение дополнительных функциональных возможностей. Если шина i486 была ориентирована на максимальную гибкость и простоту подключения устройств с различной разрядностью, то шина Pentium ориентирована на достижение максимальной производительности. Шина данных стала 64-битной для повышения производительности обмена с памятью. Возможность динамического управления разрядностью шины (сигналы BS16# и BS8#) изъята, согласование по разрядности с интерфейсными шинами возложено на микросхемы чипсета.

При разрешенном контроле паритета данных (сигналом PEN) ошибка вызывает не только срабатывание сигнала РСНК#, но и фиксацию сбойного адреса и данных в регистре машинного контроля. А если установлен бит MCE регистра CR4, по этой ошибке генерируется исключение 18.

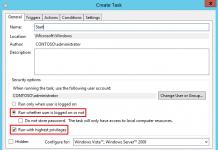

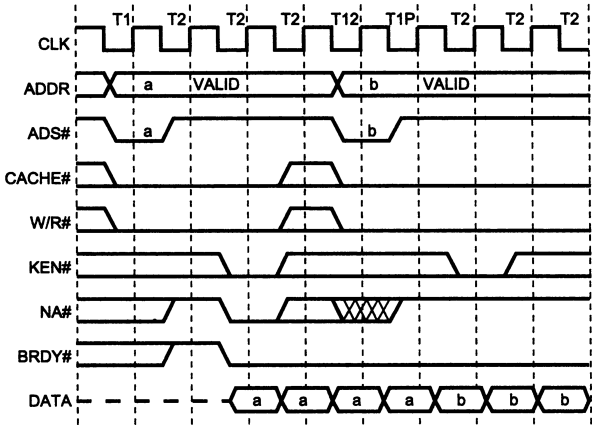

В дополнение к контролю паритета шины данных введен контроль паритета шины адреса. Обнаруженная ошибка паритета бит А шины адреса только вызывает сигнал ошибки АРСНК#, который может быть обработан системной логикой. Пакетные циклы выполняются только при обращениях к памяти, причем как при чтении (как это было у 486-го), так и при записи. Пакетные циклы связаны только с кэшируемой памятью, при этом кэшируемость памяти подразумевает и ее поддержку пакетного режима. Во время пакетного цикла сигналы разрешения байт и младшие биты адреса А не меняются (пакеты всегда выровнены по границам строк кэша). Порядок чередования адресов (табл. 1), как и у процессора 486, оптимизирован для двухбанковой организации памяти. Снова появилась конвейерная адресация на шине (как у 286-го и 386-го), что позволяет одновременно на шине присутствовать двум обслуживаемым запросам. На рис.1 и 2 приведены временные диаграммы одиночных и конвейеризованных пакетных циклов. Признаком пакетного цикла (и его окончания) является сигнал CACHE#. Внешняя система не может прервать пакетный цикл, начатый процессором (в 486-м она могла заставить процессор любой пакетный цикл преобразовать в обычные сигналом RDY#). Конвейеризация запрашивается сигналом NA#, в ответ на который процессор через такт выдаст адрес следующего цикла. Без конвейеризации следующий адрес (и тип цикла) был бы выставлен только после завершения передачи данных текущего цикла.

Как и у предыдущих процессоров, тип шинного цикла задается управляющими сигналами М/Ю#, D/C# и W/R#, действующими одновременно со стробом ADS#. Кроме циклов обращения к памяти, вводу-выводу и подтверждения прерывания, процессор имеет специальные шинные циклы, идентифицируемые по комбинации сигналов ВЕ# (табл.2). Эти циклы, так же как и остальные, требуют подтверждения сигналом BRDY#.

Рис.1. Одиночные циклы чтения и записи на шине Pentium

Рис.2. Конвейеризованные пакетные циклы чтения на шине Pentium

Процессор имеет вход EWBE#, с помощью которого он отслеживает состояние внешних буферов отложенной записи для обеспечения корректной последовательности шинных циклов записи. Для поддержания согласованности данных кэша и основной памяти процессор отрабатывает циклы слежения (Snoop Cycle или Inquire Cycle), инициированные внешней (для него) системой. Эти циклы, как и в 486-м, используют сигналы AHOLD#, EADS# и ответные сигналы процессора HIT# и HITM#. Сигнал FLUSH# вызывает выгрузку всех модифицированных строк первичного кэша (обратную запись). Циклы слежения инициируется системой для определения присутствия затребованной области памяти в строке какой-либо кэш памяти и определения ее состояния. Процессоры, начиная с Pentium, поддерживают протокол MESI, названный по определяемым им состояниям М (Modified), Е (Exclusive), S (Shared) и I (Invalid). Состояния определяются следующим образом:

M-state

- строка присутствует только в одном кэше и модифицирована, то есть отличается от содержимого основной памяти. Доступ к этой строке возможен без генерации внешнего (по отношению к локальной шине) цикла обращения;

E-state

- строка присутствует только в одном кэше, но не модифицирована. Доступ к этой строке возможен без генерации внешнего цикла обращения, при записи в нее она перейдет в состояние «М»;

S-state

- строка потенциально может присутствовать в нескольких кэшах. Ее чтение возможно без генерации внешнего цикла, а запись в нее должна сопровождаться сквозной записью в основную память, что повлечет аннулирование соответствующих строк в других кэшах;

I-state

- строка отсутствует в кэше, ее чтение может привести к генерации цикла заполнения строки. Запись в нее будет сквозной и выйдет на внешнюю шину.

Инициализация процессора выполняется по сигналу RESET, как и для предыдущих процессоров. В дополнение ко входу сброса RESET введен сигнал INIT, по которому процессор переходит в то же состояние, что и по сигналу RESET, но сохраняя содержимое кэша и регистров FPU. Этот сигнал может быть использован для переключения из защищенного режима в реальный.

Во время действия сигнала RESET должны установиться значение на входах управления коэффициентом умножения BF и частота на входе CLC. Колебания входной частоты не могут быстро отрабатываться схемой умножителя, построенной на основе петли фазовой автоподстройки частоты PLL (Phase Lock Loop). При нестабильности генератора входной частоты работоспособность процессора не гарантируется.

Для процессоров первого поколения умножение частоты не применялось (KF=1). Для процессоров с частотой 75-133 МГц коэффициент умножения (1,5 или 2) официально определялся сигналом BF, но фактически многие процессоры воспринимали два сигнала: BF0 (называемый просто BF) и BF1. Значение коэффициентов умножения для различных моделей Pentium приведены в табл.3. Пока что они отличаются только трактовкой коэффициента по умолчанию (когда оба вывода BF0 и BF1 свободны), но для грядущего процессора 266 МГц, вероятно, комбинация 10 будет означать коэффициент 4 (а не 2, как указано в справочном листке на процессоры ММХ).

|

||||||||||||||||||||||||||||||

** Допустимый диапазон внешней частоты 33,33-66,66 МГц.

В момент окончания действия сигнала RESET процессор кроме нормального рабочего режима может быть переведен в один из следующих режимов:

- BIST (Built-In Self Test) - встроенный тест, выполняемый приблизительно за 219 тактов ядра и охватывающий около 70% внутренних блоков процессора. Во время выполнения теста процессор не генерирует внешних циклов. После выполнения теста процессор переходит в рабочий режим, о результате завершения можно судить по содержимому регистра ЕАХ. Нулевое значение указывает на исправность, любое другое - на отказ какого-либо блока. Если во время выполнения BIST процессор обнаружит внутреннюю ошибку паритета, он выставит сигнал IERR# и попытается выполнить ShutDown. BIST запускается при высоком уровне сигнала INIT во время спада сигнала RESET;

- Tristate Test Mode - режим, при котором все (кроме TDO) выходные и двунаправленные сигналы переходят в третье состояние, включается по низкому уровню сигнала FLUSH# во время спада сигнала RESET;

- FRC - режим, при котором процессор работает в качестве проверяющего в функционально-избыточной двухпроцессорной системе. Включается при низком уровне на входе FRCMC# во время спада сигнала RESET.

Для процессоров Pentium источниками аппаратно вызываемых прерываний являются следующие входные сигналы, расположенные в порядке убывания приоритета:

- BUSCHK# - контроль шины, вызывающий исключение MCE;

- R/S# - переключение в зондовый режим;

- FLUSH# - очистка кэш-памяти (может вызвать поток операций записи);

- SMI# - прерывание входа в режим SMM;

- INIT - «мягкий» сброс процессора;

- NMI - немаскируемое прерывание;

- INTR - запрос маскируемых прерываний;

- STOPCLK# - останов синхронизации.

Здесь понятие прерывания трактуется несколько шире и относится ко всем событиям, заставляющим процессор генерировать внешние циклы вне очереди, определяемой прерываемой последовательностью инструкций (таким образом можно определить действие сигнала FLUSH#). Если в процессоре разрешена работа контроллера APIC, то прерывания, поступающие по его шине, заменяют в данном списке сигналы NMI и INTR.

Процессоры второго поколения имеют возможность изменять порядок приоритета прерываний с помощью бита ITR (бит 9 регистра TR12). В табл.4 приведены два возможных варианта приоритетов прерываний.

Зондовый режим отладки (Probe Mode) использует тестовый порт ТАР (Test Acess Port) подключения интерфейса JTAG. Этот интерфейс может использоваться не только для тестирования (Boundary Scan), но и для отладочных целей. Для этого в состав порта ТАР введен сигнал R/S#, по его отрицательному перепаду процессор завершает выполнение текущей инструкции и останавливается, сообщив об этом сигналом PRDY. В этом состоянии по интерфейсу JTAG внешнее отладочное устройство может «пообщаться» со всеми внутренними регистрами процессора, после чего, возвратив сигнал в неактивное состояние (высокий уровень), «отпустить» процессор для продолжения выполнения прерванного потока инструкций. По предоставляемым возможностям отладки зондовый режим эквивалентен внутрисхемному эмулятору - мечте любого разработчика самого аппаратно-зависимого программного обеспечения. Для подключения порта ТАР фирма Intel предлагает на системной плате устанавливать специальный 20- или 30-штырьковый разъем, к которому подключается шлейф внешнего отладчика. На этот разъем выводятся сигналы процессора R/S#, PRDY, TDI, TDO, TMS, ТСК и TRST# - все, что нужно для внутрисхемной отладки. Но даже если этого разъема нет на системной плате, подключиться к выводам ТАР можно через специальную переходную колодку, к которой подключен шлейф ТАР. Колодка вставляется в сокет, а в нее - процессор. Есть и сдвоенные колодки для отладки двухпроцессорных систем.

|

Режим SMM реализован аналогично предыдущим процессорам 386SL и 486SL, но начиная со второго поколения имеется возможность рестарта инструкций (см. табл. 3.9) и входа в SMM по сообщению, принятому с шины APIC.

Процессоры Pentium 2-го поколения имеют возможность снижения энергопотребления в нерабочем режиме (табл. 5). По сигналу STOPCLK# процессор выгружает буфера записи и входит в режим Stop Grant, в котором прекращается тактирование большинства узлов процессора, что вызывает снижение энергопотребления примерно в 10 раз. В этом состоянии он прекращает исполнение инструкций и не обслуживает прерывания, однако продолжает слежение за шиной данных, отслеживая кэш-попадания. Из этого состояния процессор выходит по снятию сигнала STOPCLK#. Управление сигналом STOPCLK# совместно с использованием режима SMM реализует механизм расширенного управления питания АРМ (Advanced Power Management). При отсутствии активности внешняя схема (чипсет) по команде, исполненной в режиме SMM, устанавливает данный сигнал. По пробуждающему событию внешняя схема (без участия процессора, который «спит») снимает сигнал, и процессор продолжает работу. Кроме того, с помощью сигнала STOPCLK# возможно и замедление процессора (с пропорциональным снижением потребляемой мощности), если на этот вход подавать периодический импульсный сигнал. Скважность импульсов будет определять коэффициент простоя процессора и, следовательно, его производительность (как бы снижая условную тактовую частоту).

В состояние пониженного потребления Auto HALT PowerDown процессор переходит при исполнении инструкции HALT. В этом состоянии процессор реагирует на все прерывания и также продолжает слежение за шиной. В режиме остановки внешней синхронизации процессор потребляет минимальную мощность, но в этом режиме он не выполняет никаких функций, а последующая подача синхронизации должна сопровождаться сигналом аппаратного сброса RESET.

*В режиме остановки синхронизации процессор потребляет менее 0,3 Вт.В Pentium первого поколения имеются выходные сигналы трассировки, отражающие работу конвейеров (IU, IV), факты ветвлений (IBT) и трассу ветвлений ВТЗ-ВТО. Однако в процессорах второго поколения этих выводов нет - видимо, их наблюдать стало уже не интересно. Назначение сигналов приведено в табл.6.

|

Расширения архитектуры

Относительно базовой архитектуры 32-разрядных процессоров и ее развития в процессорах четвертого поколения процессоры Pentium (и старше) имеют ряд расширений, появляющихся по мере совершенствования моделей. Для возможности получения сведений о них в систему команд включена инструкция CPUID, позволяющая программно в любой момент времени (а не только сразу после сигнала RESET) получить сведения о классе, модели и архитектурных особенностях конкретного процессора. Подробно применение этой инструкции описано в п. 7.2.

В дополнение к базовой архитектуре 32-разрядных процессоров Pentium имеет набор регистров, специфических для модели - MSR (Model Specific Registers). В их число входит группа тестовых регистров (TR1-TR12), средства мониторинга производительности, регистры-фиксаторы адреса и данных цикла, вызвавшего срабатывание контроля машинной ошибки. Название этой группы регистров указывает на их возможную несовместимость для разных классов (Pentium и Pentium Pro) и даже моделей процессоров. Программа, их использующая, должна опираться на сведения о процессоре, полученные по инструкции CPUID.

Средства для мониторинга производительности включают таймер реального времени и счетчики событий. Таймер TSC (Time Stamp Counter) представляет собой 64-битный счетчик, инкрементируемый с каждым тактом ядра процессора. ДЛЯ чтения его содержимого предназначена инструкция RDTSC.

Счетчики событий CTRO, CTR1 разрядностью по 40 бит программируются на подсчет событий различных классов, связанных с шинными операциями, исполнением инструкций, событиями во внутренних узлах, связанных с работой конвейеров, кэша, контролем точек останова и т. п. Шестибитные поля типов событий позволяют каждому из счетчиков независимо назначить подсчет событий из обширного списка. Состояние счетчиков может быть предустановлено и считано программно. Кроме того, имеются внешние сигналы РМ, которые программируются на указание фактов срабатывания или переполнения соответствующих счетчиков. Поскольку эти сигналы могут менять свое значение с частотой, не превышающей частоту системной шины, из-за внутреннего умножения частоты каждое появление этих сигналов может отражать и несколько (до значения коэффициента умножения) фактов срабатывания счетчиков.

Тестовые регистры позволяют управлять большинством функциональных узлов процессора, обеспечивая возможность весьма подробного тестирования их работоспособности. С помощью бит регистра TR12 можно запретить новые архитектурные свойства (предсказание и трассировку ветвлений, параллельное выполнение инструкций) а также работу первичного кэша:

- бит 0 - NBP (No Branch Prediction) - запрещает заполнение буфера ВРВ. При этом прежние вхождения продолжают действовать, для полного отключения предсказания необходимо загрузить регистр CR3 (это вызовет сброс таблицы ветвлений);

- бит 1 - TR - разрешает формирование специального цикла сообщения о ветвлении;

- бит 2 - SE (Single Pipe Execution) - запрещает работу второго конвейера (отменяет парное исполнение инструкций);

- бит 3 - Cl (Cache Inhibit) - запрещает заполнение строк первичного кэша. В отличие от бита CD регистра CR0, этот бит не влияет на сигнал PCD, тем самым обеспечивается возможность работы внешнего вторичного кэша при запрещенном первичном (в тестовых целях);

- бит 9 - ITR (Ю Trap Restart) - разрешает поддержку рестарта инструкций ввода-вывода при прерываниях SMI.

В технической информации на процессоры Pentium есть упоминание о свойстве «Programmable Buffer Size». Первое, что приходит в голову при переводе, будет звучать «как программируемый размер буферов» и наводит на мысль о буферах записи. На самом деле к свойствам программной или логической архитектуры это не имеет никакого отношения, а является способностью управлять чисто электрическими свойствами буферных схем интерфейса.

Двухпроцессорные системы

Процессоры Pentium начиная со второго поколения имеют специальные интерфейсные средства для построения двухпроцессорных систем. Интерфейс позволяет на одной локальной системной шине устанавливать два процессора, при этом почти все их одноименные выводы просто непосредственно объединяются. Целью объединения является либо использование симметричной мультипроцессорной обработки SMP (Symmetric Multi-Processing), либо построение функционально-избыточных систем FRC (Functional Redundancy Checking).

В системе с SMP каждый процессор выполняет свою задачу, порученную ему операционной системой. Поддержку SMP имеют такие ОС, как Novell NetWare, Windows NT, Unix. Оба процессора разделяют общие ресурсы компьютера, включая память и внешние устройства. В каждый момент времени шиной может управлять только один процессор из двух, по определенным правилам они меняются ролями.

Поскольку каждый из процессоров имеет свой внутренний первичный кэш, в круг задач интерфейса входит поддержание согласованности данных во всех иерархических ступенях оперативной памяти (два первичных, один вторичный кэш и основная память). Эта задача решается с помощью локальных циклов слежения, воспринимаемых процессором, не управляющим шиной в данный момент по сигналу ADS#, генерируемому другим процессором. Ответами на локальные циклы слежения являются сигналы PHIT# и PHITM#, а роль сигналов HIT# и HITM# остается прежней - они используются во внешних (по отношению к обоим процессорам) циклах слежения, инициируемых сигналами EADS#.

Для обработки аппаратных прерываний в многопроцессорных системах традиционные аппаратные средства становятся непригодными, поскольку прежняя схема подачи запроса INTR и передачи вектора в цикле INTA# явно ориентирована на единственность процессора. Для решения этой задачи в структуру процессоров Pentium начиная со второго поколения введен расширенный программируемый контроллер прерывания APIC (Advanced Programmable Interruption Controller). Этот контроллер имеет внешние сигналы локальных прерываний LINT и трехпроводную интерфейсную шину (PICD и PICCLK), по которым оба процессора связываются с контроллером APIC системной платы. Запросы локальных прерываний обслуживаются только тем процессором, на выводы которого (LINTO, LINT1) поступают их сигналы. Общие (разделяемые) прерывания (в том числе и SMI) приходят к процессорам в виде сообщений по интерфейсу APIC. При этом контроллеры предварительно программируются, определяя функции каждого из процессоров в случае возникновения того или иного аппаратного прерывания. Контроллеры APIC каждого из процессоров и контроллер системной платы, связанные интерфейсом APIC, выполняют маршрутизацию прерываний (Interrupt Routing), причем как статическую, так и динамическую. Внешне программный интерфейс обработки прерываний остается совместимым с управлением контроллера 8259А, что обеспечивает прозрачность присутствия APIC для прикладного программного обеспечения. Режим обработки прерываний посредством APIC разрешается сигналом APICEN по аппаратному сбросу, впоследствии он может быть запрещен программно.

Арбитраж процессоров выполняется с помощью «приватных» сигналов запроса (PBREQ#) и подтверждения передачи (PBGNT#) управления локальной шиной. Процессор - текущий владелец шины - отдаст управление шиной другому процессору по его запросу только по завершении операции. Сблокированные циклы не могут прерываться другим процессором, кроме случая, когда обращение к памяти попадает в область, модифицированный образ которой находится в кэше другого процессора. В этом случае, индицируемом сигналом PHITM#, ему отдадут управление для выполнения обратной записи из кэша. Сигналы обычного системного арбитража (HOLD, HLDA, BOFF#) в двухпро-цессорной системе действуют обычным образом, но воспринимаются и управляются поочередно текущим владельцем локальной шины.

В конфигурации FRC два процессора выступают как один логический: функционально-избыточная пара master/checker. Основной процессор (Master) работает в обычном однопроцессорном режиме. Проверочный процессор выполняет все те же операции «про себя», не управляя шиной, и сравнивает выходные сигналы основного (проверяемого) процессора с теми сигналами, которые он генерирует сам, выполняя те же операции без выхода на шину. В случае обнаружения расхождения вырабатывается сигнал ошибки IERR, который может обрабатываться как прерывание.