Dit is het eerste deel van een serie gewijd aan programmeerbare logica en de Quartus-ontwikkelomgeving van Altera. Het legt het proces uit voor het verkrijgen van een distributiekit voor de gratis editie van de Quartus IDE. En ook het proces van het creëren van een nieuw project in deze omgeving.

Volgend deel van de serie: Altera FPGA. Deel 2: Ontwerp van digitale schakelingen.

Het tweede deel onderzoekt het proces van het toevoegen van nieuwe bestanden aan het project. Visueel ontwerp van een digitaal circuit.

Deze serie artikelen is gericht op het werken met het CTRL-CPLD-EPM570-bord op de Altera Max II-chip. Dit bord is niet strikt noodzakelijk voor een succesvolle beheersing van het materiaal, aangezien het daarin beschreven project geen gebruik maakt van de speciale kenmerken van de Max II.

Om het project in de chip te laden, wordt een goedkope programmeur gebruikt die compatibel is met Altera USB Blaster.

Stap 1. Verkrijgen van de Altera Quartus-distributie

Aandacht! In 2015 werd Altera overgenomen door Intel. Het merk Altera hield op te bestaan in juli 2018 en het websiteadres altera.com leidt nergens meer naar. De nieuwe naam van Altera is Intel Programmable Solutions Group (PSG). Alle documentatie en software die nodig is om met Altera FPGA's te werken, is nu beschikbaar op intel.com

Om projecten voor de Altera FPGA te maken, wordt een eigen IDE gebruikt: Quartus. Er zijn talloze versies van Quartus, en je moet de juiste kiezen voor de bestaande chip. Altera verwijdert regelmatig de ondersteuning voor oudere chips uit nieuwe versies van haar software. Nieuwe versies van Quartus veranderen op hun beurt de vereisten voor computersoftware en hardware. Quartus 13.1 is bijvoorbeeld de nieuwste versie die zowel op 64-bit als op 32-bit systemen werkt.

Deze serie artikelen is gericht op Quartus versie 13.1. Omdat het enerzijds geen speciale eisen stelt aan de bitheid van het besturingssysteem. Aan de andere kant ondersteunt het chips uit de MAX II-serie.

Om de Quartus-distributie te verkrijgen, moet u een account hebben op intel.com of intel.ru. Helaas is de registratieprocedure op de Intel-website momenteel (in december 2018) enigszins moeilijk. Het inschrijfformulier is niet gemakkelijk te vinden. Het is alleen toegankelijk in de laatste fase van het laden van de distributie. Tijdens het registratieproces moet u ook een geldig e-mailadres en mobiel telefoonnummer opgeven en een complex wachtwoord bedenken.

Terwijl het actieve fusieproces tussen Intel en Altera aan de gang is, is het beter om bronnen van derden te gebruiken om Quartus te downloaden. De distributie is openbaar beschikbaar op de Yandex-schijf, downloadlink: https://yadi.sk/d/bcrz7IAAKY6dQg

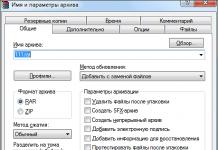

Om met de MAX II-chip te werken heb je Quartus zelf nodig, en een pakket ter ondersteuning van MAX II en MAX V. Dit zijn de bestanden “ QuartusSetupWeb-13.1.0.162.exe" En " max_web-13.1.0.162.qdz"respectievelijk.

Aan het einde van het artikel is een oude versie van instructies voor het downloaden van de distributie beschikbaar: . Je kunt het gebruiken om een globaal idee te krijgen van hoe je de distributie kunt downloaden van de Intel-website, aangezien de Intel-website Software Selector van Altera gebruikt. En net als Altera leidt Software Selector de gebruiker door naar de inlogpagina wanneer hij een bestand probeert te downloaden, als de gebruiker nog niet eerder met zijn account op de site heeft ingelogd.

Deze inlogpagina is de enige plaats die een link bevat naar het registratieformulier op de Intel-website. Registratielinks bevinden zich aan de rechterkant van de pagina. Voor gewone gebruikers kunt u de link “Registreer nu voor een individueel account” gebruiken. De link is aangegeven op onderstaande afbeelding.

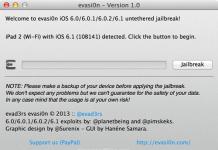

Stap 2: Installeer Quartus II Web Edition 13.1

De installatie van de Quartus II CAD-software kent geen verrassingen en volgt het beproefde “Next → Next → Finish”-algoritme.

Het is niet nodig om de installatie-instellingen te wijzigen. In het volgende wordt ervan uitgegaan dat Quartus II met standaardinstellingen is geïnstalleerd.

Zodra de installatie is voltooid, wordt de Quartus-omgeving automatisch gestart. Deze autorun is standaard ingeschakeld.

Wanneer u Quartus CAD voor het eerst start, wordt u gevraagd om het verzenden van telemetrie naar Altera (hier TalkBack genoemd) te configureren en een licentietype te selecteren.

Het in- of uitschakelen van “TalkBack” wordt ingesteld door het selectievakje “Verzenden van TalkBack-gegevens naar Altera inschakelen” aan te vinken, dat ook beschikbaar is na het installeren van Quartus via het menu Extra → Opties → Internetverbinding → knop “TalkBack-opties...”.

Wanneer u om een licentietype wordt gevraagd, selecteert u eenvoudigweg de tweede optie: “Voer de Quartus II-software uit.” Op deze manier selecteert u een gratis licentie.

Op dit punt is de installatie en initiële configuratie van de software voltooid en kunt u doorgaan met het maken van uw eerste project.

Stap 3. Quartus II - het eerste project maken

Maak eerst een map voor het nieuwe project. Noem het "eerste project".

Aandacht! Het pad naar de projectmap mag geen Cyrillische tekens bevatten! Quartus II 15 en 13 versies hebben problemen met Cyrillische ondersteuning. Andere versies zijn niet getest.

Start nu Quartus II. Wanneer u een vers geïnstalleerde Quartus II start, wordt u begroet door een venster dat lijkt op het onderstaande venster.

Om een nieuw project aan te maken, gebruikt u de wizard die beschikbaar is door op de knop “Nieuw projectwizard” te klikken of via het menu Bestand → Nieuw projectwizard.

Wanneer u de wizard start, wordt een venster weergegeven met een korte lijst met projectparameters die tijdens de wizard kunnen worden geconfigureerd.

Klik op “Volgende” en u wordt naar het venster geleid dat in de onderstaande schermafbeelding wordt weergegeven. In dit venster moet u de werkmap opgeven (“Wat is de werkmap voor dit project?”) en de naam van het gehele project (“Wat is de naam van dit project?”). En ook de naam van de hoofdmodule (“Wat is de naam van de ontwerpentiteit op het hoogste niveau voor dit project? …”).

De wizard vervangt automatisch de naam van het project door de naam van de hoofdmodule, en dit is een algemene aanbeveling voor projecten in Quartus II, waarvan u niet mag afwijken, tenzij dit echt nodig is.

Een paar woorden over de “hoofdmodule” zelf. Een Quartus II-project kan vele bestanden (modules) bevatten die verschillende functionele blokken van de ontworpen geïntegreerde schakeling beschrijven. En onder deze set valt noodzakelijkerwijs één bestand op, dat de relaties tussen alle blokken van het diagram beschrijft: de ontwerpentiteit op het hoogste niveau. Voor kleine projecten die slechts één bestand bevatten, zal dit enkele bestand ook de hoofdmodule van het project zijn.

Bij de volgende stap zal de wizard aanbieden om bestanden van eerder gemaakte projecten toe te voegen aan het nieuwe project. Omdat dit je eerste project is, ga je gewoon door naar stap drie.

De derde stap is een van de belangrijkste. Hier moet u het specifieke model van de FPGA-chip aangeven die u gebruikt. Het wizardvenster bij deze stap wordt weergegeven in de onderstaande schermafbeelding. In dit venster zijn veel parameters beschikbaar voor stapsgewijze selectie van de vereiste microschakeling uit een uitgebreide lijst met beschikbare microschakelingen. De beste plaats om te beginnen is met het blok ‘Apparaatfamilie’. Hier selecteert u de familie waartoe uw chip behoort. Het CTRL-CPLD-EPM570-bord bevat de EPM570T100C5N-chip, die tot de Max II-familie behoort.

In het blok aan de rechterkant – ‘Toon in de lijst ‘Beschikbare apparaten’’ kunt u een filter instellen om de lijst met microschakelingen te verkleinen, die zich onderaan het venster bevindt. U kunt het type chipverpakking opgeven. Het aantal pinnen van de behuizing. En ook de snelheid van de kern in conventionele eenheden. Het voorlaatste filter wordt gefilterd op de naam van de microschakeling. Het is het handigst om het te gebruiken, omdat de naam van de microschakeling al precies bekend is. Maar volgens de EPM570T100C5N-markering worden er geen microschakelingen aangeboden voor selectie. Verkort de naam tot EPM570T100C5 en selecteer de chip met deze naam uit de lijst die verschijnt als de meest compatibele chip.

Als je naar de datasheet kijkt, blijkt dat de laatste letter N in de chipmarkering alleen de afwezigheid van lood in de chipverpakking betekent. Dit feit doet er niet toe voor uw project in Quartus II, aangezien de kern van de EPM570T100C5N en EPM570T100C5 absoluut identiek is.

Ga verder naar de volgende, vierde stap - "EDA Tool-instellingen". Hier kunt u de integratie instellen met verschillende CAD-tools van derden die worden gebruikt door professionele chipontwerpers. Omdat het doel van dit artikel is om u te helpen Quartus II CAD onder de knie te krijgen, en niet een heel pakket aan applicaties die vele duizenden dollars kosten, kunt u gewoon doorgaan naar de laatste stap.

In de laatste stap wordt een algemene lijst met parameters voor uw nieuwe project weergegeven. Controleer of parameters zoals de naam en werkmap van het project, de ontwerpentiteit op het hoogste niveau en de markering van de gebruikte chip correct zijn ingesteld. Klik vervolgens op de knop “Voltooien”. Dat is alles! Het project is gemaakt.

Het is u misschien opgevallen dat u vanaf de eerste stap van de wizard op de knop “Voltooien” kunt klikken. En u kunt er al in de eerste stap op klikken, waarbij u alleen de werkmap, de naam van het project en de hoofdmodule opgeeft. Alleen deze informatie is absoluut noodzakelijk om een nieuw project aan te maken. Alle andere parameters zijn op elk moment beschikbaar voor configuratie via het hoofdmenu van het programma. Om dus meer bestanden aan uw project toe te voegen (tweede stap van de wizard), gebruikt u het menu Project → Bestanden toevoegen/verwijderen in project. Om het model van de chip waarvoor het project wordt aangemaakt (de derde stap van de wizard) te selecteren of te wijzigen, gebruikt u het menu Toewijzingen → Apparaat. Integratie met aanvullende ontwikkeltools (de voorlaatste stap van de wizard) is Opdrachten → Instellingen → EDA Tool-instellingen.

Over het algemeen worden alle projectinstellingen verzameld in een venster, waarvan de weergave wordt weergegeven in de onderstaande schermafbeelding. Het venster wordt opgeroepen via het menu Toewijzingen → Instellingen.

Het item Bestanden – dit is het venster dat wordt opgeroepen vanuit het hoofdmenu van het programma (Project → Bestanden toevoegen/verwijderen in project). EDA Tool-instellingen – vergelijkbaar. De keuze van de microschakeling is beschikbaar via de knop "Apparaat..." in de rechterbovenhoek van het venster met projectinstellingen.

Hiermee is het eerste deel van het artikel afgesloten over training in het werken met FPGA's van Intel (Altera).

(Archief) Het verkrijgen van de Altera Quartus-distributie

Om de Quartus-distributie te verkrijgen, logt u in op uw account myAltera op altera.com: knop “LOG IN” in de rechterbovenhoek van de site, naast de zoekbalk.

Heeft u nog geen myAltera-account, dan kunt u deze eenvoudig aanmaken door helemaal onderaan het registratieformulier op de link ‘Heeft u nog geen account? Creëer er een."

Eenmaal ingelogd op myAltera, ga naar downloadcentrum van de site. Link op het moment van schrijven: https://www.altera.com/downloads/download-center.html

Als de link niet werkt, ga dan naar het downloadcentrum via de startpagina van uw account. Om dit te doen, selecteert u het gedeelte "ONDERSTEUNING" en volgt u daarin de link "Downloads", die u naar het downloadcentrum brengt.

Het downloadcentrum heeft directe links om de nieuwste versie van Quartus in verschillende edities te downloaden. Hieronder vindt u het blok “Software Selector”, blader er op de pagina naartoe.

Het downloadcentrum heeft directe links om de nieuwste versie van Quartus in verschillende edities te downloaden. Hieronder vindt u het blok “Software Selector”, blader er op de pagina naartoe.

In Softwarekiezer Er zijn verschillende manieren om te selecteren wat u nodig heeft Quartus-distributie, tabbladen: “Select by Version” (directe selectie volgens de vereiste softwareversie), “Select by Device” ( het selecteren van een softwareversie op basis van ondersteuning voor een specifieke chip), Selecteer op software ( selectie van softwareproducten bij zijn naam).

In Softwarekiezer Er zijn verschillende manieren om te selecteren wat u nodig heeft Quartus-distributie, tabbladen: “Select by Version” (directe selectie volgens de vereiste softwareversie), “Select by Device” ( het selecteren van een softwareversie op basis van ondersteuning voor een specifieke chip), Selecteer op software ( selectie van softwareproducten bij zijn naam).

De handigste optie lijkt de keuze te zijn op basis van de beschikbaarheid van ondersteuning voor de bestaande microschakeling.

Als er bijvoorbeeld een microschakeling wordt gebruikt AlteraMax II dan moet je het tabblad “ Selecteer op apparaat", en in het blok "Apparaten". » artikel uitbreiden « MAX-serie". IN selecteer uit de lijst die verschijnt Maximaal II.

Rechts van het blok Apparaten worden weergegeven lijst met edities en versies van Quartus die ondersteuning bieden Maximaal II. De gratis versie is alleen de webeditie.

Rechts van het blok Apparaten worden weergegeven lijst met edities en versies van Quartus die ondersteuning bieden Maximaal II. De gratis versie is alleen de webeditie.

Let er bij het kiezen van een versie op dat Quartus II vanaf versie 14.0 alleen werkt op 64-bit systemen. Om deze reden raad ik aan om Quartus II 13.1 te kiezen. Vervolgens wordt specifiek voor de dertiende het werk- en installatieproces beschrevenversies.

Nadat u de versie hebt geselecteerd, wordt u naar de pagina met downloadopties voor de Quartus II Web Edition-distributie geleid.

"Besturingssysteem" - Windows.

"Downloadmethode" kies naar eigen goeddunken. Verschil"Akamai DLM3 Download Manager" van "Direct downloaden" is dat u in het eerste geval, voordat u de bestanden van Quartus zelf downloadt, eerst een extra applicatie onder Windows OS moet downloaden en uitvoeren.Met deze applicatie kunt u meerdere bestanden tegelijkertijd selecteren om te downloaden, en wordt ook het hervatten ervan ondersteund. Wanneer u de downloadmodus “Direct downloaden” selecteert, kunnen bestanden afzonderlijk worden gedownload, elk met behulp van een eigen link, met behulp van een webbrowser.

In de bovenstaande schermafbeelding is de downloadoptie “Direct downloaden” geselecteerd.

Download de bestanden "Quartus II Software" en "MAX II, MAX V apparaatondersteuning". Dit is het minimum dat nodig is om met de MAX II-chip te werken.

INVOERING

Als iemand een functionerend bord ziet, stellen ze meestal altijd dezelfde vragen: - Is dit een Arduino? - Hoe werkt het zonder Arduino?

Het is geen microcontroller, het is niet eens een processor, het is een FPGA. FPGA is een programmeerbaar logisch geïntegreerd circuit Zo'n microschakeling bestaat uit veel identieke blokken of macrocellen, elke fabrikant noemt ze anders, dus voor Xilinx zijn het Slices (slices) voor Altera - LogicElements (logische elementen). Deze blokken zijn relatief eenvoudig, ze kunnen fungeren als verschillende logische elementen, een kleine opzoektabel (LUT) zijn, een kant-en-klaar optel-, vermenigvuldiger-, digitaal signaalverwerkingsblok (DSP) bevatten, in het algemeen alles wat de fabrikant in gedachten heeft . De gebruiker kan deze blokken naar wens rangschikken en configureren, waardoor vrij complexe digitale circuits worden geïmplementeerd. Je kunt zelfs een microcontroller op een FPGA implementeren, bijvoorbeeld door dezelfde Arduino te implementeren of een processor van je eigen architectuur, bijvoorbeeld geen registerprocessor maar een stackprocessor, je kunt zelfs je eigen FPGA op een FPGA implementeren!

Onder de beschikbare budget-FPGA's kunnen twee belangrijke fabrikanten worden geïdentificeerd: Altera en Xilinx; met hun producten kunt u beginnen aan uw reis om deze technologieën onder de knie te krijgen. Naar mijn mening is het beter om voor Altera-chips te kiezen, aangezien hun ontwerpomgeving voortdurend wordt bijgewerkt, en als je voor één populaire Xilinx XC3S500E-chip kiest, zul je genoegen moeten nemen met de verouderde ISE 14.7-omgeving (hoewel deze ook zijn voordelen heeft) .

In de buitenlandse literatuur vind je afkortingen voor FPGA’s: FPGA en CPLD. CPLD (Complex Programmable Logic Device) - chips met een klein aantal macrocellen, gespecialiseerde blokken en een laag stroomverbruik. Voor dit type chip kan geen groot project worden gesynthetiseerd, maar in de praktijk worden ze ook gebruikt: een zeldzame microcontroller heeft bijvoorbeeld 300 poten. Dergelijke chips worden vaak gebruikt als interfacesystemen, preprocessors en I/O-expanders. FPGA (Field-Programmable Gate Array) is een field-programmable gate array (FPGA), veel krachtigere chips vergeleken met CPLD, maar verbruikt meer stroom en kost aanzienlijk meer. Om de kosten van het chipoppervlak te verlagen, kunnen FPGA-chips kant-en-klare functies bevatten, zoals digitale signaalverwerkingseenheden (DSP-eenheden), ingebedde processors en ingebed geheugen. FPGA's worden veel gebruikt voor het testen en verifiëren van ontwerpen, in de zogenaamde pre-siliciumvalidatie, waardoor de kosten en de tijd vóór de productrelease worden verlaagd. FPGA-chips kunnen op vrijwel elk moment opnieuw worden geconfigureerd; momenteel zijn er ontwikkelingen gaande, bijvoorbeeld bij Intel, om de architecturen van een conventionele processor en een FPGA-chip te combineren. Xilinx heeft dergelijke oplossingen al - Zynq, maar daar zullen we voorlopig niet over praten.

We zullen het over eenvoudigere dingen hebben, vooral sinds ik een ontwikkelingskit in handen heb gekregen: Cyclone IV 4 FPGA Core Board en Altera USB Blaster Downloader PLD Development kit voor $ 35, gekocht op AliExpress.

1 Demobord Cyclone IV 4 FPGA Core Board, korte beschrijving

Rijst. 1 - Demobetaling Cyclone IV 4 FPGA-kernbord

Op het bord (Fig. 1) is een EP4CE6E22C8N-chip geïnstalleerd, de kenmerken ervan:

| Brontype | Korte beschrijving | Hoeveelheid |

|---|---|---|

| Logische elementen (Les) | Het aantal logische blokken - cellen, het belangrijkste kenmerk waarmee we de "kracht" van chips kunnen vergelijken; elke gesynthetiseerde logica zal deze blokken gebruiken | 6,272 |

| Ingebed geheugen (Kbits) | Ingebouwd geheugen is voor ons nog geen belangrijk kenmerk | 270 |

| Ingebouwde 18x18 vermenigvuldigers | Ingebouwde hardwarevermenigvuldigers, een zeer belangrijke parameter bij digitale signaalverwerking; de volledige kracht van FPGA's komt tot uiting wanneer meerdere vermenigvuldigers parallel werken | 15 |

| PLL's voor algemeen gebruik | Phase-locked loop-knooppunten, nog geen belangrijk kenmerk, vereenvoudigen de synchronisatie van apparaten die op verschillende frequenties werken | 2 |

| Mondiale kloknetwerken | Het aantal frequentiedomeinen is nog geen belangrijk kenmerk | 10 |

| Gebruikers-I/O-banken | Het aantal afzonderlijke gebruikers-I/O-banken is nog geen belangrijk kenmerk | 8 |

| Maximale gebruikers-I/O | Aantal aangepaste I/O-pinnen, we kunnen elk apparaat aansluiten, zoals Arduino | 91 |

Het bestuur heeft:

- Flash-geheugen – Wanneer de stroom wordt ingeschakeld, wordt de FPGA geconfigureerd om in flash-geheugen te worden geïmplementeerd. U kunt uw project synthetiseren en in deze flitser schrijven

- 25 MHz kwarts is eenr, het is op deze frequentie dat al onze projecten zullen werken, onze FPGA kan maximaal 10 van dergelijke kanalen ondersteunen.

- LED's – 10, knoppen – 2.

- I/O-pinnen 61 + 2 aarde, 1 niet aangesloten. Je kunt allerlei apparaten aansluiten. DAC-ADC, versnellingsmeters en gyroscopen, karakter- en grafische displays, zoals Arduino.

- Voeding via USB, of externe 5V.

De kit bevat ook een JTAG-programmeur, Altera USB Blaster.

2. Quartus II-omgeving en ons eerste project

Om met deze FPGA te kunnen werken, moeten we de officiële ontwikkelomgeving downloaden - Quartus II webeditie, het is gratis. We gaan naar de officiële website http://dl.altera.com/15.0/?edition=web, op het moment van schrijven is versie 15.0 de nieuwste, als deze nieuwer is, download deze dan.

Kiezen:

Rijst. 2 - selecteer de benodigde Altera-producten

En klik op de downloadknop (Geselecteerde bestanden downloaden). Hierna wordt ons gevraagd om te registreren, registreren, downloaden en installeren.

Laten we ons eerste project maken.

Start Quartus, selecteer het hoofdmenu Bestand -> Nieuwe projectwizard, het introductievenster verschijnt, klik op Volgende. Vervolgens moet u de map voor het project en de naam ervan opgeven. Het derde veld is de naam van de bovenste module, u zult later zien wat het is. We selecteren de map waarin we het project willen opslaan en bedenken een naam, ik heb test1.

Rijst. 3 - nieuw projectwizardvenster

Klik op volgende, er wordt gevraagd of het een leeg project of een projectsjabloon is. Laat leeg, volgende. Vervolgens wordt ons gevraagd bestaande bestanden toe te voegen, we hebben niets, aangezien we nog maar net aan onze reis zijn begonnen, klik je op Volgende.

Vervolgens moeten we onze chip selecteren; dit kan op elk moment worden gedaan. We selecteren zoals in de figuur, Familie – Cycloon IV E, een specifiek apparaat geselecteerd in "Beschikbare apparaten" en selecteren onze EP4CE6E22C8N-chip, dit staat helemaal aan het begin. Als je er nog een hebt, zoek dan de jouwe, Het is belangrijk. Klik volgende.

Rijst. 4 -

Er verschijnt een venster waarin u ontwerptools kunt selecteren, fouten kunt opsporen. Sla dit voorlopig over, klik op Volgende en voltooi vervolgens.

Rijst. 5 - Venster "Assinments-Deice"

Selecteer in het venster het item "Ongebruikte pinnen". Deze instelling bepaalt wat er gebeurt met niet-verbonden pinnen. Dit kan belangrijk zijn; in uw project is het onwaarschijnlijk dat u alle pinnen gebruikt, en de pinnen die niet zijn aangesloten, zijn mogelijk in feite verbonden met aarde of stroom (nou ja, u weet nooit wie het bord heeft aangesloten). Als u er een op een geaarde pin aanbrengt, zal deze doorbranden, dus u moet dit zorgvuldig in de gaten houden.

Standaard zijn de ongebruikte pinnen “Als input tri-stated met zwakke pull-up” (input-pinnen bevinden zich in de derde staat met hoge impedantie, met een zwakke power pull-up), je kunt “Als input tri-stated” laten staan of selecteren ”. Je kunt over de pull-up-weerstand lezen op Wikipedia https://ru.wikipedia.org/wiki/Pull-up_resistor. In de digitale technologie kunnen er drie toestanden zijn: een logische is de voedingsspanning of een hoog niveau, een logische nul is wanneer de pin is verbonden met aarde of een laag niveau en een hoge impedantie. Hoge impedantie- dit is wanneer een pin een zeer hoge weerstand heeft en praktisch geen invloed heeft op de draad waarmee hij is verbonden; deze toestand is bijvoorbeeld nodig bij het organiseren van bussen, wanneer veel apparaten op één draad zijn aangesloten en inactieve apparaten niet interfereren met bediening.

Rijst. 6 - Venster “Apparaat- en pinopties”, Ongebruikte pinnen

We verbinden het allemaal in de “Assignment Editor”

Rijst. 7 - Roep “Toewijzingseditor” op vanuit het menu of paneel

In het venster dat verschijnt, doe je het zoals ik deed, of, als het absoluut correct is, dan volgens het diagram van je bord.

Rijst. 8 - Assinement-editor

Voer in de kolom “Aan” de naam van de in- of uitgang in. Selecteer in de kolom 'Toewijzingsnaam' de optie 'Locatie'. In de kolom "Waarde" staat het pinnummer van de microschakeling, volgens het borddiagram (ik heb pinnummers rechtstreeks op het bord geschreven).

Ook moet je opgeven wat je met de knoppen moet doen, die met één poot met de grond verbonden zijn en met de andere met de ingang van de chip. Als je op het been drukt, zal er een laag niveau zijn, maar zonder te drukken is het onduidelijk, het been van de chip hangt gewoon in de lucht, wat erg slecht is. Je moet de chipingang op de voeding aansluiten met een weerstand op het bord of op een elegantere manier in de “Assignments Editor”. In de kolom “Toewijzingsnaam” selecteert u “Zwakke Pull Up-weerstand” voor de toetsgroep* (de groep wordt aangegeven met een asterisk).

Rijst. 9 - Toewijzingseditor

Vervolgens moet u een beschrijving maken van de module op het hoogste niveau, die rechtstreeks met de chippoten zal werken; alle andere modules zullen er alleen mee werken. Klik in het hoofdmenu op Nieuw en selecteer "Ontwerpbestanden-> Blokdiagram/Schematisch bestand".

Rijst. 10 - Dialoogvenster Nieuwe bestanden

In het geopende venster selecteert u de “Pin Tool” en plaatst u de invoer en uitvoer (invoer- en uitvoerpinnen) op het diagram. We hernoemen de ingang naar sleutel, de uitgang naar led en verbinden deze met een geleider. Sla op en klik op "Compilatie starten".

Rijst. 11 - Grafisch beschrijvingsvenster, Pin Tool en Start compilatie gemarkeerd

Na de compilatie kregen we waarschuwingen, die we voorlopig negeren, deze hebben betrekking op niet-verbonden pinnen, de afwezigheid van een kloksignaal en de beschrijving voor de “Timing Analyzer”.

We verbinden het demobord en de programmeur en selecteren de tool "Programmer". Het venster zou "USB-Blaster" moeten zeggen, zo niet, klik dan op "Hardware Setup" en probeer uit te vinden waarom niet, hoogstwaarschijnlijk zijn de stuurprogramma's niet geïnstalleerd, kijk naar Windows-apparaten, zoek naar niet-geïdentificeerde apparaten, misschien is er een probleem met de kabel. Als alles in orde is, klik je op “Auto Detect” en selecteer je onze chip.

Rijst. 12 - Programmeervenster

Dubbelklik in het veld "Bestand" en selecteer het bestand dat u naar de FPGA wilt schrijven (in de map output_files van ons project), vink het veld "Programma / Configureren" aan en klik op de knop "Start".

Rijst. 13 - Programmeervenster, onze chip is al geconfigureerd

Gefeliciteerd met uw eerste FPGA-configuratie! Diode D1 zou moeten oplichten, als je op toets 1 drukt zou deze uit moeten gaan (aangezien de knop de poot naar de grond sluit), dan gaan we er iets aan doen)

(C) Onderzoek/VolgaSoft Moderne technologieën. ALTERA.(inleidend materiaal) INVOERING Dit artikel gaat over een modern klein wonder, een berekende doorbraak in de wereld van digitale elektronica: programmeerbare logica-chips. Dit is de steen die in de modernste modellen staat ZX-SPECTRUM - GMX en SPRINTER , dit is dezelfde microschakeling waarop je bijna alles kunt doen - van Z80X (laten we zeggen, 30 MHz, machinecyclus 1 klokcyclus), tot alles Pentagon samen met een 2D-versneller, GS, muis en IDE-controller. Waarschijnlijk droomde elke radioamateur bij het ontwikkelen van een digitaal apparaat in zijn hart - waar hij een pil voor alle ziekten kon vinden - een microschakeling die alles zou vervangen. Ingenieurs hadden dergelijke apparaten vooral nodig, omdat ze bij het ontwikkelen van een serieus product een op maat gemaakt geïntegreerd circuit moesten ontwerpen ‘voor de taak’. Vanaf het moment dat de logica werd opgesteld totdat het werkende product verscheen, gingen er meestal enkele maanden voorbij en werd er een enorme hoeveelheid middelen uitgegeven. Maar de vraag schept aanbod: er zijn semi-aangepaste grootschalige geïntegreerde schakelingen (LSI) en programmeerbare logische arrays (PLA) verschenen. De wetenschap stond niet stil, technologieën werden steeds geavanceerder en op een dag werd de release aangekondigd van een pakket “software” + “hardware” + “steen”. Het idee was heel eenvoudig: de ontwikkelaar tekent een diagram in de software (zet het misschien over van papier), of beschrijft de logica van het toekomstige product met binaire vergelijkingen en eenvoudige operatoren, vervolgens vertaalt de compiler het diagram in een code, en de code wordt door een programmeur (“hardware”) samengevoegd tot een programmeerbare logica-chip (“stone”), die onmiddellijk op het bord kan worden gesoldeerd. En er zijn geen kosten verbonden aan het ontwikkelen of testen van de chip. Ontwikkelaars van digitale apparaten omarmden het nieuwe product met een knal. Tegenwoordig zijn er veel fabrikanten van LSI programmeerbare logica (PL) op de markt. Hun producten verschillen zowel qua capaciteit en architectuur, als qua kwaliteit van software- en hardwareondersteuning, service en uiteindelijk de kosten. De duidelijke leider van vandaag is het bedrijf Altera Corporation . Het veroverde de markt niet alleen dankzij het brede productassortiment, maar ook dankzij de competente distributie van zijn producten. Zo is het gebruik van softwareproducten (studentenversies) voor educatieve doeleinden gratis. Voor Rusland is het over het algemeen niet belangrijk (bijna niemand heeft ooit de auteursrechtwet gezien), maar in het buitenland is deze kwestie relevant. Bovendien braken de producten van het bedrijf letterlijk door op de binnenlandse markt - als gevolg daarvan zijn we er nu bijna allemaal mee bezig. VAN WOORDEN NAAR ACTIE VLSI PL van Altera geclassificeerd volgens de volgende criteria: 1) mate van integratie (aantal beschikbare poorten (2I-NOT-elementen) en flip-flops); 2) architectuur van de eenvoudigste functionele converter (cel); 3) organisatie van de interne structuur van VLSI en de structuur van de matrix van verbindingen van functionele converters (methode voor het verbinden van cellen); 4) de aanwezigheid van intern RAM-geheugen; 5) technologie voor het vervaardigen van een programmeerbaar element (Fuse, EPROM, EEPROM, FLASH, SRAM) - hoe het circuit is bedraad. Om samen te werken met het grootste deel van zijn BIS PL-bedrijf Altera biedt de hardwarebeschrijvingstaal MAX+plus II. Het MAX+plus II ontwerpautomatiseringssysteem ondersteunt zes families van VLSI PL.┌─────────┬──────────────────────┐ │ │ Parameters │ │ ├────────── ┬─────┬─────┤ │Family│Logic│UPin │Tech │ │ │ capaciteit │ │ │ │ │ │ │ │ ├─── ─ ─────┼────── ────┼─────┼─────┤ │Klassiek │ 300-900 │22-64│EPROM│ │MAX5000 │ 600-3750 │24-84│EPRO M │ │MAX7000E │ 600-5000 │ tot 164│EEP- │ │MAX9000 │ 6e3-12e3 │tot 216│ROM │ │FLEX8000A│ 2500-16e3│tot 208│SRAM │ │FLEX10K │ 1e4-1e5 │ tot 406 │SRAM │ └── ───────┴─ ─────────┴─────┴─────┘De logische capaciteit is het aantal beschikbare 2I-NOT-elementen, dat wil zeggen dat er maximaal 25.000 van onze LA3's in de FLEX10K passen. UPin - aantal gebruikerspinnen. Technologie - technologie. Praktische uitleg voor de tabel: laten we zeggen dat we de meest dodelijke FLEX8000A nemen (SRAM-technologie - d.w.z. na het inschakelen van de stroom moet het circuit van het apparaat in de dynamo worden "gegoten") en deze met de voeten van de gebruiker op de Rodimigo-bus hangen Speccy (er zijn er nog een paar vrij), we maken in bulk een eenvoudige poortdecoder en sluiten deze aan op de alterina-ingang. Wat krijgen we? We krijgen een superapparaat!!! Je kunt nu immers vrijwel elk plan in een alter gieten!!! Het kan van alles zijn, van een externe mat. processor (laten we zeggen dat we een 16-bits getal byte voor byte in de ene poort stoppen, het tweede getal in een andere, de bewerkingscode ergens anders, en dan het resultaat lezen), tot alles wat begrijpelijk is voor de geest (als je een paar vrije benen "waar zou moeten" - je kunt hardware-vulling en hardware-constructie van segmenten maken, meerkanaals programmeerbare interrupts (vooral relevant voor digitale audio), nieuwe processoropdrachten (zoals in"sprinter" of extra processorregisters...). Je kunt bibliotheken met hardwarefuncties creëren om geen grote te verzinnen, zoals hardnekkige 'codeerders' nog steeds doen, en deze lezen in overeenstemming met de taak. De “firmware” van het circuit van dezelfde FLEX8282A (“de dodelijkste”, zie hierboven) weegt, als ik me goed herinner, 6 kB. Tijdens de configuratie bevinden alle gebruikersbenen zich in de Z-status en hebben ze geen invloed op de werking van het systeem. Als u ervoor wilt zorgen dat een apparaat “eeuwig meegaat” en het niet telkens opnieuw configureert nadat u het hebt ingeschakeld, kunt u de MAX-familie gebruiken. Ook hebben sommige LSI's van de MAX-familie bescherming tegen "circuitlekkage" - een beetje ontwikkelingsgeheim, maar naar mijn mening is het gebruik van deze familie enigszins beperkt (althans in "thuis" -omstandigheden) vanwege de behoefte aan programmeur en een beperkt aantal programmeercycli.NU EEN PAAR WOORDEN OVER DE ONTWIKKELINGSOMGEVING: HARDWARE BESCHRIJVING TAAL MAX + PLUS II.Het MAX+plus II-systeem is geschreven voor de volgende platforms: PC, MAC, ZON. Geen Speccy Om de een of andere reden stond zelfs de beruchte vriendin niet op deze lijst. Het systeem is zeer goed, eenvoudig en met ruime mogelijkheden. De belangrijkste componenten zijn grafische en teksteditors, een compiler, een diagrameditor (ook wel een “debugger” genoemd), een timer en een lay-out- en lay-outeditor. In de grafische editor wordt een diagram van het apparaat getekend (als een grafische taak wordt gebruikt). Als elementen van het schema kun je de logica gebruiken ‘volgens de burgerlijke gast’, de hele 74e serie is er, en als je de aanduidingen van de vijand niet leuk vindt, kun je alles op onze manier tekenen en laten werken. Er wordt een teksteditor gebruikt om een tekstbeschrijving van de hardware te geven. De taal zit er ergens tussenin dBase, C, Pascal . Er bestaat bijna een kant-en-klaar commando voor het beschrijven van een synchrone eindige toestandsmachine, en dat is er ook als en geval . De opteller wordt letterlijk beschreven als C=A+B . Een telefoonchipkaart wordt in een uur zonder inspanning beschreven en getest (zie hieronder). De compiler controleert het schema (of de tekst) en genereert firmware voor de gegeven “steen”. Dankzij de breed instelbare optimalisatielimieten voor snelheid en volume kunt u de maximale prestaties uit het apparaat of het minimaal bezette gebied op de chip halen. Er is iets nuttigs ontworpen door de dokter. Laat zien waar er races en gevaarlijke plaatsen zijn, en onder welke omstandigheden ze zullen verschijnen, vergeet niet te vragen om op reset te drukken om het apparaat te initialiseren nadat het is ingeschakeld, enz. In de diagrameditor kun je de werking van het toekomstige apparaat simuleren: stel dat je de ingangssignalen instelt en naar de bijbehorende uitgangen kijkt; de races vergeten ook niet te worden weergegeven. Daarom is het beter om, voordat u het circuit monteert, het op "max" te laten draaien en het te controleren. Toegegeven, er was ook een bug - de T-trigger was gemaakt R.S. , gesynchroniseerd door het verschil, hoewel het in de praktijk ploegde. Het bekijken van diagrammen is heel gemakkelijk gemaakt: u kunt diagrammen bekijken door ze in groepen te combineren en een gemakkelijk te bekijken getalsysteem te presenteren (binair, decimaal, hexadecimaal). Invoergegevens kunnen ook per code worden gespecificeerd Grijs . U kunt ook de interne status van de machine bekijken. De timer - het is ook een timer in Afrika - geeft vertragingen en de maximaal mogelijke werkfrequentie van het apparaat weer. De lay-out- en lay-outeditor wordt gebruikt voor het “hardware” verwijderen van races (herschikking van logische cellen) en het plaatsen van aangepaste pinnen. Distributeur prijs Altera Helaas ben ik hem kwijtgeraakt, dus ik kan alleen maar uit mijn hoofd zeggen dat de FLEX10K10 vanaf $20 kost, de FLEX8282A vanaf $8, en elementen van de MAX-familie vanaf $3,3 kosten. Als u geïnteresseerd bent waar u informatie kunt krijgen, kunt u naar het einde van het artikel scrollen, want verdere informatie volgt.MEER INFORMATIE OVER FAMILIES De Classic-familie omvat 3 series VLSI. LSI's van deze familie maken het mogelijk een apparaat te vervangen dat 10 tot 20 microcircuits met een gemiddelde mate van integratie bevat, en bieden: * signaalvoortplantingsvertraging van elke invoer en uitvoer van de LSI van niet meer dan 10 ns; * stabiele werking bij frequenties tot 100 MHz; * mogelijkheid om te werken in een modus met laag energieverbruik; * de mogelijkheid om de ontwikkelingsgeheimmodus in te stellen (het circuit kan niet worden samengevoegd vanuit de mikruhi). Let op: het lijkt erop dat ze al zijn stopgezet. De MAX5000-familie omvat 5 series VLSI. LSI's uit deze familie maken het mogelijk om een apparaat met tientallen microschakelingen met een gemiddelde mate van integratie te vervangen, en zorgen voor: * een vertraging in de signaalvoortplanting van elke in- en uitgang van de LSI van niet meer dan 15 ns; * stabiele werking bij frequenties tot 76 MHz; * mogelijkheid om de ontwikkelingsgeheimmodus in te stellen; * de mogelijkheid om drie bedrijfsmodi van uitvoerbuffers te gebruiken: invoer, uitvoer, bidirectioneel. De MAX7000-familie omvat 7 series VLSI. LSI's uit deze familie maken het mogelijk om een apparaat met maximaal honderden microschakelingen met een gemiddelde mate van integratie te vervangen, en bieden: * signaalvoortplantingsvertraging van elke ingang naar de uitgang van de LSI, niet meer dan 5 ns; * stabiele werking bij frequenties tot 178 MHz; * mogelijkheid om de snelheid van schakeluitgangsbuffers te regelen; * mogelijkheid om 4 bedrijfsmodi van uitgangsbuffers te gebruiken: ingang, uitgang, bidirectioneel, open collector; * de mogelijkheid om een modus met laag energieverbruik in te stellen, zowel voor de gehele VLSI als geheel als voor de voortplantingscircuits van individuele signalen; * mogelijkheid tot programmeren en herprogrammeren na bedrading op het bord; * mogelijkheid om de ontwikkelingsgeheimmodus in te stellen; * werken met verlaagde (3,3 V) voedingsspanning. Let op: een aantal series voldoen aan de PCI-busstandaard. De FLEX8000A-familie omvat 7 series VLSI. LSI's uit deze familie maken het mogelijk om een apparaat te vervangen dat tientallen platen in beslag neemt die zijn gemaakt op microcircuits met een gemiddelde mate van integratie, en bieden de mogelijkheid om: * stabiele werking bij frequenties tot 294 MHz; * emulatie van een interne bus met 3 statussen; * werken met verlaagde (3,3 V) voedingsspanning; * werken in systemen met gemengde (3,3 V, 5 V) voedingsspanning; * implementatie van een onbeperkt aantal configuratiecycli, inclusief “on the fly”, d.w.z. zonder de VLSI-voeding uit te schakelen; * regeling van de schakelsnelheid van uitgangsbuffers; * mogelijkheid om 3 bedrijfsmodi van uitvoerbuffers te gebruiken: invoer, uitvoer, bidirectioneel. Let op: alle VLSI's in deze serie voldoen aan de PCI-busstandaard. De MAX9000-familie omvat 4 series chips. LSI's uit deze familie maken het mogelijk om een apparaat te vervangen dat tientallen platen in beslag neemt die zijn gemaakt op microcircuits met een gemiddelde mate van integratie en bieden de mogelijkheid om: * stabiele werking bij frequenties tot 125 MHz; * onafhankelijk gebruik van het logische deel en trigger van de macrocel; * de mogelijkheid om een modus met laag energieverbruik in te stellen, zowel voor de gehele VLSI als geheel als voor de voortplantingscircuits van individuele signalen; * mogelijkheid tot programmeren en herprogrammeren na bedrading op het bord; * werken in systemen met gemengde (3,3 V, 5 V) voedingsspanning; * regeling van de schakelsnelheid van uitgangsbuffers; * gebruik van 3 bedrijfsmodi van uitvoerbuffers: invoer, uitvoer, bidirectioneel. Let op: een aantal series voldoen aan de PCI-busstandaard. De FLEX10K-familie omvat 7 series VLSI. LSI's uit deze familie maken het mogelijk om een apparaat te vervangen dat honderden borden in beslag neemt die zijn gemaakt op microcircuits met een gemiddelde mate van integratie, en bieden de mogelijkheid om: * stabiele werking bij frequenties tot 450 MHz; * on-chip implementatie van statisch geheugen en ROM met een capaciteit tot 24 Kbit; * onafhankelijk gebruik van het logische deel en trigger van elk logisch element; * emulatie van een interne bus met 3 statussen; * vermenigvuldigen van de interne klokfrequentie; * werken in systemen met gemengde (3,3 V, 5 V) voedingsspanning; * implementatie van een onbeperkt aantal configuratiecycli, inclusief “on the fly”, d.w.z. zonder de VLSI-voeding uit te schakelen; * regeling van de schakelsnelheid van uitgangsbuffers; * mogelijkheid om 4 bedrijfsmodi van uitgangsbuffers te gebruiken: ingang, uitgang, bidirectioneel, open collector. Let op: alle VLSI's in deze serie voldoen aan de PCI-busstandaard. Dat is het. Ik wil er alleen aan toevoegen dat de vooruitgang niet stilstaat en dat er aan elke familie meer series zijn toegevoegd. VOORKOMENS WWW.ALTERA.COM - daar kunt u meer gedetailleerde informatie en elektronische sleutels voor het MAX + Plus II-programma krijgen (als u zich voordoet als student of onderzoeker).EFO-bedrijf. E-mail: [e-mailadres beveiligd] Tel. (812) 247-5340 194021 St. Petersburg, Politekhnicheskaya st., 21(hier kunt u de bijbehorende elementen kopen).LITERATUUR 1. Herziening van de ALTERA-elementbasis (Antonov A.P., Melekhin V.F., Fillipov A.S.; St. Petersburg 1997) 2. Hetzelfde boek (alleen lijkt het groter) staat op de compact met MAX + Plus II in video.PDF (blijkbaar 45 MB), hoewel in het Engels.

ALTERA programmeerbare logische geïntegreerde schakelingen en MAX+PLUS II computerondersteund ontwerpsysteem

Programmable Logic Integrated Circuits (FPGA's), of in de buitenlandse literatuur PLD's (Programmable Logic Devices) genoemd, zijn semi-aangepaste digitale LSI's, die dankzij hun architectonische en technologische kenmerken kunnen worden ontwikkeld en vervaardigd zonder gespecialiseerde technische apparatuur. FPGA's verschenen halverwege de jaren 80 op de wereldmarkt. En ze werden onmiddellijk wijdverspreid, waardoor het proces van het creëren van een gespecialiseerde LSI van de fabriek naar de werkplek van de ontwerper werd verplaatst. De LSI-ontwikkelcyclus is teruggebracht tot enkele uren en de bijbehorende kosten zijn aanzienlijk verlaagd.

Sinds begin jaren 90. De grootste vraag is naar FPGA's die:

hoge logische integratie gebaseerd op CMOS-technologieën;

snelheid tot 80 -100 MHz en hoger;

Mogelijkheid om te programmeren (interne configuratie laden) zonder programmeur.

Aan al deze eisen wordt voldaan door FPGA’s van ALTERA (USA), een wereldleider op het gebied van FPGA’s. Momenteel produceert ALTERA zeven families van FPGA's met verschillende architecturen [14].

In Rusland zijn de bekendste FPGA's de Classic-familie, die al enige tijd door INTEL wordt geproduceerd. De belangrijkste voordelen van deze microschakelingen zijn eenvoud, lage kosten, eenvoudig te installeren DIP-pakketten, micro-energieverbruik in statische modus en de mogelijkheid om te worden ondersteund door huishoudelijke middelen (CAD FORS+, Blitz, Sterkh, Forsys-programmeurs). FPGA EP220 vervangt alle microcircuits uit de 1556-serie (HP4, HP6, HP8, XL8).

Alle FPGA's worden vervaardigd met behulp van ultraviolet-wisbare CMOS-technologie (EPROM), die de volgende energieverbruiksparameters biedt:

in statische modus - 10-30 µA;

bij een frequentie van 1 MHz - 2-8 mA;

met toenemende klokfrequentie - 1 mA/MHz.

Om de prijs bij massaproductie van producten met 30-40% te verlagen, worden alle FPGA’s ook geproduceerd in plastic verpakkingen (DIP en PLCC) met eenmalige programmering.

De nadelen van FPGA's uit de klassieke familie zijn de relatief lage mate van integratie en enkele architectonische kenmerken: het gebrek aan invoer voor triggers die op "1" (SET) moeten worden ingesteld, het blokkeren van contacten bij het implementeren van interne geheugenelementen.

FPGA's van de MAX7000- en FLASHlogic-families, die een matrixarchitectuur hebben, d.w.z. bevatten programmeerbare matrices van logische poorten "AND", "OR" en flip-flops.

De MAX7000-familie bestaat uit zeven chips met integratieniveaus variërend van 1.200 tot 10.000 equivalente logische poorten, met daarin 32 (EPM7032) tot 256 (EPM 7256) flip-flops.

Bovendien wordt FPGA EPM7032V geproduceerd - een functioneel analoog van de EPM7032-microschakeling met een voedingsspanning van 3,3 V.

De MAX7000-familie van FPGA's wordt vervaardigd met behulp van elektrisch uitwisbare CMOS-technologie (EEPROM). Ze bieden:

minimale signaalvoortplantingsvertraging van ingang naar uitgang 5 ns;

maximale klokfrequentie 190 MHz;

tot 100 programmeer-/wiscycli.

De MAX7000-familie van FPGA's heeft een flexibele architectuur. Hun macrocellen bevatten twee onafhankelijke feedbacklijnen; van de trigger en van het contact. Hierdoor kan de flip-flop tegelijkertijd als intern register worden gebruikt en kan de pin als ingangspoort worden gebruikt. Bijkomende bronnen van de FPGA zijn uitbreidingstermen - conjunctoren, waarvan de inverse uitgangen feedbackverbindingen vormen met de matrix van "EN"-elementen. Met termen kunt u besturingssignalen genereren (bijvoorbeeld CLK, SET, RESET) zonder macrocellen uit te geven. Als gevolg van de herverdeling van termen tussen macrocellen kan het aantal ingangen van de “OR”-elementen worden verhoogd tot 32.

Elke macrocel heeft een individuele turbobit, waarvan de programmering u in staat stelt het energieverbruik te verminderen met een lichte prestatievermindering. Vanaf 1996 zullen alle FPGA's uit de MAX7000-familie beschikbaar zijn in de ISP-variant (in systeemprogrammeerbaar). Hierdoor kunt u het circuit rechtstreeks op het werkbord programmeren en wissen via de 4e signaalinterface die op de computerpoort is aangesloten. De aanwezigheid van een programmeur wordt optioneel, wat de kosten van het gebruik van FPGA's aanzienlijk vereenvoudigt en verlaagt.

De MAX7000-familie van FPGA's is goedkoop. De prijs van de EPM7032-chip is bijvoorbeeld minder dan 7 en de EPM7128-chip minder dan 25.

Met de komst van de MAX7000-familie is de praktische waarde van de eerder geproduceerde FPGA’s van de MAX5000-familie aanzienlijk afgenomen, omdat Er zijn analogen van alle microschakelingen verschenen (bijvoorbeeld EPM5128 - EPM7128) met betere prestatiekenmerken en stroomverbruik tegen lagere prijzen.

MAX+PLUS II is een geautomatiseerd ontwerpsysteem voor programmeerbare logica-geïntegreerde circuits (FPGA), ontwikkeld door Altera Corporation, een wereldleider in FPGA-productie.

MAX+PLUS II is een multifunctioneel softwareproduct dat de ontwerper de mogelijkheid biedt om een FPGA volledig te ontwerpen, vanaf het invoeren van het circuit dat de ontwerper op de FPGA wil implementeren en eindigend met het programmeren van de FPGA zelf op de programmeur.

MAX+PLUS II biedt de volgende gebruikersopties:

invoer van de interne structuur van de FPGA door grafische invoer van het functionele diagram;

invoer van de interne structuur van de FPGA met behulp van de hoogwaardige programmeertaal Altera Hardware Description Language (AHDL), die volledig in de MAX+PLUS II-shell is ingebouwd;

modellering van FPGA-werking in de vorm van timingdiagrammen;

Als je een programmeur hebt, schrijf dan de ontworpen structuur naar de FPGA, enz.

Bij het beschrijven van de interne structuur van een FPGA met behulp van AHDL zijn verschillende opties mogelijk.

Beschrijf in de eerste optie de structuur in primitieven, d.w.z. met behulp van eenvoudige functies zoals RS-trigger, D-trigger, T-trigger, JK-trigger, enz.

Voer bij de tweede optie de beschrijving uit met behulp van primitieven en megafuncties.

Megafuncties zijn complexe logische functies zoals teller, multiplexer, decoder, register, enz.

Het voordeel van de eerste optie is dat de vertaler minder tijd kwijt is aan het omzetten van de eenvoudigste functies van de AHDL-taal in machinecodes.

De nadelen van deze optie zijn het grote volume aan programmatekst en de behoefte aan een gedetailleerde beschrijving van het hele systeem.

Bij de tweede optie is er bij het gebruik van megafuncties geen behoefte aan een gedetailleerde beschrijving van de elementen, in die zin dat de programmeur alleen de parameters van een complexe logische functie instelt. Met behulp van de megafunctie lpm_counter kan een teller bijvoorbeeld worden beschreven door alleen de geklokte invoer en de breedte van de teller zelf op te geven. Hierdoor wordt het volume van de programmatekst aanzienlijk verminderd en kunt u ook de tijd die nodig is om een programma te schrijven enigszins verkorten.

Het nadeel is dat het meer tijd kost om het programma in machinecodes te vertalen dan bij de eerste optie.

Maar uiteindelijk is het resultaat hetzelfde, dus de stijl van het schrijven van een softwareproduct hangt volledig af van de ontwerper.

Bij het debuggen van een geschreven softwareproduct kunt u met SIMULATOR MAX+PLUS II het resultaat van de FPGA-bewerking in detail onderzoeken in de vorm van timingdiagrammen. De ontwerper kan verschillende outputs en tussentoestanden selecteren die in het programma worden beschreven, en verschillende invoeracties specificeren.

Het eerste bedrijf dat de markt betrad met programmeerbare geïntegreerde schakelingen (FPGA's). Altera biedt twee CAD-systemen: MAX+PLUS II en Quartus II. Elk CAD-systeem ondersteunt alle ontwerpfasen: ontwerpinvoer, compilatie, verificatie en programmering. Elk CAD-systeem heeft een zelfstudie, die wordt geïnstalleerd tijdens de installatie van het pakket. De Tutorial bestaat uit lessen die u door de gehele ontwerpcyclus leiden, van ontwerpinvoer tot chipprogrammering. Tijdens de installatie worden ook bestanden geïnstalleerd die het project beschrijven, zodat u tijdens het studeren van Tutorial individuele lessen kunt overslaan en kant-en-klare bestanden kunt gebruiken. U kunt bijvoorbeeld "Projectinvoer" overslaan en het project "Compileren" met behulp van kant-en-klare bestanden.

Het MAX+PLUSII-systeem beschikt over efficiënte synthese-algoritmen die maximaal gebruik van chipbronnen mogelijk maken en een groot aantal tools voor apparaatverificatie op functioneel en timingontwerpniveau.

Het bedrijf distribueert ook gespecialiseerde Design Kits die het gebruik van FPGA's bij specifieke taken vergemakkelijken. Dergelijke kits bevatten CAD-compatibele logische functies en een methodologie om deze te gebruiken. Van belang zijn de Design Kit, gewijd aan de ontwikkeling van producten in de PCI-busstandaard en digitale signaalverwerkingscircuits. De eerste omvat sjabloonfuncties voor het implementeren van controllers (Master/Slave) en pariteitscontrolecircuits. De tweede is gericht op de efficiënte implementatie van circuits zoals vermenigvuldigers, FIR-filters, drijvende-kommabewerkingen, Fourier-transformaties, Reed-Solomon-transformaties, enz.

MAX is ontworpen om te communiceren met VHDL-, EDIF- en Verilog-standaarden. Elke CAD-configuratie importeert invoergegevens in EDIF-formaat en produceert ontwerpresultaten in alle vermelde formaten. Met behulp van vertaalprogramma's is het mogelijk om informatie in het CAD MAX-tekstbeschrijvingsformaat te importeren uit bestanden in de formaten PDS (CAD PLDShell, PALASM) en XNF (CAD XACT van Xilinx). Het is mogelijk om diagrammen die in het OrCAD-systeem zijn gemaakt, om te zetten in bestanden in het formaat van uw eigen grafische editor.

Altera biedt gratis CAD-versies MAX+PLUS II BASELINE en Quartus II Web Edition, die alle ontwerpfasen ondersteunen, van ontwerpinvoer tot programmering. Beperkingen zijn het aantal ondersteunde chips en enkele functies voor Quartus II. Gratis versies van CAD kunnen worden gedownload van de Altera-website (https://www.altera.com/support/software/download/sof-download_center.html).