В случае вычислительных и информационных систем персональный компьютер не нуждается в подключении нестандартной аппаратуры, все сводится к подбору или написанию необходимого программного обеспечения. В случае же контрольно-измерительных и управляющих систем персональный компьютер оснащается набором инструментов для сопряжения с внешними устройствами и соответствующими программными средствами. Во многих случаях строить систему на основе персонального компьютера оказывается гораздо проще, быстрее и даже дешевле, чем проектировать ее с нуля на базе какого-то микропроцессора, микропроцессорного комплекта или микроконтроллера.

Конечно, в большинстве случаев система на основе персонального компьютера оказывается сильно избыточной, это плата за универсальность. Но в то же время один и тот же компьютер может решать самые разнообразные задачи. Например, в системе управления технологическими процессами или научными установками он может математически моделировать происходящие процессы, выдавать в реальном времени управляющие сигналы, принимать в реальном времени ответные сигналы, накапливать информацию, обрабатывать ее, обмениваться информацией с другими компьютерами и т.д. Развитый интерфейс пользователя (видеомонитор, полноразмерная клавиатура, мышь) делают работу с персональным компьютером комфортной и эффективной. А стоимость персональных компьютеров вследствие большого объема выпуска постоянно снижается. Поэтому их использование не только удобно, но и экономически выгодно.

Но чтобы грамотно и полноценно использовать персональный компьютер в составе любых систем, надо иметь представление о его архитектуре, об основных принципах построения, об устройствах, входящих в его состав, наконец, о внешних интерфейсах.

7.1. Архитектура персонального компьютера

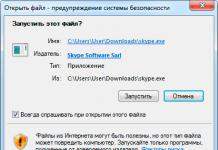

Персональный компьютер типа IBM PC имеет довольно традиционную архитектуру микропроцессорной системы и содержит все обычные функциональные узлы: процессор, постоянную и оперативную память, устройства ввода/вывода, системную шину, источник питания (рис.7.1). Основные особенности архитектуры персональных компьютеров сводятся к принципам компоновки аппаратуры, а также к выбранному набору системных аппаратных средств.

Рис. 7.1. Архитектура персонального компьютера типа IBM PC.

Функции основных узлов компьютера следующие:

Центральный процессор - это микропроцессор со всеми необходимыми вспомогательными микросхемами, включая внешнюю кэш-память и контроллер системной шины. (О кэш-памяти подробнее будет рассказано в следующих разделах). В большинстве случаев именно центральный процессор осуществляет обмен по системной шине.

Оперативная память может занимать почти все адресуемое пространство памяти процессора. Однако чаще всего ее объем гораздо меньше. В современных персональных компьютерах стандартный объем системной памяти составляет, как правило, от 64 до 512 Мбайт. Оперативная память компьютера выполняется на микросхемах динамической памяти и поэтому требует регенерации.

Постоянная память (ROM BIOS - Base Input/Output System) имеет небольшой объем (до 64 Кбайт), содержит программу начального запуска, описание конфигурации системы, а также драйверы (программы нижнего уровня) для взаимодействия с системными устройствами.

Контроллер прерываний преобразует аппаратные прерывания системной магистрали в аппаратные прерывания процессора и задает адреса векторов прерывания. Все режимы функционирования контроллера прерываний задаются программно процессором перед началом работы.

Контроллер прямого доступа к памяти принимает запрос на ПДП из системной магистрали, передает его процессору, а после предоставления процессором магистрали производит пересылку данных между памятью и устройством ввода/вывода. Все режимы функционирования контроллера ПДП задаются программно процессором перед началом работы. Использование встроенных в компьютер контроллеров прерываний и ПДП позволяет существенно упростить аппаратуру применяемых плат расширения.

Контроллер регенерации осуществляет периодическое обновление информации в динамической оперативной памяти путем проведения по шине специальных циклов регенерации. На время циклов регенерации он становится хозяином (задатчиком) шины.

Перестановщик байтов данных помогает производить обмен данными между 16-разрядным и 8-разрядным устройствами, пересылать целые слова или отдельные байты.

Часы реального времени и таймер-счетчик - это устройства для внутреннего контроля времени и даты, а также для программной выдержки временных интервалов, программного задания частоты и т.д.

Системные устройства ввода/вывода - это те устройства, которые необходимы для работы компьютера и взаимодействия со стандартными внешними устройствами по параллельному и последовательному интерфейсам. Они могут быть выполнены на материнской плате, а могут располагаться на платах расширения.

Платы расширения устанавливаются в слоты (разъемы) системной магистрали и могут содержать оперативную память и устройства ввода/вывода. Они могут обмениваться данными с другими устройствами на шине в режиме программного обмена, в режиме прерываний и в режиме ПДП. Предусмотрена также возможность захвата шины, то есть полного отключения от шины всех системных устройств на некоторое время.

Важная особенность подобной архитектуры - ее открытость, то есть возможность включения в компьютер дополнительных устройств, причем как системных устройств, так и разнообразных плат расширения. Открытость предполагает также возможность простого встраивания программ пользователя на любом уровне программного обеспечения компьютера.

Первый компьютер семейства, получивший широкое распространение, IBM PC XT, был выполнен на базе оригинальной системной магистрали PC XT-Bus. В дальнейшем (начиная с IBM PC AT) она была доработана до магистрали, ставшей стандартной и получившей название ISA (Industry Standard Architecture). До недавнего времени ISA оставалась основой компьютера. Однако, начиная с появления процессоров i486 (в 1989 году), она перестала удовлетворять требованиям производительности, и ее стали дублировать более быстрыми шинами: VLB (VESA Local Bus) и PCI (Peripheral Component Interconnect bus) или заменять совместимой с ISA магистралью EISA (Enhanced ISA). Постепенно шина PCI вытеснила конкурентов и стала фактическим стандартом, а начиная с 1999 года в новых компьютерах рекомендуется полностью отказываться от магистрали ISA, оставляя только PCI. Правда, при этом приходится отказываться от применения плат расширения, разработанных за долгие годы для подключения к магистрали ISA.

Другое направление совершенствования архитектуры персонального компьютера связано с максимальным ускорением обмена информацией с системной памятью. Именно из системной памяти компьютер читает все исполняемые команды, и в системной же памяти он хранит данные. То есть больше всего обращений процессор совершает именно к памяти. Ускорение обмена с памятью приводит к существенному ускорению работы всей системы в целом. Но при использовании для обмена с памятью системной магистрали приходится учитывать скоростные ограничения магистрали. Системная магистраль должна обеспечивать сопряжение с большим числом устройств, поэтому она должна иметь довольно большую протяженность; она требует применения входных и выходных буферов для согласования с линиями магистрали. Циклы обмена по системной магистрали сложны, и ускорять их нельзя. В результате существенного ускорения обмена процессора с памятью по магистрали добиться невозможно.

Разработчиками был предложен следующий подход. Системная память подключается не к системной магистрали, а к специальной высокоскоростной шине, находящейся «ближе» к процессору, не требующей сложных буферов и больших расстояний. В таком случае обмен с памятью идет с максимально возможной для данного процессора скоростью, и системная магистраль не замедляет его. Особенно актуальным это становится с ростом быстродействия процессора (сейчас тактовые частоты процессоров персональных компьютеров достигают 1-3 ГГц).

Таким образом, структура персонального компьютера из одношинной, применявшейся только в первых компьютерах, становится трехшинной (рис. 7.2).

Рис. 7.2. Организация связей в случае трехшинной структуры.

Назначение шин следующее:

к локальной шине подключаются центральный процессор и кэш-память (быстрая буферная память);

к шине памяти подключается оперативная и постоянная память компьютера, а также контроллер системной шины;

к системной шине (магистрали) подключаются все остальные устройства компьютера.

Все три шины имеют адресные линии, линии данных и управляющие сигналы. Но состав и назначение линий этих шин не совпадают между собой, хотя они и выполняют одинаковые функции. С точки зрения процессора, системная шина (магистраль) в системе всего одна, по ней он получает данные и команды и передает данные как в память, так и в устройства ввода/вывода.

Временные задержки между системной памятью и процессором в данном случае минимальны, так как локальная шина и шина памяти соединены только простейшими быстродействующими буферами. Еще меньше задержки между процессором и кэш-памятью, подключаемой непосредственно к локальной шине процессора и служащей для ускорения обмена процессора с системной памятью.

Если в компьютере применяются две системные шины, например, ISA и PCI, то каждая из них имеет свой собственный контроллер шины, и работают они параллельно, не влияя друг на друга. Тогда получается уже четырехшинная, а иногда и пятишинная структура. Пример такой структуры компьютера приведен на рис. 7.3.

Рис. 7.3. Пример многошинной структуры.

В наиболее распространенных настольных компьютерах класса Desk-top в качестве конструктивной основы используется системная или материнская плата (motherboard), на которой располагаются все основные системные узлы компьютера, а также несколько разъемов (слотов) системной шины для подключения дочерних плат - плат расширения (интерфейсных модулей, контроллеров, адаптеров). Как правило, современные системные платы допускают замену процессора, выбор его тактовой частоты, замену и наращивание оперативной памяти, выбор режимов работы других узлов.

На системной плате сейчас обычно располагаются также основные средства внешнего интерфейса, служащие для присоединения как встроенных устройств (например, дисковых носителей), так и внешних устройств компьютера (например, клавиатуры, мыши, принтера, сканера, модема). Для подключения видеомонитора, как правило, используется специальная плата расширения (контроллер дисплея), вставляемая в один из слотов. Это позволяет заменять ее более мощной при необходимости установки нового монитора.

Отметим, что для получающих все более широкое распространение портативных персональных компьютеров класса ноутбуков (notebook) применяются несколько иные конструктивные решения. В частности, в них отсутствуют слоты расширения системной шины, а практически все узлы компьютера выполняются на одной плате. Но мы в основном будем говорить о компьютерах типа desktop (настольных), так как именно они наиболее приспособлены для построения сложных систем, допускают довольно простую модернизацию (upgrade) и настройку на конкретные нужды пользователя.

Процессоры персональных компьютеров

Несмотря на то, что первый персональный компьютер был выпущен фирмой Apple, сейчас персональными компьютерами называют в основном IBM PC-совместимые компьютеры. Это связано, прежде всего, с тем, что фирма IBM выбрала правильную рыночную политику: она не скрывала принципов устройства своих компьютеров и не патентовала основных решений. В результате многие производители стали выпускать совместимые компьютеры, и они быстро стали фактическим стандартом. Из-за большого объема выпуска персональные компьютеры начали быстро дешеветь. К тому же для IBM-совместимых персональных компьютеров стали разрабатывать множество программных средств, что еще больше способствовало их распространению. Поэтому, несмотря на некоторые существенные архитектурные недостатки, IBM-совместимые персональные компьютеры сейчас уверенно занимают первое место на рынке.

С самого начала фирма IBM ориентировалась на процессоры Intel. У этих процессоров были очень мощные конкуренты, например, процессоры фирм Motorola или Zilog, превосходившие процессоры Intel по многим параметрам, но именно благодаря персональным компьютерам процессоры Intel смогли выйти победителями в конкурентной борьбе. К тому же еще некоторые фирмы (например, AMD, VIA, Cyrix) выпускают Intel-совместимые процессоры. Поэтому мы рассмотрим основные особенности процессоров фирмы Intel. Это позволит нам также проследить основные тенденции в развитии процессоров за последние десятилетия.

Свой первый 16-разрядный процессор i8086 фирма Intel выпустила в 1978 году. Он мог адресовать 1 Мбайт памяти (то есть имел 20-разрядную шину адреса), производительность его при тактовой частоте 5 МГц составляла 0,33 MIPS, но вскоре появились процессоры с тактовой частотой 8 и 10 МГц. Чуть позже (через год) была выпущена упрощенная версия процессора i8086 - i8088, который отличался только 8-разрядной внешней шиной данных. За счет этого он был медленнее, чем i8086, на 20-60% при той же тактовой частоте, но зато заметно дешевле. Именно на его основе был собран очень популярный персональный компьютер IBM PC XT.

16-разрядный процессор i80286, выпущенный в 1982 году, был использован в персональных компьютерах IBM PC AT. Принципиально новым было в нем то, что он мог адресовать до 16 Мбайт памяти и имел помимо реального режима, аналогичного i8086, еще и так называемый защищенный режим, позволяющий более гибко управлять памятью. Производительность этого процессора при тактовой частоте 8 МГц составляла 1,2 MIPS.

Важным шагом стало появление в 1985 году полностью 32-разрядного процессора i80386, способного адресовать до 4 Гбайт памяти (32-разрядная адресная шина). Он имел еще более развитую систему управления памятью MMU (Memory Management Unit). Производительность его при тактовой частоте 16 МГц составляла 6 MIPS. С появлением этого процессора стала бурно развиваться операционная система MS Windows, существенно изменившая процесс работы с компьютерами типа IBM PC.

Еще одним принципиальным шагом стало создание в 1989 году процессора Intel 486DX, в котором появились встроенный математический сопроцессор, существенно ускоривший выполнение арифметических операций, и внутренняя кэш-память, ускоряющая обмен с оперативной памятью. Максимальный объем адресуемой памяти этого процессора - 4 Гбайт. На тактовой частоте 25 МГц производительность была 16,5 MIPS. Начиная с процессора 486, получило распространение так называемое умножение тактовой частоты, то есть внутреннее удвоение и даже учетверение внешней тактовой частоты (обозначается 486DX2, 486DX4).

В 1995 году появились первые процессоры Pentium, открывшие новый этап в развитии семейства. Они были 32-разрядными внутри, но имели 64-разрядную внешнюю шину данных. Принципиальным отличием было использование в них так называемой суперскалярной архитектуры, следствием чего стало более высокое быстродействие при той же тактовой частоте, что и i486DX. При тактовой частоте 66 МГц производительность процессора достигала 112 MIPS. В 1996 году тактовая частота Pentium была доведена до 200 МГц, а стоимость снизилась настолько, что он стал рядовым процессором персональных компьютеров семейства IBM PC.

В 1997 году Pentium был дополнен технологией MMX, призванной ускорять выполнение мультимедийных приложений (обработку изображений и звука). И в этом же году появился процессор Pentium II, который включает в себя технологию ММХ и имеет более высокое быстродействие. Возможная тактовая частота достигла 400 МГц.

В последние годы появились процессоры Pentium III и Pentium IV, имеющие еще более развитую архитектуру и тактовую частоту, превышающую 1 ГГц у Pentium III и 3 ГГц у Pentium IV.

Таким образом, содружество компании Intel и производителей IBM-совместимых персональных компьютеров успешно продолжается. Другие фирмы, выпускающие процессоры, вряд ли существенно потеснят в ближайшие годы Intel. Поэтому рассмотрим чуть подробнее характерные особенности процессоров для персональных компьютеров этой компании.

Особенности процессоров 8086/8088

Описание микропроцессоров фирмы Intel мы начнем с процессоров i8086/8088. Именно заложенные в них архитектурные решения во многом определили архитектуру последующих моделей семейства Intel, поддерживающих совместимость с более ранними моделями. В том числе и с недостатками и ограничениями предыдущих моделей.

Процессор i8086 имеет совмещенную (мультиплексированную) 20-разрядную внешнюю шину адреса/данных. Данные передаются по 16 разрядам, адрес - по 20 разрядам. Шина управления имеет 16 разрядов (в частности, в нее входят строб адреса и стробы обмена с памятью и устройствами ввода/вывода). Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена по внешней шине требует 4 тактов (без учета тактов ожидания, вводимых при асинхронном обмене). У процессора i8088 внешняя шина данных 8-разрядная.

Одна из характерных особенностей процессоров i8086/8088 - принцип сегментирования памяти. То есть вся память представляется не в виде непрерывного пространства, а в виде нескольких кусков - сегментов заданного размера (по 64 Кбайта), положение которых в пространстве памяти можно программно изменять. Об этом уже говорилось в разделе 3.1.2 (см. рис. 3.5 и 3.6).

Процессор 8086/8088 имеет 14 регистров разрядностью по 16 бит. Об их назначении также уже говорилось в разделе 3.2.

Для ускорения выборки команд из памяти в процессоре 8086 предусмотрен внутренний 6-байтный конвейер (в процессоре 8088 - 4-байтный). Конвейер заполняется читаемыми из памяти командами во время выполнения предыдущей команды и сбрасывается (считается пустым) при выполнении любой команды перехода (даже если это команда перехода на следующий адрес).

Система команд процессора включает в себя 133 команды, поддерживающие 24 метода адресации операндов. Такое большое число команд может рассматриваться как достоинство (можно гибко выбирать команду, оптимально подходящую для каждого конкретного случая), но оно же заметно усложняет структуру процессора.

Каждая команда содержит 1, 2 или 4 байта кода команды, за которыми могут следовать 1, 2 или 4 байта операнда.

В процессоре предусмотрены программные и аппаратные прерывания, разделение внешней шины с другими процессорами или с контроллером прямого доступа к памяти, а также возможность подключения математического сопроцессора i8087, существенно увеличивающего производительность вычислений.

Процессор может обрабатывать 256 типов прерываний: внешних (аппаратных), программных и внутренних. Векторы прерываний представляют собой двойное слово (два слова по 16 разрядов), определяющее сегмент и смещение начального адреса программы обработки прерываний.

Особое место занимает немаскируемое прерывание NMI (Non-Masked Interrupt), которое вырабатывается при поступлении внешнего сигнала NMI и не зависит от состояния флага разрешения аппаратных прерываний IF. В компьютере оно используется для контроля четности памяти, контроля корректности обмена с памятью и устройствами ввода/вывода, а также для обработки так называемых исключений, то есть особых условий, возникающих в процессе работы. Немаскируемым оно называется именно потому, что его нельзя запретить.

Важная отличительная особенность процессора - разделение операций обмена с устройствами ввода/вывода и с памятью. Для обмена с устройствами ввода/вывода используются как отдельные команды ввода и вывода, так и специальные управляющие сигналы на шине управления. Адреса и данные как при обмене с памятью, так и при обмене с устройствами ввода/вывода передаются по одним и тем же шинам Микропроцессоры i8086/8088 выполнены в виде интегральной микросхемы в 40-выводном корпусе. Отличие в назначении выводов микросхемы между ними только одно: адрес в процессоре 8088 не мультиплексирован с данными (передается по отдельным линиям), а в процессоре 8086 - мультиплексирован.

Процессор работает от одного источника питания напряжением +5В и требует внешнего тактирующего сигнала с частотой, определяемой номером модели (от 4,77 МГц до 10 МГц).

Специальный управляющий сигнал MN/MX определяет минимальный или максимальный режим работы процессора. В минимальном режиме процессор сам вырабатывает сигналы управления для внешней шины. Этот режим используется для построения простейших систем. Для работы в составе компьютера применяется максимальный режим, при котором сигналы управления внешней шиной вырабатываются специальной микросхемой контроллера шины i8288.

Особенности процессоров Pentium

Процессоры Pentium относятся к пятому поколению процессоров или к третьему поколению 32-разрядных процессоров. По своим основным архитектурным принципам они совместимы с процессорами 386 и 486. Но имеются существенные отличия, позволяющие говорить о новом поколении:

Суперскалярная архитектура процессора, то есть процессор имеет два пятиступенчатых параллельно работающих конвейера обработки информации, благодаря чему он способен одновременно выполнять две команды за один такт. Необходимо отметить, что преимущества такой архитектуры проявляются только в случае специальной компиляции программного обеспечения, позволяющей осуществлять параллельную обработку.

Внешняя 64-разрядная шина данных для повышения производительности. Это требует соответствующей организации памяти. Из-за такой особенности процессор иногда неправильно называют 64-разрядным (хотя внутри он все-таки остался 32-разрядным). Внешняя шина адреса процессора - 32-разрядная.

Применение технологии динамического предсказания ветвлений (переходов).

Раздельный кэш для команд и данных объемом 8 Кбайт каждый. Длина строки кэша - 32 байта. Оба кэша работают в режиме обратной записи.

Повышенная в 2-10 раз по сравнению с процессором 486 производительность встроенного математического сопроцессора. В нем применена восьмиступенчатая конвейеризация и специальные блоки сложения, умножения и деления, что позволяет выполнять операции с плавающей точкой за один такт процессора.

Сокращено время (число тактов) выполнения команд.

Предусмотрена возможность построения двухпроцессорных систем.

Введены средства управления энергопотреблением и тестирования.

Предсказание ветвлений позволяет продолжать выборку и декодирование потока команд после выборки команды ветвления (перехода), не дожидаясь проверки условия перехода. В прежних моделях в данном случае приходилось приостанавливать конвейер. Динамическое предсказание основывается на анализе предыдущей программы и накапливании статистики поведения. Исходя из этого анализа предсказывается наиболее вероятное условие каждого встречающегося в программе перехода.

В дополнение к базовой архитектуре 32-разрядных процессоров Pentium имеет набор регистров MSR (Model Specific Registers). В него входит группа тестовых регистров (TR1 - TR12), средства слежения за производительностью, регистры-фиксаторы адреса и данных цикла, вызвавшего срабатывание контроля машинной ошибки. Название этой группы регистров указывает на их уникальность для каждой модели процессоров Pentium.

Средства для слежения за производительностью (мониторинга производительности) включают в себя таймер реального времени и счетчики событий. Таймер представляет собой 64-разрядный счетчик, инкрементируемый с каждым тактом процессора. Два счетчика событий имеют разрядность по 40 бит и программируются на подсчет событий различных классов, связанных с шинными операциями, исполнением команд, связанных с работой кэша, контролем точек останова и т.д. Сравнивая состояния таймера и счетчиков событий, можно сделать вывод о производительности процессора.

Тестовые регистры позволяют управлять большинством функциональных узлов процессора, обеспечивая возможность подробного тестирования их работоспособности. Специальные биты регистра TR12 позволяют отключить новые архитектурные свойства (предсказание и трассировку ветвлений, параллельное выполнение инструкций), а также работу первичного кэша.

Средства для построения двухпроцессорных систем позволяют на одной локальной шине устанавливать два процессора с объединением почти всех одноименных выводов. Это дает возможность использовать симметричную мультипроцессорную обработку (SMP - Symmetric Multi-Processing) или строить функционально избыточные системы (FRC - Functional Redundancy Checking).

В режиме SMP каждый процессор выполняет свою задачу, порученную ему операционной системой, что поддерживается такими системами, как Novell NetWare, Windows NT, Unix. Оба процессора разделяют общие ресурсы компьютера, включая память и устройства ввода/вывода. В каждый момент шиной управляет один процессор, по определенным правилам они меняются ролями. В идеальном случае производительность системы увеличивается вдвое (без учета обращений к шине и времени на переключение процессоров).

В конфигурации FRC два процессора выступают как один логический процессор. Основной процессор (Master) работает в обычном однопроцессорном режиме. Проверочный процессор (Checker) выполняет все те же операции внутри себя, не управляя внешней шиной, и сравнивает сигналы основного процессора с теми, которые генерирует сам. В случае несовпадения формируется сигнал ошибки, обрабатываемый как прерывание. То есть в данном случае увеличивается надежность системы в целом (в идеале - вдвое).

Развитием Pentium стало добавление технологии MMX, рассчитанной на мультимедийное, графическое и коммуникационное применение. Основная идея ММХ заключается в одновременной обработке нескольких элементов данных за одну команду (SIMD, Single Instruction - Mutiple Data). Расширение ММХ использует новые типы упакованных 64-битных данных:

упакованные байты - восемь байт;

упакованные слова - четыре слова;

упакованные двойные слова (два двойных слова);

учетверенное слово (одно слово).

Эти типы данных могут обрабатываться в восьми дополнительных 64-разрядных регистрах ММХ0 - ММХ7. В систему команд для поддержки MMX введено 57 дополнительных команд для одновременной обработки нескольких единиц данных (команды пересылки, арифметические, логические команды и команды преобразования форматов данных). Команды ММХ доступны из любого режима процессора.

Кроме того, в процессорах Pentium ММХ увеличен объем кэша данных и программ (до 16 Кбайт каждый), увеличено число ступеней конвейеров и введено еще несколько усовершенствований, повышающих производительность обычных (не мультимедийных) операций.

От процессора Pentium Pro принято отсчитывать шестое поколение процессоров. Pentium Pro по сравнению с Pentium имеет следующие усовершенствования:

Динамическое исполнение команд предполагает, что команды, не зависящие от результатов предыдущих операций, могут выполняться в измененном порядке (последующие раньше предыдущих), однако последовательность обмена с внешними устройствами (памятью и устройствами ввода/вывода) будет соответствовать программе. То есть процессор сам выбирает удобный ему порядок выполнения команд. Это позволяет повысить производительность процессора без увеличения тактовой частоты.

Архитектура двойной независимой шины повышает суммарную пропускную способность. Одна шина (системная) служит для обмена с основной памятью и устройствами ввода/вывода, а другая (локальная) предназначена только для обмена с вторичным кэшем В процессор введен кэш второго уровня объемом 256-512 Кбайт.

Возможно построение многопроцессорных систем (до четырех микропроцессоров).

Процессор Pentium II сочетает в себе архитектуру Pentium Pro с технологией ММХ.

Размер первичных кэшей данных и команд составляет 16 Кбайт, вторичного кэша - до 512 Кбайт. Кэш второго уровня несколько медленнее, чем кэш первого уровня, зато он имеет больший объем. Такая двухуровневая организация позволяет достигать компромисса между быстродействием кэш-памяти и ее объемом.

Шина адреса имеет 36 разрядов (то есть максимально допустимый объем памяти - 64 Гбайта).

Процессоры Pentium III и Pentium 4 отличаются значительно возросшей предельной тактовой частотой (до 3 ГГц у Pentium 4, а в перспективе и до 5 ГГц), увеличенным объемом кэша (от 512 Кбайт до нескольких мегабайт) и дальнейшим совершенствованием архитектуры Pentium. Размер внутреннего конвейера у Pentium 4 доведен до 20 ступеней.

Уже появились и полностью 64-разрядные процессоры. Правда, полное использование возможностей 64-разрядной архитектуры потребует существенного изменения программного обеспечения.

Надо отметить, что в составе персональных компьютеров практически никогда не используются все возможности процессоров семейства Pentium. Например, многопроцессорные системы встречаются достаточно редко, а объем системной памяти лишь иногда превышает 512 Мбайт.

Для портативных компьютеров были предложены упрощенные версии процессоров Pentium III и Pentium 4, продаваемые под маркой Celeron. Они отличаются уменьшенной тактовой частотой и сокращенным объемом кэша второго уровня. Их тактовая частота сейчас доходит до 2 ГГц. Надо учитывать, что рассеиваемая мощность процессора Celeron остается практически такой же, как у процессоров Pentium III и Pentium 4.

Тема 1.2 Организация управления процессом обработки информации

План:

1 Структура микропроцессора

2 Аппаратный принцип управления выполнением операций

3 Микропрограммный принцип управления выполнением операций

Структура микропроцессора

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле.

В эту структуру входят:

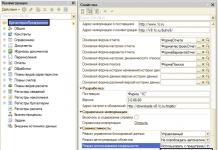

центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ), структурная схема приведена на рисунке 2;

внутренняя память (РЗУ, кэш-память, блоки оперативной и постоянной памяти);

интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода/вывода;

периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры);

различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Рисунок 2 – Структурная схема процессора

Операционное устройство (ОУ) - устройство, в котором выполняются операции. Оно включает в качестве узлов регистры, сумматоры, арифметико–логическое устройство (АЛУ), каналы передачи информации, мультиплексоры для коммутации каналов, шифраторы, дешифраторы и т.д.

Арифметико–логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций.

Управляющее устройство (УУ) координирует действия узлов операционного устройства; оно вырабатывает в некоторой временной последовательности управляющие сигналы, под действием которых в узлах операционного устройства выполняются требуемые действия.

Процесс функционирования операционного устройства распадается на последовательность элементарных действий в его узлах:

1) установка регистра в некоторое состояние (например, запись в регистр R1 числа 0, обозначаемая R1 <− 0);

2) инвертирование содержимого разрядов регистра (например, если регистр R2 содержал двоичное число 101101, то после инвертирования его содержимое будет равно 010010; такое действие обозначают R2 <− ());

3) пересылка содержимого одного узла в другой (например, пересылка содержимого регистра R2 в регистр R1, обозначаемая R1 <− (R2));

4) сдвиг содержимого узла влево, вправо (например, сдвиг на один разряд влево содержимого регистра R1, обозначаемый R1 <− СдвЛ (R1);

5) счет, при котором число в счетчике (регистре) возрастает или убывает на единицу (Сч<− (Сч ± 1));

6) сложение (например, R2 <− (R2) + (R1));

7) сравнение содержимого регистра на равенство с некоторым числом; результат сравнения: лог. 1 (при выполнении равенства) либо лог.0 (при невыполнении равенства);

8) некоторые логические действия (поразрядно выполняемые операции конъюнкции, дизъюнкции и др.). Каждое такое элементарное действие, выполняемое в одном из узлов ОУ в течение одного тактового периода, называется микрооперацией.

В определенные тактовые периоды одновременно могут выполняться несколько микроопераций, например R2 <− 0, Сч <− (Сч) - 1. Такая совокупность одновременно выполняемых микроопераций называется микрокомандой , а весь набор микрокоманд, предназначенный для решения определенной задачи, - микропрограммой.

Таким образом, если в операционном устройстве предусматривается возможность исполнения п различных микроопераций, то из управляющего устройства выходят п управляющих цепей, каждая из которых соответствует определенной микрооперации. И если необходимо в операционном устройстве выполнить некоторую микрооперацию, достаточно из управляющего устройства по определенной управляющей цепи, соответствующей этой микрооперации, подать сигнал (например, напряжение уровня лог. 1). В силу того, что управляющее устройство определяет микропрограмму, т.е. какие и в какой временной последовательности должны выполняться микрооперации, оно получило название микропрограммного автомата.

Формирование управляющих сигналов y 1 , ... ,y п для выполнения микрокоманд может происходить в зависимости от состояния узлов операционного устройства, определяемого сигналами х 1 , ... x s , которые подаются с соответствующих выходов операционного устройства на входы управляющего устройства. Управляющие сигналы y 1 , ..., y п могут также зависеть от внешних сигналов x s +1 ,..., x L .

Для сокращения числа управляющих цепей, выходящих из управляющего устройства (в тех случаях, когда оно конструктивно выполняется отдельно от операционного), микрокоманды могут кодироваться.

Существует два принципиально разных подхода к проектированию микропрограммного автомата (управляющего устройства):

Использование принципа схемной логики;

Использование принципа программируемой логики.

В первом случае в процессе проектирования подбирается некоторый набор цифровых микросхем (обычно малой и средней степени интеграции) и определяется такая схема соединения их выводов, которая обеспечивает требуемое функционирование (т.е. функционирование процессора определяется тем, какие выбраны микросхемы и по какой схеме выполнено соединение их выводов). Устройства, основанные на таком принципе схемной логики, способны обеспечивать наивысшее быстродействие при заданном типе технологии элементов. Недостаток этого принципа построения процессора состоит в трудности использования БИС и СБИС.

Второй подход предполагает построение процессора с использованием одной или нескольких БИС некоторого универсального устройства, в котором требуемое функционирование (т.е. специализация устройства на выполнение определенных функций) обеспечивается занесением в память устройства определенной программы (или микропрограммы).

В зависимости от введенной программы такое универсальное управляющее устройство способно обеспечивать требуемое управление операционным устройством при решении самых разнообразных задач. В этом случае число типов БИС, необходимых для построения управляющего устройства, окажется небольшим, а потребность в БИС каждого типа высокой, что обеспечит целесообразность их выпуска промышленностью.

При построении операционных устройств целесообразно широко использовать БИС с таким набором узлов и схемой соединения, которые обеспечили бы решение разнообразных задач. Независимо от решаемой задачи может быть использовано одно и то же универсальное операционное устройство, функционирующее под действием микропрограммы, хранящейся в управляющем устройстве. Следует иметь в виду, что наивысшее быстродействие достигается в процессорах, в которых управляющее устройство строится с использованием принципа схемной логики, а операционное устройство выполняется в виде устройства, специализированного для решения конкретной задачи.

Рисунок 5 - Типовая структура микропроцессорной системы

Разрядность шины адреса определяет максимальный объем адресуемой процессором внешней памяти. Например, 16-разрядная шина А обеспечивает адресацию памяти объемом до 64 Кбайт, а 32-разрядная шина-до 4 Гбайт.

В некоторых системах для уменьшения числа необходимых линий связи и соответствующих выводов и контактов используетсямультиплексирование линий адреса и данных. В таких системах для передачи адреса и данных используются одни и те же линии связи, на которые сначала выдается адрес, а затем поступают данные. Обмен информацией по мультиплексированной шине AD требует введения отдельного регистра для хранения адреса в процессе пересылки данных.

Разрядность шины управления С определяется организацией работы системы, возможностями реализации различных режимов ее функционирования, используемыми методами контроля микропроцессора и других устройств. Поэтому набор передаваемых по шине С управляющих сигналов является индивидуальным для каждой модели микропроцессора. В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы:

выполнение основной программы;

вызов подпрограммы;

обслуживание прерываний и исключений;

прямой доступ к памяти.

Рассмотрим основные принципы реализации этих режимов.

Режим вызова программы

Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR - Jump-to-SubRoutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм,

т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм,

т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Рисунок 7 - Последовательный вызов (вложение) подпрограмм

Для реализации этой процедуры используетсястек - специальная память магазинного типа, работающая по принципу «последний пришел - первый ушел» (стек типа LIFO -«Last In-First Out»). Существуют различные варианты реализации стека. Регистровый стек (Рисунок 5) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом, обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т.е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стек значений PC теряются, т.е. возврат к основной программе не будет обеспечен. Поэтому при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20).

Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (Рисунок 8). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра - указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL.

Рисунок 8 - Варианты реализации стека:

регистровый стек (а) и стек, реализуемый в ОЗУ (б)

При поступлении новой команды CALL (операция PUSH ) содержимое SP автоматически уменьшается на 1, адресуя следующую, еще незаполненную ячейку стека. Полученный адрес SP-1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке.

Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN (операция POP ) текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PC, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

Рисунок 9 - Реализация конвейерного исполнения команд

при идеальной (а) и реальной (б) загрузке 6-ступенчатого конвейера

Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. В идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнения очередной команды (Рисунок 9, а). В этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с). Реально отдельные ступени конвейера могут оказаться незагруженными, находясь в состоянии ожидания или простоя. Ожиданием называется состояние исполнительной ступени, когда она не может выполнить требуемую микрооперацию, так как еще не получен необходимый операнд, являющийся результатом выполнения предыдущей команды. Простоем называется состояние ступени, когда она вынуждена пропустить очередной такт, так как поступившая команда не требует выполнения соответствующего этапа. На рисунке 8,б показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываются в состоянии ожидания (ОЖ) или простоя (ПР).

При использовании в программе разноформатных команд, содержащих различное количество байтов, число состояний простоя и ожидания, которые приходится вводить в процессе выполнения команд, значительно увеличивается. Поэтому принятый во многих RISC-процессорах стандартный 4-байтный формат команд обеспечивает существенное сокращение числа ожиданий и простоев конвейера, что позволяет значительно повысить производительность.

Другой причиной снижения эффективности конвейера являются команды условного ветвления. Если выполняется условие ветвления, то приходится производить перезагрузку конвейера командами из другой ветви программы, что требует выполнения дополнительных рабочих тактов и вызывает значительное снижение производительности. Поэтому одним из основных условий эффективной работы конвейера является сокращение числа его перезагрузок при выполнении условных переходов. Эта цель достигается с помощью реализации различных механизмов предсказания направления ветвления, которые обеспечиваются с помощью специальных устройств - блоков предсказания ветвления , вводимых в структуру процессора.

Возможность повышения производительности процессора достигается также при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. В этих процессорах реализуется параллельная работа нескольких исполнительных конвейеров, в каждый из которых поступает для выполнения одна из выбранных и декодированных команд. В идеальном случае число одновременно выполняемых команд равно числу операционных устройств, включенных в исполнительные конвейеры. Однако при выполнении реальных программ трудно обеспечить полную загрузку всех исполнительных конвейеров, поэтому на практике эффективность использования суперскалярной структуры оказывается несколько ниже. Современные суперскалярные процессоры содержат до 4 до 10 различных операционных устройств, параллельная работа которых обеспечивает выполнение за один такт в среднем от 2 до 6 команд.

Эффективная одновременная работа нескольких исполнительных конвейеров обеспечивается путем предварительной выборки-декодирования ряда команд и выделения из них группы команд, которые могут выполняться одновременно. В современных суперскалярных процессорах производится выборка нескольких десятков команд, которые декодируются, анализируются и группируются для параллельной загрузки в исполнительные конвейеры.

Вывод:

Большинство микропроцессорных систем имеет магистрально-модульную структуру, в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине – магистрали (фон Неймановская архитектура). Системная шина содержит несколько десятков проводников, которые в соответствии с их функции-ональным назначением подразделяются на отдельные шины - адреса А, данных D и управления С. В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы: выполнение основной программы; вызов подпрограммы; обслуживание прерываний и исключений; прямой доступ к памяти.

В микропроцессорах с Гарвардской архитектурой и физическим разделением памяти команд и данных, реализуется конвейерный принципвыполнения команд, обеспечивая высокую производительность.При этом процесс выполнения команды разбивается на ряд этапов: выборка очередной команды (ВК); декодирование выбранной команды (ДК); формирование адреса операнда (ФА); прием операнда из памяти (ПО); выполнение операции (ВО); размещение результата в памяти (РР). Повысить производительность процессора можно при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной.

Контрольные вопросы:

1 Что представляет собой архитектура процессора фон Неймана типа?

2 Каков состав общей шины в структуре процессора?

3 Какие режимы при работе процессора?

4 Объяснить принцип конвейерной обработки команд.

5 Каков принцип работы процессора с суперскалярной структурой?

Тема 1.4 Ассемблерная мнемоника. Структура и форматы команд. Виды адресации. Система команд микропроцессора

План:

1 Язык ассемблера. Основные понятия

2 Символы языка ассемблера

3 Типы операторов ассемблера

4 Директивы ассемблера

5 Система команд процессора

Язык ассемблера. Основные понятия

Язык ассемблера - это символическое представление машинного языка. Все процессы в машине на самом низком, аппаратном уровне приводятся в действие только командами (инструкциями) машинного языка. Отсюда понятно, что, несмотря на общее название, язык ассемблера для каждого типа компьютера свой.

Программа на ассемблере представляет собой совокупность блоков памяти, называемых сегментами памяти. Программа может состоять из одного или нескольких таких блоков-сегментов. Каждый сегмент содержит совокупность предложений языка, каждое из которых занимает отдельную строку кода программы.

Предложения ассемблера бывают четырех типов:

1) команды или инструкции, представляющие собой символические аналоги машинных команд. В процессе трансляции инструкции ассемблера преобразуются в соответствующие команды системы команд микропроцессора;

2) макрокоманды - оформляемые определенным образом предложения текста программы, замещаемые во время трансляции другими предложениями;

3) директивы, являющиеся указанием транслятору ассемблера на выполнение некоторых действий. У директив нет аналогов в машинном представлении;

4) строки комментариев , содержащие любые символы, в том числе и буквы русского алфавита. Комментарии игнорируются транслятором.

Рисунок 11 - Формат директив

Рисунок 12 - Формат команд и макрокоманд

На этих рисунках:

имя метки - идентификатор, значением которого является адрес первого байта того предложения исходного текста программы, которое он обозначает;

имя - идентификатор, отличающий данную директиву от других одноименных директив. В результате обработки ассемблером определенной директивы этому имени могут быть присвоены определенные характеристики;

код операции (КОП) и директива - это мнемонические обозначения соответствующей машинной команды, макрокоманды или директивы транслятора;

операнды - части команды, макрокоманды или директивы ассемблера, обозначающие объекты, над которыми производятся действия. Операнды ассемблера описываются выражениями с числовыми и текстовыми константами, метками и идентификаторами переменных с использованием знаков операций и некоторых зарезервированных слов.

Синтаксические диаграммы помогаютнайти и затем пройти путь от входа диаграммы (слева) к ее выходу (направо). Если такой путь существует, то предложение или конструкция синтаксически правильные. Если такого пути нет, значит эту конструкцию компилятор не примет.

Символы языка ассемблера

Допустимыми символами при написании текста программ являются:

1) все латинские буквы: A-Z ,a-z . При этом заглавные и строчные буквы считаются эквивалентными;

2) цифры от 0 до 9 ;

3) знаки ? ,@ ,$ ,_ ,& ;

4) разделители , . () < > { } + / * % ! " " ? \ = # ^ .

Предложения ассемблера формируются из лексем , представляющих собой синтаксически неразделимые последовательности допустимых символов языка, имеющие смысл для транслятора.

Лексемами являются:

1) идентификаторы- последовательности допустимых символов, использующиеся для обозначения таких объектов программы, как коды операций, имена переменных и названия меток. Правило записи идентификаторов заключается в следующем: идентификатор может состоять из одного или нескольких символов;

2) цепочки символов- последовательности символов, заключенные в одинарные или двойные кавычки;

3) целые числав одной из следующих систем счисления: двоичной, десятичной, шестнадцатеричной. Отождествление чисел при записи их в программах на ассемблере производится по определенным правилам:

4) десятичные числа не требуют для своего отождествления указания каких-либо дополнительных символов, например 25 или 139. Для отождествления в исходном тексте программы двоичных чисел необходимо после записи нулей и единиц, входящих в их состав, поставить латинское “b ”, например 10010101b .

5) шестнадцатеричные числа имеют больше условностей при своей записи:

Во-первых, они состоят из цифр 0...9 , строчных и прописных букв латинского алфавита a ,b , c ,d ,e ,f или A ,B ,C ,D ,E ,F .

Во-вторых, у транслятора могут возникнуть трудности с распознаванием шестнадцатеричных чисел из-за того, что они могут состоять как из одних цифр 0...9 (например, 190845), так и начинаться с буквы латинского алфавита (например, ef15 ). Для того чтобы "объяснить" транслятору, что данная лексема не является десятичным числом или идентификатором, программист должен специальным образом выделять шестнадцатеричное число. Для этого на конце последовательности шестнадцатеричных цифр, составляющих шестнадцатерич-ное число, записывают латинскую букву “h ”. Это обязательное условие. Если шестнадцатеричное число начинается с буквы, то перед ним записывается ведущий ноль: 0 ef15h.

Практически каждое предложение содержит описание объекта, над которым или при помощи которого выполняется некоторое действие. Эти объекты называются операндами . Их можно определить так: операнды - это объекты (некоторые значения, регистры или ячейки памяти), на которые действуют инструкции или директивы, либо это объекты, которые определяют или уточняют действие инструкций или директив.

Возможно, провести следующую классификацию операндов:

постоянные или непосредственные операнды;

адресные операнды;

перемещаемые операнды;

счетчик адреса;

регистровый операнд;

базовый и индексный операнды;

структурные операнды;

записи.

Операнды являются элементарными компонентами, из которых формируется часть машинной команды, обозначающая объекты, над которыми выполняется операция. В более общем случае операнды могут входить как составные части в более сложные образования, называемые выражениями .

Выражения представляют собой комбинации операндов и операторов, рассматриваемые как единое целое. Результатом вычисления выражения может быть адрес некоторой ячейки памяти или некоторое константное (абсолютное) значение.

Типы операторов ассемблера

Перечислим возможные типы операторов ассемблера и синтаксические правила формирования выражений ассемблера:

арифметические операторы;

операторы сдвига;

операторы сравнения;

логические операторы;

индексный оператор;

оператор переопределения типа;

оператор переопределения сегмента;

оператор именования типа структуры;

оператор получения сегментной составляющей адреса выражения;

оператор получения смещения выражения.

Директивы ассемблера

Директивы ассемблера бывают:

1) Директивы сегментации. В ходе предыдущего обсуждения мы выяснили все основные правила записи команд и операндов в программе на ассемблере. Открытым остался вопрос о том, как правильно оформить последовательность команд, чтобы транслятор мог их обработать, а микропроцессор - выполнить.

При рассмотрении архитектуры микропроцессора мы узнали, что он имеет шесть сегментных регистров, посредством которых может одновременно работать:

с одним сегментом кода;

с одним сегментом стека;

с одним сегментом данных;

с тремя дополнительными сегментами данных.

Физически сегмент представляет собой область памяти, занятую командами и (или) данными, адреса которых вычисляются относительно значения в соответствующем сегментном регистре. Синтаксическое описание сегмента на ассемблере представляет собой конструкцию, изображенную на рисунке 13:

Рисунок 13 - Синтаксическое описание сегмента на ассемблере

Важно отметить, что функциональное назначение сегмента несколько шире, чем простое разбиение программы на блоки кода, данных и стека. Сегментация является частью более общего механизма, связанного с концепцией модульного программирования. Она предполагает унификацию оформления объектных модулей, создаваемых компилятором, в том числе с разных языков программирования. Это позволяет объединять программы, написанные на разных языках. Именно для реализации различных вариантов такого объединения и предназначены операнды в директиве SEGMENT.

2) Директивы управления листингом. Директивы управления листингом делятся на следующие группы:

общие директивы управления листингом;

директивы вывода в листинг включаемых файлов;

директивы вывода блоков условного ассемблирования;

директивы вывода в листинг макрокоманд;

директивы вывода в листинг информации о перекрестных ссылках;

директивы изменения формата листинга.

Система команд процессора

Система команд процессора представлена на рисунке 14.

Рассмотрим основные группы команд.

Рисунок 14 - Классификация команд ассемблера

Команды бывают:

1 Команды пересылки данных. Эти команды занимают очень важное место в системе команд любого процессора. Они выполняют следующие важнейшие функции:

сохранение в памяти содержимого внутренних регистров процессора;

копирование содержимого из одной области памяти в другую;

запись в устройства ввода/вывода и чтение из устройств ввода/вывода.

В некоторых процессорах все эти функции выполняются одной единственной командой MOV (для байтовых пересылок - MOVB) но с различными методами адресации операндов.

В других процессорах помимо команды MOV имеется еще несколько команд для выполнения перечисленных функций. Также к командам пересылки данных относятся команды обмена информацией (их обозначение строится на основе слова Exchange). Может быть предусмотрен обмен информацией между внутренними регистрами, между двумя половинами одного регистра (SWAP) или между регистром и ячейкой памяти.

2 Арифметические команды. Арифметические команды рассматривают коды операндов как числовые двоичные или двоично-десятичные коды. Эти команды могут быть разделены на пять основных групп:

команды операций с фиксированной запятой (сложение, вычитание, умножение, деление);

команды операций с плавающей запятой (сложение, вычитание, умножение, деление);

команды очистки;

команды инкремента и декремента;

команда сравнения.

3 Команды операций с фиксированной запятой работают с кодами в регистрах процессора или в памяти как с обычными двоичными кодами. Команды операций с плавающей запятой (точкой) используют формат представления чисел с порядком и мантиссой (обычно эти числа занимают две последовательные ячейки памяти). В современных мощных процессорах набор команд с плавающей запятой не ограничивается только четырьмя арифме-тическими действиями, а содержит и множество других более сложных команд, например, вычисление тригонометрических функций, логарифмических функций, а также сложных функций, необходимых при обработке звука и изображения.

4 Команды очистки предназначены для записи нулевого кода в регистр или ячейку памяти. Эти команды могут быть заменены командами пересылки нулевого кода, но специальные команды очистки обычно выполняются быстрее, чем команды пересылки.

5 Команды инкремента (увеличения на единицу) и декремента

(уменьшения на единицу) также бывают очень удобны. Их можно в принципе заменить командами суммирования с единицей или вычитания единицы, но инкремент и декремент выполняются быстрее, чем суммирование и вычитание. Эти команды требуют одного входного операнда, который одновременно является и выходным операндом.

6 Команда сравнения предназначена для сравнения двух входных операндов. По сути, она вычисляет разность этих двух операндов, но выходного операнда не формирует, а всего лишь изменяет биты в регистре состояния процессора по результату этого вычитания. Следующая за командой сравнения команда (обычно это команда перехода) будет анализировать биты в регистре состояния процессора и выполнять действия в зависимости от их значений. В некоторых процессорах предусмотрены команды цепочечного сравнения двух последовательностей операндов, находящихся в памяти.

7 Логические команды. Логические команды выполняют над операндами логические (побитовые) операции, то есть они рассматривают коды операндов не как единое число, а как набор отдельных битов. Этим они отличаются от арифметических команд. Логические команды выполняют следующие основные операции:

логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ);

логические, арифметические и циклические сдвиги;

проверка битов и операндов;

установка и очистка битов (флагов) регистра состояния процессора (PSW).

Команды логических операций позволяют побитно вычислять основные логические функции от двух входных операндов. Кроме того, операция И используется для принудительной очистки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие очистки, установлены в нуль). Операция ИЛИ применяется для принудительной установки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие установки в единицу, равны единице). Операция «Исключающее ИЛИ» используется для инверсии заданных битов (в качестве одного из операндов при этом применяется код маски, в котором биты, подлежащие инверсии, установлены в единицу). Команды требуют двух входных операндов и формируют один выходной операнд.

8 Команды сдвигов позволяют побитно сдвигать код операнда вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Тип сдвига (логический, арифметический или циклический) определяет, каково будет новое значение старшего бита (при сдвиге вправо) или младшего бита (при сдвиге влево), а также определяет, будет ли где-то сохранено прежнее значение старшего бита (при сдвиге влево) или младшего бита (при сдвиге вправо). Циклические сдвиги позволяют сдвигать биты кода операнда по кругу (по часовой стрелке при сдвиге вправо или против часовой стрелки при сдвиге влево). При этом в кольцо сдвига может входить или не входить флаг переноса. В бит флага переноса (если он используется) записывается значение старшего бита при циклическом сдвиге влево и младшего бита при циклическом сдвиге вправо. Соответственно, значение бита флага переноса будет переписываться в младший разряд при циклическом сдвиге влево и в старший разряд при циклическом сдвиге вправо.

9 Команды переходов. Команды переходов предназначены для организации всевозможных циклов, ветвлений, вызовов подпрограмм и т.д., то есть они нарушают последовательный ход выполнения программы. Эти команды записывают в регистр-счетчик команд новое значение и тем самым вызывают переход процессора не к следующей по порядку команде, а к любой другой команде в памяти программ. Некоторые команды переходов предусматривают в дальнейшем возврат назад, в точку, из которой был сделан переход, другие не предусматривают этого. Если возврат предусмотрен, то текущие параметры процессора сохраняются в стеке. Если возврат не предусмотрен, то текущие параметры процессора не сохраняются.

Команды переходов без возврата делятся на две группы:

команды безусловных переходов;

команды условных переходов.

В обозначениях этих команд используются слова Branch (ветвление) и Jump (прыжок).

Команды безусловных переходов вызывают переход в новый адрес независимо ни от чего. Они могут вызывать переход на указанную величину смещения (вперед или назад) или же на указанный адрес памяти. Величина смещения или новое значение адреса указываются в качестве входного операнда.

Команды условных переходов вызывают переход не всегда, а только при выполнении заданных условий. В качестве таких условий обычно выступают значения флагов в регистре состояния процессора (PSW). То есть условием перехода является результат предыдущей операции, меняющей значения флагов. Всего таких условий перехода может быть от 4 до 16. Несколько примеров команд условных переходов:

переход, если равно нулю;

переход, если не равно нулю;

переход, если есть переполнение;

переход, если нет переполнения;

переход, если больше нуля;

переход, если меньше или равно нулю.

Введение

Введение

Микропроцессоры и микроконтроллеры являются одной из наиболее динамично развивающихся областей современной электронной техники. Впервые появившись в 1971 году, эти электронные приборы быстро прошли путь от простейших устройств, выполняющих несложные вычисления, до современных высокопроизводительных процессоров, реализующих сотни миллионов операций в секунду. Еще более впечатляющим является лавинообразное расширение их областей применения. В настоящее время на производстве и в быту нас окружают десятки микропроцессоров и микроконтроллеров, встроенных в аппаратуру различного назначения. Это не только персональные компьютеры, которые стали обязательным атрибутом, как домашнего интерьера, так и рабочего места специалистов во многих сферах производства и обслуживания. Это и современная бытовая техника, средства проведения досуга, автомобильная электроника и медицинская аппаратура, средства связи, разноообразные приборы и системы, используемые в производственном оборудовании, и многое другое.

Знание основ микропроцессорной техники является необходимым для многих специалистов, как разрабатывающих новые виды устройств на базе современных микропроцессоров и микроконтроллеров, так и использующих в своей профессиональной деятельности аппаратуру, реализованную на их основе. Данное учебное пособие имеет целью помочь освоению этой техники широкому кругу специалистов, выпускаемых учебными заведениями для различных отраслей народного хозяйства.

Современная электронная цифровая вычислительная техника широко применяется в народном хозяйстве. В настоящее время создано четыре поколения ЭВМ с улучшающимися технико-экономическими показателями, что способствует дальнейшему расширению сферы применения ЭВМ и их эффективности.

Микроконтроллеры являются наиболее массовым представителем микропроцессорной техники. Интегрируя на одном кристалле высоко производительный процессор, память и набор периферийных устройств, микроконтроллеры позволяют с минимальными затратами реализовать широкую номенклатуру систем управления различными объектами и процессами. Использование микроконтроллеров в системах управления и обработки информации обеспечивает исключительно высокие показатели эффективности при достаточно низкой стоимости. Микроконтроллерам практически нет альтернативы, когда нужно создать качественные и дешевые системы. Иногда система может состоять только из одного микроконтроллера. Исключение составляет применение программируемых логических интегральных схем (ПЛИС) в области обработки сигналов в том случае, когда требуется параллельная обработка большого потока входных данных.

микропроцессор микроконтроллер архитектура вычислительный

1. Микропроцессоры, функциональные возможности и архитектурные решения

Развитие технологии обеспечивает возможность создания на кристалле все большего количества активных компонентов - транзисторов, которые могут быть использованы для реализации новых архитектурных и структурных решений, обеспечивающих повышение производительности и расширение функциональных возможностей микропроцессоров. Кратко рассмотрим основные из этих решений.

Архитектурой процессора называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и способы обработки прерываний. Например, все модификации процессоров Pentium, Celeron, i486 и i386 имеют архитектуру IA-32 (Intel Architecture - 32 bit), которая характеризуется стандартным набором регистров, предоставляемых пользователю, общей системой основных команд и способов организации и адресации памяти, одинаковой реализацией защиты памяти и обслуживания прерываний.

При описании архитектуры и функционирования процессора обычно используется его представление в виде совокупности программно-доступных регистров, образующих регистровую или программную модель. В этих регистрах содержатся обрабатываемые данные (операнды) и управляющая информация. Соответственно, в регистровую модель входит группа регистров общего назначения, служащих для хранения операндов, и группа служебных регистров, обеспечивающих управление выполнением программы и режимом работы процессора, организацию обращения к памяти (защита памяти, сегментная и страничная организация и др.).

Регистры общего назначения образуют РЗУ - внутреннюю регистровую память процессора (см. раздел 1.3). Состав и количество служебных регистров определяется архитектурой микропроцессора. Обычно в их состав входят:

программный счетчик PC (или CS + IP в архитектуре микропроцессоров Intel),

регистр состояния SR (или EFLAGS),

регистры управления режимом работы процессора CR (Control Register),

регистры, реализующие сегментную и страничную организацию памяти,

регистры, обеспечивающие отладку программ и тестирование процессора.

Кроме того, различные модели микропроцессоров содержат ряд других специализированных регистров.

Функционирование процессора представляется в виде реализации регистровых пересылок - процедур проверки и изменения состояния этих регистров путем чтения-записи их содержимого. В результате таких пересылок обеспечивается адресация и выбор команд и операндов, хранение и пересылка результатов, изменение последовательности команд и режимов функционирования процессора в соответствии с поступлением нового содержимого в служебные регистры, а также все другие процедуры, реализующие процесс обработки информации согласно заданным условиям.

В ряде процессоров выделяются регистры, которые используются при выполнении прикладных программ и доступны каждому пользователю, и регистры, которые управляют режимом работы всей системы и доступны только для привилегированных программ, входящих в состав операционной системы (супервизора). Соответственно, такие процессоры представляются в виде регистровой модели пользователя, в которую входят регистры, используемые при выполнении прикладных программ, или регистровой модели супервизора, которая содержит весь набор программно-доступных регистров процессора, используемых операционной системой.

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят:

центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ),

внутренняя память (РЗУ, кэш-память, в микроконтроллерах - блоки оперативной и постоянной памяти),

интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода-вывода,

периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры),

различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Состав устройств и блоков, входящих в структуру микропроцессора, и реализуемые механизмы их взаимодействия определяются функциональным назначением и областью применения микропроцессора.

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования.

В современных микропроцессорах реализуются следующие варианты архитектур.(Complex Instruction Set Computer) - архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Эта классическая архитектура процессоров, которая начала свое развитие в 40-х годах прошлого века с появлением первых компьютеров. Типичным примером CISC-процессоров являются микропроцессоры семейства Pentium. Они выполняют более 300 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенно усложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В то же время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 80-х годов прошлого века, интенсивное развитие получила архитектура процессоров с сокращенным набором команд (RISC-процессоры).(Reduced Instruction Set Computer) - архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 2 или 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего РЗУ - от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.

Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЗУ или пересылки результатов из РЗУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Указанные достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром. Таким образом, работают, например, последние модели микропроцессоров Pentium и K7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.(Very Large Instruction Word) - архитектура появилась относительно недавно - в 90-х годах. Ее особенностью является использование очень длинных команд (до 128 бит), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций, которые могут производиться параллельно в различных операционных устройствах, входящих в структуру микропроцессора. При трансляции программ, написанных на языке высокого уровня, соответствующий компилятор производит формирование "длинных" VLIW-команд, каждая из которых обеспечивает реализацию процессором целой процедуры или группы операций. Данная архитектура реализована в некоторых типах современных микропроцессоров (PA8500 компании Hewlett-Packard, Itanium - совместная разработка Intel и Hewlett-Packard, некоторые типы DSP - цифровых процессоров сигналов) и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров.

Кроме набора выполняемых команд и способов адресации важной архитектурной особенностью микропроцессоров является используемый вариант реализации памяти и организация выборки команд и данных. По этим признакам различаются процессоры с Принстонской и Гарвардской архитектурой. Эти архитектурные варианты были предложены в конце 40-х годов специалистами, соответственно, Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Структура и функционирование цифровой системы с Принстонской архитектурой описаны в разделе 1. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится "узким местом" (bottle-neck - "бутылочное горло"), которое ограничивает производительность цифровой системы. Постоянно возрастающие требования к производительности микропроцессорных систем вызвали в последние годы все более широкое применение Гарвардской архитектуры при создании многих типов современных микропроцессоров.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходиться использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

Гарвардская архитектура получила также широкое применение в микроконтроллерах - специализированных микропроцессорах для управления различными объектами, рабочая программа которых обычно хранится в отдельном ПЗУ.