З підвищенням тактових частот і розрядності процесорів настала нагальна проблема підвищення швидкості передачі даних у шинах (який сенс використовувати камінь з тактовою частотою, скажімо, 66 МГц, якщо шина працює на частоті лише 8,33 МГц). В одних випадках, наприклад, клавіатурі або мишці, висока швидкість ні до чого. Але інженери фірм платників розширення готові були виготовляти пристрої зі швидкістю, яку шини не могли надати.

У

вихід із становища було знайдено наступний: частина операцій обміну даними, потребують високих швидкостей, повинна здійснюватися через стандартні роз'єми шини вводу/вывода, а ще через додаткові високошвидкісні інтерфейси- шину процесора, приблизно так само, як підключається зовнішній кеш.

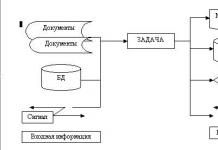

Справа в тому, що ці високошвидкісні інтерфейси підключаються до шини процесора. З цього випливає, що плати, що підключаються, матимуть доступ безпосередньо до процесора через його шину. Така конструкція отримала назву локальної шини (LB, Local Bus). Локальна шина не замінювала колишні стандарти, а доповнювала їх. Малюнок демонструє різницю між звичайною архітектурою та архітектурою з локальною шиною. Між іншим, перші шини ISA якраз і були локальними, але коли їхня тактова частота перевищила 8 МГц, стався поділ.

Основними шинами в комп'ютері залишалися ISA або EISA, але до них додавалися один або кілька слотів локальної шини. Спочатку ці слоти використовувалися майже виключно для встановлення відеоадаптерів, при цьому до 1992 року було розроблено кілька несумісних між собою варіантів локальних шин, виняткові права на які належали фірмам-виробникам.

Така різноманітність стримувала поширення локальних шин, тому Асоціація зі стандартів у галузі відеоелектроніки VESA (Video Electronic Standard Association), що представляє понад 100 компаній, запропонувала у серпні 1992 року свою специфікацію локальної шини VESA Local Bus (VL-bus або VLB), яка не змінювала , а доповнювала існуючі стандарти. Шина VLB розроблена з метою збільшення пропускну спроможністьміж основним процесором і відеокартою, для цього просто до основних шин додавали кілька нових швидкодіючих локальних слотів. Основна функція, для якої була призначена нова шина – обмін даними з відеоадаптером.

Була 32-бітною шиною, яка використовувала третій і четвертий роз'єм у вигляді продовження звичайного слота ISA. Шина працювала на номінальній частоті 33 МГц та забезпечувала суттєвий приріст продуктивності в порівнянні з ISA. Надалі шину VLB стали використовувати виробники контролерів жорстких дисків та інших пристроїв, які потребують високошвидкісної передачіданих. Випускалися навіть 100-мегабітні Ethernet контролериіз шиною VLB. Широке поширення шини VESA зумовила її відносна дешевизна та сумісність "згори донизу" зі своєю попередницею - шиною ISA. Роз'єм VLB є роз'єм ISA з "продовженням".

Основні характеристики VL-bus такі:

підтримка процесорів серій 80386 та 80486. Шина розроблена для використання в однопроцесорних системах, при цьому у специфікації передбачена можливість підтримки х86-несумісних процесорів за допомогою моста (bridge chip);

максимальне число bus master – 3 (не включаючи контролер шини). При необхідності можливе встановлення кількох підсистем для підтримки більшого числа master. Незважаючи на те, що спочатку шина була розроблена для підтримки відеоконтролерів, можлива підтримка та інших пристроїв (наприклад, контролерів жорсткого диска);

допускається робота шини на частоті до 66 МГц, проте електричні характеристики роз'єму VL-bus обмежують її до 50 МГц (це обмеження, природно, не відноситься до інтегрованих у материнську плату пристроїв);

двонаправлена (bi-directional) 32-розрядна шина даних підтримує 16-розрядний обмін. У специфікацію закладено можливість 64-розрядного обміну;

підтримка DMA забезпечується лише для bus masters. Шина не підтримує спеціальних "ініціаторів" DMA;

максимальна теоретична пропускна здатність шини 160 Мб/с (при частоті шини 50 МГц); стандартна - 107 Мб/с при частоті 33 МГц;

підтримка пакетного режиму обміну (для материнських плат 80486, які підтримують цей режим). П'ять ліній використовується для ідентифікації типу та швидкості процесора, сигнал Burst Last (BLAST#) використовується для активізації цього режиму. Для систем, що не підтримують цей режим, лінія встановлюється 0;

використання 58-контактного роз'єму МСА. Максимально підтримується 3 слоти (на деяких 50-мегагерцових шинах можливе встановлення лише 1 слота). Слот VL-bus встановлюється в лінію за слотами ISA/EISA/MCA, тому VL-плат доступні всі лінії цих шин;

підтримка як інтегрованого кеш-процесора, так і кеша на материнській платі. Напруга живлення - 5 В. Пристрої з рівнем вихідного сигналу 3,3 підтримуються за умови, що вони можуть працювати з рівнем вхідного сигналу 5 Ст.

Ця 32/32-розрядна шина розроблялася для машин з 386, 486 та Pentium процесорами. Найбільшого поширення шина VLB отримала на материнських платах 486. На них VESA – це лінії адреси, даних та управління процесора, виведені на роз'єм. Ця обставина накладає значні обмеження на VLB-карти розширення – тимчасові та навантажувальні параметри мають бути чітко витримані. Як зазначено в інструкціях на багато материнських плат, число VLB-карт при тактовій частоті 25 МГц не повинно перевищувати трьох, при 33 МГц - двох, при 40 і 50 МГц - однієї. У разі порушення цих вимог система працюватиме нестабільно, оскільки перевищено здатність навантаження процесора.

Для оцінки швидкості шини можна навести наступний розрахунок: якщо карта розширення працює на частоті 50 МГц, тоді пропускна здатність шини дорівнюватиме 32*50*10 6 = 1,6*10 9 Мбіт/с = 200 Мбайт/с, що досить багато. Однак не слід забувати, що така швидкість майже ніколи не може бути потрібна, оскільки дані з відеопам'яті не можуть читатися з такою швидкістю. Крім того, під час звернення до VLB-карти процесор не може більше займатися нічим, скільки б повільним не було пристрій на цій карті (наприклад, послідовний порт).

Шина VL-bus стала величезним кроком вперед у порівнянні з ISA як за продуктивністю, так і дизайном. Однією з переваг шини було те, що вона дозволяла створювати карти, що працюють з існуючими чіпсетами і не містять великої кількості схем дорогої логіки, що управляє. В результаті VL-карти виходили дешевше за аналогічні EISA-картки. Однак і ця шина не була позбавлена недоліків, головними з яких були:

орієнтація на 486 процесор. VL-bus жорстко прив'язана до шини процесора 80486, яка відрізняється від шин Pentium та Pentium Pro/Pentium II.

обмежена швидкодія. Як уже було сказано, реальна частота VL-bus – не більше 50 МГц. Причому при використанні процесорів з множником частоти шина використовує основну частоту (так, для 486DX2-66 частота шини буде 33 МГц);

схемотехнічні обмеження До якості сигналів, що передаються по шині процесора, пред'являються дуже жорсткі вимоги, дотримуватися яких можна лише за певних параметрів навантаження кожної лінії шини. На думку Intel, установка недостатньо акуратно розроблених VL-плат може призвести не лише до втрат даних та порушень синхронізації, а й до пошкодження системи;

обмеження кількості плат. Це обмеження випливає також із необхідності дотримання обмежень на навантаження кожної лінії.

Популярність шини VLB тривала до 1994 року. Головна особливість шини, яка дозволяла досягти високої продуктивності, Послужила і причиною відходу VLB з ринку. Шина була прямим розширенням шини 486 процесора/пам'яті, що працює на тій же швидкості, що і процесор (звідси і ім'я локальна шина - local bus). Пряме з'єднанняозначає, що підключення занадто великої кількостіпристроїв призводило до небезпеки створення перешкод самому процесору, якщо сигнали проходили через слот. VESA рекомендувала використовувати не більше двох слотів на тактових частотах 33 МГц або трьох слотів, якщо вони використовували спеціальний буфер. На більш високих тактових частотах слід підключати не більше двох пристроїв, а на частоті 50 МГц обидва пристрої VLB повинні бути вбудовані в материнську плату.

Оскільки шина VLB працює синхронно із процесором, збільшення частоти процесора призводило до появи проблем із периферією VLB. Чим швидше мала працювати периферія, тим вона дорожче коштувала через труднощі, пов'язані з виробництвом високошвидкісних компонент. Лише деякі пристрої VLB підтримували швидкість вище 40 МГц.

ВСТУП

Шина – це канал пересилання даних, використовуваний спільно різними блоками системи. Шина може являти собою набір провідних ліній, витравлених на друкованій платі, дроти, припаяні до висновків роз'ємів, які вставляють друковані плати, або плоский кабель. Компоненти комп'ютерної системи фізично розташовані на одній або кількох друкованих платах, причому їх кількість та функції залежать від конфігурації системи, її виробника, а часто й від покоління мікропроцесора.

Основними характеристиками шин є розрядність даних і швидкість передачі даних.

Найбільший інтерес викликають два типи шин – системний та локальний.

Системна шина призначена для забезпечення передачі даних між периферійними пристроями та центральним процесором, а також оперативною пам'яттю.

Локальної шиною, зазвичай, називається шина, безпосередньо підключена до контактів мікропроцесора, тобто. шина процесора.

1. СИСТЕМНІ ШИНИ

Основним обов'язком системної шини є передача інформації між базовим мікропроцесором та іншими електронними компонентами комп'ютера. По цій шині здійснюється адресація пристроїв і відбувається обмін спеціальними службовими сигналами. Таким чином, спрощено системну шину можна як сукупність сигнальних ліній, об'єднаних за призначенням (дані, адреси, управління). Передачею інформації по шині управляє один із підключених до неї пристроїв або спеціально виділений для цього вузол, званий арбітром шини.

Системна шина IBM PC і IBM PC/XT була призначена для одночасної передачі лише 8 біт інформації, оскільки мікропроцесор 18088, що використовується в комп'ютерах, мав 8 ліній даних. Крім того, системна шина включала 20 адресних ліній, які обмежували адресний простір межею 1 Мбайт. Для роботи із зовнішніми пристроями у цій шині були передбачені також 4 лінії апаратних переривань (IRQ) та 4 лінії для вимоги зовнішніми пристроями прямого доступу до пам'яті (DMA, Direct Memory Access). Для підключення плат розширення використовувалися спеціальні 62-контактні роз'єми. Зауважимо, що системна шина та мікропроцесор синхронізувалися від одного тактового генератора з частотою 4,77 МГц. Таким чином, теоретично швидкість передачі могла досягати більше 4,5 Мбайта/с.

1.1 ШинаISA

Шина ISA (Industry Standart Architecture) – шина, що застосовувалася з перших моделей PC і стала промисловим стандартом. У PC моделей XT застосовувалася шина з розрядністю даних 8 біт та адреси – 20 біт. У моделях AT шина була розширена до 16 біт даних та 24 біта адреси, якою вона залишається досі. Конструктивно шина виконана у вигляді двох слотів. Підмножина ISA-8 використовує тільки перший 62-контактний слот, ISA-16 застосовується додатковий 36-контактний слот. Тактова частота – 8 МГц. Швидкість передачі до 16 Мбайт\с. Має хорошу завадостійкість.

Шина забезпечує своїм абонентам можливість відображення 8- або 16-бітових регістрів на простір введення-виведення та пам'яті. Діапазон доступних адрес пам'яті обмежений областю UMA ( U nified M emory A rchitecture - уніфікована архітектура пам'яті), але для шини ISA-16 спеціальними опціями BIOS Setup може бути дозволено і простір в області між 15-м та 16-м мегабайтом пам'яті (правда при цьому комп'ютер не зможе використовувати більше 15 Мбайт ОЗП). Діапазон адрес вводу-виводу зверху обмежений кількістю використовуваних для дешифрації біт адреси, нижня межа обмежена областю адрес 0-FFh, зарезервованих під пристрої системної плати. В PC була прийнята 10-бітна адресація вводу-виводу, при якій лінії адреси A пристроями ігнорувалися. Таким чином, діапазон адрес пристроїв шини ISA обмежується областю 100h-3FFh, тобто всього 758 адрес 8-бітових регістрів. На деякі області цих адрес претендують і системні пристрої. Згодом стали застосовувати і 12-бітну адресацію (діапазон 100h-FFFh), але при її використанні завжди необхідно враховувати можливість присутності на шині і старих 10-бітових адаптерів, які "відгукуються" на адресу з бітами A, що підходять йому, у всій допустимій області чотири рази .

У розпорядженні абонентів шини ISA-8 може бути до 6 ліній запитів переривань IRQ (Interrupt Request), для ISA-16 їхня кількість досягає 11. Зауважимо, що при конфігуруванні BIOS Setup частина цих запитів можуть відібрати пристрої системної плати або шина PCI.

Абоненти шини можуть використовувати до трьох 8-бітових каналів DMA ( D irect M emory A ccess - прямий доступ до пам'яті), а на 16-бітовій шині можуть бути доступними ще три 16-бітові канали. Сигнали 16-бітових каналів можуть використовуватись і для отримання прямого керування шиною пристроєм Bus-Master. При цьому канал DMA використовується для забезпечення арбітражу керування шиною, а адаптер Bus-Master формує всі адресні та керуючі сигнали шини, не забуваючи "віддати" керування шиною процесору не більше ніж через 15 мікросекунд (щоб не порушити регенерацію пам'яті).

Усі перелічені ресурси системної шинимають бути безконфліктно розподілені між абонентами. Безконфліктність має на увазі наступне:

Кожен абонент повинен при операціях читання керувати шиною даних (видавати інформацію) тільки за своїми адресами або за зверненням до каналу DMA, що використовується. Області адрес для читання не повинні перетинатися. "Підглядати" не йому адресовані операції запису не можна.

Призначену лінію запиту переривання IRQx абонент повинен тримати на низькому рівні в пасивному стані та переводити на високий рівень для активації запиту. Лініями запитів, що не використовуються, абонент керувати не має права, вони повинні бути електрично відкоммутовані або підключатися до буфера, що знаходиться в третьому стані. Однією лінією запиту може користуватися лише один пристрій. Така безглуздість (з погляду схемотехніки ТТЛ) була допущена в перших PC і в жертву сумісності старанно тиражується вже багато років.

Завдання розподілу ресурсів у старих адаптерах вирішувалося за допомогою джамперів, потім з'явилися програмно-конфігуровані пристрої, які практично витіснені платами PnP, що автоматично конфігуруються.

Для шин ISA ряд фірм випускає карти-прототипи (Protitype Card), що є друкованими платами повного або зменшеного формату з скобою. На платах встановлені обов'язкові інтерфейсні ланцюги - буфер даних, дешифратор адреси та інші. Решта поля плати є "сліпаком", на якому розробник може розмістити макетний варіант свого пристрою. Ці плати зручні для макетної перевірки нового виробу, а також для монтажу одиничних екземплярів пристрою, коли розробка та виготовлення друкованої плати є нерентабельним.

З появою 32-бітових процесорів робилися спроби розширення розрядності шини, але всі 32-бітові шини ISA є стандартизованими, крім шини EISA.

1.2 ШинаEISA

З появою 32-розрядних мікропроцесорів 80386 (версія DX) фірмами Compaq, NEC та рядом інших фірм була створена 32-розрядна шина EISA, повністю сумісна з ISA.

Шина EISA (Extended ISA) – жорстко стандартизоване розширення ISA до 32 біт. Конструктивне виконання забезпечує сумісність із нею та звичайних ISA-адаптерів. Вузькі додаткові контакти розширення розташовані між ламелями роз'єму ISA і нижче таким чином, що адаптер ISA, який не має додаткових ключових прорізів у крайовому роз'ємі, не дістає до них. Встановлення карток EISA у слоти ISA неприпустиме, оскільки її специфічні ланцюги потраплять на контакти ланцюгів ISA, внаслідок чого системна плата виявиться непрацездатною.

Розширення шини стосується не тільки збільшення розрядності даних та адреси: для режимів EISA використовуються додаткові сигнали керування, що забезпечують можливість застосування більш ефективних режимів передачі. У звичайному (не пакетному) режимі передачі за кожну пару тактів можна передати до 32 біт даних (один такт на фазу адреси, один - на фазу даних). Максимальну продуктивність шини реалізує пакетний режим (Burst Mode) – швидкісний режим пересилання пакетів даних без зазначення поточної адреси всередині пакета. Усередині пакета чергові дані можуть передаватися у кожному такті шини, довжина пакета може досягати 1024 байт. Шина передбачає і більш продуктивні режими DMA, за яких швидкість обміну може досягати 33 Мбайт/с. Лінії запитів переривань допускають використання, що розділяється, причому зберігається і сумісність з ISA-картами: кожна лінія запиту може програмуватися на чутливість як по перепаду, як в ISA, так і за низькому рівню. Шина допускає споживання кожною картою розширення потужності до 45 Вт, але повну потужність зазвичай не споживає жоден адаптер.

Кожен слот (максимум - 8) та системна плата можуть мати селективний дозвіл адресації вводу-виводу та окремі лінії запиту та підтвердження керування шиною. Арбітраж запитів виконує пристрій ISP (Integrated System Peripheral). Обов'язковою приналежністю системної плати з шиною EISA є енергонезалежна пам'ять конфігурації NVRAM, де зберігається інформація про пристрої EISA для кожного слота. Формат записів стандартизований, для модифікації конфігураційної інформації використовується спеціальна утиліта ECU (EISA Configuration Utility). Архітектура дозволяє при використанні програмно-конфігурованих адаптерів автоматично вирішувати конфлікти використання системних ресурсів програмним шляхом, але на відміну від специфікації PnP EISA не допускає динамічного реконфігурування. Усі зміни конфігурації можливі лише в режимі конфігурації, після виходу з якого потрібне перезавантаження комп'ютера. Ізольований доступ до портів вводу-виводу кожної картки під час конфігурування забезпечує просто: сигнал AEN, що дозволяє декодування адреси в циклі введення-виводу, на кожен слот приходить окремою лінією AENx, в цей час програмно-керованою. Таким чином можна окремо звертатися і до звичайним картам ISA, але це марно, оскільки карти ISA не підтримують обміну конфігураційною інформацією, передбаченого шиною EISA. На деяких ідеях конфігурування EISA зросла специфікація PnP для шини ISA (формат конфігураційних записів ESCD багато в чому нагадує NVRAM EISA).

EISA - дорога, але архітектура, що виправдовує себе, застосовується в багатозадачних системах, на файл-серверах і скрізь, де потрібно високоефективне розширення шини введення-виведення.

1.3 ШинаMCA

Шина MCA (MicroChannel Architecture) - мікроканальна архітектура - була введена в пік конкурентам фірмою IBM для своїх комп'ютерів PS/2 починаючи з моделі 50 в 1987 році. Забезпечує швидкий обмін даними між окремими пристроями, зокрема оперативної пам'яттю. Шина MCA абсолютно несумісна з ISA/EISA та іншими адаптерами. Склад керуючих сигналів, протокол та архітектура орієнтовані на асинхронне функціонування шини та процесора, що знімає проблеми узгодження швидкостей процесора та периферійних пристроїв. Адаптери MCA широко використовують Bus-Mastering, всі запити йдуть через пристрій CACP (Central Arbitration Control Point). Архітектура дозволяє ефективно та автоматично конфігурувати всі пристрої програмним шляхом (у MCA PS/2 немає жодного перемикача).

При всій прогресивності архітектури (щодо ISA) шина MCA не користується популярністю через вузькість кола виробників MCA-пристроїв та повну їх несумісність з масовими ISA-системами. Однак MCA ще знаходить застосування у потужних файл-серверах, де потрібне забезпечення високонадійного продуктивного вводу-виводу.

2. ЛОКАЛЬНІ ШИНИ

Розробники комп'ютерів, системні плати яких ґрунтувалися на мікропроцесорах 180386/486, стали використовувати роздільні шини для пам'яті та пристроїв введення-виведення, що дозволило максимально задіяти можливості оперативної пам'яті, оскільки саме в цьому випадку пам'ять може працювати з найвищою для неї швидкістю. Тим не менш, при такому підході вся система не може забезпечити достатньої продуктивності, так як пристрої, підключені через роз'єм розширення, не можуть досягти швидкості обміну, порівнянної з процесором. В основному це стосується роботи з контролерами накопичувачів та відеоадаптерами. Для вирішення проблеми стали використовувати так звані локальні (local) шини, які безпосередньо пов'язують процесор з контролерами периферійних пристроїв.

Перші IBM PC-сумісні комп'ютери з локальними шинами були, звичайно, стандартизовані. Одним із провідних виробників персональних комп'ютерів, що вперше реалізував відеопідсистему з локальною шиною, була компанія NECTechnologies. Ще 1991 року ця фірма представила свою оригінальну розробку Image Video.

Останнім часом з'явилися дві локальні шини, визнані промисловими: шина VLB, запропонована асоціацією VESA (Video Electronics Standards Association), та PCI (Peripheral Component Interconnect), розроблена фірмою Intel. Обидві ці шини призначені, взагалі кажучи, для того самого - для збільшення швидкодії комп'ютера, дозволяючи таким периферійним пристроям, як відеоадаптери і контролери накопичувачів, працювати з тактовою частотою до 33 МГц і вище. Обидві шини використовують роз'єм типу МСА. На цьому, втім, їхня схожість і закінчується, оскільки необхідна мета досягається різними засобами.

Якщо VL-bus є, по суті, розширенням шини процесора (згадаємо шину IBM PC/XT), то PCI по своїй організації більш тяжіє до системних шин, наприклад EISA, і є абсолютно нову розробку. Строго кажучи, PCI відноситься до класу так званих mezzanine-шин, тобто шин-"пристроїв", оскільки між локальною шиною процесора і самої PCI знаходиться спеціальна мікросхема "моста" (bridge).

2.1 ШинаVLB

Локальна шина стандарту VLB (VESA Local Bus, VESA – Video Equipment Standart Association – Асоціація стандартів відеообладнання) розроблена у 1992 році. Головним недоліком шини VLB є неможливість її використання з процесорами, що прийшли на заміну МП 80486 або існуючими паралельно з ним (Alpha, PowerPC та ін.).

Шини введення-виведення ISA, MCA, EISA мають низьку продуктивність, обумовлену їх місцем у структурі PC. Сучасні програми (особливо графічні) вимагають суттєвого підвищення пропускної спроможності, яке можуть забезпечити сучасні процесори. Одним із рішень проблеми підвищення пропускної здатності було застосування як шина підключення периферійних пристроїв локальної шини процесора 80486. Шину процесора використовували як місце підключення вбудованої периферії системної плати (контролер дисків, графічного адаптера).

VLB - стандартизована 32-бітна локальна шина, що практично є сигналами системної шини процесора 486, виведені на додаткові роз'єми системної плати. Шина сильно орієнтована на 486 процесор, хоча можливе її використання і з процесорами класу 386. Для процесорів Pentium була прийнята специфікація 2.0, в якій розрядність даних шини збільшена до 64, але вона поширення не отримала. Апаратні перетворювачі шини нових процесорів у шину VLB, будучи штучними "наростами" на шинній архітектурі, не прижилися і VLB подальшого розвитку не отримала.

Конструктивно VLB-слот аналогічний 16-бітному звичайному MCA-слоту, але є розширенням системного слота шини ISA-16, EISA або MCA, розташовуючись за ним поблизу процесора. Через обмежену здатність навантаження шини процесора більше трьох слотів VLB на системній платі не встановлюють. Максимальна тактова частота шини – 66 МГц, хоча надійніше шина працює на частоті 33 МГц. При цьому декларується пікова пропускна здатність 132 Мбайт/с (33 МГц x 4 байти), але вона досягається лише всередині пакетного циклу під час передачі даних. Реально в пакетному циклі передача 4 x 4 = 16 байт даних вимагає 5 тактів шини, так що навіть у пакетному режиміпропускна здатність становить 105.6 Мбайт/с, а звичайному режимі (такт на фазу адреси і такт на фазу даних) - всього 66 Мбайт/с, хоча це значно більше, ніж в ISA. Жорсткі вимоги до тимчасових характеристик процесорної шини при великому навантаженні (у т. ч. і мікросхемами зовнішнього кешу) можуть призвести до нестійкої роботи: всі три VLB-слоти можуть використовуватися тільки на частоті 40 МГц, при навантаженій системній платі на 50 МГц може працювати тільки один слот. Шина в принципі допускає застосування активних (Bus-Master) адаптерів, але арбітраж запитів покладається на самі адаптери. Зазвичай шина допускає встановлення не більше двох Bus-Master адаптерів, один з яких встановлюється в Master-слот.

Шину VLB зазвичай використовували для підключення графічного адаптера та контролера дисків. Адаптери локальних мереж для VLB мало зустрічаються. Іноді зустрічаються системні плати, які мають в описі зазначено, що вони мають вбудований графічний і дисковий адаптер з шиною VLB, але самих слотів VLB немає. Це означає, що на платі встановлені мікросхеми зазначених адаптерів, призначені для підключення до VLB шини. Така неявна шина за продуктивністю, звичайно, не поступається шині з явними слотами. З точки зору надійності та сумісності це навіть краще, оскільки проблеми сумісності карт та системних плат для шини VLB стоять особливо гостро.

2.2 ШинаPCI

Шина PCI (Peripheral Component Interconnect bus – взаємозв'язок периферійних компонентів) – шина з'єднання периферійних компонентів. Була анонсована компанією Intel у червні 1992 року на виставці PC Expo.

Ця шина займає особливе місце в сучасній PC-архітектурі (mezzanine bus), будучи мостом між локальною шиною процесора та шиною вводу-виводу ISA/EISA або MCA. Ця шина розроблялася в розрахунку на Pentium-системи, але добре поєднується і з 486 процесорами, а також з не-Intel"івськими процесорами. Шина PCI є чітко стандартизованою високопродуктивною шиною розширення вводу-виводу. 64-розрядна версія Частота шини 20-33 МГц Стандарт PCI 2.1 допускає і частоту 66 МГц Теоретична максимальна швидкість 132/264 Мбайт/с для 32/64 біт при 33 МГц і 528 Мбайт/с при 66 МГц. достатній для підключення адаптера (на відміну від VLB), на системній платі він може співіснувати з будь-якою з шин введення-виводу і навіть з VLB (хоча в цьому немає необхідності).

На одній шині PCI може бути не більше чотирьох пристроїв (слотів). Міст шини PCI (PCI Bridge) – це апаратні засоби підключення шини PCI до інших шин. Host Bridge – головний міст – використовується для підключення PCI до системної шини (шини процесора або процесорів). Peer-to-Peer Bridge – одноранговий міст – використовується для з'єднання двох шин PCI. Дві і більше шини PCI застосовуються в потужних серверних платформах - додаткові шини PCI дозволяють збільшити кількість пристроїв, що підключаються.

Автоконфігурація пристроїв (вибір адрес, запитів переривання) підтримується засобами BIOS і орієнтоване на технологію Plug and Play. Стандарт PCI визначає кожному слоту конфігураційний простір розміром до 256 восьмибітних регістрів, не приписаних ні простору пам'яті, ні простору ввода-вывода. Доступ до них здійснюється за спеціальними циклами шини Configuration Read і Configuration Write, що виробляються контролером при зверненні процесора до регістрів контролера шини PCI, розташованим у його просторі введення-виведення.

До складу PCI шини введені сигнали для тестування адаптерів за інтерфейсом JTAG. На системній платі ці сигнали не завжди задіяні, але можуть і організовувати логічний ланцюжок адаптерів, що тестуються.

Шина PCI всі обміни трактує як пакетні: кожен кадр починається фазою адреси, яку може йти одна чи кілька фаз даних. Кількість фаз даних у пакеті невизначена, але обмежена таймером, що визначає максимальний час, протягом якого пристрій може користуватися шиною. Кожен пристрій має власний таймер, значення якого задається при конфігуруванні пристроїв шини.

У кожному обміні беруть участь два пристрої - ініціатор обміну (Initiator) та цільовий пристрій (Target). Арбітражем запитів використання шини займається спеціальний функціональний вузол, що входить до складу чіпсету системної плати. Для узгодження швидкодії пристроїв-учасників обміну передбачено два сигнали готовності IRDY# та TRDY#. Для адреси та даних на шині використовуються загальні мультиплексовані лінії AD. Чотири мультиплексовані лінії C/BE використовуються для кодування команд у фазі адреси та дозволу байт у фазі даних.

Шина має версії з живленням 5, 3.3 В. Також існує універсальна версія (з перемиканням ліній +V I/O c 5 на 3.3 В). Ключами є пропущені ряди контактів 12, 13 і 50, 51. Для 5-слота ключ розташований на місці контактів 50, 51; для 3 - 12, 13; для універсального - два ключі: 12, 13 та 50, 51. Ключі не дозволяють встановити карту в слот з невідповідною напругою живлення. 32-бітовий слот закінчується контактами A62/B62, 64-бітовий – A94/B94.

На відміну від адаптерів інших шин, компоненти карток PCI розташовані на лівій поверхні плат. Тому крайній PCI-слот зазвичай поділяє використання посадкового місця адаптера з сусіднім ISA-слотом (Shared slot).

Шина PCI була до останнього часу другою (після ISA) за популярністю застосування. У сучасних системах відмова від шин ISA, і шина PCI виходить на головні позиції. Деякі фірми для цієї шини випускають карти-прототипи, але, звичайно, доукомплектувати їх периферійним адаптером або пристроєм власної розробки набагато складніше, ніж карту ISA. Тут позначаються і складніші протоколи, і більше високі частоти(8 МГц у шини ISA проти 33 або 66 МГц у шини PCI). Також шина PCI має погану стійкість до перешкод, тому для побудови вимірювальних систем і промислових комп'ютерів використовується все ще відносно рідко.

На деяких системних (материнських) платах є невеликий роз'єм, який називається Media Bus. Він розташований за роз'ємом шини PCI одного зі слотів. На цей роз'єм виводяться сигнали звичайної шини ISA, і він призначений для того, щоб на графічному адаптері з шиною PCI можна було розмістити і недорогий чіпсет звукової карти, призначений для шини ISA. Цей роз'єм, а тим більше й такі комбіновані аудіо-відео карти, широкого поширення не набули.

ВИСНОВОК

З самого розвитку й досі шина вводу/виводу є вузьким місцем сучасних персональних комп'ютерів, що негативно позначається на загальних швидкісних характеристиках системи. З'являлися нові шини, збільшувалася розрядність, швидкодія шин, їхня пропускна здатність. Але розробки нових стандартів шин продовжуються. Багато фірм поєднують свої зусилля для розробки нових стандартів.

На прикладах існуючих стандартів видно, що кожен стандарт шин має свої переваги, але є й недоліки. Одні шини дозволяють отримувати цілком задовільну швидкодію, але дуже дорогі і складні у виготовленні, і витрати не часто окупаються. Інші дешеві, але дуже вимогливі до системи загалом.

Список використаних джерел

1. Інформатика: Практикум з технології робіт на комп'ютері: Навчальний посібникдля вузів/За ред. Н.В. Макарової. - М.: Фінанси та статистика, 1997. - 384 с.

2. Могильов А.В. та ін Інформатика: Навчальний посібник для студентів пед. вузів/А.В. Могильов, Н.І. Пак - М.: Академія, 1999. - 816 с.

3. Острейковський В.А. Інформатика: Підручник для технічних вишів - М.: Вища школа, 1999. - 511 с.

4. Інформатика: Базовий курс: Навчальний посібник для втузів/Под ред С.В. Симоновича - СПб. : Пітер, 2003. - 640 с.

5. Хохлова Н.В. та ін. Інформатика: Навчальний посібник для вузів/Н.В. Хохлова, А.І. Істеменко, Б.В. Петренко. - М.: Вища школа, 1990. - 195 с.

Шини розподіляються на ряд локальних шин, шкірна... такої мікросхеми. Крім того, відновлення стандартів периферії відбувається дуже часто.

Сучасні обчислювальні системихарактеризуються:

□ стрімким зростаннямшвидкодії мікропроцесорів та деяких зовнішніх пристроїв (так, для відображення цифрового повноекранного відео з високою якістю потрібна пропускна здатність 22 Мбайт/с);

□ появою програм, що вимагають виконання великої кількості інтерфейсних операцій (наприклад, програми обробки графіки у Windows, мультимедіа).

У умовах пропускної спроможності шин розширення, обслуговуючих одночасно кілька пристроїв, виявилося замало комфортної роботи користувачів, оскільки комп'ютери стали довго «замислюватися». Розробники інтерфейсів пішли шляхом створення локальних шин, що підключаються безпосередньо до шини МП, що працюють на тактовій частоті МП (але не на внутрішній робочій його частоті) і забезпечують зв'язок з деякими швидкісними зовнішніми по відношенню до МП пристроями: основний і зовнішньою пам'яттю, відеосистемами і т.д.

Зараз існують три основні стандарти універсальних локальних шин: VLB, PCI та AGP.

Шина VLB(VL-bus, VESA Local Bus)представлена в 1992 році асоціацією стандартів відеоелектроніки (VESA – торгова марка Video Electronics Standards Association) і тому часто її називають шиною VESA. Шина VLB, по суті, є розширенням внутрішньої шиниМП для зв'язку з відеоадаптером та рідше - з жорстким диском, платами мультимедіа, мережним адаптером. Розрядність шини для даних – 32 біти, для адреси – 30, реальна швидкість передачі даних за VLB – 80 Мбайт/с, теоретично досяжна – 132 Мбайт/с (у версії 2 – 400 Мбайт/с).

Недоліки шини VLB:

□ орієнтація лише на МП 80386, 80486 (не адаптована для процесорів класу Pentium);

□ жорстка залежність від тактової частотиМП (кожна шина VLB розрахована лише з конкретну частоту до 33 МГц);

□ мала кількість пристроїв, що підключаються - до шини VLB може підключатися тільки 4 пристрої;

□ відсутній арбітраж шини - можуть бути конфлікти між пристроями, що підключаються.

Шина PCI(Peripheral Component Interconnect,з'єднання зовнішніх компонентів) - найпоширеніший та універсальний інтерфейс для підключення різних пристроїв. Розроблена у 1993 році фірмою Intel. Шина PCI є більш універсальною, ніж VLB; допускає підключення до 10 пристроїв; має свій адаптер, що дозволяє їй налаштовуватися працювати з будь-яким МП від 80486 до сучасних Pentium. Тактова частота PCI - 33 МГц, розрядність - 32 розряду для даних і 32 розряду для адреси з можливістю розширення до 64 біт, теоретична пропускна здатність 132 Мбайт/с, а 64-бітовому варіанті - 264 Мбайт/с. Модифікація 2.1 локальної шини PCI працює на тактовій частоті до 66 МГц і за розрядності 64 має пропускну здатність до 528 Мбайт/с. Здійснено підтримку режимів Plug and Play, Bus Mastering та автоконфігурування адаптерів.

Конструктивно роз'єм шини на системній платі складається із двох наступних поспіль секції по 64 контакти (кожна зі своїм ключем). За допомогою цього інтерфейсу до материнської плати підключаються відеокарти, звукові карти, модеми, контролери SCSI та інші пристрої Як правило, на материнській платі є кілька роз'ємів PCI. Шина PCI, хоч і є локальною, виконує і багато функцій шини розширення. Шини розширення ISA, EISA, MCA (а вона сумісна з ними) за наявності шини PCI підключаються не безпосередньо до МП (як це має місце при використанні шини VLB), а до самої шини PCI (через інтерфейс розширення). Завдяки такому рішенню шина є незалежною від процесора (на відміну від VLB) і може працювати паралельно з шиною процесора, не звертаючись до неї за запитами. Таким чином, завантаження шини процесора суттєво знижується. Наприклад, процесор працює з системною пам'яттю або з кеш-пам'яттю, а в цей час по мережі жорсткий дискпишеться інформація. Конфігурація системи з шиною PCI показано на рис. 5.8.

Шина AGP(Accelerated Graphics Port -прискорений графічний порт) – інтерфейс для підключення відеоадаптера до окремої магістралі AGP, що має

Глава 5. Мікропроцесори та системні плати

вихід безпосередньо на системну пам'ять. Розроблено шину на основі стандарту PCI v2.1. Шина AGP може працювати з частотою системної шини до 133 МГц та забезпечує найвищу швидкістьпередачі графічних даних Її пікова пропускна здатність у режимі чотириразового множення AGP4x (передаються 4 блоки даних за один такт) має величину 1066 Мбайт/с, а в режимі восьмикратного множення AGP8x – 2112 Мбайт/с. Порівняно з шиною PCI, у шині AGP усунуто мультиплексованість ліній адреси та даних (у PCI для здешевлення конструкції адресу та дані передаються по одних і тих же лініях) та посилено конвеєризацію операцій читання-запису, що дозволяє усунути вплив затримок у модулях пам'яті на швидкість виконання цих операцій.

Мал. 5.8. Конфігурація системи із шиною PCI

Шина AGP має два режими роботи: DMAі Execute.У режимі DMAосновною пам'яттю є пам'ять відеокарти. Графічні об'єктизберігаються в системній пам'яті, але перед використанням копіюються в локальну пам'ятькартки. Обмін проводиться великими послідовними пакетами. У режимі Execute системна пам'ять і локальна відеокарта логічно рівноправні. Графічні об'єкти не копіюються в локальну пам'ять, а вибираються безпосередньо із системної. При цьому доводиться вибирати з пам'яті відносно малі, випадково розташовані шматки. Оскільки системна пам'ять виділяється динамічно, блоками по 4 Кбайт, у цьому режимі для забезпечення прийнятної швидкодії передбачено механізм, що відображає послідовні адреси фрагментів на реальні адреси 4-кілобайтових блоків у системній пам'яті. Ця процедура виконується за допомогою спеціальної таблиці (Graphic Address Re-mapping Table або GART), розташованої у пам'яті. Інтерфейс виконаний у вигляді окремого роз'єму, який встановлюється AGP-відео-адаптер. Конфігурація системи із шиною AGP показана на рис. 5.9.

Внутрішньомашинні системний та периферійні інтерфейси

Мал. 5.9. Конфігурація системи із шиною AGP

Все вищесказане щодо шин узагальнюється в табл. 5.4. Таблиця 5.4. Основні характеристики шин

Шина є невід'ємною частиною материнської плати, на якій розташовуються роз'єми (слоти) для підключення плат адаптерів пристроїв (відеокарти, звукові карти, внутрішні модеми, накопичувачі інформації, пристрої введення-виводу і т. д.) і розширень базової конфігурації (додаткові роз'єми, що порожні) . Зовні вона не проглядається, а знаходиться між текстолітовими пластинами материнської плати.

Як зазначалося раніше, на продуктивність комп'ютерної системи загалом великий вплив має системна шина. Шини – це артерії, якими передаються електричні сигнали. Строго кажучи, це канали зв'язку, які застосовуються організації взаємодії між пристроями комп'ютера. А ті роз'єми, в які встановлюються плати розширення, підтримуються локальними шинами або інтерфейсами. Ці роз'єми виконані як слотів, і з допомогою здійснюється підключення додаткових пристроїв (компонентів) через локальні шини, яких, як і системну шину, немає на материнських платах. Схематично структура взаємозв'язку шин відбито на рис. 9.

Дамо характеристику шинам, які є на материнській платі. Основною вважається системна шина FSB (Front Side Bus). По цій шині передаються дані між процесором та оперативною пам'яттю, а також між процесором та іншими пристроями персонального комп'ютера. Ось тут є один підводний камінь. Справа в тому, що є головна шина, шина процесора. Одні автори стверджують, що системна шина та шина процесора це одне й те саме, а інші – ні. Більшість приходять до висновку: спочатку процесор підключався до основної системної шини через власну, процесорну, шину, в сучасних системах ці шини стали одним цілим. Ми говоримо: "системна шина", а маємо на увазі процесорну, ми говоримо: "процесорна шина", а маємо на увазі системну. Фраза: "материнська плата працює на частоті 100 МГц" означає, що саме системна шина працює на тактовій частоті 100 МГц. Розрядність FSB дорівнює розрядності CPU. Якщо використовується 64-розрядний процесор, а тактова частота системної шини 100 МГц, швидкість передачі даних дорівнюватиме 800 Мбайт/сек (що і наведено нижче в розрахунках).

Існує три основні показники роботи шини. Це тактова частота, розрядність та швидкість передачі даних.

Тактова частота.Чим вище тактова частота системної шини, тим швидше здійснюватиметься передача інформації між пристроями і, як наслідок, збільшиться загальна продуктивність комп'ютера, тобто підвищиться швидкість передачі даних і, отже, швидкодія комп'ютера.

Тактова частота, стосовно персональних комп'ютерів, вимірюється в МГц, де герц – це одне коливання за секунду, відповідно 1 МГц – мільйон коливань за секунду. Теоретично, якщо системна шина комп'ютера працює на частоті 100 МГц, то вона може виконувати до 100 000 000 операцій на секунду. Зовсім не обов'язково, щоб кожен компонент системи обов'язково виконував що-небудь з кожним тактом. Існують так звані порожні такти (цикли очікування), коли пристрій знаходиться в процесі очікування відповіді від будь-якого іншого пристрою. Персональні комп'ютери класу Pentium I оснащувалися материнськими платами з допомогою частоти системної шини 33 МГц, Pentium II - 66 МГц, Pentium III – 133 МГц. Сучасні материнські плати підтримують роботу системної шини на частотах 400, 533, 800, 1066 і навіть 1600 МГц.

Розрядність.Шина складається з кількох каналів передачі електричних сигналів. Якщо шина тридцятидворозрядна, це означає, що вона здатна передавати електричні сигнали по тридцяти двох каналах одночасно. Шина будь-якої заявленої розрядності (8, 16, 32, 64) має насправді б ольша кількість каналів. Тобто, якщо взяти ту ж тридцятидворозрядну шину, то для передачі власне даних виділено 32 канали, а додаткові каналипризначені передачі специфічної інформації, наприклад сигналів управління.

Швидкість передачі даних.Назва цього параметра говорить сама за себе. Він вираховується за формулою

тактова частота * розрядність = швидкість передачі.

Зробимо розрахунок швидкості передачі даних для 64-розрядної системної шини, що працює на тактовій частоті 100 МГц.

100*64 = 6400 Мбіт/сек;

6400/8 = 800 Мбайт/сек.

Але отримана кількість не є реальною. У житті на шини впливають різні чинники: неефективна провідність матеріалів, перешкоди, недоліки конструкції та складання, а також багато іншого. За деякими даними, різниця між теоретичною швидкістю передачі даних та практичною може становити до 25%.

Крім системної шини на материнській платі є ще шини введення-виводу, які відрізняються одна від одної з архітектури. Вони отримали назву локальні.

У персональних комп'ютерах різних поколінь використовувалися шини стандартів ISA, EISA, VESA, VLB та PCI. ISA, EISA, VESA і VLB, нині вони є застарілими і випускаються на сучасних материнських платах. Сьогодні всі материнські плати базуються на шині PCI.

Усі стандарти розрізняються як за кількістю та використання сигналів, так і за протоколами їх обслуговування.

ISA (Industrial Standard Architecture – промислова стандартна архітектура). Перша 8-розрядна шина ISA з'явилася в 1981 році, а в 1984 з'явився її 16-розрядний варіант. Перші шини ISA фактично були єдиним типом, але потім розрізнялися за тактовою частотою 8 МГц і 16 МГц. Слід зазначити, що шини ISA практично 10 років були єдиними на материнських платах і досі зустрічаються на деяких із них. До 1987 року IBM відмовлялася публікувати повний опис ISA, багато виробників заліза зважилися на розробку власних шин. Так з'явилася 32-розрядна ISA, яка не знайшла застосування, але фактично зумовила появу шин наступних поколінь MCA та EISA. 1985 року фірма Intelрозробила 32-розрядний 80386 процесор, який побачив світ наприкінці 1986 року. З'явилася нагальна необхідність у 32-розрядній шині введення-виводу. Замість того щоб продовжити подальшу розробку ISA, в IBM створили нову шину MCA (Micro Channel Architecture - мікроканальна архітектура), яка в усіх відношеннях перевершувала свою попередницю. Але цей стандарт проіснував недовго, і незабаром фірмою Compaq було розроблено нову шину EISA.

EISA (Extended Industry Standard Architecture – розширена промислова стандартна архітектура). Основна її відмінність полягала в 32-розрядній технології, що призвело до збільшення швидкості обміну даними. При цьому було збережено сумісність із платами, розрахованими для роботи з ISA. Швидкість передачі вже дорівнювала 33 Мбайт/сек. Але, як і раніше, внутрішня тактова частота залишилася низькою - 8,33 МГц. З підвищенням тактових частот і розрядності процесорів настала нагальна проблема підвищення швидкості передачі у шинах. У 1992 році з'явився ще один розширений варіант ISA – VLB (VESA Local Bus) – Video Electronic Standard Association. VLB була локальною шиною, яка не змінювала, а доповнювала наявні стандарти. Просто до основних шин додавали кілька нових швидкодіючих локальних слотів. Популярність шини VLB тривала до 1994 року. Швидкість передачі VLB дорівнювала 128 – 132 Мбайт/сек, а розрядність –32. Тактова частота досягала 50 МГц, але реально не перевищувала 33 МГц у зв'язку із частотними обмеженнями самих слотів. Основна функція, для якої була призначена нова шина – обмін даними з відеоадаптером. Але нова шина мала низку недоліків, які дозволили їй довго проіснувати над ринком.

1991 року почалися розробки нової локальної шини PCI. PCI (Peripheral Component Interconnect bus) – шина сполучення периферійних компонентів. І в червні 1992 року з'явився цей новий стандарт- PCI (2.0), розробником якого була фірма Intel спільно з іншими компаніями Compaq, HP та ін. Це була своєрідна революція. Різноманітність плат розширення, що використовують шину PCI, була великою. Тактова частота шини PCI дорівнювала 33 МГц і 66 МГц. Розрядність – 32 або 64. Швидкість передачі – 132 Мбайт/сек чи 264 Мбайт/сек. Шина PCI забезпечує самоконфігурованість периферійного (додаткового) обладнання - підтримку стандарту Plug and Play, що виключає ручну конфігурацію апаратних параметрів периферійного обладнання при його зміні або нарощуванні. Операційна система, що підтримує цей стандарт, сама налаштовує обладнання, підключене по шині PCI без втручання користувача.

Постійне вдосконалення відеокарт призвело до того, що фізичних параметрів шини PCI стало не вистачати, що призвело до появи в 1996 р. AGP. До 1997 року графічна підсистемасильно навантажувала шину PCI. Випуск разом із чіпсетом Intel 440LX прискореного графічного порту AGP (Accelerated Graphics Port) послужив двом цілям: збільшити графічну продуктивністьта прибрати графічні дані з шини PCI. Оскільки графічна інформація почала передаватися по іншій "шині", перевантажена шина PCI змогла звільнитися для роботи з іншими пристроями.

На материнській платі цей порт існує у єдиному вигляді. Ні фізично, ні логічно не залежить від PCI. Перший стандарт AGP 1.0 з'явився 1997 року завдяки інженерам фірми Intel. Цій специфікації відповідала тактова частота 66 МГц. Наступна версія, AGP 2.0, з'явилася на світ у 1998 році та швидкість передачі даних – 533 Мбайт/сек (2х) та 1066 Мбайт/сек (4х). Останньою версією AGP стала AGPх8 (2004-2005рр.). Основним (базовим) режимом AGP є 1х. У цьому режимі відбувається одиночна передача даних кожного циклу. У режимі 2-х передача відбувається двічі за цикл, у режимі 4-х передача даних відбувається чотири рази за кожен цикл, і так далі. Ширина лінії пропускання AGP 1.0 – 32 біта. Великим досягненням AGP є те, що ця специфікація дозволяє отримати швидкий доступдо оперативної пам'яті.

Однак AGP став лише першим кроком у справі зменшення навантаження шини PCI. Шина PCI Express, раніше відома як шина введення-виведення третього покоління (3rd Generation I/O, 3GIO), покликана замінити шину PCI і взяти на себе завдання щодо зв'язку компонентів усередині комп'ютера на найближчі десять років.

Що стосується вартості впровадження, то нова шина покликана відповідати рівню PCI або навіть бути нижчою за нього. Послідовна шина потребує наявності меншого числапровідників на друкованій платі, полегшуючи дизайн плати та збільшуючи його ефективність – адже місце, що звільнилося, можна використовувати для інших компонентів.

Шина підтримує сумісність з PCI на програмному рівні, тобто існуючі операційні системи завантажуватимуться без будь-яких змін. Крім того, конфігурація та драйвери пристроїв PCI Express будуть сумісні з наявними PCI-варіантами.

Однією з найбільш вражаючих функцій PCI Express є можливість масштабування швидкості, використовуючи кілька ліній передачі. Фізичний рівеньпідтримує ширину шини X1, X2, X4, X8, X12, X16 та X32 ліній. Передача кількома лініями прозора інших шарів.

Оскільки PCI Express забезпечує швидкість передачі 200 Мбайт/с вже за ширини X1, шина є дуже ефективним рішеннямпо відношенню вартість/число контактів. Шин PCI Express х16 дозволяє досягти пропускної спроможності 4 Гбайт/с у кожному напрямку (сумарна пропускна спроможність 8 Гбайт/с) для графіки, що більш ніж удвічі більше пропускної спроможності AGP 8X.

Іншими словами, специфікація описує кілька видів з'єднань та роз'ємів: PCI Express 1x, 4x, 8x, 16x. Перший складається з однієї так званої Lane. Останній – із шістнадцяти. Відповідно, пропускна здатність першого становить 500 Мбайт/с в обидві сторони, а останнього – 8 Гбайт/с (по 4 Гбайт/с у кожну сторону). При цьому всі 20 наявних груп Lane можуть бути довільним чином розподілені між роз'ємами 1х, 4х, 8х і 16х. Роз'єми сумісні знизу вгору, тобто PCI Express 1х карту можна вставити в роз'єм PCI Express 4х, 8х, або 16х. Але не навпаки. Залишається додати, що на настільних ПК в основному застосовуються шини 1х та 16х. Слід також звернути увагу на зменшення габаритів PCI Express у порівнянні просто з PCI. на початкових етапах PCI Express був призначений для підключення відеокарти, які були досить дорогими (400 $ і більше). В даний час відеокарти нижчого та середнього цінового діапазону для шини PCI Express стали доступними. І виробники інших компонент комп'ютера починають активно розробляти нові пристрої під цю шину. І як вказується в прогнозах, щонайменше на 10 років шина PCI Express буде основною для підключення внутрішніх пристроїв ПК і поступово витисне шину PCI.

Чіпсет

Як можна було переконатися з прикладу системної і локальних шин, материнська плата досить складним пристроєм і включає наступний важливий компонент – чіпсет. Від чіпсету безпосередньо залежать усі основні характеристики материнської плати, а отже, і конструюється на її базі комп'ютерної системи.

Чіпсет є основою будь-якої материнської плати. Фактично функціональність материнської плати та її продуктивність на 90% визначаються саме чіпсетом, від якого залежать підтримуваний тип процесора, тип пам'яті, а також функціональні можливостіщодо підключення периферійних пристроїв.

Чіпсет – це набір мікросхем системної логіки(Називають скорочено НМС або МСЛ). Загальновідомо, що персональний комп'ютер складається з деякої кількості пристроїв, які так чи інакше підключені до материнської плати та займаються тим, що приймають, обробляють та передають будь-яку інформацію. Логічною організацією всієї цієї роботи займаються чіпсети. На перших поколіннях ПК, коли НМС ще існувало, материнські плати несли у собі до ста мікросхем, які займалися логічною організацією роботи окремих пристроїв, що було вкрай незручно. Ось деякі з них: контролери переривань, контролер прямого доступу, контролер клавіатури, годинник, системний таймер, контролер шин та інше. Таке становище проіснувало до 1986 року, коли фірма Chip and Technologies запропонувала справді революційне рішення. Мікросхема називалася 82С206 та стала основною частиною набору мікросхем системної логіки. Вона виконувала такі функції, як:

Контролер шин;

Генератор тактової частоти;

Системний таймер;

Контролер переривань;

Контролер прямого доступу до пам'яті;

З появою процесора i80486 окремі мікросхеми стали об'єднувати в одну-дві великі мікросхеми, які отримали найменування чіпсету. У буквальному перекладі чіпсет означає «набір мікросхем». Чіпсет, який також називають набором системної логіки, - це одна або найчастіше дві мікросхеми (чіпи), призначені для організації взаємодії між процесором, пам'яттю, портами вводу-виводу та іншими компонентами комп'ютера.

З появою шини PCI окремі мікросхеми чіпсету стали називати мостами - так з'явилися терміни: північний міст (North Bridge) і південний міст (South Bridge) чіпсету, при цьому північний міст з'єднується безпосередньо з процесором, а південний - з північним. У деяких випадках виробники поєднують північний і південний міст в одну мікросхему, і таке рішення називають одночіповим, а якщо мікросхеми дві, то це двомостова схема.

У північний міст чіпсету традиційно включені контролер оперативної пам'яті (за винятком чіпсетів для процесорів з архітектурою AMD64), контролер графічної шини (AGP або PCI Express x16), інтерфейс взаємодії із південним мостом та інтерфейс взаємодії з процесором. У деяких випадках північний міст чіпсету може містити додаткові лінії PCI Express x1 для організації взаємодії з картами розширення, що мають відповідний інтерфейс.

На південний міст чіпсету покладається функція організації взаємодії з пристроями вводу-виводу. Південний міст містить контролери жорсткихдисків (SATA та/або PATA), USB-контролер, мережевий контролер, контролер PCI-шини та PCI-Express-шини, контролер переривання та DMA-контролер. Також у південний міст зазвичай вбудовується звуковий контролер, і в цьому випадку ще потрібна зовнішня до чіпсета мікросхема кодека. Крім того, південний міст з'єднується з ще двома важливими мікросхемами на материнській платі: мікросхемою ROM-пам'яті BIOS і мікросхемою Super I/O, що відповідає за послідовні та паралельні порти та за флоппі-дисковод.

Для з'єднання північного та південного мостів один з одним використовується спеціальна виділена шина, причому різні виробникивикористовують для цього різні шини (з різною пропускною здатністю):

· Intel-DMI (Direct Media Interface),

· VIA Technologies (основний виробник для процесорів AMD)-V-Link;

· SiS (Silicon Integrated System Corporation) - MuTIOL;

· ATI-HyperTransport, PCI Express;

· NVIDIA-HyperTransport.

Як правило, назва чіпсету збігається з назвою північного мосту, хоча більш правильною є вказівка саме сукупності північного та південного мостів, оскільки в багатьох випадках один і той самий північний міст чіпсета може поєднуватися з різними варіантами південних мостів.

Вибір чіпсетів сьогодні дуже великий. І якщо процесори випускають лише дві компанії - Intel і AMD-, то чіпсети виробляють і Intel, і VIA, і SiS, і NVIDIA, і ATI, і ULi.

Розглянемо деякі особливості сучасних чіпсетів компанії Intel. Сьогодні компанія Intelвипускає дуже різноманітний спектр чіпсетів для процесорів Intel Pentium D, Intel Pentium 4 та Intel Celeron D. У 2004-2005рр. застосовувалося сімейство Intel 915, Intel 925, 2006 р. – Intel 945. Разом з новими процесорами Intel Pentium Extreme Edition 8хх та Intel Pentium D компанія Intel представила і новий чіпсет Intel 955X Express (кодова назва Glenwood). Всі ці чіпсети призначені для корпусу мікропроцесора LGA775.

Чіпсет Intel 955X Express є на сьогодні старшою моделлю та логічним продовженням чіпсетів серії Intel 945, Intel 925X Express. Він може підтримувати двоядерний процесор Intel Pentium Extreme Edition 8хх із частотою FSB 800 МГц або одноядерний процесор Intel Pentium 4 Extreme Edition із частотою FSB 1066 МГц та звичайні процесори Intel Pentium 4. Для процесора Intel Pentium D призначений чіпсет Intel 945X Express. А тепер перерахуємо основні особливості набору системної логіки Intel 955X Express (рис. 10) порівняно з попередніми серіями.

Контролер пам'яті цього чіпсету підтримує пам'ять DDR2-667 двоканальному режимі, А шина пам'яті має пропускну здатність 8,5 Гбайт/с. Усього підтримується до 8 Гбайт пам'яті, причому реалізовано підтримку пам'яті з ECC. Крім того, в контролері пам'яті реалізовано технологію оптимізації продуктивності пам'яті (Performance Memory Optimizations).

Для сумісності з процесорами Intel Pentium 4 Extreme Edition частота FSB може бути як 800, і 1066 МГц. Особливістю північного мосту чіпсету Intel 955X Express є також підтримка двох графічних шин із зовнішнім мостом, що забезпечує два фізичні слота PCI Express x16. Південний міст чіпсету ICH7 - це нова версія вже добре знайомого контролера вводу-виводу ICH6. Серед функціональних особливостей – підтримка чотириканального SATA RAID-контролера, восьмиканального аудіоформату Intel High Definition Audio, PCI-шини та шести слотів шини PCI Express x1.

Чіпсети розробляються під конкретні покоління процесорів та конкретні моделі процесорів. Так, наприклад, компанії VIA Technologies, NVIDIA, SiS більшою мірою розробляють чіпсети для процесорів AMD. А фірма Intel, природно, працює на власний модельний ряд Pentium 4. Основні характеристики чіпсетів Intel відображені у табл. 5. Як видно, чим старший модельний ряд, тим великі можливостіза продуктивністю та функціональністю закладені в них. Підтримка високошвидкісних шин (FSB 800/1066 МГц), сучасний процесорний роз'єм (LGA 775), швидка та великої ємностіпам'яті (DDR2), збільшена кількість USB портів, високошвидкісні інтерфейси вінчестера (SATA II) та інші.

Мал. 10. Структурна схемачіпсету Intel 955X Express

BIOS (Basic Input/Output System - базова система введення-виведення) - це вбудоване в комп'ютер на чіпі програмне забезпечення, яка доступна на першому етапі без звернення до диска. Воно являє собою набір програм перевірки та обслуговування апаратури комп'ютера, зокрема необхідних для управління клавіатурою, відеокартою, дисками, портами та званим «холодним» завантаженням) та скиданням («гарячим» завантаженням) системної плати, тестує саму плату та основні блоки комп'ютера - відеоадаптер , клавіатуру, контролери дисків і портів введення-виведення, налаштовує чіпсет і передає управління завантажувачу операційної системи. Приклад мікросхеми BIOSа представлений на рис. 11.

Мал. 11. Мікросхема BIOSа компанії American Megatrends Inc (AMI).

Таблиця 5

Основні характеристики чіпсетів для мікропроцесорів Intel

По суті, BIOS – це набір драйверів (драйвер – програма управління пристроєм), що забезпечують роботу системи під час запуску комп'ютера або завантаження безпечному режимі. При включенні живлення комп'ютера ще до завантаження ОС можна керувати ним з клавіатури, бачити всі дії на моніторі. Крім цього, якщо завантаження відбувається у безпечному режимі, то здійснюється відмова від драйверів операційної системи та в роботі залишаються лише драйвера BIOS.

При роботі під операційними системами DOSі Windows 9x BIOS також керувала основними пристроями, тобто виступала посередником між операційною системою та апаратурою комп'ютера. При роботі під Windows NT/2000/XP, різновидами UNIX, OS/2 та іншими альтернативними ОС BIOS практично не використовується, виконуючи лише початкову перевірку та налаштування.

BIOS складається з наступних частин:

1. POST (Power On Self Test) – програма, відповідальна за тестування апаратних засобів комп'ютера при включенні живлення.

2. System Setup – програма налаштування системи.

3. Набір програм управління роботою апаратури ПК.

BIOS, взагалі кажучи, унікальний кожної моделі материнської плати комп'ютера, тобто він розробляється з урахуванням особливостей функціонування тієї комбінації устаткування, яка характерна саме цієї моделі.

BIOS для сучасних системних плат розробляється найчастіше однією з фірм, що спеціалізуються на цьому. Award Software (що поглинула Phoenix Technology – одного з найвідоміших у минулому виробників BIOS), American Megatrends Inc. ( AMI), Microid Research. В даний час найбільш популярним є Award BIOS. Деякі виробники материнських плат – Intel, IBM або Acer – самі розробляють BIOS для своїх плат. Вони або суттєво розширюють набір налаштувань або (як у випадку з Intel), навпаки, обмежують кількість налаштувань лише мінімально необхідними.

Спочатку BIOS розміщувалася в мікросхемі ПЗУ (постійний пристрій - ROM, Read-Only Memory: тільки для читання), розміщеній на материнській платі комп'ютера. Ця технологія дозволяє BIOS завжди бути доступною, незважаючи на пошкодження, наприклад, дискової системи. Це також дозволяє комп'ютеру самостійно завантажуватись з інших носіїв. Оскільки доступ до оперативної пам'яті здійснюється значно швидше, ніж ПЗУ, виробники комп'ютерів створювали системи таким чином, щоб при включенні комп'ютера виконувалося копіювання BIOS з ПЗУ в оперативну пам'ять. Задіяна у своїй область пам'яті називається тіньової пам'яттю.

У всіх сучасних платах BIOS зберігається в електрично перепрограмованих ПЗП (Flash ROM), які допускають перепрошивку BIOSзасобами самої плати за допомогою спеціальної програми. Це дозволяє виправляти заводські помилки в BIOS, змінювати заводські умовчання, вносити інші зміни, оновлювати BIOS під нові материнські плати чи компоненти комп'ютера.

Однак, крім явних плюсів у цій технології є й слабкі сторони. Наприклад, зараз існує група вірусів, які, користуючись можливістю змінювати вміст BIOS, стирають або змінюють його і таким чином роблять комп'ютер непрацездатним. Через неправильний або відсутній BIOS комп'ютер відмовляється завантажуватися. Виправити таку ситуацію можна тільки в сервісному центрі, де у спеціальному пристрої – програматорі – на мікросхему Flash ROM буде записана вихідна версія BIOS. Наприклад, відомий вірусЧорнобиль, епідемія якого була 26 квітня 1999 р., знищив мільйони BIOS по всьому світу. Після цієї епідемії деякі виробники стали постачати свої материнські плати двома копіями BIOS. У разі пошкодження основної копії завантажується вміст резервної мікросхеми. Однак такі плати трапляються досить рідко.

Свої установки BIOS зберігає в так званій CMOS RAM. CMOS RAM називається так тому, що вона виконана на основі CMOS-структур (CMOS – Complementary Metal Oxide Semiconductor), які відрізняються малим енергоспоживанням. CMOS-пам'ять є незалежною тільки тому, що постійно живиться від акумулятора, розташованого на системній платі. У той час, коли комп'ютер увімкнено, CMOS RAM живиться від блока живлення комп'ютера. Енергоспоживання CMOS RAM настільки мало, що навіть при вимкненому комп'ютері та відсутня батареяїї вміст може зберігатися понад добу лише рахунок залишкових зарядів на конденсаторах блока живлення.

У CMOS RAM зберігається інформація про поточні показання годинника, значення часу для будильника, конфігурацію комп'ютера: кількість пам'яті, типи накопичувачів і т. д. У разі пошкодження мікросхеми CMOS RAM (а також розряд батареї або акумулятора) BIOS має можливість скористатися налаштуваннями за замовчуванням.

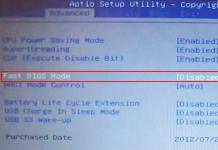

Загальний принцип, якого слід дотримуватись: якщо комп'ютер працює стабільно і жодних недоліків у його роботі, пов'язаних з BIOS, не виявлено, то оновлювати BIOS не слід.

Однак існують ситуації, коли оновлення BIOS потрібне. Зазвичай це вихід нового процесора, підтримка якого не була закладена в попередній версії. Перш ніж встановлювати нову версію, потрібно відправитися на сайт технічної підтримкифірми-виробника системної плати, прочитати специфікації нової версії BIOS і за необхідності завантажити їх, упевнившись, що ця версія виправляє саме ті недоліки, які були виявлені у вашому комп'ютері.

При включенні комп'ютера на процесор подається напруга живлення, і він прокидається. Першими прочитаними процесором командами є інструкції із чіпа BIOS (про це дбають мікросхеми системної плати). Першим запускається POST – програма самотестування. POST виконує такі кроки:

· Ініціалізує системні ресурси та регістри чіпсетів, систему управління електроживленням;

· Визначає обсяг оперативної пам'яті (RAM) і тестує її;

· Ініціалізує відеоадаптер;

· Включає клавіатуру;

· Тестує послідовні та паралельні порти;

· ініціалізує дисководи та контролери жорстких дисків;

· Відображає підсумкову системну інформацію.

Всі ці дії швидко відображаються на екрані монітора (в чорно-білому варіанті) і їх можна простежити і навіть проаналізувати, натиснувши клавішу Pause.

В процесі роботи BIOSпорівнює дані поточної системної конфігурації з інформацією, що зберігається в CMOS, та за необхідності оновлює її. Якщо при виконанні будь-якого кроку виникли збої, BIOS інформує про це повідомленнями на екрані монітора, а якщо це неможливо (наприклад, ще не проніціалізовано відеоадаптер), видає звукові сигналичерез системний динамік. Кількість гудків відповідає кодам помилки, які можна дізнатися із документації. Деякі системні плати забезпечуються рідкокристалічним індикатором, де відображаються стадії проходження POST-тестів і коди помилок, що виникли.

Після того як всі POST-завдання завершені, BIOS починає пошук програми-завантажувача. Сучасні версії BIOS дозволяють завантажувати операційну систему не тільки з флоппі-дисководів та жорсткого диска, але й приводу CD-ROM, ZIP-пристроїв або Flash накопичувачів. Програма-завантажувач зазвичай розташовується в першому секторі диска (вінчестера), на якому розміщено операційну систему. Порядок перебору дисків під час пошуку завантажувача задається в налаштуваннях BIOS. Якщо завантажувач знайдено, він поміщається в пам'ять і йому передається керування. Після цього він знаходить і поміщає в пам'ять власне програму завантаження операційної системи (operation system loader), яка завантажує, ініціалізує та конфігурує операційну систему та драйвера пристроїв. І вже на завершення, коли операційну систему завантажено, все керування передається ОС Windows, а потім запускаються інші програми, і в першу чергу з папки «Автозавантаження».

Як уже говорилося раніше, в системах під управлінням DOS або Windows 9х BIOS перебирає роль управління апаратною частиною ПК і служить посередником між операційною системою та обладнанням.

BIOS реалізує свої функції через систему переривань програмного забезпечення. Переривання програмного забезпечення призводять до того, що мікропроцесор припиняє виконання поточного завдання і починає виконувати підпрограму обробки переривання.

Проблема BIOSв тому, що обмеженою кількістю підпрограм неможливо оптимальним чином накрити всі потреби програмного забезпечення та всі особливості роботи обладнання. Таким чином, використання підпрограм BIOS не завжди є благом. Зокрема ці підпрограми реалізують деякі функції комп'ютера дуже повільно. Іншим негативним моментом є те, що BIOS не дозволяє повністю використовувати можливості наявного обладнання, наприклад, його можливості, які були реалізовані після написання BIOS. Тому всі сучасні операційні системи, маючи розвинену систему виявлення, конфігурування та роботи з апаратним забезпеченням комп'ютерів за допомогою драйверів, не користуються послугами BIOS.

У майбутньому низка виробників системних плат мають намір відмовитися від використання BIOS. Наприклад, Intel розробляє низку технологій, які дозволять перерозподілити функції BIOS між чіпсетом і розширеннями операційної системи і позбавитися найстарішої з дожили до наших днів частини ПК.

Повна назва BIOSу – ROM BIOS (Read Only Memory Basic Input/Output System – тільки для читання основна система введення-виводу). На початкових етапах розвитку персональних комп'ютерів BIOS коротко назвали ПЗУ (Постійний пристрій). ПЗП є сполучною ланкою, між операційною системою та залізом. Якби не було ROM BIOS, то операційна система була б прив'язана до апаратних засобів (як це і було практично на всіх моделях мікро-ЕОМ) і повністю від них залежала б. Оскільки операційні системи мають єдиний інтерфейс для роботи з різною апаратурою, то проблем у несумісності hardware та software, як правило, не відбуваються, оскільки між ними якраз і стоїть BIOS. Нагадаємо, що в комп'ютерному світіза прийнятою термінологією hardware – це апаратна частина комп'ютера, а software – програмне забезпечення. Все це може виглядати приблизно так (рис.12):

Мал. 12. Роль BIOSа у створенні єдиного апаратно-програмного комплексу

Кожна материнська плата оснащена мікросхемою BIOS, яких існує чотири типи:

1. ROM (Read Only Memory) або ПЗП;

2. PROM (Programmable ROM) або ППЗУ (Програмоване ПЗП);

3. EPROM (Erasable PROM) або СППЗУ (Стирається ППЗУ);

4. EEPROM (Electrically EPROM) або ЕСППЗУ (Електронне – Стирається ППЗУ), друга назва – flash ROM.

ROM.Перші ПЗУ були матрицею, на якій був випалений код програми. Матриця була кремнієвим кристалом. Перезаписати дані неможливо. Ця технологія протрималася не надто довго.

PROM.Наприкінці 70-х фірма Texas Instrumentsрозробила вперше програмоване ПЗП. Перше ППЗУ мало ємність до 2 Мбайт. Запис на мікросхему PROM можна зробити один раз. Але, на відміну від ПЗУ, ППЗУ можна було запрограмувати в домашніх умовах. Потрібно було лише купити нову ІВ та мати вдома програмуючий пристрій, підключений до комп'ютера. Мікросхеми ППЗУ мали свої ідентифікаційні номериза якими можна було визначити тип ППЗП та обсяг у Кбайтах.

EPROM.На нових мікросхемах було кварцове віконце, досить дороге. Через віконце під впливом ультрафіолетових променів виникала хімічна реакція, яка відновлювала осередки. Для стирання записаної інформації застосовувалося спеціальний пристрій. За фізичними та функціональними параметрами мікросхеми EPROM особливо не відрізнялися від PROM.

EEPROM.Основна перевага цих мікросхем полягає в тому, що для перепрограмування не потрібно їх зняття з материнської плати і не потрібне додаткове обладнання. Вже з 1994 року майже всі системні плати оснащуються flash ROM, а на Наразічасу іншого BIOS на сучасній материнській платі не зустрінеш.