Де застосовуються негорюча тканина www.algo-textile.ru. Москітні сітки комплектуючі для москітних сіток 2-sklad.ru.

PCI та PCI-X

Шини PCI та PCI-X

Вступ

Шини PCI та PCI-X є основними шинами розширення вводу/виводу в сучасних комп'ютерах; для підключення відеоадаптерів їх доповнює порт AGP. Шини розширення вводу/виводу (Expansion Bus) є засобами підключення системного рівня: вони дозволяють адаптерам та контролерам периферійних пристроїв безпосередньо використовувати системні ресурси комп'ютера – простір адрес пам'яті та вводу/виводу, переривання, прямий доступ до пам'яті. Пристрої, підключені до шин розширення, можуть і самі керувати цими шинами, одержуючи доступ до інших ресурсів комп'ютера. Шини розширення механічно реалізуються у вигляді слотів (щілинних роз'ємів) або штиркових роз'ємів; їм характерна мала довжина провідників, тобто вони суто локальні, що дозволяє досягати високих швидкостей роботи. Ці шини можуть не виводитися на роз'єми, але використовуватися для підключення пристроїв в інтегрованих системних платах.

Спочатку шина PCI вводилася як прибудова (mezzanine bus) до систем із шиною ISA. Вона розроблялася для процесори Pentium, але добре поєднувалася і з процесорами i486. Пізніше PCI на деякий час стала центральною шиною: вона з'єднувалася з шиною процесора високопродуктивним мостом (північним мостом), що входить до складу чіпсету системної плати. Інші шини розширення вводу/виводу (ISA/EISA або MCA), а також локальна ISAподібна шина X-BUS та інтерфейс LPC, до яких підключаються мікросхеми системної плати (ROM BIOS, контролери переривань, клавіатури, DMA, портів COM і LPT, НГМД та інші «дрібниці», підключалися до шини PCI через «південний» міст. У сучасних системних платах з «хабовою» архітектурою шину PCI відсунули на периферію, не обмежуючи її в потужності каналу зв'язку з процесором та пам'яттю, але й не навантажуючи транзитним трафіком пристроїв інших шин.

Шина PCI є синхронною – фіксація всіх сигналів виконується за позитивним перепадом (фронтом) сигналу CLK. Номінальною частотою синхронізації вважається частота 33,3 МГц, за необхідності вона може бути знижена. Починаючи з версії PCI 2.1, допускається підвищення частоти до 66,6 МГц при «згоді» всіх пристроїв на шині. У PCI-X частота може досягати 133 МГц.

PCI використовується паралельна мультиплексована шина адреси/даних (AD) з типовою розрядністю 32 біт. Специфікація визначає можливість розширення розрядності до 64 біт; у PCI-X версії 2.0 визначено також 16-бітний варіант шини. При частоті шини 33 МГц теоретична пропускна здатність досягає 132 Мбайт/с для 32-бітної шини та 264 Мбайт/с для 64-бітної; при частоті синхронізації 66 МГц - 264 Мбайт/с та 528 Мбайт/с відповідно. Однак ці пікові значення досягаються лише під час передачі пакета: через протокольні накладні витрати реальна середня пропускна здатність шини виявляється нижче.

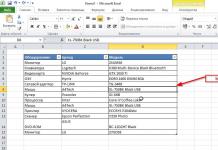

Порівняльні характеристики шин PCI і PCI-X та інших шин розширення PCсумісних комп'ютерів наведено в табл. 1.1. Шина ISA з настільних комп'ютерів йде, але вона зберігає свої позиції в промислових і вбудованих комп'ютерах, як у традиційному, слотовому, так і в бутербродному варіанті PC/104. У блокнотних комп'ютерах широко застосовуються слоти PCMCIA із шинами PC Card та Card Bus. Шина LPC є найсучаснішим дешевим засобом для підключення нересурсоємних пристроїв до системної плати.

| Шина | Пікова пропускна спроможність Мбайт/с | Канали DMA | Bus-Master | ACFG | Розрядність даних | Розрядність адреси | Частота МгГц |

| ISA-8 | 4 | 3 | - | - | 8 | 20 | 8 |

| ISA-16 | 8 |

7 |

+ |

- |

16 |

24 |

8 |

| LPC | 6,7 |

7 |

+ |

- |

8/16/32 |

32 |

33 |

| EISA |

33,3 | 7 | + |

+ |

32 |

32 |

8,33 |

| MCA-16 |

16 |

- |

+ |

+ |

16 |

24 |

10 |

| MCA-32 |

20 |

- |

+ |

+ |

32 |

32 |

10 |

| VLB |

132 |

- |

(+) |

- |

32/64 |

32 |

33-50(66) |

| PCI |

133-533 |

- |

+ |

+ |

32/64 |

32/64 |

33/66 |

| PCI-X |

533-4256 |

- |

+ |

+ |

16/32/64 |

32/64 |

66-133 |

| PCI Express |

496-15872 |

- |

+ |

+ |

1/2/4/8/12/16/32 |

32/64 |

2,5 ГГц |

| AGP 1x/2x/4x/8x |

266/533/1066/2132 |

- |

+ |

+ |

32 |

32/64 |

66 |

| PCMCIA |

10/22 |

+ |

- |

+ |

8/16 |

26 |

10 |

| Card Bus | 132 | - | + | + | 32 | 32 | 33 |

ACFG1-Підтримка автоматичного конфігурування. Для ISA PnP є пізнім надбудовою, що реалізується адаптерами та ПЗ.

Сигнальний протокол шин PCI та PCI-X

Обмін інформацією по шині PCI та PCI-X організовано у вигляді транзакцій – логічно завершених операцій обміну. У типовій транзакції беруть участь два пристрої-ініціатор обміну (initiator), він же провідний пристрій (master), і цільовий пристрій (ЦУ, target)), воно ж ведене (slave). Правила взаємодії цих пристроїв визначаються протоколом PCI шини. Пристрій може стежити за транзакціями на шині і не є учасником (не вводячи жодних сигналів); режиму стеження відповідає термін Snooping. Є особливий тип транзакції (Special Cycle) - широкомовний, в якому ініціатор протокольно не взаємодіє з жодним з пристроїв. У кожній транзакції виконується одна команда — зазвичай читання або запис даних за вказаною адресою. Транзакція починається з фази адреси, в якій ініціатор задає команду та цільову адресу. Далі можуть слідувати фази даних, в яких один пристрій (джерело даних) поміщає дані на шину, а інший (приймач) їх зчитує. Транзакції, в яких є безліч фаз даних, називаються пакетними. Є й поодинокі транзакції (з однією фазою даних). Транзакція може завершитися без фаз даних, якщо цільовий пристрій (або ініціатор) не готовий до обміну. У шині PCI-X додано фазу атрибутів, в якій передається додаткова інформація про транзакцію.

Сигнальний протокол шин PCI та PCI-X

Склад та призначення інтерфейсних сигналів шини розкриває таблиці нижче. Стану всіх сигнальних ліній сприймаються за позитивним перепадом CLK, і саме ці моменти в подальшому описі маються на увазі під тактами шини (на малюнках відзначені вертикальними пунктирними лініями). У різні моменти часу одними й тими самими сигнальними лініями керують різні пристрої шини, й у коректної (безконфліктної) «передачі повноважень» потрібно, щоб існував проміжок часу, протягом якого лінією не керує жодне пристрій. На тимчасових діаграмах ця подія - так званий "пірует" (turnaround) - позначається парою напівкруглих стрілок.

Таблиця. сигнали шини PCI

| Сигнал |

Призначення |

| AD | Address/Data – мультиплексована шина адреси/даних. На початку транзакції передається адреса, у наступних тактах – дані |

| C/B # | Command/Byte Enable — команда/дозвіл звернення до байтів. Команда, що визначає тип чергового циклу шини, задається чотирибітним кодом у фазі адреси |

| FRAME# |

кадр. Введенням сигналу відзначається початок транзакції (фаза адреси), зняття сигналу вказує на те, що наступний цикл передачі даних є останнім у транзакції |

| DEVSEL# |

Device Select — пристрій вибраний (відповідь ЦП на адресовану до нього транзакцію) |

| IRDY# |

Initiator Ready – готовність провідного пристрою до обміну даними |

| TRDY# |

Target Ready - готовність ЦП до обміну даними |

| STOP# |

Запит ЦУ до провідного пристрою на зупинку поточної транзакції |

| LOCK# |

Сигнал блокування (захоплення) шини забезпечення цілісного виконання операції. Використовується мостом, якому для виконання однієї операції потрібно виконати кілька транзакцій PCI |

| REQ# |

Request – запит від провідного пристрою на захоплення шини |

| GNT# |

Grant - надання провідному пристрою керування шиною |

| PAR |

Parity – загальний біт парності для ліній AD та C/BE# |

| PERR# |

Parity Error – сигнал про помилку парності (для всіх циклів, крім спеціальних). Виробляється будь-яким пристроєм, що виявив помилку |

| PME# |

Power Management Event – сигнал про події, що викликають зміну режиму споживання (додатковий сигнал, введений у PCI 2.2) |

| CLKRUN# |

Clock running – шина працює на номінальній частоті синхронізації. Зняття сигналу означає уповільнення або зупинку синхронізації з метою зниження споживання (для мобільних застосувань) |

| PRSN # |

Present - індикатори присутності плати, що кодують запит споживаної потужності. На карті розширення одна чи дві лінії індикаторів з'єднуються з шиною GND, що сприймається системною платою |

| RST# |

Reset — скидання всіх регістрів у початковий стан (на кнопці «Reset») та при перезавантаженні) |

| IDSEL |

Initialization Device Select - вибір пристрою в циклах конфігураційного зчитування та запису; на ці цикли відповідає пристрій, який виявив на цій лінії високий рівень сигналу |

| SERR# |

System Error – системна помилка. Помилка парності адреси чи даних у спеціальному циклі чи інша катастрофічна помилка, виявлена пристроєм. Активізується будь-яким пристроєм PCI та викликає NMI |

| REQ64# |

Request 64 bit – запит на 64-бітовий обмін. Сигнал вводиться 64-бітовим ініціатором, за часом він збігається із сигналом FRAME#. Під час закінчення скидання (сигналом RST#) сигналізує 64-бітного пристрою про те, що він підключений до 64-бітної шини. Якщо 64-бітовий пристрій не виявить цього сигналу, він має переконфігуруватися на 32-бітовий режим, відключивши буферні схеми старших байтів |

| ACK64# |

Підтвердження 64-розрядного обміну. Сигнал вводиться 64-бітовим ЦП, що впізнав свою адресу, одночасно з DEVSEL #. Відсутність цього підтвердження змусить ініціатор виконувати обмін із 32-бітною розрядністю |

| INTA#, INTB#, INTC#, INTD# |

Interrupt A, B, C, D – лінії запитів переривання, чутливість до рівня, активний рівень – низький, що допускає роздільність (спільне використання) ліній |

| CLK |

Clock – тактова частота шини. Повинна лежати в межах 20-33 МГц, починаючи з PCI 2.1 може бути до 66 МГц, PCI-X до 100 і 133 МГц |

| M66EN |

66MHz Enable — роздільна здатність частоти синхронізації до 66 МГц (на картах 33 МГц заземлений, на 66 МГц — вільний) |

| PCIXCAP (38B) |

Можливості PCI-X: на платах PCI – заземлений, на PCI-X133 з'єднаний із землею через конденсатор 0,01 мкФ, на PCI-X66 – паралельним RC-ланцюжком 10 кОм, 0,01 мкФ. |

| SDONE |

Snoop Done — сигнал завершеності циклу стеження поточної транзакції. Низький рівень вказує на незавершеність циклу стеження за когерентністю пам'яті та кешу. Необов'язковий сигнал, використовується лише пристроями шини з пам'яттю, що кешується. Виключений з PCI 2.2 |

| SBO# |

Snoop Backoff — попадання поточного звернення до пам'яті абонента шини модифікований рядок кеша. Необов'язковий сигнал, використовується лише абонентами шини з пам'яттю, що кешується, при алгоритмі зворотного запису. Виключений з PCI 2.2 |

| SMBCLK |

SMBus Clock – тактовий сигнал шини SMBus (інтерфейс I2C). Введений починаючи з PCI 2.3 |

| SMBDAT |

SMBus Data – послідовні дані шини SMBus (інтерфейс I2C). Введений починаючи з PCI 2.3 |

| TCK |

Test Clock – синхронізація тестового інтерфейсу JTAG |

| TDI |

Test Data Input - вхідні дані тестового інтерфейсу JTAG |

| TDO |

Test Data Output - вихідні дані тестового інтерфейсу JTAG |

| TMS |

Test Mode Select — Вибір режиму тестового інтерфейсу JTAG |

| TRST |

Test Logic Reset - скидання тестової логіки |

У кожний момент часу шиною може керувати тільки один провідний пристрій, який отримав це право від арбітра. Кожен провідний пристрій має пару сигналів – REQ# для запиту на керування шиною та GNT# для підтвердження надання керування шиною. Пристрій може починати транзакцію (встановлювати сигнал FRAME#) тільки за отриманого активного сигналу GNT# і дочекавшись відсутності активності шини. Зауважимо, що за час очікування спокою арбітр може передумати і віддати управління шиною іншому пристрою з вищим пріоритетом. Зняття сигналу GNT# не дозволяє пристрою розпочати наступну транзакцію, а за певних умов (див. далі) може змусити припинити розпочату транзакцію. Арбітражем запитів на використання шини займається спеціальний вузол - арбітр, що входить у міст, що з'єднує шину з центром. Схема пріоритетів (фіксований, циклічний, комбінований) визначається програмуванням арбітра.

Для адреси та даних використовуються загальні мультиплексовані лінії AD. Чотири мультиплексовані лінії C/BE забезпечують кодування команд у фазі адреси та дозвіл байтів у фазі даних. У транзакціях запису лінії C/BE дозволяють використання байтів даних одночасно з їхньою присутністю на шині AD, в транзакціях читання ці сигнали відносяться до байтів наступної за ними фази даних. У фазі адреси (початок транзакції) провідний пристрій активує сигнал FRAME#, передає цільову адресу по шині AD, а лініям C/BE# — інформацію про тип транзакції (команду). Адресований цільовий пристрій відкликається сигналом DEVSEL #. Провідний пристрій вказує на свою готовність до обміну даними IRDY#, ця готовність може бути виставлена і до отримання DEVSEL#. Коли цільовий пристрій буде готовий до обміну даними, він встановить сигнал TRDY#. Дані по шині AD передаються лише за одночасної наявності сигналів IRDY# і TRDY#. За допомогою цих сигналів провідне та цільове пристрої узгоджують свої швидкості, вводячи такти очікування (wait states). На малюнку нижче наведено часову діаграму обміну, в якій і провідне і цільове пристрої вводять такти очікування. Якби вони обидва ввели сигнали готовності в кінці фази адреси і не знімали їх до кінця обміну, то в кожному такті після фази адреси передавалися б по 32 біта даних, що забезпечило б вихід на граничну продуктивність обміну. У транзакціях читання після фази адреси необхідний додатковий такт для піруету, під час якого ініціатор припиняє керування лінією AD; цільовий пристрій зможе взяти на себе керування шиною AD лише у наступному такті. У транзакції запису пірует не потрібний, оскільки дані передає ініціатор.

На шині PCI всі транзакції трактуються як пакетні: кожна транзакція починається фазою адреси, яку може йти одна чи кілька фаз даних. Кількість фаз даних у пакеті явно не вказується, але в такті останньої фази даних провідний пристрій при введеному IRDY# знімає сигнал FRAME#. В одиночних транзакціях сигнал FRAME активний лише протягом одного такту. Якщо пристрій не підтримує пакетні транзакції у веденому режимі, він повинен вимагати припинення пакетної транзакції протягом першої фази даних (виставивши сигнал STOP# одночасно з TRDY#). У відповідь на цей провідний пристрій завершить дану транзакцію та продовжить обмін наступною транзакцією з наступним значенням адреси. Після завершальної фази даних провідне пристрій знімає сигнал IRDY#, і шина перетворюється на стан спокою (Idle) — обидва сигналу: — FRAME# і IRDY# — у пасивному стані.

Ініціатор може розпочати наступну транзакцію без такту спокою, встановивши FRAME# одночасно зі зняттям IRDY#. Такі швидкі суміжні транзакції (Fast Back-to-Back) можуть бути звернені як до одного, так і різних цільових пристроїв. Перший тип швидких суміжних транзакцій підтримується всіма пристроями PCI, які у ролі цільового пристрою. На підтримку другого типу суміжних транзакцій (така підтримка необов'язкова) вказує біт 7 регістру стану. Ініціатору дозволяють (якщо він вміє) використовувати швидкі суміжні транзакції з різними пристроями (роздільна здатність визначається бітом 9 регістра команд), тільки якщо всі агенти шини допускають швидкі звернення. При обміні даних у режимі PCI-X швидкі суміжні транзакції неприпустимі.

Протокол шини забезпечує надійність обміну - провідний пристрій завжди отримує інформацію про відпрацювання транзакції цільовим пристроєм. Засобом підвищення достовірності обміну є застосування контролю парності: лінії AD і C/BE# та у фазі адреси, і у фазі даних захищені бітом парності PAR (кількість встановлених бітів цих ліній, включаючи PAR, має бути парною). Справжнє значення PAR з'являється на шині із затримкою в один такт щодо ліній AD та C/BE#. При виявленні помилки пристрій виробляє сигнал PERR # (зі зрушенням на такт після появи на шині дійсного біта парності). У підрахунку парності при передачі враховуються всі байти, включаючи і недійсні (відзначені високим рівнем сигналу C/BEx#). Стан біт, навіть у недійсних байтах даних, під час фази даних має залишатися стабільним.

Кожна транзакція на шині має бути завершена планово або припинена, при цьому шина повинна перейти у стан спокою (сигнали FRAME і IRDY пасивні). Завершення транзакції виконується з ініціативи провідного пристрою, або з ініціативи цільового пристрою.

Провідний пристрій може завершити транзакцію одним із таких способів:

- comletion - нормальне завершення після закінчення обміну даними;

- time-out - завершення по тайм-ауту. Відбувається, коли під час транзакції у провідного пристрою відбирають право на керування шиною (зняттям сигналу GNT#), і закінчується час, вказаний у його таймері Latency Timer. Це може статися, якщо адресований цільовий пристрій виявився непередбачено повільним або заплановано надто довгу транзакцію. Короткі транзакції (з однією-двома фазами даних) навіть у разі зняття сигналу GNT# та спрацьовування таймера завершуються нормально;

- master-Abort — припинення транзакції, коли протягом заданого часу провідний пристрій не отримує відповіді цільового пристрою (сигналу DEVSEL#).

Транзакція може бути припинена з ініціативи цільового устрою; для цього може ввести сигнал STOP#. Можливі три типи припинення транзакції:

- retry - повтор, введення сигналу STOP # при пасивному сигналі TRDY до першої фази даних. Ця ситуація виникає, коли цільовий пристрій із-за внутрішньої зайнятості не встигає видати перші дані у визначений термін (16 тактів). Припинення типу retry є вказівкою провідного пристрою необхідність повторного запуску тієї ж транзакції;

- disconnect — вимкнення, введення сигналу STOP# протягом або після першої фази даних. Якщо сигнал STOP# введений при активному сигналі TRDY# чергової фази даних, ці дані передаються, на чому транзакція і завершується. Якщо сигнал STOP# виставлений при пасивному сигналі TRDY#, транзакція завершується без передачі даних чергової фази. Вимкнення відбувається, коли цільовий пристрій не здатний своєчасно видати або прийняти чергову порцію даних пакета. Вимкнення є вказівкою провідного пристрою на необхідність повторного запуску цієї транзакції, але з модифікованою стартовою адресою;

- target-abort - відмова, введення сигналу STOP# одночасно зі зняттям сигналу DEVSEL# (у попередніх випадках під час появи сигналу STOP# сигнал DEVSEL# був активним). Після цього дані вже не передаються. Відмова провадиться, коли цільовий пристрій виявляє фатальну помилку або інші умови, за якими воно вже ніяк не зможе обслужити даний запит (у тому числі й команду, що не підтримується).

Використання трьох типів припинення транзакції зовсім не є обов'язковим для всіх цільових пристроїв, проте будь-який провідний пристрій повинен бути готовим до завершення транзакцій з будь-якої з цих причин.

Припинення типу retry використовується організації відкладених транзакцій (delayed transactions). Відкладені транзакції використовуються лише повільними цільовими пристроями, а також мостами PCI під час трансляції транзакцій на іншу шину. Припиняючи (для ініціатора) транзакцію умовою retry, цільовий пристрій внутрішньо виконує цю транзакцію. Коли ініціатор повторить цю транзакцію (видасть ту ж команду з тією ж адресою і тим же набором сигналів C/BE# у фазі даних), цільовий пристрій (або мост) вже буде готовий результат (дані читання або стан виконання запису), який воно швидко поверне ініціатору. Результат відкладеної транзакції, виконаної цим пристроєм, пристрій або міст повинні зберігати доти, доки результати не будуть запитані ініціатором. Однак він може і «забути» повторити транзакцію (через будь-які нештатні ситуації). Щоб уникнути переповнення буфера зберігання результатів, пристрою доводиться відкидати ці результати. Відкидання може бути виконане без побічних ефектів, якщо відкладалася транзакція до пам'яті, що допускає передвиборку (з атрибутом prefetchable, див. далі). Інші типи транзакцій у загальному випадку безкарно відкидати не можна (може порушитись цілісність даних), для них відкидання дозволяється лише після безрезультатного очікування повтору протягом 215 тактів шини (за спрацьовуванням discard timer). Про цю особливу ситуацію пристрій може повідомити свого драйвера (або всієї системи).

Ініціатор транзакції може вимагати монопольного використання шини PCI на весь час операції обміну, що вимагає декількох шинних транзакцій. Так, наприклад, якщо центральний процесор виконує інструкцію модифікації даних у комірці пам'яті, що належить пристрою PCI, йому потрібно прочитати дані з пристрою, модифікувати їх у своєму АЛП та повернути результат у пристрій. Щоб у цю операцію не вклинювалися транзакції від інших ініціаторів (що загрожує порушенням цілісності даних), головний міст виконує її як блоковану - на весь час виконання операції подається шинний сигнал LOCK #. Цей сигнал не використовується (і не виробляється) звичайними пристроями PCI (не мостами); він використовується лише мостами для управління арбітражем.

Апаратні переривання в PC-сумісних комп'ютерах

Пристрої PCI мають можливість сигналізації про асинхронні події за допомогою переривань. На шині PCI можливі чотири типи сигналізації переривань:

- традиційна дротова сигналізація лініями INTx;

- провідна сигналізація подій керування енергоспоживанням по лінії PME#;

- сигналізація за допомогою повідомлень - MSI;

- сигналізація фатальної помилки лінії SERR#.

У цьому розділі розглядаються ці типи сигналізації, і навіть загальна картина підтримки апаратних переривань в PC-совместимых комп'ютерах.

Апаратні переривання в PC-сумісних комп'ютерах

Апаратні переривання забезпечують реакцію процесора на події, що відбуваються асинхронно по відношенню до програмного коду. Нагадаємо, що апаратні переривання діляться на маскувані і немасковані. Процесор x86 за сигналом переривання зупиняє виконання поточного потоку інструкцій, зберігаючи в стеку стан (прапори та адресу повернення), та виконує процедуру обробки переривання. Конкретна процедура обробки вибирається з таблиці переривань за вектором переривання - однобайтним номером елемента в цій таблиці. Вектор переривання доводиться до процесора різними способами: для переривання, що не маскується, він фіксований, для маскуваних переривань його повідомляє спеціальний контролер переривань. Крім апаратних переривань у процесорів x86 є також внутрішні переривання - винятки (exceptions), пов'язані з особливими випадками виконання інструкцій, та програмні переривання. Для винятків вектор визначається особливою умовою, і під винятком фірмою Intel зарезервовані перші 32 вектори (0-31 або 00-1Fh). У програмних перериваннях номер вектора міститься у самій інструкції (програмні переривання — це лише специфічний спосіб виклику процедур за номером, із попереднім збереженням у стеку регістру прапорів). Всі ці переривання використовують один і той же набір із 256 можливих векторів. Історично склалося так, що вектори, що використовуються для апаратних переривань, перетинаються з векторами винятків та векторами для програмних переривань, які використовуються для викликів сервісів BIOS та DOS. Таким чином, для ряду номерів векторів процедура, на яку посилається таблиця переривань, повинна спочатку містити програмний код, що визначає, з якого приводу вона викликана: за винятком апаратного переривання або для виклику якогось системного сервісу. Таким чином, процедура, що власне і забезпечує реакцію процесора на ту саму асинхронну подію, буде викликана тільки після низки дій щодо ідентифікації джерела переривань. Тут ще зауважимо, що один і той же вектор переривання може використовуватися і декількома периферійними пристроями - це так зване використання переривань, що розділяється, яке докладно обговорюється нижче.

Виклик процедури обслуговування переривань у реальному та захищеному режимах процесора істотно відрізняється:

- у реальному режимі таблиця переривань містить 4-байтні дальні покажчики (сегмент та зміщення) на відповідні процедури, що викликаються далеким викликом (Call Far з попереднім збереженням прапорів). Розмір (256 × 4 байт) та положення таблиці (починається з адреси 0) фіксовані;

- у захищеному режимі (і в його окремому випадку – режимі V86) таблиця містить 8-байтні дескриптори переривань, які можуть бути шлюзами переривань (Interrupt Gate), пасток (Trap Gate) або завдань (Task Gate). Розмір таблиці може бути зменшений (максимальний - 256 × 8 байт), положення таблиці може змінюватись (визначається вмістом регістра IDT процесора). Код обробника переривань має бути не менш привілейованим, ніж код завдання, що переривається (інакше спрацює виняток захисту). Тому обробники переривань повинні працювати на рівні ядра ОС (на нульовому рівні привілеїв). Зміна рівня привілею під час виклику оброблювача призводить до додаткових витрат часу на перевизначення стека. Переривання, що викликають перемикання завдань (через Task Gate), витрачають значно часу на перемикання контексту - вивантаження регістрів процесора в сегмент стану старої задачі та їх завантаження з сегмента стану нової.

Номери векторів, що використовуються для апаратних переривань в операційних системах захищеного режиму, відрізняються від номерів, що використовуються в ОС реального режиму, щоб виключити конфлікти з векторами, що використовуються для виключень процесора.

На переривання, що не маскується (NMI - Non-Maskable Interrrupt) процесор реагує завжди (якщо обслуговування попереднього NMI завершено); цьому перериванню відповідає фіксований вектор 2. Переривання в PC, що не маскуються, використовуються для сигналізації про фатальні апаратні помилки. Сигнал на лінію NMI походить від схем контролю пам'яті (парності або ECC), ліній контролю шини ISA (IOCHK) і шини PCI (SERR#). Сигнал NMI блокується до входу процесора установкою в 1 біта 7 порту 070h, окремі джерела дозволяються та ідентифікуються бітами порту 061h:

- біт 2 R/W - ERP - дозвіл контролю ОЗУ та сигналу SERR# шини PCI;

- біт 3 R/W - EIC - дозвіл контролю шини ISA;

- біт 6 R - IOCHK - помилка контролю на шині ISA (сигнал IOCHK #);

- біт 7 R - PCK - помилка парності ОЗП або сигнал SERR # на шині PCI.

Реакція процесора на маскування переривання може бути затримана скиданням його внутрішнього прапора IF (інструкція CLI забороняє переривання, STI - дозволяє). Переривання, що маскуються, використовуються для сигналізації про події в пристроях. Після виникнення події, що вимагає реакції, адаптер (контролер) пристрою формує запит переривання, який надходить на вхід контролера переривань. Завдання контролера переривань - довести до процесора запит переривання і повідомити вектор, яким вибирається програмна процедура обробки переривань.

Процедура обробки переривання від пристрою повинна виконати дії обслуговування цього пристрою, включаючи скидання його запиту для забезпечення можливості реакції на наступні події, і надіслати команди завершення в контролер переривань. Викликаючи процедуру обробки, процесор автоматично зберігає в стеку значення всіх прапорів і скидає прапор IF, що забороняє переривання, що маскуються. При поверненні цієї процедури (за інструкцією IRET) процесор відновлює збережені прапори, зокрема і встановлений (до переривання) IF, що знову дозволяє переривання. Якщо під час роботи обробника переривань потрібна реакція на інші переривання (пріоритетніші), то в обробнику повинна бути інструкція STI. Особливо це стосується довгих обробників; тут інструкція STI повинна вводитися якомога раніше, відразу після критичної (не допускає переривань) секції. Наступні переривання того ж чи більш низького рівня пріоритету контролер переривань буде обслуговувати лише після отримання команди завершення переривання EOI (End Of Interrupt).

В IBM PC-сумісних комп'ютерах застосовується два основних типи контролерів переривань:

- PIC (Peripheral Interrupt Controller) - периферійний контролер переривань, програмно сумісний з "історичним" контролером 8259A, що застосовувався ще перших моделях IBM PC. З часів IBM PC/AT застосовується зв'язка із пари каскадно з'єднаних PIC, що дозволяє обслуговувати до 15 ліній запитів переривань;

- APIC (Advanced Peripheral Interrupt Controller) - удосконалений периферійний контролер переривань, введений для підтримки мультипроцесорних систем в комп'ютери на базі процесорів 4-5 поколінь (486 і Pentium) і використовується досі для пізніших моделей процесорів. Крім підтримки мультипроцесорних конфігурацій, сучасний APIC дозволяє збільшувати кількість доступних ліній переривань і обробляти запити переривань від пристроїв PCI, що надсилаються через механізм повідомлень (MSI). Комп'ютер, оснащений контролером APIC, обов'язково має можливість функціонувати і в режимі сумісному зі стандартним зв'язуванням пари PIC. Цей режим включається з апаратного скидання (і включення живлення), що дозволяє використовувати старі ОС та додатки MS DOS, які не знають APIC і мультипроцесування.

Традиційна схема формування запитів переривань із використанням пари PIC зображена на малюнку нижче.

На входи контролерів переривань надходять запити від системних пристроїв (клавіатура, системний таймер, CMOS-таймер, співпроцесор), периферійних контролерів системної плати та карт розширення. Традиційно всі лінії запитів, не зайняті переліченими пристроями, є на всіх слотах шини ISA/EISA. Ці лінії позначаються як IRQx та мають загальноприйняте призначення (див. таблицю нижче). Частина цих ліній віддається у розпорядження шини PCI. У таблиці відображено пріоритети переривань — запити розташовані в порядку їх зменшення. Номери векторів, що відповідають лініям запитів контролерів, система пріоритетів та деякі інші параметри задаються програмно під час ініціалізації контролерів. Ці основні настройки залишаються традиційними для сумісності з програмним забезпеченням, але відрізняються для ОС реального та захищеного режимів. Так, наприклад, в ОС Windows базові вектори для провідного та керованого контролерів — 50h і 58h відповідно.

| Ім'я (номер 1) | Вектор 2 | Вектор 3 | Контролер/маска | Опис |

| NMI | 02h | |||

| IRQ0 | 08h | 50h |

#1/1h |

Контроль каналу, парність пам'яті (XT — співпроцесор) |

| IRQ1 | 09h | 51h |

#1/2h |

Клавіатура |

| IRQ2 | 0Ah | 52h |

#1/4h |

XT – резерв, AT – недоступно (підключається каскад IRQ8-IRQ15) |

| IRQ8 | 70h |

58h |

#2/1h |

CMOS RTC - годинник реального часу |

| IRQ9 | 71h |

59h |

#2/2h |

Резерв |

| IRQ10 | 72h |

5Ah |

#2/4h |

Резерв |

| IRQ11 | 73h |

5Bh |

#2/8h |

Резерв |

| IRQ12 | 74h |

5Ch |

#2/10h |

PS/2-Mouse (резерв) |

| IRQ13 | 75h |

5Dh |

#2/20h |

Математичний співпроцесор |

| IRQ14 | 76h |

5Eh |

#2/40h |

HDC - контролер НЖМД |

| IRQ15 | 77h |

5Fh |

#2/80h |

Резерв |

| IRQ3 | 0Bh |

52h |

#1/4h |

COM2, COM4 |

| IRQ4 | 0Ch |

53h |

#1/10h |

COM1, COM3 |

| IRQ5I | 0Dh |

54h |

#1/20h |

XT – HDC, AT – LPT2, Sound (резерв) |

| IRQ6 | 0Eh |

55h |

#1/40h |

FDC - контролер НГМД |

| IRQ7 | 0Fh |

56h |

#1/80h |

LPT1 - принтер |

*1 Запити переривань 0, 1, 8 та 13 на шини розширення не виводяться.

*2 Вказано номери векторів під час роботи в реальному режимі процесора.

*3 Вказано номери векторів під час роботи в Windows.

Кожному пристрою, для підтримки роботи якого потрібні переривання, має бути призначено свій номер переривання. Призначення номерів переривань виконуються з двох сторін: по-перше, адаптер, який потребує переривань, повинен бути налаштований на використання конкретної лінії шини (джамперами або програмно). По-друге, програмне забезпечення, яке підтримує цей адаптер, має бути проінформовано про номер використовуваного вектора. У процесі призначення переривань може брати участь система PnP для шин ISA і PCI, розподілу ліній запитів між шинами служать спеціальні параметри CMOS Setup. Сучасні ОС мають можливість змінити призначення запитів щодо розподілу через CMOS Setup.

Після того як здійснено конфігурування системи переривань (проініціалізований контролер переривань, пристроям призначені лінії запитів та встановлені покажчики на процедури обробки), відпрацювання апаратних переривань, що маскуються, відбувається наступним чином:

- пристрій події переривання збуджує призначену йому лінію запиту переривання;

- контролер приймає сигнали запитів від джерел переривань (сигнали IRQx) та за наявності незамаскованого запиту подає сигнал загального запиту переривання (сигнал INTR) процесору x86;

- процесор, реагуючи на запит (коли переривання прапором IF дозволено), зберігає в стеку вміст регістру прапорів та адресу повернення, після чого формує шинний цикл INTA (Interrupt Acknowledge, підтвердження переривання), який доводиться до контролера переривань;

- в момент отримання сигналу INTA контролер переривань фіксує стан своїх входів запитів - до цього моменту їх стан міг змінитися: могли з'явитися нові запити або зникнути запит від "нетерплячого" пристрою. Контролер аналізує запити, що надійшли, відповідно до запрограмованої схеми пріоритетів і посилає процесору вектор переривання, відповідний самому пріоритетному незамаскованого запиту, що присутній на вході контролера в момент подачі шинної команди INTA. При цьому контролер виконує і деякі дії відповідно до встановленої пріоритетної політики, які враховують, який саме вектор був надісланий (який із запитів пішов на обслуговування);

- отримавши вектор переривання, процесор за номером викликає відповідну процедуру обробки переривання. Якщо цей вектор переривання використовується як для апаратних переривань, але й винятків і/або програмних переривань, то процедура насамперед має визначити, якого з цих типів належить дане подія. Для цього процедура може звернутися до контролера PIC (прочитати регістр ISR) та проаналізувати стан регістрів процесора. Подальші кроки розглядаються випадку, коли виявлено апаратне переривання;

- процедура обробки переривання має ідентифікувати джерело переривання - визначити пристрій, що його викликав. У разі роздільного використання кількома пристроями даного номера запиту (отже, і вектора) ідентифікувати джерело переривання можна лише послідовними зверненнями до регістрів кожного з цих пристроїв. При цьому слід враховувати можливість надходження запитів від декількох пристроїв одночасно або в процесі переривання від одного з них;

- процедура повинна обслужити пристрій-джерело переривання - виконати «корисні» дії, пов'язані з подією, про яку сигналізував пристрій. Це обслуговування має забезпечити та зняття сигналу запиту переривання від цього пристрою. У разі переривань джерел може бути і кілька, і всі вони вимагають обслуговування;

- якщо обробка переривання займає значний час, протягом якого потрібна реакція системи на пріоритетні запити, то після критичної секції обробник включають інструкцію STI, що встановлює прапор дозволу переривань (IF) в процесорі. З цього моменту можливі вкладені переривання, що переривають роботу даного оброблювача іншою, пріоритетнішою процедурою;

- процедура обробки переривання повинна надіслати контролеру команду завершення обробки переривання EOI (End Of Interrupt), за якою контролер дозволить наступний прийом сигналу з обслуговуваного входу та менш пріоритетних. Це має бути зроблено після зняття сигналу переривання від обслуговуваних пристроїв, інакше контролер після EOI надішле повторний запит. Обробник переривання, для якого запит надійшов від керованого контролера, повинен послати EOI як веденому, так і провідному контролеру. Ділянка обробника, що починається від подачі команди EOI до завершення (інструкції IRET), має бути безперервною, тобто вона є критичною секцією. Якщо обробник дозволяв вкладені переривання, то перед подачею команди EOI має бути присутня інструкція CLI, яка забороняє переривання;

- завершується обробка переривання інструкцією IRET, за якою процесор повертається до виконання перерваного потоку інструкцій, попередньо витягуючи зі стека вміст регістру прапорів. При цьому апаратні переривання знову виявляться дозволеними.

Ця послідовність описана стосовно звичайного контролера переривань (PIC), в системах з APIC змінюється спосіб доставки вектора переривання від контролера до процесора, а перериваннях MSI змінюється спосіб доставки сигналу від пристрою до контролера APIC. Ці нюанси описані у наступних розділах.

Загальна інформація

Мости PCI (PCI Bridge) — спеціальні апаратні засоби з'єднання шин PCI (та PCI-X) між собою та іншими шинами. Головний міст (Host Bridge) використовується для підключення PCI до центру комп'ютера (системної пам'яті та процесора). «Почесним обов'язком» головного мосту є генерація звернень до конфігураційного простору під управлінням центрального процесора, що дозволяє хосту (центральному процесору) виконувати конфігурування всієї підсистеми PCI шин. У системі може бути і кілька головних мостів, що дозволяє надати високопродуктивний зв'язок з центром більшій кількості пристроїв (кількість пристроїв на одній шині обмежена). З цих шин одна призначається умовно головною (bus 0).

Рівнорангові мости PCI (PeertoPeer Bridge) використовуються для підключення додаткових шин PCI. Ці мости завжди вносять додаткові накладні витрати на передачу даних, так що ефективна продуктивність при обміні пристрою з центром знижується з кожним мостом, що встає на шляху.

Для підключення шин PCMCIA, CardBus, MCA, ISA/EISA, X-Bus і LPC використовуються спеціальні мости, що входять у чіпсети системних плат або є окремими пристроями PCI (мікросхемами). Ці мости виконують перетворення інтерфейсів шин, що з'єднуються ними, синхронізацію і буферизацію обмінів даних.

Кожен міст програмується - йому вказуються діапазони адрес у просторах пам'яті та введення-виводу, відведені пристроям його шин. Якщо адреса ЦП поточної транзакції на одній шині (стороні) моста відноситься до шини протилежної сторони, міст транслює транзакцію на відповідну шину та забезпечує узгодження протоколів шин. Таким чином, сукупність мостів PCI виконує маршрутизацію (routing) звернень по зв'язаних шинах. Якщо в системі є кілька головних мостів, то наскрізна маршрутизація між пристроями різних шин може бути неможливою: головні мости один з одним можуть бути пов'язані лише через магістральні шляхи контролера пам'яті. Підтримка трансляції всіх типів транзакцій PCI через головні мости в цьому випадку виявляється надто складною, тому специфікацією PCI суворо і не потрібно. Таким чином, всі активні пристрої всіх шин PCI можуть звертатися до системної пам'яті, але можливість рівнорангового спілкування може виявитися залежно від належності цих пристроїв тій чи іншій PCI шині.

Застосування мостів PCI надає такі можливості, як:

- збільшення можливої кількості підключених пристроїв, долаючи обмеження електричних специфікацій шини;

- поділ пристроїв PCI на сегменти – шини PCI – з різними характеристиками розрядності (32/64 біт), тактової частоти (33/66/100/133 МГц), протоколу (PCI, PC-X Mode 1, PCI-X Mode 2, PCI Express). На кожній шині всі абоненти дорівнюють найслабшому учаснику; правильне розміщення пристроїв по шинах дозволяє з максимальною ефективністю використовувати можливості пристроїв і системної плати;

- організація сегментів із «гарячим» підключенням/відключенням пристроїв;

- організація одночасного паралельного виконання транзакцій від ініціаторів, що розташовані на різних шинах.

Кожен міст PCI з'єднує лише дві шини: первинну (primary bus), що знаходиться ближче до вершини ієрархії, з вторинною (secondary bus); інтерфейси мосту, якими він пов'язаний із цими шинами, називаються відповідно первинним та вторинним. Допускається лише суто деревоподібна конфігурація, тобто дві шини з'єднуються одна з одною лише одним мостом і немає «петлі» з мостів. Шини, що приєднуються до вторинного інтерфейсу цього мосту іншими мостами, називаються підлеглими (subordinated bus). Мости PCI утворюють ієрархію шин PCI, на вершині якої знаходиться головна шина з нульовим номером, підключена до головного мосту. Якщо головних мостів кілька, то з їх шин (рівних один одному за рангом) умовно головною буде шина, якій призначено нульовий номер.

Міст повинен виконувати низку обов'язкових функцій:

- обслуговувати шину, підключену до його вторинного інтерфейсу:

- виконувати арбітраж — прийом сигналів запиту REQx# від провідних пристроїв шини та надання їм права керувати шиною сигналами GNTx#

- паркувати шину — подавати сигнал GNTx# якомусь пристрою, коли керування шиною не потрібно жодному із задатчиків;

- генерувати конфігураційні цикли типу 0 з формуванням індивідуальних сигналів IDSEL до пристрою PCI, що адресується;

- "підтягувати" керуючі сигнали до високого рівня;

- визначати можливості підключених пристроїв і вибирати режим роботи шини, що задовольняє їх (частота, розрядність, протокол);

- формувати апаратне скидання (RST#) за скиданням від первинного інтерфейсу і за командою, повідомляючи про обраний режим спеціальною сигналізацією.

- підтримувати карти ресурсів, що знаходяться з різних боків моста;

- відповідати під виглядом цільового пристрою на транзакції, ініційовані майстром на одному інтерфейсі та адресовані ресурсу, що знаходиться з боку іншого інтерфейсу; транслювати ці транзакції в інший інтерфейс, виступаючи у ролі провідного пристрою (майстра), і передавати їх результати істинному ініціатору.

Мости, що виконують ці функції, називаються прозорими (transparrent bridge); для роботи з пристроями, що знаходяться за такими мостами, не потрібні додаткові драйвери моста. Саме такі мости описані в специфікації PCI Bridge 1.1, і для них як пристроїв PCI є спеціальний клас (06). В даному випадку мається на увазі «плоска» модель адресації ресурсів (пам'яті та введення-виведення): кожен пристрій має свої адреси, унікальні (не перетинаються з іншими) у межах даної системи (комп'ютера).

Існують і непрозорі мости (non-transparrent bridge), які дозволяють організовувати відокремлені сегменти з локальними адресними просторами. Непрозорий міст виконує трансляцію (перетворення) адрес для транзакцій, у яких ініціатор і цільовий пристрій знаходяться по різні боки моста. Досяжними через такий міст можуть і не всі ресурси (діапазони адрес) протилежної сторони. Непрозорі мости використовуються, наприклад, коли в комп'ютері виділяється підсистема інтелігентного введення-виводу (I20) зі своїм процесором введення-виводу і локальним адресним простором.

Загальна інформація

У шину PCI спочатку закладено можливості автоматичного конфігурування системних ресурсів (просторів пам'яті та введення-виведення та ліній запиту переривань). Автоматичне конфігурування пристроїв (вибір адрес та переривань) підтримується засобами BIOS та ОС; воно орієнтоване на технологію PnP. Стандарт PCI визначає кожної функції конфігураційний простір розміром до 256 регістрів (8-бітних), не приписаних ні до простору пам'яті, ні простору ввода-вывода. Доступ до них здійснюється за спеціальними командами шини Configuration Read і Configuration Write, що виробляються за допомогою одного з апаратно-програмних механізмів, описаних далі. У цьому просторі є області, обов'язкові всім пристроїв, і специфічні. Конкретний пристрій може мати регістри не в усіх адресах, але повинен підтримувати нормальне завершення для операцій, що адресуються до них. При цьому читання неіснуючих регістрів має повертати нулі, а запис виконуватиметься як неодружена операція.

Конфігураційний простір функції починається зі стандартного заголовка, в якому містяться ідентифікатори виробника, пристрою та його класу, а також опис необхідних системних ресурсів. Структура заголовка стандартизована для стандартних пристроїв (тип 0), мостів PCI-PCI (тип 1), мостів PCI-CardBus (тип 2). Тип заголовка визначає розташування загальновідомих регістрів та призначення їх біт. Після заголовка можуть розташовуватись регістри, специфічні для пристрою. Для стандартизованих властивостей (capability) пристроїв (наприклад, управління енергоспоживанням) конфігураційному просторі є блоки регістрів відомого призначення. Ці блоки організуються в ланцюжки, перший такий блок є посилання стандартному заголовку (CAP_PTR); у першому ж регістрі блоку є посилання на наступний блок (або 0, якщо цей блок останній). Таким чином, переглянувши ланцюжок, конфігураційне програмне забезпечення отримує список всіх доступних властивостей пристрою та їх позицій у конфігураційному просторі функції. У PCI 2.3 визначено такі ідентифікатори CAP_ID, частину яких ми розглянемо:

- 01 - управління енергоспоживанням;

- 02 - порт AGP;

- 03 - VPD (Vital Product Data), дані, що дають вичерпний опис апаратних (можливо, і програмних) властивостей пристроїв;

- 04 - нумерація слотів та шасі;

- 05 - переривання MSI;

- 06 - Hot Swap, гаряче підключення для Compact PCI;

- 07 - протокольні розширення PCI-X;

- 08 - зарезервовано для AMD;

- 09 - на розсуд виробника (Vendor Specific);

- 0Ah - налагоджувальний порт (Debug Port);

- 0Bh - PCI Hot Plug, стандартне забезпечення гарячого підключення.

У PCI-X для пристроїв Mode 2 конфігураційний простір розширений до 4096 байт; у розширеному просторі можуть бути розширені описи властивостей.

Після апаратного скидання (або при включенні живлення) пристрої PCI не відповідають на звернення до простору пам'яті та вводу-виводу, вони доступні тільки для операцій конфігураційного зчитування та запису. У цих операціях пристрою вибираються за індивідуальними сигналами IDSEL, читанням регістрів конфігураційне ПЗ дізнається про потреби в ресурсах та можливі варіанти конфігурування пристроїв. Після розподілу ресурсів, що виконується програмою конфігурування (під час тесту POST або завантаження ОС), в конфігураційні регістри пристрою записуються параметри конфігурування (базові адреси). Тільки після цього пристроям (точніше, функціям) встановлюються біти, що дозволяють їм відповідати на команди звернення до пам'яті та портів вводу-виводу, а також самим керувати шиною. Щоб завжди можна було знайти працездатну конфігурацію, всі ресурси, займані картами, мають бути переміщуваними у своїх просторах. Для багатофункціональних пристроїв кожна функція повинна мати власний конфігураційний простір. Пристрій може одні й самі регістри відображати і пам'ять, і простір ввода-вывода. При цьому в їх конфігураційних регістрах повинні бути обидва описувачі, але драйвер повинен використовувати тільки один спосіб звернення (переважно через пам'ять).

У заголовку конфігураційного простору описуються потреби на адреси трьох типів:

- регістри у просторі вводу-виводу (I/O Space));

- регістри вводу-виводу, відображені на згадку (Memory Mapped I/O). Це область пам'яті, звернення до якої повинні проводитися у суворій відповідності до того, що запитує ініціатор обміну. Звернення до цих регістрів може змінювати внутрішній стан периферійних пристроїв;

- пам'ять, що припускає передвиборку (Prefetchable Memory). Це область пам'яті, «зайве» читання якої (з результатами, що не використовуються) не призводить до побічних ефектів, всі байти зчитуються незалежно від сигналів BE#, і записи окремих байтів мостом можуть бути об'єднані (тобто це пам'ять у чистому вигляді).

Потреби в адресах вказуються в регістрах базових адрес - BAR (Base Address Register). Конфігуруюча програма може визначити розміри необхідних областей. Для цього після апаратного скидання вона повинна рахувати та зберегти значення базових адрес (це будуть адреси за замовчуванням), записати в кожен регістр FFFFFFFFh і знову рахувати їх значення. В отриманих словах потрібно обнулити біти декодування типу (біти для пам'яті та біти для вводів виводу), інвертувати та інкрементувати отримане 32-бітне слово – результатом буде довжина області (для портів біти ігнорувати). Метод передбачає, що довжина області виражається числом 2n і вирівняна область природним чином. Стандартний заголовок вміщує до 6 регістрів базової адреси, але при використанні 64-бітної адресації кількість блоків, що описуються, скорочується. Регістри BAR, що не використовуються, при читанні завжди повинні повертати нулі.

У PCI є підтримка старих (legacy) пристроїв (VGA, IDE), які самі себе оголошують за кодом класу в заголовку. Їх традиційні (фіксовані) адреси портів не заявляються в конфігураційному просторі, але як тільки встановлюється біт дозволу звернення до портів, пристроям дозволяється відповідь і за цими адресами.

AGP-слот із клямкою для графічної карти.

Більшість графічних карт у ПК використовують інтерфейс Accelerated Graphics Port (AGP). У найстаріших систем тієї ж мети застосовується інтерфейс PCI. Втім, на заміну обом інтерфейсам покликаний PCI Express (PCIe). Незважаючи на назву, PCI Express є послідовною шиною, а PCI (без суфікса Express) – паралельною. Загалом, шини PCI та PCI Express не мають нічого спільного, крім назви.

Графічна карта AGP (згори) та графічна карта PCI Express (знизу).

Материнські плати для робочих станцій використовують слот AGP Pro, який забезпечує додаткове харчування для ненажерливих карток OpenGL. Втім, до нього можна встановлювати і звичайні графічні карти. Однак AGP Pro так і не набув широкого визнання. Зазвичай ненажерливі графічні карти комплектуються додатковим гніздом живлення - для тієї ж вилки Molex, наприклад.

Додаткове харчування для графічної карти: 4- або 6-контактне гніздо.

Додаткове харчування для графічної карти: гнідо Molex.

Стандарт AGP пережив кілька оновлень.

| Стандарт | Пропускна здатність |

| AGP 1X | 256 Мбайт/с |

| AGP 2X | 533 Мбайт/с |

| AGP 4X | 1066 Мбайт/с |

| AGP 8X | 2133 Мбайт/с |

Якщо ви любите копатися в "залізі", слід пам'ятати про два рівні напруги інтерфейсу. Стандарти AGP 1X і 2X працюють на 3,3 В, в той час як AGP 4X і 8X вимагають лише 1,5 В. Крім того, існують карти типу Universal AGP, які підходять для роз'єму будь-якого типу. Щоб запобігти помилковій установці карт, слоти AGP використовують спеціальні виступи. А карти – прорізи.

У верхній карті є проріз для AGP 3,3 В. У середині: універсальна карта з двома вирізами (один для AGP 3,3, другий - для AGP 1,5 В). Знизу показано карту з вирізом праворуч для AGP 1,5 Ст.

Слоти розширення материнської плати: PCI Express x16 ліній (згори) та 2 PCI Express x1 лінія (знизу).

Два слоти PCI Express для встановлення двох графічних карт nVidia SLi. Між ними можна побачити маленький слот PCI Express x1.

PCI Express є послідовним інтерфейсом і його не слід плутати з шинами PCI-X або PCI, які використовують паралельну передачу сигналів.

PCI Express (PCIe) є найсучаснішим інтерфейсом для графічних карток. У той же час він підходить і для встановлення інших карт розширення, хоча на ринку поки їх дуже мало. PCIe x16 забезпечує вдвічі більшу пропускну здатність, ніж AGP 8x. Але на практиці ця перевага так і не проявила себе.

Графічна карта AGP (згори) порівняно з графічною карткою PCI Express (знизу).

Зверху вниз: PCI Express x16 (послідовний), два інтерфейси паралельної PCI та PCI Express x1 (послідовний).

| Число ліній PCI Express | Пропускна спроможність в одному напрямку | Сумарна пропускна спроможність |

| 1 | 256 Мбайт/с | 512 Мбайт/с |

| 2 | 512 Мбайт/с | 1 Гбайт/с |

| 4 | 1 Гбайт/с | 2 Гбайт/с |

| 8 | 2 Гбайт/с | 4 Гбайт/с |

| 16 | 4 Гбайт/с | 8 Гбайт/с |

PCI є стандартною шиною для підключення периферійних пристроїв. Серед них можна відзначити мережеві карти, модеми, звукові карти та плати захоплення відео.

Серед материнських плат для широкого ринку найбільше поширена шина PCI стандарту 2.1, що працює на частоті 33 МГц і має ширину 32 біти. Вона має пропускну здатність до 133 Мбіт/с. Виробники так широко і не прийняли шини PCI 2.3 із частотою до 66 МГц. Саме тому карт цього стандарту дуже мало. Але деякі материнські плати цей стандарт підтримують.

Ще одна розробка у світі паралельної шини PCI відома як PCI-X. Дані слоти найчастіше зустрічаються на материнських платах для серверів та робочих станцій, оскільки PCI-X забезпечує більш високу пропускну здатність для RAID-контролерів чи мережевих карток. Наприклад, шина PCI-X 1.0 пропонує пропускну здатність до 1 Гбіт/с із частотою шини 133 МГц і розрядністю 64 біти.

Специфікація PCI 2.1 сьогодні передбачає напругу живлення 3,3 В. Лівий виріз/виступ запобігає установці старих 5 В карт, які показані на ілюстрації.

Карта з вирізом, а також PCI-слот із ключем.

RAID-контролер для 64-розрядного слота PCI-X.

Класичний 32-бітний слот PCI зверху, а три 64-бітові слоти PCI-X знизу. Зелений слот підтримує ZCR (Zero Channel RAID).

Словник

- PCI = Peripheral Component Interconnect

|

|||

|

| |||

Коли йдеться про будь-які інтерфейси в контексті комп'ютерних систем, потрібно бути дуже уважним, щоб не «нарватися» на несумісні інтерфейси для тих самих комплектуючих в рамках системи.

На щастя, коли йдеться щодо інтерфейсу PCI-Express для підключення відеокарти, проблем з несумісністю практично не буде. У цій статті ми це детальніше розберемо, а також поговоримо щодо того, що ж таке цей PCI-Express.

Для чого потрібний PCI-Express і що це таке?

Почнемо, як завжди, з самих азів. Інтерфейс PCI-Express (PCI-E)- Це засіб взаємодії, в даному контексті, що складається з контролера шини і відповідного слота (рис.2) на материнської плати(якщо узагальнити).

Цей високопродуктивний протокол використовується, як було зазначено вище, для підключення відеокарти до системи. Відповідно, на материнській платі є відповідний слот PCI-Express, куди і встановлюється відеоадаптер. Раніше відеокарти підключалися по інтерфейсу AGP, але коли даного інтерфейсу, просто кажучи: «перестало хапати», на допомогу прийшов PCI-E, про докладні характеристики якого ми зараз і поговоримо.

Рис.2 (Слоти PCI-Express 3.0 на материнській платі)

Основні характеристики PCI-Express (1.0, 2.0 та 3.0)

Незважаючи на те, що назви PCI та PCI-Express дуже схожі, принципи з'єднання (взаємодії) у них кардинально відрізняються. У випадку PCI-Express використовується лінія - двонаправлене послідовне з'єднання типу «точка-точка», даних ліній може бути кілька. У випадку з відеокартами та материнськими платами (не враховуємо Cross Fire та SLI), які підтримують PCI-Express x16 (тобто більшість), можна запросто здогадатися, що таких ліній 16 (рис.3), часто на материнських платах з PCI- E 1.0 можна було спостерігати другий слот x8, для роботи в режимі SLI або Cross Fire.

Ну, а в PCI, пристрій підключається до загальної 32-х розрядної паралельної шини.

Мал. 3. Приклад слотів із різною кількістю ліній

(як говорилося раніше, найчастіше використовується х16)

Для інтерфейсу пропускну здатність становить 2,5 Гбіт/c. Ці дані потрібні нам, щоб відстежувати зміни цього параметра у різних версіях PCI-E.

Далі, версія 1.0 еволюціонувала в PCI-E 2.0. В результаті цього перетворення ми отримали вдвічі більшу пропускну здатність, тобто 5 Гбіт/c, але хотілося б відзначити, що в продуктивності графічні адаптери особливо не виграли, оскільки це просто версія інтерфейсу. Більшість продуктивності залежить від самої відеокарти, версія інтерфейсу може лише трохи покращувати або гальмувати передачу даних (в даному випадку «гальмування» немає, і є непоганий запас).

Так само в 2010 році, із запасом, був розроблений інтерфейс PCI-E 3.0, на даний момент він використовується у всіх нових системах, але якщо у Вас все ще 1.0 або 2.0, то не журіться - нижче ми поговоримо про зворотну сумісність різних версій.

У версії PCI-E 3.0 пропускну здатність було збільшено вдвічі в порівнянні з версією 2.0. Також там було здійснено чимало технічних змін.

До 2015 року очікується поява на світ PCI-E 4.0, Що для динамічної IT-індустрії абсолютно не дивно.

Ну та гаразд, будемо закінчувати з цими версіями і цифрами пропускної спроможності, і порушимо дуже важливе питання зворотної сумісності різних версій PCI-Express.

Зворотна сумісність версій PCI-Express 1.0, 2.0 та 3.0

Це питання хвилює багатьох, особливо при виборі відеокартидля поточної системи Так як задовольняючись системою з материнською платою, яка підтримує PCI-Express 1.0, виникають сумніви, чи коректно працюватиме відеокарта з PCI-Express 2.0 або 3.0? Так, буде принаймні так обіцяють розробники, які забезпечили цю сумісність. Єдине те, що відеокарта не зможе повністю розкритися у всій красі, але втрати продуктивності, в більшості випадків, будуть незначні.

З точністю навпаки, можна спокійнісінько встановлювати відеокарти з інтерфейсом PCI-E 1.0, в материнські плати, які підтримують PCI-E 3.0 або 2.0, тут взагалі нічого не обмежується, тому будьте спокійні з приводу сумісності. Якщо, звісно ж, з іншими факторами все гаразд, до таких можна віднести недостатньо потужний блок живлення тощо.

Загалом, ми досить докладно поговорили щодо PCI-Express, що дозволить вам позбавитися безлічі неясностей і сумнівів щодо сумісності та розуміння відмінностей у версіях PCI-E.

Якщо запитати, який інтерфейс слід використовувати для твердотільного накопичувача з підтримкою протоколу NVMe, то будь-яка людина (загалом знає, що таке NVMe) відповість: звичайно PCIe 3.0 x4! Щоправда, з обґрунтуванням у нього, найімовірніше, виникнуть складності. У найкращому разі отримаємо відповідь, що такі накопичувачі підтримують PCIe 3.0 x4, а пропускна спроможність інтерфейсу має значення. Мати має, проте всі розмови про це почалися тільки тоді, коли деяким накопичувачам на деяких операціях стало тісно в рамках «звичайного» SATA. Але між його 600 МБ/с і (так само теоретичними) 4 ГБ/с інтерфейсу PCIe 3.0 x4 - просто прірва, причому заповнена масою варіантів! А раптом і однієї лінії PCIe 3.0 вистачить, оскільки це вже в півтора рази більше за SATA600? Масла у вогонь підливають виробники контролерів, які погрожують у бюджетній продукції перейти на PCIe 3.0 x2, а також той факт, що у багатьох користувачів такого немає. Точніше, теоретично є, але звільнити їх можна, лише переконфігурувавши систему чи навіть щось у ній змінивши, чого не хочеться. А ось купити топовий твердотільний накопичувач – хочеться, але є побоювання, що користі від цього не буде зовсім ніякої (навіть моральне задоволення від результатів тестових утиліт).

Але так це чи ні? Іншими словами, чи потрібно дійсно орієнтуватися виключно на режим роботи, що підтримується - чи все-таки на практиці можна поступитися принципами? Саме це ми сьогодні й вирішили перевірити. Нехай перевірка буде швидкою і не претендує на вичерпну повноту, однак отриманої інформації має бути достатньо (як нам здається) хоча б для того, щоб замислитися... А поки що коротко ознайомимося з теорією.

PCI Express: існуючі стандарти та їх пропускна спроможність

Почнемо з того, що є PCIe і з якою швидкістю цей інтерфейс працює. Часто його називають «шиною», що дещо невірно ідеологічно: як такої шини, з якою з'єднані всі пристрої, немає. Насправді є набір з'єднань «точка-точка» (схожий на інші послідовні інтерфейси) з контролером у середині і приєднаними до нього пристроями (кожне з яких саме по собі може бути і концентратором наступного рівня).

Перша версія PCI Express з'явилася майже 15 років тому. Орієнтація використання всередині комп'ютера (нерідко - й у межах однієї плати) дозволила зробити стандарт швидкісним: 2,5 гігатранзакції на секунду. Оскільки послідовний і дуплексний інтерфейс, одна лінія PCIe (x1; фактично атомарна одиниця) забезпечує передачу даних на швидкостях до 5 Гбіт/с. Однак у кожному напрямі - лише половина від цього, тобто 2,5 Гбіт/с, причому це повна швидкість інтерфейсу, а не "корисна": для підвищення надійності кожен байт кодується 10 бітами, так що теоретична пропускна спроможність однієї лінії PCIe 1.x становить приблизно 250 МБ/с у кожну сторону. Насправді потрібно ще передавати службову інформацію, й у результаті правильніше говорити про ≈200 МБ/с передачі даних. Що, втім, на той час не тільки покривало потреби більшості пристроїв, а й забезпечувало солідний запас: досить згадати, що попередниця PCIe в сегменті масових системних інтерфейсів, а саме шина PCI, забезпечувала пропускну здатність в 133 МБ/с. І навіть якщо розглядати не тільки масову реалізацію, але й усі варіанти PCI, то максимумом були 533 МБ/с, причому на всю шину, тобто така ПС ділилася на всі підключені до неї пристрої. Тут же 250 МБ/с (оскільки для PCI наводиться зазвичай повна, а чи не корисна пропускна спроможність) однією лінію - в монопольному використанні. А для пристроїв, яким потрібно більше, спочатку була передбачена можливість агрегування кількох ліній в єдиний інтерфейс, за ступенями двійки - від 2 до 32, тобто передбачений стандартом варіант х32 в кожну сторону міг передавати вже до 8 ГБ/с. У персональних комп'ютерах х32 не використовувався через складність створення та розведення відповідних контролерів та пристроїв, так що максимумом став варіант із 16 лініями. Використовувався він (та й зараз використовується) переважно відеокартами, оскільки більшості пристроїв стільки не потрібно. Взагалі, чималої їх кількості та однієї лінії цілком достатньо, але деякі застосовують з успіхом і х4, і х8: якраз на накопичувальну тему - RAID-контролери або SSD.

Час на місці не стояло і близько 10 років тому з'явилася друга версія PCIe. Поліпшення стосувалися не тільки швидкостей, але і в цьому відношенні було зроблено крок уперед - інтерфейс почав забезпечувати 5 гігатранзакцій на секунду із збереженням тієї ж схеми кодування, тобто пропускна спроможність подвоїлася. І ще раз вона подвоїлася у 2010 році: PCIe 3.0 забезпечує 8 (а не 10) гігатранзакцій на секунду, але надмірність зменшилася – тепер для кодування 128 біт використовується 130, а не 160, як раніше. В принципі, і версія PCIe 4.0 з черговим подвоєнням швидкостей вже готова з'явитися на папері, але найближчим часом в залізі ми навряд чи побачимо її масово. Насправді і PCIe 3.0 досі в масі платформ використовується спільно з PCIe 2.0, тому що продуктивність останньої для багатьох сфер застосування просто... не потрібна. А де потрібна – працює старий добрий метод агрегації ліній. Тільки кожна з них стала за минулі роки вчетверо швидше, тобто PCIe 3.0 х4 - це PCIe 1.0 x16, найшвидший слот в комп'ютерах середини нульових. Саме цей варіант підтримують топові контролери SSD, і його рекомендується використовувати. Зрозуміло, якщо така можливість є - багато чимало. А якщо її нема? Чи виникатимуть якісь проблеми, і якщо так, то які? Ось із цим питанням нам і належить розібратися.

Методика тестування

Провести тести з різними версіями стандарту PCIe нескладно: практично всі контролери дозволяють використовувати не тільки підтримуваний ними, але й більш ранні. Ось із кількістю ліній – складніше: нам хотілося безпосередньо протестувати і варіанти з однією-двома лініями PCIe. Використовувана нами зазвичай плата Asus H97-Pro Gamer на чіпсеті Intel H97 повного набору не підтримує, але крім процесорного слота х16 (який зазвичай і використовується) на ній є ще один, що працює в режимах PCIe 2.0 х2 або х4. Ось цією трійкою ми й скористалися, додавши до неї ще й режим PCIe 2.0 "процесорного" слота, щоб оцінити, чи є різниця. Все-таки в цьому випадку між процесором і SSD сторонніх "посередників" немає, а ось при роботі з "чіпсетним" слотом - є: власне чіпсет, що фактично з'єднується з процесором PCIe 2.0 x4. Можна було додати ще кілька режимів роботи, але основну частину дослідження ми збиралися провести на іншій системі.

Справа в тому, що ми вирішили скористатися нагодою і заразом перевірити одну «міську легенду», а саме повіру про корисність використання топових процесорів для тестування накопичувачів. Ось і взяли восьмиядерний Core i7-5960X - родича, що зазвичай застосовується в тестах Core i3-4170 (це Haswell і Haswell-E), але у якого ядер вчетверо більше. Крім того, виявлена в засіках плата Asus Sabertooth X99 нам сьогодні корисна наявністю слота PCIe x4, здатного на ділі працювати як х1 або х2. У цій системі ми протестували три варіанти х4 (PCIe 1.0/2.0/3.0) від процесора і чіпсетні PCIe 1.0 х1, PCIe 1.0 х2, PCIe 2.0 х1 і PCIe 2.0 х2 (у всіх випадках чіпсетні конфігурації відзначені на діаграмі (c)). Чи є сенс зараз звертатися до першої версії PCIe, враховуючи те, що навряд чи знайдеться хоч одна плата з підтримкою тільки цієї версії стандарту, здатна завантажитися з NVMe-пристрою? З практичної точки зору - ні, а ось для перевірки апріорі передбачуваного співвідношення PCIe 1.1х4 = PCIe 2.0х2 і подібних воно нам знадобиться. Якщо перевірка покаже, що масштабованість шини відповідає теорії, значить, і неважливо, що нам не вдалося поки що отримати практично значущі способи підключення PCIe 3.0 x1/х2: перший буде ідентичний саме PCIe 1.1 х4 або PCIe 2.0 х2, а другий - PCIe 2.0 х4 . А вони маємо.

У плані ПЗ ми обмежилися лише Anvil's Storage Utilities 1.1.0: різноманітні низькорівневі характеристики накопичувачів вона вимірює непогано, а нічого іншого нам і не потрібно. Навіть навпаки: будь-який вплив інших компонентів системи є вкрай небажаним, тому низькорівнева синтетика для наших цілей безальтернативна.

Як «робоче тіло» ми використовували Patriot Hellfire ємністю 240 ГБ. Як було встановлено при його тестуванні, це не рекордсмен за продуктивністю, але його швидкісні характеристики цілком відповідають результатам кращих SSD того ж класу і тієї ж ємності. Та й повільніші пристрої на ринку вже є, причому їх ставатиме дедалі більше. В принципі, можна буде повторити тести і з чимось швидшим, проте, як нам здається, потреби в цьому немає – результати передбачувані. Але не забігатимемо вперед, а подивимося, що ж у нас вийшло.

Результати тестів

Тестуючи Hellfire, ми звернули увагу на те, що максимальну швидкість на послідовних операціях з нього можна «вичавити» лише багатопоточним навантаженням, так що це теж треба брати до уваги на майбутнє: теоретична пропускна здатність на те й теоретична, що «реальні» дані отримані в різних програмах за різними сценаріями, більше залежатимуть не від неї, а від цих самих програм і сценаріїв - у тому випадку, звичайно, коли не завадять обставини непереборної сили:) Саме такі обставини ми зараз і спостерігаємо: вище вже було сказано , що PCIe 1.x x1 – це ≈200 МБ/с, і саме це ми й бачимо. Дві лінії PCIe 1.x або одна PCIe 2.0 – удвічі швидше, і саме це ми й бачимо. Чотири лінії PCIe 1.x, дві PCIe 2.0 або одна PCIe 3.0 - ще вдвічі швидше, що підтвердилося для перших двох варіантів, тож і третій навряд чи відрізнятиметься. Тобто в принципі масштабованість, як і передбачалося, ідеальна: лінійні операції, флеш з ними справляється добре, так що інтерфейс має значення. Флеш перестає справлятися добрена PCIe 2.0 x4 для запису (означає, підійде і PCIe 3.0 x2). Читання «може» більше, але останній крок дає вже півтора-, а не дворазовий (яким він потенційно має бути) приріст. Також відзначимо, що помітної різниці між чіпсетним та процесорним контролером немає, та й між платформами теж. Втім, LGA2011-3 трохи попереду, але на зовсім небагато.

Все рівно та красиво. Але шаблони не рве: максимум у цих тестах становить лише трохи більше 500 МБ/с, а це цілком під силу навіть SATA600 або (у додатку до сьогоднішнього тестування) PCIe 1.0 х4 / PCIe 2.0 х2 / PCIe 3.0х1. Саме так: не варто лякатися випуску бюджетних контролерів під PCIe х2 або наявності лише такої кількості ліній (причому версії стандарту 2.0) у слотах М.2 на деяких платах, коли більше не потрібно. Іноді й стільки не потрібно: максимальних результатів досягнуто при черзі до 16 команд, що для масового ПЗ не типово. Найчастіше зустрічається черга з 1-4 командами, а для цього обійтися можна і однією лінією першого PCIe і навіть першим SATA. Втім, накладні витрати та інше мають місце бути, тому швидкий інтерфейс корисний. Однак надмірно швидкий – хіба що не шкідливий.

А ще в цьому тесті по-різному поводяться платформи, причому з одиничною чергою команд принципово по-різному. "Біда" зовсім не в тому, що багато ядер - погано. Вони тут все одно не використовуються, хіба що одне, і не настільки, щоб на повну силу розгорнувся буст-режим. Ось і маємо різницю десь у 20% за частотою ядер і півтора рази по кеш-пам'яті – вона у Haswell-E працює на більш низькій частоті, а не синхронно з ядрами. Загалом, топова платформа може стати в нагоді хіба що для вибивання максимуму «йопсів» за допомогою максимально багатопотокового режиму з великою глибиною черги команд. Шкода тільки, що з погляду практичної роботи це зовсім сферична синтетика у вакуумі:)

На записі стан справ принципово не змінилося – у всіх сенсах. Але, що забавно, на обох системах найшвидшим виявився режим PCIe 2.0 х4 у процесорному слоті. На обох! І при багаторазових перевірках/перевірках. Тут мимоволі замислишся, чи потрібні ці ваші нові стандартиабо краще взагалі нікуди не поспішати...

При роботі з блоками різного розміру теоретична ідилія розбивається про те, що підвищення швидкості інтерфейсу все ж таки має сенс. Результати цифри такі, що вистачило б пари ліній PCIe 2.0, але реально в такому випадку продуктивність нижче, ніж у PCIe 3.0 х4, нехай і не в рази. І взагалі тут бюджетна платформа топову «забиває» значно більшою мірою. Адже саме такого роду операції в основному в прикладному ПЗ і зустрічаються, тобто ця діаграма - найбільш наближена до реальності. У результаті немає нічого дивного, що ніякого "вау-ефекту" товсті інтерфейси та модні протоколи не дають. Точніше, що переходить з механіки - дадуть, але такою самою, якою йому забезпечить будь-який твердотільний накопичувач з будь-яким інтерфейсом.

Разом

Для полегшення сприйняття картини по лікарні в цілому ми скористалися балом, що видається програмою (сумарним - з читання та запису), провівши його нормування за «чіпсетним» режимом PCIe 2.0 x4: на даний момент саме він є найбільш масово доступним, оскільки зустрічається навіть на LGA1155 або платформах AMD без необхідності "кривдити" відеокарту. Крім того, він еквівалентний PCIe 3.0 x2, який готуються освоїти бюджетні контролери. Та й на новій платформі AMD АМ4, знову ж таки, саме цей режим можна отримати без впливу на дискретну відеокарту.

Отже, що бачимо? Застосування PCIe 3.0 x4 за наявності можливості є, безумовно, кращим, але не необхідним: NVMe-накопичувачам середнього класу (у своєму спочатку топовому сегменті) він приносить буквально 10% додаткової продуктивності. Та й то - за рахунок операцій загалом не так часто зустрічаються на практиці. Навіщо ж у разі реалізований саме цей варіант? По-перше, була така можливість, а запас кишені не тягне. По-друге, є накопичувачі та швидше, ніж наш тестовий Patriot Hellfire. По-третє, є такі сфери діяльності, де «атипові» для настільної системи навантаження – якраз цілком типові. Причому саме там найкритичніша швидкодія системи зберігання даних або, принаймні, можливість зробити її частину дуже швидкою. Але до звичайних персональних комп'ютерів це не стосується.

Вони, як бачимо, і використання PCIe 2.0 x2 (або, відповідно, PCIe 3.0 х1) не призводить до драматичного зниження продуктивності - лише на 15-20%. І це незважаючи на те, що потенційні можливості контролера у цьому випадку ми обмежили вчетверо! Для багатьох операцій та такої пропускної спроможності достатньо. Ось однієї лінії PCIe 2.0 вже недостатньо, тому контролерам має сенс підтримувати саме PCIe 3.0 – і в умовах жорсткої нестачі ліній у сучасній системі це працюватиме непогано. Крім того, корисна ширина х4 - навіть за відсутності підтримки сучасних версій PCIe в системі вона все одно дозволить працювати з нормальною швидкістю (нехай і повільніше, ніж могло б потенційно), якщо знайдеться більш-менш широкий слот.

У принципі, велика кількість сценаріїв, в яких вузьким місцем виявляється власне флеш-пам'ять (так, це можливо і властиво не тільки механіці), призводить до того, що чотири лінії третьої версії PCIe на цьому накопичувачі обганяють одну першу приблизно в 3,5 рази - теоретична ж пропускна здатність цих двох випадків відрізняється у 16 разів. З чого, очевидно, годі було, що необхідно швидко бігти освоювати дуже повільні інтерфейси - їхній час пішов безповоротно. Просто багато можливостей швидких інтерфейсів можуть бути реалізовані лише в майбутньому. Або в умовах, з якими звичайний користувач звичайного комп'ютера ніколи в житті безпосередньо не зіткнеться (за винятком любителів мірятися відомо чим). Власне, і все.

У цій статті ми розповімо про причини успіху шини PCI та дамо опис високопродуктивної технології, яка приходить їй на зміну – шини PCI Express. Також ми розглянемо історію розвитку, апаратні та програмні рівні шини PCI Express, особливості її реалізації та перерахуємо її переваги.

Коли на початку 1990-х років. вона з'явилася, то за своїми технічними характеристиками значно перевершувала всі шини, що існували до того моменту, такі, як ISA, EISA, MCA і VL-bus. Тоді шина PCI(Peripheral Component Interconnect - взаємодія периферійних компонентів), що працювала на частоті 33 МГц, добре підходила більшості периферійних пристроїв. Але сьогодні ситуація багато в чому змінилася. Насамперед, значно зросли тактові частоти процесора та пам'яті. Наприклад, тактова частота процесорів збільшилася з 33 МГц до декількох ГГц, тоді як робоча частота PCI збільшилася всього до 66 МГц. Поява таких технологій, як Gigabit Ethernet та IEEE 1394B, загрожувала тим, що вся пропускна здатність шини PCI може піти на обслуговування одного-єдиного пристрою на основі даних технологій.

При цьому архітектура PCI має низку переваг у порівнянні з попередниками, тому повністю переглядати було нераціонально. Насамперед, вона не залежить від типу процесора, підтримує буферну ізоляцію, технологію bus mastering (захоплення шини) та технологію PnP у повному обсязі. Буферна ізоляція означає, що шина PCI діє незалежно від внутрішньої шини процесора, що дає можливість шині процесора функціонувати незалежно від швидкості та завантаженості системної шини. Завдяки технології захоплення шини периферійні пристрої отримали можливість безпосередньо керувати процесом передачі даних по шині, замість очікувати допомоги від центрального процесора, що позначилося б на продуктивності системи. Нарешті, підтримка Plug and Play дозволяє здійснювати автоматичне налаштування і конфігурування пристроїв, що користуються нею, і уникнути метушні з джамперами і перемикачами, яка неабияк псувала життя власникам ISA-пристроїв.

Незважаючи на безперечний успіх PCI, нині вона стикається із серйозними проблемами. Серед них – обмежена пропускна спроможність, нестача функцій передачі даних у реальному часі та відсутність підтримки мережевих технологій нового покоління.

Порівняльні характеристики різних стандартів PCI

Слід врахувати, що реальна пропускна здатність може бути меншою за теоретичну через принцип роботи протоколу та особливості топології шини. До того ж загальна пропускна здатність розподіляється між усіма підключеними до неї пристроями, тому чим більше пристроїв сидить на шині, тим менша пропускна здатність дістається кожному з них.

Такі вдосконалення стандарту, як PCI-X і AGP, були покликані усунути її головний недолік - низьку тактову частоту. Однак збільшення тактової частоти в цих реалізаціях спричинило зменшення ефективної довжини шини і кількості роз'ємів.

Нове покоління шини - PCI Express (або скорочено PCI-E), було вперше представлене в 2004 році і покликане було вирішити всі ті проблеми, з якими зіткнулася її попередниця. Сьогодні більшість нових комп'ютерів постачається шиною PCI Express. Хоча стандартні слоти PCI у них також присутні, проте не за горами той час, коли шина стане надбанням історії.

Архітектура PCI Express

Архітектура шини має багаторівневу структуру, як показано малюнку.

Шина підтримує модель адресації PCI, що дозволяє працювати з нею всім драйверам і програмам, що існують на даний момент. Крім того, шина PCI Express використовує стандартний механізм PnP, передбачений попереднім стандартом.

Розглянемо призначення різних рівнів організації PCI-E. На програмному рівні шини формуються запити читання/запису, які передаються транспортному рівні з допомогою спеціального пакетного протоколу. Рівень даних відповідає за перешкодостійке кодування та забезпечує цілісність даних. Базовий апаратний рівень складається з подвійного симплексного каналу, що складається з передавальної та приймаючої пари, які разом називаються лінією. Загальна швидкість шини в 2,5 Гб/с означає, що пропускна спроможність кожної лінії PCI Express становить 250 Мб/c у кожну сторону. Якщо взяти до уваги втрати на накладні витрати протоколу, для кожного пристрою доступно близько 200 Мб/c. Ця пропускна здатність у 2-4 рази вища, ніж та, яка була доступна для пристроїв PCI. І, на відміну від PCI, у тому випадку, якщо пропускна здатність розподіляється між усіма пристроями, то вона в повному обсязі дістається кожному пристрою.

На сьогоднішній день існує кілька версій стандарту PCI Express, що відрізняються своєю пропускною здатністю.

Пропускна здатність шини PCI Express x16 для різних версій PCI-E, Гб/c:

- 32/64

- 64/128

- 128/256

Формати шини PCI-E

На даний момент доступні різні варіанти форматів PCI Express, залежно від призначення платформи – комп'ютер, ноутбук або сервер. Сервери, що потребують більшої пропускної здатності, мають більше слотів PCI-E, і ці слоти мають більшу кількість з'єднувальних ліній. На противагу цьому ноутбуки можуть мати лише одну лінію для середньошвидкісних пристроїв.

Відеокарта із інтерфейсом PCI Express x16.

Плати розширення PCI Express дуже схожі на плати PCI, однак роз'єми PCI-E відрізняються підвищеним зчепленням, що дозволяє бути впевненим у тому, що плата не вислизне зі слота через вібрацію або транспортування. Існує кілька форм-факторів слотів PCI Express, розмір яких залежить від кількості ліній, що використовуються. Наприклад, шина, що має 16 ліній, позначається як PCI Express x16. Хоча загальна кількість ліній може досягати 32, практично більшість материнських плат в даний час оснащені шиною PCI Express x16.

Карти менших форм-факторів можуть підключатися до роз'ємів для великих без шкоди для працездатності. Наприклад, картка PCI Express х1 може підключатися до роз'єму PCI Express x16. Як і у випадку шини PCI, для підключення пристроїв за потреби можна використовувати РCI Express-подовжувач.

Зовнішній вигляд рознімання різних типів на материнській платі. Зверху донизу: слот PCI-X, слот PCI Express х8, слот PCI, слот PCI Express х16.

Express Card

Стандарт Express Card пропонує дуже простий спосіб додавання обладнання до системи. Цільовим ринком для модулів Express Card є ноутбуки та невеликі ПК. На відміну від традиційних плат розширення настільних комп'ютерів, картка Express може підключатися до системи будь-коли під час роботи комп'ютера.