Isinasalin namin... Isalin ang Chinese (Pinasimple) Chinese (Tradisyonal) Ingles Pranses Aleman Italyano Portuges Ruso Espanyol Turkish

Sa kasamaang palad, hindi namin magawang isalin ang impormasyong ito sa ngayon - pakisubukang muli sa ibang pagkakataon.

Panimula

Ang software na idinisenyo para sa komunikasyon at paglilipat ng data ay nangangailangan ng napakataas na pagganap dahil naglilipat ito ng malaking bilang ng maliliit na data packet. Isa sa mga tampok ng virtualization application development mga function ng network(NFV) ay kinakailangan na gumamit ng virtualization sa pinakamaraming lawak na posible, ngunit sa parehong oras mga kinakailangang kaso i-optimize ang mga application para sa hardware na ginamit.

Sa artikulong ito, iha-highlight ko ang tatlong feature ng mga Intel® processor na kapaki-pakinabang para sa pag-optimize ng performance ng mga NFV application: Cache Allocation Technologies (CAT), Intel® Advanced Vector Extensions 2 (Intel® AVX2) para sa pagpoproseso ng vector, at Intel® Transactional Synchronization Extension (Intel® TSX).

Paglutas ng priority inversion na problema gamit ang CAT

Kapag ang isang mababang priyoridad na function ay nagnanakaw ng mga mapagkukunan mula sa isang mataas na priyoridad na function, tinatawag namin itong "priority inversion."

Hindi lahat ng virtual function ay ginawang pantay. Halimbawa, ang function ng pagruruta ay mahalaga para sa oras ng pagpoproseso at pagganap, habang ang function ng pag-encode ng media ay hindi kasinghalaga. Ang tampok na ito ay maaaring pahintulutan na pana-panahong mag-drop ng mga packet nang hindi naaapektuhan ang karanasan ng user, dahil walang makakapansin sa pagbaba ng video frame rate mula 20 hanggang 19 na mga frame bawat segundo.

Ang default na cache ay idinisenyo sa paraang natatanggap ito ng pinaka-aktibong mamimili ang pinakamalaking bahagi. Ngunit ang pinaka-aktibong mamimili ay hindi palaging ang pinakamahalagang aplikasyon. Sa katunayan, ang kabaligtaran ay kadalasang totoo. Ang mga application na may mataas na priyoridad ay na-optimize, ang dami ng data ng mga ito ay nabawasan sa pinakamaliit na posibleng hanay. Ang mga application na mababa ang priyoridad ay hindi nangangailangan ng mas maraming pagsisikap sa pag-optimize, kaya malamang na kumonsumo sila ng mas maraming memorya. Ang ilan sa mga function na ito ay kumonsumo ng maraming memorya. Halimbawa, ang function na view ng package para sa pagsusuri sa istatistika ay may mababang priyoridad, ngunit kumokonsumo ng maraming memorya at ginagamit nang husto ang cache.

Madalas na ipinapalagay ng mga developer na kung maglalagay sila ng isang application na may mataas na priyoridad sa isang partikular na kernel, magiging ligtas ang application doon at hindi maaapektuhan ng mga application na mababa ang priyoridad. Sa kasamaang palad, hindi ito ang kaso. Ang bawat core ay may sariling Level 1 cache (L1, ang pinakamabilis ngunit pinakamaliit na cache) at isang Level 2 cache (L2, bahagyang mas malaki ngunit mas mabagal). Mayroong hiwalay na L1 cache area para sa data (L1D) at program code (L1I, "I" ay nangangahulugang mga tagubilin). Ang pangatlong antas ng cache (ang pinakamabagal) ay karaniwan sa lahat ng mga core ng processor. Sa mga arkitektura ng processor ng Intel® hanggang sa at kabilang ang Broadwell family, ang L3 cache ay ganap na kasama, ibig sabihin, naglalaman ito ng lahat ng nasa L1 at L2 cache. Dahil sa paraan ng paggana ng inclusion cache, kung may aalisin sa ikatlong antas ng cache, aalisin din ito sa kaukulang una at ikalawang antas ng cache. Nangangahulugan ito na ang isang mababang priyoridad na application na nangangailangan ng espasyo sa L3 cache ay maaaring magpalit ng data mula sa L1 at L2 na mga cache ng isang mataas na priyoridad na application, kahit na ito ay tumatakbo sa ibang core.

Noong nakaraan, mayroong isang diskarte upang malutas ang problemang ito na tinatawag na "warm-up." Kapag ang pag-access sa L3 cache ay nakikipagkumpitensya, ang "nagwagi" ay ang application na madalas na nag-a-access sa memorya. Samakatuwid, ang solusyon ay ang pagkakaroon ng isang mataas na priyoridad na function na patuloy na ina-access ang cache, kahit na walang ginagawa. Ito ay hindi isang napaka-eleganteng solusyon, ngunit ito ay madalas na medyo katanggap-tanggap, at hanggang kamakailan ay walang mga alternatibo. Ngunit ngayon ay may alternatibo na: ang Intel® Xeon® E5 v3 processor na pamilya ay nagpapakilala ng Cache Allocation Technology (CAT), na nagbibigay sa iyo ng kakayahang maglaan ng cache batay sa mga application at klase ng serbisyo.

Epekto ng priority inversion

Upang ipakita ang epekto ng pagbabaligtad ng priyoridad, sumulat ako ng isang simpleng microbench na pana-panahong nagpapatakbo ng isang naka-link na traversal ng listahan sa isang thread na may mataas na priyoridad, habang ang thread na may mababang priyoridad ay patuloy na nagpapatakbo ng isang in-memory copy function. Ang mga thread na ito ay itinalaga sa iba't ibang mga core ng parehong processor. Ginagaya nito ang pinakamasamang sitwasyon para sa pagtatalo sa mapagkukunan: ang operasyon ng pagkopya ay nangangailangan ng maraming memorya, kaya malamang na makagambala sa mas mahalagang thread ng access sa listahan.

Narito ang code sa C.

// Bumuo ng naka-link na listahan ng laki N na may pseudo-random pattern void init_pool(list_item *head, int N, int A, int B) ( int C = B; list_item *current = head; for (int i = 0; i< N - 1; i++) { current->lagyan ng tsek = 0;< N - 1; i++) { current = current->C = (A*C + B) % N;< 50; j++) { list_item* current = head; #if WARMUP_ON while(in_copy) warmup_list(head, N); #else while(in_copy) spin_sleep(1); #endif i1 = __rdtsc(); for(int i = 0; i < N; i++) { current->kasalukuyang->susunod = (list_item*)&(head[C]);

kasalukuyang = kasalukuyang->susunod;

- ) ) // Pindutin muna ang N elemento sa isang naka-link na listahan void warmup_list(list_item* current, int N) ( bool write = (N > POOL_SIZE_L2_LINES) ? true: false; for(int i = 0; i

- susunod;

- kung (isulat) kasalukuyang->tik++;

) ) void measure(list_item* head, int N) ( unsigned __long long i1, i2, avg = 0; for (int j = 0; j

Ang pangunahing tagapagpahiwatig ay ang pulang-kayumanggi na linya, ito ay tumutugma sa isang programa na walang kopya ng thread sa memorya, iyon ay, nang walang pagtatalo. Ang asul na linya ay nagpapakita ng mga kahihinatnan ng priority inversion: dahil sa memory copy function, ang pag-access sa listahan ay mas matagal. Ang epekto ay lalo na malaki kung ang listahan ay umaangkop sa isang high-speed L1 o L2 cache. Kung ang listahan ay napakalaki na hindi ito magkasya sa ikatlong antas ng cache, ang epekto ay bale-wala.

Ang berdeng linya ay nagpapakita ng warm-up effect kapag gumagana ang memory copy function: ang oras ng pag-access ay bumababa nang husto at lumalapit sa base value.

Kung paganahin namin ang CAT at maglalaan ng mga bahagi ng L3 cache sa bawat core para sa eksklusibong paggamit, ang mga resulta ay magiging napakalapit sa baseline (masyadong malapit na ipakita sa diagram), na aming layunin.

PinapaganaPUSA

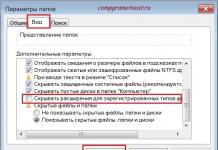

Una sa lahat, tiyaking sinusuportahan ng platform ang CAT. Maaari mong gamitin ang pagtuturo ng CPUID sa pamamagitan ng pagsuri sa dahon ng address 7, idinagdag ang subleaf 0 upang isaad ang pagkakaroon ng CAT.

Kung pinagana at sinusuportahan ang CAT, may mga rehistro ng MSR na maaaring i-program upang maglaan ng iba't ibang bahagi ng L3 cache sa iba't ibang mga core.

Lahat meron socket ng processor may mga rehistro ng MSR na IA32_L3_MASKn (halimbawa, 0xc90, 0xc91, 0xc92, 0xc93). Ang mga rehistrong ito ay nag-iimbak ng kaunting mask na nagsasaad kung magkano ang L3 cache na dapat ilaan para sa bawat klase ng serbisyo (COS). Iniimbak ng 0xc90 ang paglalaan ng cache para sa COS0, 0xc91 para sa COS1, atbp.

Halimbawa, ang diagram na ito ay nagpapakita ng ilang posibleng bit mask para sa iba't ibang klase ng serbisyo upang ipakita kung paano maaaring hatiin ang cache: ang COS0 ay nakakakuha ng kalahati, ang COS1 ay nakakakuha ng quarter, at ang COS2 at COS3 ay nakakuha ng ikawalo. Halimbawa, ang 0xc90 ay maglalaman ng 11110000, at ang 0xc93 ay maglalaman ng 00000001.

Ang Direct Data Input/Output (DDIO) algorithm ay may sarili nitong hidden bit mask na nagbibigay-daan sa daloy ng data mula sa mga high-speed PCIe device gaya ng mga network adapter na mailipat sa mga partikular na lugar ng L3 cache. Gayunpaman, may posibilidad ng isang salungatan sa tinukoy na mga klase ng serbisyo, kaya kailangan mong isaalang-alang ito kapag gumagawa ng mga de-kalidad na NFV application. bandwidth. Upang subukan para sa mga salungatan, gamitin upang matukoy ang mga miss ng cache. Ang ilang BIOS ay may setting na nagbibigay-daan sa iyong tingnan at baguhin ang DDIO mask.

Ang bawat core ay may MSR register IA32_PQR_ASSOC (0xc8f) na nagsasaad kung aling klase ng serbisyo ang nalalapat sa core na iyon. Ang default na klase ng serbisyo ay 0, na nangangahulugan na ang bitmask sa MSR 0xc90 ay ginagamit. (Bilang default, ang bitmask 0xc90 ay nakatakda sa 1 upang matiyak ang maximum na availability ng cache.)

Ang pinaka simpleng modelo gamit ang CAT sa NFV - paglalaan ng L3 cache chunks sa iba't ibang mga core gamit ang mga nakahiwalay na bit mask at pagkatapos ay i-pin ang mga thread o mga virtual machine sa likod ng mga core. Kung ang mga VM ay kailangang magbahagi ng mga core upang maipatupad, posible ring gumawa ng walang kuwentang pag-aayos sa OS scheduler, magdagdag ng cache mask sa mga thread kung saan tumatakbo ang mga VM, at dynamic na paganahin ito sa bawat kaganapan sa pag-iiskedyul.

May isa pa hindi pangkaraniwang paraan gamit ang CAT para i-lock ang data sa cache. Una, lumikha ng isang aktibong cache mask at i-access ang data sa memorya upang i-load ito sa L3 cache. Pagkatapos ay huwag paganahin ang mga bit na kumakatawan sa bahaging ito ng L3 cache sa anumang CAT bitmask na gagamitin sa hinaharap. Ang data ay mai-lock sa L3 cache dahil imposible na itong paalisin mula doon (bukod sa DDIO). Sa isang NFV application, pinapayagan ng mekanismong ito ang mga medium-sized na lookup table para sa pagruruta at packet parsing na mai-lock sa L3 cache upang matiyak ang patuloy na pag-access.

Paggamit ng Intel AVX2 para sa Vector Processing

Nagbibigay-daan sa iyo ang mga tagubilin sa SIMD (isang pagtuturo, maraming data) na gawin ang parehong operasyon sa iba't ibang piraso ng data nang sabay-sabay. Ang mga tagubiling ito ay kadalasang ginagamit upang pabilisin ang mga pagkalkula ng floating point, ngunit magagamit din ang mga bersyon ng integer, boolean, at data ng mga tagubilin.

Depende sa processor na iyong ginagamit, magkakaroon ka ng iba't ibang pamilya ng mga tagubilin sa SIMD na magagamit mo. Mag-iiba din ang laki ng vector na naproseso ng mga command:

- Sinusuportahan ng SSE ang 128-bit na mga vector.

- Sinusuportahan ng Intel AVX2 ang mga integer na tagubilin para sa 256-bit na mga vector at nagpapatupad ng mga tagubilin para sa mga operasyon ng pagtitipon.

- Ang mga extension ng AVX3 sa hinaharap na mga arkitektura ng Intel® ay susuportahan ang 512-bit na mga vector.

Maaaring gamitin ang isang 128-bit na vector para sa dalawang 64-bit na variable, apat na 32-bit na variable, o walong 16-bit na variable (depende sa ginamit na mga tagubilin sa SIMD). Ang mga mas malalaking vector ay makakatanggap ng higit pang mga elemento ng data. Dahil sa mataas na hinihingi ng throughput ng mga NFV application, dapat mong palaging gamitin ang pinakamakapangyarihang mga tagubilin sa SIMD (at nauugnay na hardware), na kasalukuyang Intel AVX2.

Ang mga tagubilin sa SIMD ay kadalasang ginagamit upang maisagawa ang parehong operasyon sa isang vector ng mga halaga, tulad ng ipinapakita sa figure. Dito, ang pagpapatakbo ng paggawa ng X1opY1 hanggang X4opY4 ay iisang pagtuturo, sabay-sabay na nagpoproseso ng mga item ng data X1 hanggang X4 at Y1 hanggang Y4. Sa halimbawang ito, ang speedup ay magiging apat na beses na mas mabilis kaysa sa normal na (scalar) execution dahil apat na operasyon ang pinoproseso nang sabay-sabay. Ang speedup ay maaaring kasing laki ng SIMD vector ay malaki. Ang mga application ng NFV ay madalas na nagpoproseso ng maraming packet stream sa parehong paraan, kaya ang mga tagubilin sa SIMD ay nagbibigay ng natural na paraan upang ma-optimize ang pagganap.

Para sa mga simpleng loop, kadalasang awtomatikong i-vector ng compiler ang mga operasyon sa pamamagitan ng paggamit ng pinakabagong mga tagubilin sa SIMD na magagamit para sa isang partikular na CPU (kung gagamitin mo ang mga tamang flag ng compiler). Maaari mong i-optimize ang iyong code upang magamit ang pinakamodernong set ng pagtuturo na sinusuportahan ng hardware sa runtime, o maaari mong i-compile ang code para sa isang partikular na target na arkitektura.

Sinusuportahan din ng mga operasyon ng SIMD ang mga memory load, pagkopya ng hanggang 32 bytes (256 bits) mula sa memory patungo sa isang rehistro. Ito ay nagpapahintulot sa data na mailipat sa pagitan ng memorya at mga rehistro, pag-bypass sa cache, at upang mangolekta ng data mula sa iba't ibang lokasyon sa memorya. Maaari ka ring magsagawa ng iba't ibang mga operasyon gamit ang mga vectors (pagbabago ng data sa loob ng isang rehistro) at pag-iimbak ng mga vectors (pagsusulat ng hanggang 32 byte mula sa isang rehistro hanggang sa memorya).

Ang Memcpy at memmov ay mga kilalang halimbawa ng mga pangunahing gawain na ipinatupad gamit ang mga tagubilin sa SIMD mula sa simula dahil ang pagtuturo ng REP MOV ay masyadong mabagal. Regular na na-update ang memcpy code sa mga library ng system upang magamit ang pinakabagong mga tagubilin sa SIMD. Ang CPUID manager table ay ginamit upang makakuha ng impormasyon tungkol sa kung alin sa mga pinakabagong bersyon ang magagamit para sa paggamit. Kasabay nito, ang pagpapatupad ng mga bagong henerasyon ng mga tagubilin ng SIMD sa mga aklatan ay karaniwang naantala.

Halimbawa, susunod na pamamaraan Ang memcpy, na gumagamit ng simpleng loop, ay nakabatay sa mga built-in na function (sa halip na library code), kaya ma-optimize ito ng compiler para sa pinakabagong bersyon ng mga tagubilin ng SIMD.

Mm256_store_si256((__m256i*) (dest++), (__m256i*) (src++))

Nag-compile ito sa sumusunod na code ng pagpupulong at may dobleng pagganap ng mga kamakailang aklatan.

C5 fd 6f 04 04 vmovdqa (%rsp,%rax,1),%ymm0 c5 fd 7f 84 04 00 00 vmovdqa %ymm0.0x10000(%rsp,%rax,1)

Kokopyahin ang assembly code mula sa isang inline na function ng 32 byte (256 bits) gamit ang pinakabagong available na mga tagubilin sa SIMD, samantalang ang code ng library na gumagamit ng SSE ay kokopyahin lamang ang 16 bytes (128 bits).

Ang mga application ng NFV ay madalas na kailangang magsagawa ng operasyon sa pagkolekta sa pamamagitan ng paglo-load ng data mula sa maraming lokasyon papunta sa iba't ibang lugar hindi magkakasunod na alaala. Halimbawa, maaaring i-cache ng network adapter ang mga papasok na packet gamit ang DDIO. Ang isang NFV application ay maaaring kailangan lang ng access sa bahagi ng header ng network kasama ang patutunguhang IP address. Gamit ang operasyon ng pagkolekta, ang application ay maaaring mangolekta ng data para sa 8 packet sa parehong oras.

Hindi na kailangang gumamit ng mga inline na function o assembly code para sa operasyon ng koleksyon dahil maaaring i-vector ng compiler ang code, tulad ng para sa program na ipinapakita sa ibaba, batay sa isang pagsubok na summing ng mga numero mula sa mga pseudo-random na lokasyon sa memorya.

Int a; int b; para sa (i = 0; i< 1024; i++) a[i] = i; for (i = 0; i < 64; i++) b[i] = (i*1051) % 1024; for (i = 0; i < 64; i++) sum += a]; // This line is vectorized using gather.

Huling linya ay pinagsama-sama sa sumusunod na code ng pagpupulong.

C5 fe 6f 40 80 vmovdqu -0x80(%rax),%ymm0 c5 ed fe f3 vpaddd %ymm3,%ymm2,%ymm6 c5 e5 ef db vpxor %ymm3,%ymm3,%ymm3 c5 d5 76 ed vpcmpeqd %ymmmpeqd ymm5,%ymm5 c4 e2 55 90 3c a0 vpgatherdd %ymm5,(%rax,%ymm4,4),%ymm7

Ang isang operasyon ng pagkolekta ay makabuluhang mas mabilis kaysa sa isang pagkakasunud-sunod ng mga pag-download, ngunit ito ay makatuwiran lamang kung ang data ay nasa cache na. Kung hindi, ang data ay kailangang kunin mula sa memorya, na nangangailangan ng daan-daan o libu-libong mga cycle ng CPU. Kung nasa cache ang data, posible ang 10x speedup

(ibig sabihin, 1000%). Kung ang data ay wala sa cache, ang speedup ay 5% lamang.

Kapag gumagamit ng mga diskarteng tulad nito, mahalagang suriin ang application upang matukoy ang mga bottleneck at maunawaan kung ang application ay gumugugol ng masyadong maraming oras sa pagkopya o pagkolekta ng data. Maaari mong gamitin ang .

Ang isa pang kapaki-pakinabang na tampok para sa NFV sa Intel AVX2 at iba pang mga operasyon ng SIMD ay bit at lohikal na mga operasyon. Sila ay ginagamit upang mapabilis hindi karaniwang code encryption, at bit checking ay maginhawa para sa mga developer ng ASN.1 at kadalasang ginagamit para sa data sa telekomunikasyon. Maaaring gamitin ang Intel AVX2 para sa mas mabilis na paghahambing ng string gamit ang mga advanced na algorithm gaya ng MPSSEF.

Gumagana nang maayos ang mga extension ng Intel AVX2 mga virtual machine. Ang pagganap ay pareho at walang mga maling paglabas ng virtual machine.

Paggamit ng Intel TSX para sa mas mataas na scalability

Ang isa sa mga hamon ng mga parallel na programa ay ang pag-iwas sa mga banggaan ng data, na maaaring mangyari kapag sinubukan ng maraming thread na gumamit ng parehong piraso ng data at sinubukan ng kahit isang thread na baguhin ang data. Upang maiwasan ang hindi mahuhulaan na mga resulta ng dalas, ginagamit ang pag-lock: hinaharangan ito ng unang thread na gumagamit ng item ng data mula sa iba pang mga thread hanggang sa makumpleto ang trabaho nito. Ngunit ang pamamaraang ito ay maaaring hindi epektibo kung mayroong madalas na nakikipagkumpitensya na mga kandado o kung ang mga kandado ay kumokontrol sa isang mas malaking bahagi ng memorya kaysa sa aktwal na kinakailangan.

Nagbibigay ang Intel Transactional Synchronization Extensions (TSX). mga tagubilin ng processor upang i-bypass ang mga lock sa panahon ng mga transaksyon sa memorya ng hardware. Nakakatulong ito na makamit ang mas mataas na scalability. Ang paraan ng paggana nito ay kapag ang isang programa ay pumasok sa isang seksyon na gumagamit ng Intel TSX upang protektahan ang mga lokasyon ng memorya, ang lahat ng mga pagtatangka sa pag-access sa memorya ay ire-record, at sa pagtatapos ng protektadong session ay awtomatiko silang iko-commit o awtomatikong ibabalik. Isinasagawa ang rollback kung, habang nag-e-execute mula sa isa pang thread, nagkaroon ng salungatan sa pag-access sa memory na maaaring magdulot ng kundisyon ng lahi (halimbawa, pagsulat sa isang lokasyon kung saan nagbabasa ng data ang isa pang transaksyon). Ang rollback ay maaari ding mangyari kung ang memory access record ay nagiging masyadong malaki para sa pagpapatupad ng Intel TSX, kung mayroong isang I/O instruction o system call, o kung may mga exception na naganap o ang mga virtual machine ay isinara. Ang mga I/O na tawag ay ibinabalik kapag ang mga ito ay hindi maaaring isagawa nang haka-haka dahil sa panlabas na interference. Ang isang system call ay isang napakakomplikadong operasyon na nagbabago ng mga singsing at memory handle at napakahirap ibalik.

Ang isang karaniwang kaso ng paggamit para sa Intel TSX ay ang access control sa isang hash table. Karaniwan, ginagamit ang isang lock ng talahanayan ng cache upang magarantiya ang pag-access sa talahanayan ng cache, ngunit pinapataas nito ang latency para sa mga thread na nakikipagkumpitensya para sa pag-access. Ang pag-lock ay kadalasang masyadong magaspang: ang buong talahanayan ay naka-lock, bagama't napakabihirang para sa mga thread na subukang i-access ang parehong mga elemento. Habang dumarami ang bilang ng mga core (at mga thread), pinipigilan ng magaspang na pag-lock ang scalability.

Gaya ng ipinapakita sa diagram sa ibaba, ang magaspang na pag-lock ay maaaring magsanhi sa isang thread na maghintay para sa isa pang thread na ilabas ang hash table, kahit na ang mga thread ay gumagamit ng iba't ibang elemento. Ang paggamit ng Intel TSX ay nagpapahintulot sa parehong mga thread na gumana, ang kanilang mga resulta ay naitala pagkatapos matagumpay na maabot ang dulo ng transaksyon. Nakikita ng hardware ang mga salungatan sa mabilisang pag-abort ng mga nakakasakit na transaksyon. Kapag gumagamit ng Intel TSX, ang thread 2 ay hindi kailangang maghintay, ang parehong mga thread ay isinasagawa nang mas maaga. Ang pag-lock sa mga hash table ay kino-convert sa fine-tune na pag-lock, na nagreresulta sa pinahusay na pagganap. Sinusuportahan ng Intel TSX ang katumpakan ng pagsubaybay sa pagtatalo sa antas ng isang linya ng cache (64 bytes).

Gumagamit ang Intel TSX ng dalawang interface ng programming upang tukuyin ang mga seksyon ng code upang magsagawa ng mga transaksyon.

- Ang Hardware Lock Bypass (HLE) ay backward compatible at madaling magamit upang mapabuti ang scalability nang hindi gumagawa ng malalaking pagbabago sa lock library. Ang HLE ay mayroon na ngayong mga prefix para sa mga naka-block na tagubilin. Ang prefix ng pagtuturo ng HLE ay senyales sa hardware na subaybayan ang estado ng lock nang hindi ito nakukuha. Sa halimbawa sa itaas, ang pagsasagawa ng mga hakbang na inilarawan ay titiyakin na ang pag-access sa iba pang mga entry ng hash table ay hindi na magreresulta sa isang lock maliban kung may sumasalungat na access sa pagsulat sa isang value na nakaimbak sa hash table. Bilang resulta, magiging parallelize ang access, kaya tataas ang scalability sa lahat ng apat na thread.

- Kasama sa interface ng RTM ang mga tahasang tagubilin para magsimula (XBEGIN), mag-commit (XEND), magkansela (XABORT), at subukan ang estado (XTEST) ng mga transaksyon. Ang mga tagubiling ito ay nagbibigay sa mga locking library ng isang mas nababaluktot na paraan upang ipatupad ang lock bypassing. Ang interface ng RTM ay nagpapahintulot sa mga aklatan na gumamit ng mga flexible na algorithm sa pagkansela ng transaksyon. Magagamit ang feature na ito para pahusayin ang performance ng Intel TSX gamit ang optimistic na pag-restart ng transaksyon, pagbabalik ng transaksyon, at iba pang advanced na diskarte. Gamit ang pagtuturo ng CPUID, maaaring bumalik ang library sa isang mas lumang pagpapatupad ng mga non-RTM lock, na pinapanatili pabalik na katugma gamit ang user level code.

- Para sa higit pang impormasyon tungkol sa HLE at RTM, inirerekomenda kong tingnan ang mga sumusunod na artikulo ng Intel Developer Zone.

Tulad ng pag-optimize ng mga primitive sa pag-synchronize gamit ang HLE o RTM, ang mga feature ng NFV data plan ay maaaring makinabang mula sa Intel TSX kapag ginagamit ang Data Plane Development Kit (DPDK).

Kapag gumagamit ng Intel TSX, ang pangunahing hamon ay hindi sa pagpapatupad ng mga extension na ito, ngunit sa pagsusuri at pagtukoy ng kanilang pagganap. May mga performance counter na maaaring gamitin sa Mga programa sa Linux* perf, at upang suriin ang tagumpay ng Intel TSX execution (bilang ng nakumpleto at bilang ng mga nakanselang cycle).

Ang Intel TSX ay dapat gamitin nang may pag-iingat at maingat na masuri sa mga NFV application dahil ang mga pagpapatakbo ng I/O sa isang lugar na protektado ng Intel TSX ay palaging may kasamang rollback, at maraming feature ng NFV ang gumagamit ng maraming I/O operations. Dapat na iwasan ang sabay-sabay na pag-lock sa mga aplikasyon ng NFV. Kung kailangan ang mga lock, makakatulong ang mga lock bypass algorithm na mapabuti ang scalability.

Tungkol sa may-akda

Si Alexander Komarov ay nagtatrabaho bilang isang application development engineer sa Software and Services Group ng Intel Corporation. Sa nakalipas na 10 taon, ang pangunahing gawain ni Alexander ay ang pag-optimize ng code upang makamit ang pinakamataas na pagganap sa kasalukuyan at hinaharap na mga platform ng Intel server. Kasama sa gawaing ito ang paggamit ng mga tool sa pagbuo ng software ng Intel tulad ng mga profiler, compiler, library, pinakabagong set ng pagtuturo, nanoarchitecture, at mga pagpapahusay sa arkitektura sa pinakabagong mga x86 processor at chipset.

Higit pang impormasyon

Para sa karagdagang impormasyon tungkol sa NFV, tingnan ang mga sumusunod na video.

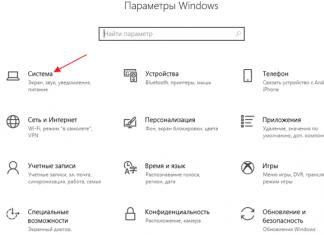

Sa bawat bagong henerasyon, ang mga processor ng Intel ay nagsasama ng higit pang mga teknolohiya at pag-andar. Ang ilan sa kanila ay kilalang-kilala (na, halimbawa, ay hindi alam ang tungkol sa hyperthreading?), Habang ang karamihan sa mga hindi-espesyalista ay hindi rin alam ang tungkol sa pagkakaroon ng iba. Buksan natin ito para sa lahat kilalang base kaalaman sa mga produkto ng Intel Automated Relational Knowledge Base (ARK) at pumili ng processor doon. Makakakita tayo ng napakaraming listahan ng mga feature at teknolohiya - ano ang nasa likod ng kanilang mahiwagang mga pangalan sa marketing? Iminumungkahi naming pag-aralan ang isyu, bigyang pansin ang kaunti mga kilalang teknolohiya- tiyak na magkakaroon ng maraming kawili-wiling bagay doon.

Intel Demand Based Switching

Kasama ng Enhanced Intel SpeedStep Technology, ang Intel Demand Based Switching technology ay responsable para sa pagtiyak na ang processor ay gumagana sa pinakamainam na dalas at nakatanggap ng sapat na kuryente: hindi hihigit at hindi bababa sa kinakailangan. Binabawasan nito ang pagkonsumo ng kuryente at pagkawala ng init, na mahalaga hindi lamang para sa mga portable na aparato, kundi pati na rin para sa mga server - dito ginagamit ang Demand Based Switching.

Intel Fast Memory Access

Memory controller function upang i-optimize ang pagganap ng RAM. Ito ay isang kumbinasyon ng mga teknolohiya na nagbibigay-daan, sa pamamagitan ng malalim na pagsusuri ng command queue, upang matukoy ang "nagpapatong" na mga utos (halimbawa, pagbabasa mula sa parehong pahina ng memorya), at pagkatapos ay muling ayusin ang aktwal na pagpapatupad upang ang "nagpapatong" na mga utos ay sunod sunod na pinaandar. Bilang karagdagan, ang mga utos sa pagsulat ng memory na may mababang priyoridad ay naka-iskedyul para sa mga oras na ang read queue ay hinulaang mawawalan ng laman, na ginagawang mas hindi mahigpit ang proseso ng pagsulat ng memorya sa bilis ng pagbasa.

Intel Flex Memory Access

Ang isa pang function ng memory controller, na lumitaw noong mga araw na ito ay isang hiwalay na chip, noong 2004. Nagbibigay ng kakayahang magtrabaho sa synchronous mode na may dalawang memory module sa parehong oras, at hindi tulad ng simpleng dual-channel mode na umiral noon, ang mga memory module ay maaaring may iba't ibang laki. Sa ganitong paraan, nakamit ang kakayahang umangkop sa pagbibigay ng memorya sa computer, na makikita sa pangalan.

Intel Instruction Replay

Isang napakalalim na teknolohiya na unang lumitaw sa mga processor ng Intel Itanium. Sa panahon ng pagpapatakbo ng mga pipeline ng processor, ang isang sitwasyon ay maaaring mangyari kapag ang mga tagubilin ay dumating na upang maisakatuparan, ngunit ang kinakailangang data ay hindi pa magagamit. Ang pagtuturo pagkatapos ay kailangang "i-replay": alisin mula sa conveyor at tumakbo sa simula nito. Na kung ano mismo ang nangyayari. Isa pa mahalagang tungkulin IRT – pagwawasto ng mga random na error sa mga pipeline ng processor. Magbasa nang higit pa tungkol dito kawili-wiling function basahin .

Intel My WiFi Technology

Teknolohiya ng virtualization na nagpapahintulot sa iyo na magdagdag ng isang virtual WiFi adapter sa isang umiiral na pisikal; kaya, ang iyong ultrabook o laptop ay maaaring maging ganap na access point o repeater. Ang aking mga bahagi ng software ng WiFi ay kasama sa bersyon ng driver ng Intel PROSet Wireless Software na 13.2 at mas bago; Dapat itong isipin na ang ilang mga adapter ng WiFi lamang ang katugma sa teknolohiya. Ang mga tagubilin sa pag-install, pati na rin ang isang listahan ng software at hardware compatibility, ay matatagpuan sa website ng Intel.

Intel Smart Idle Technology

Isa pang teknolohiya sa pag-save ng enerhiya. Binibigyang-daan kang huwag paganahin ang kasalukuyang hindi ginagamit na mga bloke ng processor o bawasan ang dalas ng mga ito. Isang kailangang-kailangan na bagay para sa isang smartphone CPU, na kung saan ay eksakto kung saan ito lumitaw - sa mga processor ng Intel Atom.

Intel Stable Image Platform

Isang termino na tumutukoy sa mga proseso ng negosyo kaysa sa teknolohiya. programa ng Intel Tinitiyak ng SIPP ang katatagan ng software sa pamamagitan ng pagtiyak na ang mga pangunahing bahagi ng platform at mga driver ay mananatiling hindi nagbabago nang hindi bababa sa 15 buwan. Kaya, may pagkakataon ang mga corporate na customer na gamitin ang parehong naka-deploy na mga imahe ng system sa panahong ito.

Intel QuickAssist

Isang set ng mga function na ipinatupad ng hardware na nangangailangan ng malaking halaga ng pag-compute, halimbawa, pag-encrypt, compression, pagkilala sa pattern. Ang punto ng QuickAssist ay upang gawing mas madali ang mga bagay para sa mga developer sa pamamagitan ng pagbibigay sa kanila ng mga functional na bloke ng gusali at pabilisin ang kanilang mga application. Sa kabilang banda, pinapayagan ka ng teknolohiya na ipagkatiwala ang "mabibigat" na mga gawain sa hindi ang pinakamakapangyarihang mga processor, na lalong mahalaga sa mga naka-embed na system na lubhang limitado sa parehong pagganap at paggamit ng kuryente.

Intel Quick Resume

Binuo ang teknolohiya para sa mga computer batay sa platform ng Intel Viiv, na nagpapahintulot sa kanila na i-on at i-off ang halos kaagad, tulad ng mga TV receiver o DVD player; sa parehong oras, sa "off" na estado, ang computer ay maaaring magpatuloy sa paggawa ng ilang mga gawain na hindi nangangailangan ng interbensyon ng user. At kahit na ang platform mismo ay maayos na lumipat sa iba pang mga anyo kasama ang mga pag-unlad na sinamahan nito, ang linya ay naroroon pa rin sa ARK, dahil hindi pa ito katagal.

Intel Secure Key

Isang generic na pangalan para sa 32- at 64-bit na RDRAND na mga tagubilin na gumagamit ng hardware na pagpapatupad ng Digital Random Number Generator (DRNG). Ang pagtuturo ay ginagamit para sa cryptographic na layunin upang makabuo ng maganda at mataas na kalidad na random key.

Intel TSX-NI

Ang teknolohiya na may kumplikadong pangalan na Intel Transactional Synchronization Extensions - Bagong Mga Tagubilin ay nagpapahiwatig ng isang add-on sa processor cache system na nag-o-optimize sa kapaligiran ng pagpapatupad ng mga multi-threaded na application, ngunit, siyempre, kung ang mga application na ito ay gumagamit lamang. mga interface ng software TSX-NI. Mula sa panig ng gumagamit, ang teknolohiyang ito ay hindi direktang nakikita, ngunit maaaring basahin ng sinuman ang paglalarawan nito sa naa-access na wika sa blog ni Stepan Koltsov.

Sa konklusyon, nais naming ipaalala sa iyo muli na ang Intel ARK ay umiiral hindi lamang bilang isang website, kundi pati na rin bilang isang offline na application para sa iOS at Android. Manatili sa paksa!

Ang arkitektura ba ni Haswell ay karapat-dapat na tawaging bago at muling idisenyo?

Higit sa lima taon Intel ay sumusunod sa isang diskarte na "tik-tok", na pinapalitan ang pagsasalin ng isang partikular na arkitektura sa mas banayad na mga teknolohikal na pamantayan sa paglabas ng isang bagong arkitektura.

Bilang resulta, bawat taon ay nakakatanggap kami ng alinman sa isang bagong arkitektura o isang paglipat sa isang bagong teknikal na proseso. Ang "So" ay binalak para sa 2013, iyon ay, ang pagpapalabas ng isang bagong arkitektura - Haswell. Ang mga processor na may bagong arkitektura ay ginawa gamit ang parehong teknolohiya ng proseso tulad ng nakaraang henerasyon ng Ivy Bridge: 22 nm, Tri-gate. Ang teknikal na proseso ay hindi nagbago, ngunit ang bilang ng mga transistor ay tumaas, na nangangahulugan na ang pangwakas na lugar ng kristal ng bagong processor ay tumaas din - at pagkatapos nito, ang pagkonsumo ng kuryente.

Ang pagsunod sa mga tradisyon, sa araw ng pag-anunsyo ng Haswell, ipinakita lamang ng Intel ang mga high-performance at mamahaling processor mula sa mga linya ng Core i5 at i7. Ang anunsyo ng mga dual-core na processor ng mas mababang linya ay, gaya ng dati, naantala. Kapansin-pansin na ang mga presyo para sa mga bagong processor ay nanatili sa parehong antas tulad ng sa Ivy Bridge.

Ihambing natin ang mga die area ng iba't ibang henerasyon ng quad-core processors:

Tulad ng nakikita mo, ang quad-core na Haswell ay may isang lugar na 177 mm² lamang, habang ang north bridge at controller ay isinama dito. RAM at graphics core. Kaya, ang bilang ng mga transistor ay tumaas ng 200 milyon, at ang lugar ay tumaas ng 17 mm². Kung ihahambing natin ang Haswell sa 32nm Sandy Bridge, pagkatapos ay tumaas ang bilang ng mga transistor ng 440 milyon (38%), at ang lugar dahil sa paglipat sa teknolohiyang proseso ng 22 nm ay bumaba ng 39 mm² (18%). Ang pagkawala ng init ay nanatiling halos parehong antas sa lahat ng mga taon na ito (95 W para sa SB at 84 W para sa Haswell), at ang lugar ay nabawasan.

Ang lahat ng ito ay humantong sa katotohanan na mas maraming init ang kailangang alisin sa bawat square millimeter ng kristal. Kung mas maaga mula sa 216 mm² kinakailangan na kumuha ng 95 W, iyon ay, 0.44 W/mm², ngayon mula sa isang lugar na 177 mm² kinakailangan na kumuha ng 84 W - 0.47 W/mm², na 6.8% na higit pa kaysa dati. . Kung magpapatuloy ang trend na ito, malapit na itong pisikal na mahirap alisin ang init mula sa mga maliliit na lugar.

Purong theoretically, maaari nating ipagpalagay na kung sa Broadwell, na gagawin gamit ang isang 14 nm na teknolohiya ng proseso, ang bilang ng mga transistor ay tataas ng 21%, tulad ng sa paglipat mula 32 hanggang 22 nm, at ang lugar ay mababawasan ng 26 % (sa parehong halaga tulad ng kapag lumilipat mula 32 hanggang 22 nm), nakakakuha kami ng 1.9 bilyong transistor sa isang lugar na 131 mm². Kung ang pagwawaldas ng init ay bumaba rin ng 19%, makakakuha tayo ng 68 W, o 0.52 W/mm².

Ito ay mga teoretikal na kalkulasyon, sa pagsasagawa ito ay magkakaiba - ang paglipat ng teknolohikal na proseso mula 32 hanggang 22 nm ay minarkahan din ng pagpapakilala ng mga 3D transistors, na nagbawas ng mga daloy ng pagtagas, at kasama nila ang pagbuo ng init. Gayunpaman, wala pang narinig na tulad nito tungkol sa paglipat mula 22 nm hanggang 14 nm, kaya sa pagsasagawa, ang mga halaga ng pagwawaldas ng init ay malamang na mas masahol pa, at hindi ka dapat umasa sa 0.52 W/mm². Gayunpaman, kahit na ang antas ng pagkawala ng init ay 0.52 W/mm², ang problema ng lokal na sobrang init at ang kahirapan sa pag-alis ng init mula sa isang maliit na kristal ay magiging mas malala.

Sa pamamagitan ng paraan, tiyak na ang mga paghihirap sa pagkawala ng init na may antas ng pagwawaldas ng init na 0.52 W/mm² ang maaaring sumasailalim sa pagnanais ng Intel na lumipat sa BGA o pagtatangka na alisin ang socket. Kung ang processor ay ibinebenta sa motherboard, pagkatapos ay direktang ililipat ang init mula sa chip patungo sa heatsink nang walang intermediate na takip. Ito ay mukhang mas may kaugnayan sa liwanag ng pagpapalit ng panghinang na may thermal paste sa ilalim ng mga pabalat ng mga modernong processor. Maaari nating asahan muli ang hitsura ng mga "hubad" na mga processor na may mga bukas na kristal na sumusunod sa halimbawa ng Athlon XP, ibig sabihin, walang takip bilang isang intermediate na link sa heat sink.

Ito ay ginawa sa mga video card sa loob ng mahabang panahon, at ang panganib ng pag-chip ng kristal ay pinapagaan ng bakal na frame sa paligid nito, kaya naman ang mga video card ay walang ganoong " kasalukuyang mga problema", tulad ng thermal paste sa ilalim ng takip ng processor. Gayunpaman, ang overclocking ay magiging mas mahirap, at ang wastong paglamig ng "thinner" processors ay magiging halos isang agham. At lahat ng ito ay naghihintay sa atin sa lalong madaling panahon, maliban kung, siyempre, isang himala ang mangyayari...

Ngunit bumaba tayo sa lupa at bumalik sa pag-uusap tungkol kay Haswell. Tulad ng alam natin, nakatanggap si Haswell ng ilang "mga pagpapabuti/pagbabago" na nauugnay sa Sandy Bridge (at, nang naaayon, Ivy Bridge, na, sa pangkalahatan, ay isang paglipat ng SB sa isang mas banayad na teknikal na proseso):

- built-in na regulator ng boltahe;

- bagong mga mode ng pag-save ng enerhiya;

- pagtaas ng dami ng mga buffer at pila;

- pagtaas ng kapasidad ng cache;

- pagtaas ng bilang ng mga launch port;

- pagdaragdag ng mga bagong block, function, API sa integrated graphics core;

- pagtaas ng bilang ng mga pipeline sa graphics core.

Kaya, ang pagsusuri ng bagong platform ay maaaring nahahati sa tatlong bahagi: processor, integrated graphics accelerator, chipset.

Bahagi ng processor

Kasama sa mga pagbabago sa processor ang pagdaragdag ng mga bagong tagubilin at bagong power saving mode, ang pagsasama ng isang voltage regulator, pati na rin ang mga pagbabago sa mismong processor core.

Mga Set ng Pagtuturo

Ang Haswell architecture ay may mga bagong set ng pagtuturo. Maaari silang hatiin sa dalawang malalaking grupo: ang mga naglalayong pataasin ang pagganap ng vector at ang mga naglalayong sa segment ng server. Kasama sa una ang AVX at FMA3, ang huli - virtualization at transactional memory.

Mga Advanced na Vector Extension 2 (AVX2)

Ang AVX suite ay pinalawak sa bersyong AVX 2.0. Ang AVX2 kit ay nagbibigay ng:

- suporta para sa 256-bit integer vectors (dati ay mayroon lamang suporta para sa 128-bit);

- suporta para sa pangangalap ng mga tagubilin, na nag-aalis ng pangangailangan para sa magkadikit na lokasyon ng data sa memorya; ngayon ang data ay "nakolekta" mula sa iba't ibang mga address ng memorya - magiging kawili-wiling makita kung paano ito nakakaapekto sa pagganap;

- pagdaragdag ng mga tagubilin para sa pagmamanipula/operasyon sa mga bit.

Sa pangkalahatan, bagong set ay mas nakatuon sa integer arithmetic, at ang pangunahing benepisyo mula sa AVX 2.0 ay makikita lamang sa mga integer na operasyon.

Fused Multiply-Add (FMA3)

Ang FMA ay isang pinagsamang multiply-add na operasyon kung saan ang dalawang numero ay pinarami at idinaragdag sa accumulator. Ang ganitong uri ng operasyon ay medyo karaniwan at nagbibigay-daan sa iyo upang mas mahusay na ipatupad ang pagpaparami ng mga vector at matrice. Ang suporta para sa extension na ito ay dapat na makabuluhang tumaas ang pagganap ng mga pagpapatakbo ng vector. Ang FMA3 ay suportado na sa Mga processor ng AMD kasama ang Piledriver core, at FMA4 sa Bulldozer.

Ang FMA ay isang kumbinasyon ng multiplication at addition operation: a=b×c+d.

Tulad ng para sa FMA3, ito ay tatlong-operand na mga tagubilin, iyon ay, ang resulta ay nakasulat sa isa sa tatlong operand na kalahok sa pagtuturo. Bilang resulta, nakakakuha tayo ng operasyon tulad ng a=b×c+a, a=a×b+c, a=b×a+c.

Ang FMA4 ay mga tagubiling may apat na operand na ang resulta ay nakasulat sa ikaapat na operand. Ang pagtuturo ay nasa anyong: a=b×c+d.

Sa pagsasalita tungkol sa FMA3: ang pagbabagong ito ay magtataas ng produktibidad ng higit sa 30% kung ang code ay iangkop sa FMA3. Kapansin-pansin na noong malayo pa si Haswell, pinaplano ng Intel na ipatupad ang FMA4 sa halip na FMA3, ngunit kalaunan ay binago ang desisyon nito pabor sa FMA3. Malamang, dahil dito lumabas ang Bulldozer na may suporta sa FMA4: sabi nila, wala silang oras upang i-convert ito sa Intel (ngunit lumabas si Piledriver kasama ang FMA3). Bukod dito, sa una ang Bulldozer noong 2007 ay binalak kasama ang FMA3, ngunit pagkatapos ipahayag ng Intel ang mga plano na ipatupad ang FMA4 noong 2008, binago ng AMD ang desisyon nito sa pamamagitan ng pagpapalabas ng Bulldozer sa FMA4. At binago ng Intel ang FMA4 sa FMA3 sa mga plano nito, dahil maliit ang pakinabang mula sa FMA4 kumpara sa FMA3, at ang komplikasyon ng electrical mga logic circuit- makabuluhan, na nagpapataas din ng badyet ng transistor.

Ang mga nadagdag mula sa AVX2 at FMA3 ay lilitaw pagkatapos na maiangkop ang software sa mga set ng pagtuturo na ito, kaya hindi mo dapat asahan ang anumang mga tagumpay sa pagganap "dito at ngayon." At dahil ang mga tagagawa ng software ay medyo hindi gumagalaw, ang "karagdagang" pagganap ay kailangang maghintay.

Memorya ng transaksyon

Ang ebolusyon ng microprocessors ay humantong sa isang pagtaas sa bilang ng mga thread - isang modernong desktop processor ay may walo o higit pa sa mga ito. Ang isang malaking bilang ng mga thread ay lumilikha ng pagtaas ng mga paghihirap kapag nagpapatupad ng multi-threaded memory access. Kinakailangang kontrolin ang kaugnayan ng mga variable sa RAM: kinakailangan upang harangan ang data para sa pagsulat sa isang napapanahong paraan para sa ilang mga thread, at payagan ang pagbabasa o pagbabago ng data para sa iba pang mga thread. Ito ay isang kumplikadong gawain, at upang panatilihing napapanahon ang data multi-threaded na mga programa Ang memorya ng transaksyon ay binuo. Ngunit hanggang ngayon, ito ay ipinatupad sa software, na nagbawas ng pagiging produktibo.

Ang Haswell ay may bagong Transactional Synchronization Extensions (TSX) - transactional memory, na idinisenyo upang mahusay na ipatupad ang mga multi-threaded na programa at pataasin ang kanilang pagiging maaasahan. Ang extension na ito ay nagbibigay-daan sa iyo na ipatupad ang transactional memory "sa hardware," sa gayon ay tumataas ang pangkalahatang pagganap.

Ano ang transactional memory? Ito ay isang memorya na nasa loob mismo ng isang mekanismo para sa pamamahala ng mga parallel na proseso upang magbigay ng access sa nakabahaging data. Ang extension ng TSX ay binubuo ng dalawang bahagi: Hardware Lock Elision (HLE) at Restricted Transaction Memory (RTM).

Ang bahagi ng RTM ay isang hanay ng mga tagubilin na magagamit ng isang programmer upang simulan, tapusin, at i-abort ang isang transaksyon. Ang HLE component ay nagpapakilala ng mga prefix na hindi pinapansin ng mga processor na walang suporta sa TSX. Ang mga prefix ay nagbibigay ng variable na pag-lock, na nagbibigay-daan sa iba pang mga proseso na gumamit (basahin) ang mga naka-lock na variable at isagawa ang kanilang code hanggang sa mangyari ang isang naka-lock na data write conflict.

Sa ngayon, lumitaw na ang mga application na gumagamit ng extension na ito.

Virtualization

Ang kahalagahan ng virtualization ay patuloy na lumalaki: lalong, maraming mga virtual server ang matatagpuan sa isang pisikal na server, at ang mga serbisyo sa cloud ay nagiging mas laganap. Samakatuwid, ang pagtaas ng bilis ng mga teknolohiya ng virtualization at virtualized na kapaligiran ay isang napaka-kagyat na gawain sa segment ng server. Naglalaman ang Haswell ng ilang mga pagpapahusay na partikular na naglalayong pataasin ang pagganap ng mga virtualized na kapaligiran. Ilista natin sila:

- mga pagpapabuti upang mabawasan ang oras na kinakailangan upang lumipat mula sa mga sistema ng panauhin patungo sa sistema ng host;

- nagdagdag ng access bits sa Extended Page Table (EPT);

- Ang oras ng pag-access ng TLB ay nabawasan;

- mga bagong tagubilin para sa pagtawag sa hypervisor nang hindi isinasagawa ang vmexit command;

Bilang resulta, ang oras ng paglipat sa pagitan ng mga virtualized na kapaligiran ay nabawasan sa mas mababa sa 500 na mga cycle ng processor. Dapat itong humantong sa isang pagbawas sa pangkalahatang overhead ng pagganap na nauugnay sa virtualization. At ang bagong Xeon E3-12xx-v3 ay malamang na mas mabilis sa klase ng mga gawaing ito kaysa sa Xeon E3-12xx-v2.

Built-in na regulator ng boltahe

Sa Haswell, ang boltahe regulator ay inilipat mula sa motherboard sa ilalim ng takip ng processor. Dati (Sandy Bridge), kailangang konektado ang processor iba't ibang mga boltahe para sa core ng graphics, para sa ahente ng system, para sa mga core ng processor, atbp. Ngayon isang boltahe lamang na Vccin 1.75 V ang ibinibigay sa processor sa pamamagitan ng socket, na ibinibigay sa built-in na regulator ng boltahe. Ang regulator ng boltahe ay binubuo ng 20 na mga cell, ang bawat cell ay lumilikha ng 16 na mga phase na may kabuuang kasalukuyang 25 A. Sa kabuuan, nakakakuha kami ng 320 na mga phase, na higit pa kaysa sa mga pinaka-sopistikadong motherboard. Ang diskarte na ito ay nagbibigay-daan hindi lamang upang gawing simple ang layout ng mga motherboards (at samakatuwid ay bawasan ang kanilang gastos), ngunit din upang mas tumpak na ayusin ang mga boltahe sa loob ng processor, na, naman, ay humahantong sa mas malaking pagtitipid ng enerhiya.

Ito ang isa sa mga pangunahing dahilan kung bakit hindi maaaring pisikal na magkatugma ang Haswell sa lumang socket ng LGA1155. Oo, maaari nating pag-usapan ang pagnanais ng Intel na kumita ng pera sa pamamagitan ng pagpapalabas ng isang bagong platform (bagong chipset) bawat taon at isang bagong socket bawat dalawang taon, ngunit sa kasong ito ay may mga layunin na dahilan para sa pagbabago ng socket: pisikal/electrical incompatibility.

Gayunpaman, lahat ay dumating sa isang presyo. Ang boltahe regulator ay isa pang kapansin-pansing pinagmumulan ng init sa bagong processor. At dahil ang Haswell ay ginawa gamit ang parehong teknolohiya ng proseso gaya ng hinalinhan nitong Ivy Bridge, dapat nating asahan na mas mainit ang processor.

Sa pangkalahatan, ang pagpapahusay na ito ay magiging mas kapaki-pakinabang sa mobile na segment: ang mas mabilis at mas tumpak na mga pagbabago sa boltahe ay magbabawas ng pagkonsumo ng kuryente, pati na rin ang mas epektibong kontrol sa dalas ng mga core ng processor. At tila, ito ay hindi isang walang laman na pahayag sa marketing, dahil ang Intel ay mag-aanunsyo ng mga mobile processor na may napakababang paggamit ng kuryente.

Mga bagong mode ng pagtitipid ng enerhiya

Ipinakilala ni Haswell ang mga bagong estado ng pagtulog ng S0ix, na katulad ng mga estado ng S3/S4, ngunit may mas maikling oras para lumipat ang processor sa estado ng pagtatrabaho. Ang isang bagong C7 idle state ay naidagdag din.

Ang Mode C7 ay sinamahan ng pag-off sa pangunahing bahagi ng processor, habang ang imahe sa screen ay nananatiling aktibo.

Ang minimum na idle frequency ng mga processor ay 800 MHz, na dapat ding bawasan ang pagkonsumo ng kuryente.

Arkitektura ng processor

Pangharap na dulo

Ang Haswell pipeline, tulad ng sa SB, ay may 14–19 na yugto: 14 na yugto para sa isang µop cache hit, 19 para sa isang miss. Ang laki ng µop cache ay hindi nagbago kumpara sa SB - 1536 µop. Ang organisasyon ng uop cache ay nanatiling pareho sa SB - 32 set ng walong linya, bawat isa ay may anim na uops. Bagaman, dahil sa pagtaas ng bilang ng mga execution device, pati na rin ang mga kasunod na buffer pagkatapos ng uop cache, maaaring asahan ng isa ang pagtaas sa uop cache - hanggang sa 1776 uops (bakit eksakto ang volume na ito ay tatalakayin sa ibaba).

Decoder

Ang decoder, maaaring sabihin ng isa, ay hindi nagbago - nananatili itong four-way, tulad ng SB. Binubuo ito ng apat na magkatulad na channel: isang kumplikadong tagasalin (complex decoder) at tatlong simple (simpleng decoder). Ang isang kumplikadong tagasalin ay maaaring magproseso/mag-decode ng mga kumplikadong tagubilin na bumubuo ng higit sa isang uop. Ang natitirang tatlong channel ay nagde-decode ng mga simpleng tagubilin. Sa pamamagitan ng paraan, dahil sa pagkakaroon ng pagsasama ng mga macro-operasyon, ang paglo-load na may mga tagubilin sa pagpapatupad at pagbabawas ay bumubuo, halimbawa, isang uop at maaaring ma-decode sa "simpleng" mga channel ng decoder. Mga tagubilin sa SSE bumuo din ng isang uop, para ma-decode ang mga ito sa alinman sa tatlong simpleng channel. Dahil sa pagdating ng 256-bit AVX, FMA3, pati na rin ang tumaas na bilang ng mga trigger port at function na device, maaaring hindi sapat ang bilis ng decoder na ito - at maaari itong maging bottleneck. Bahagyang, ang bottleneck na ito ay "pinalawak" ng L0m uop cache, ngunit gayon pa man, sa pagkakaroon ng isang processor na may 8 launch port, dapat isipin ng Intel ang pagpapalawak ng decoder - lalo na, hindi masasaktan ang pagtaas ng bilang ng mga kumplikadong channel.

Scheduler, reordering buffer, execution units

Pagkatapos ng decoder ay darating ang isang pila ng mga na-decode na tagubilin, at dito natin makikita ang unang pagbabago. Ang SB ay may dalawang pila ng 28 entry - isang pila sa bawat virtual na Hyper-Threading (HT) na thread. Sa Haswell, ang dalawang pila ay pinagsama sa isang karaniwan para sa dalawang HT na mga thread na may 56 na mga entry, iyon ay, ang dami ng pila ay hindi nagbago, ngunit ang konsepto ay nagbago. Ngayon ang buong dami ng 56 na mga tala ay magagamit sa isang thread sa kawalan ng isang segundo - samakatuwid, maaari naming asahan ang isang pagtaas sa parehong mga low-threaded na application at mga multi-threaded (ito ay dahil sa ang katunayan na ang dalawang mga thread ay maaaring gumamit ng isang solong pila nang mas mahusay).

Ang reordering buffer ay binago din - ito ay nadagdagan mula 168 hanggang 192 na mga entry. Ito ay dapat na mapabuti ang kahusayan ng HT dahil sa mas malaking posibilidad na magkaroon ng mga uops na "independyente" sa isa't isa. Ang decoded micro-op queue ay nadagdagan mula 54 hanggang 60. Ang mga pisikal na register file na lumabas sa SB ay nadagdagan din - mula 160 hanggang 168 registers para sa integer operand at mula 144 hanggang 168 para sa floating point operand, na dapat ay may positibong epekto sa pagganap ng mga kalkulasyon ng vector.

Ibuod natin ang lahat ng data sa mga pagbabago sa mga buffer at queue sa isang talahanayan.

Sa prinsipyo, ang mga pagbabago sa mga parameter sa Haswell ay mukhang lubos na inaasahan, na ibinigay sa pangkalahatang lohika ng pag-unlad ng Intel processor architecture. Batay sa parehong lohika, maaari nating ipagpalagay na sa mga sumusunod Generation Core ang mga laki ng buffer at queues ay tataas ng hindi hihigit sa 14%, iyon ay, ang laki ng reordering buffer ay magiging sa paligid ng 218. Ngunit ang mga ito ay puro theoretical assumptions.

Kasunod ng pila ng mga na-decode na operasyon ay ang mga trigger port at ang mga port na naka-attach sa kanila. mga functional na aparato. Sa yugtong ito ay tatalakayin natin nang mas detalyado.

Tulad ng alam natin, may anim na launch port ang Sandy Bridge, na minana nito mula sa Nehalem, na mula naman kay Conroe. Iyon ay, mula noong 2006, nang ang Intel ay nagdagdag ng dalawa pang port sa apat na magagamit sa Pentium 4, ang bilang ng mga launch port ay hindi nagbago - ang mga bagong functional na aparato lamang ang naidagdag. Gayunpaman, ito ay nagkakahalaga ng pagbanggit na ang P4 ay may isang uri ng orihinal na arkitektura ng NetBurst, kung saan ang dalawang port nito ay maaaring magsagawa ng dalawang operasyon sa isang ikot ng orasan (bagaman hindi sa lahat ng mga operasyon). Ngunit ito ay magiging pinaka-tama upang subaybayan ang ebolusyon ng bilang ng mga launch port na hindi gumagamit ng halimbawa ng P4, ngunit gamit ang halimbawa ng PIII, dahil ang P4 ay may mahabang pipeline, at ilunsad ang mga port na may "double" na pagganap, at isang trace cache , at ang buong arkitektura nito ay kapansin-pansing naiiba sa karaniwang tinatanggap. At ang Pentium III ay napakalapit sa mga tuntunin ng functional scheme ng mga launch port sa Conroe, at mayroon ding isang maikling lalagyan. Kaya, sa pangkalahatan, masasabi nating si Conroe ang direktang kahalili ng PIII. Batay dito, masasabing noong 2006, isang launch port lamang ang nadagdag kumpara sa PIII, na mayroong limang launch port.

Kaya, ang bilang ng mga launch port ay medyo mabagal na lumalaki, at kung ang mga bago ay idinagdag, pagkatapos ay isa-isa. Nagdagdag si Haswell ng dalawa nang sabay-sabay, na nagbibigay ng kabuuang walong port - kaunti pa, at makakarating na tayo sa Itanium. Alinsunod dito, ang Haswell ay nagpapakita ng isang teoretikal na pagganap sa landas ng pagpapatupad ng 8 UOPs/cycle, kung saan 4 na UOP ang ginugugol sa mga pagpapatakbo ng aritmetika, at ang natitirang 4 ay sa mga pagpapatakbo ng memorya. Alalahanin na ang Conroe/Nehalem/SB ay nagkaroon ng 6 uops/cycle: 3 uops para sa mga operasyon ng arithmetic at 3 uops para sa memory operations. Ang pagpapahusay na ito ay dapat na itaas ang marka ng IPC, at sa gayon ay may mga napakaseryosong pagbabago sa arkitektura ng Haswell na ganap na nagbibigay-katwiran sa lugar nito bilang "ganun" sa plano ng pagpapaunlad ng Intel.

Mga pagbabago sa FU sa Haswell

Ang bilang ng mga actuator ay nadagdagan din. Ang bagong ikaanim (ikapitong) port ay nagdagdag ng dalawang karagdagang actuator - isang integer arithmetic at shift device at isang branch prediction device. Ang ikapitong (ika-walong) port ay may pananagutan sa pag-unload ng address.

Kaya, nakakakuha kami ng apat na integer arithmetic execution unit, samantalang ang Sandy Bridge ay nagbigay sa amin ng tatlo lamang. Samakatuwid, maaari nating asahan ang pagtaas sa bilis ng integer arithmetic. Bilang karagdagan, sa teorya, ito ay dapat magbigay-daan sa amin upang maisagawa ang parehong lumulutang na punto at mga kalkulasyon ng integer nang sabay-sabay, na, sa turn, ay maaaring mapataas ang kahusayan ng NT. Sa SB, ang mga kalkulasyon ng floating point ay isinagawa sa parehong mga port kung saan ginamit ang mga integer function na device, kaya naganap ang malaking pagharang, ibig sabihin, hindi ka maaaring magkaroon ng "heterogeneous" load. Dapat ding tandaan na ang pagdaragdag karagdagang device gagawing posible ng paglipat sa Haswell na mahulaan ang paglipat nang walang "pag-block" sa panahon ng mga kalkulasyon ng aritmetika - dati, sa panahon ng mga kalkulasyon ng integer, ang tanging tagahula ng sangay ay na-block, ibig sabihin, posible na patakbuhin ang alinman sa arithmetic execution unit o ang predictor. Ang mga port 0 at 1 ay sumailalim din sa mga pagbabago - sinusuportahan na nila ngayon ang FMA3. Ipinakilala ng Intel ang ikapitong (ikawalo) port upang mapataas ang kahusayan at alisin ang "pagharang" - kapag ang pangalawa at pangatlong port ay gumagana para sa pag-download, ang ikapitong (ikawalo) port ay maaaring makisali sa pag-upload, na imposible lamang noon. Ang solusyon na ito ay kinakailangan upang matiyak ang mataas na bilis ng pagpapatupad ng AVX/FMA3 code.

Sa pangkalahatan, ang ganitong malawak na executive path ay maaaring humantong sa isang pagbabago sa HT - ginagawa itong four-threaded. Sa mga coprocessors Intel Xeon Ang Phi na may mas makitid na landas sa pagpapatupad ng HT ay may apat na sinulid, at, tulad ng ipinapakita ng mga pag-aaral at pagsubok, ang coprocessor ay kumikilos nang maayos. Iyon ay, kahit na ang isang mas makitid na landas ng pagpapatupad, sa prinsipyo, ay nagbibigay-daan sa iyo upang gumana nang epektibo sa apat na mga thread. At ang isang landas na may walong launch port ay maaaring maging mahusay na magpatakbo ng apat na mga thread, at higit pa rito, ang pagkakaroon ng apat na mga thread ay maaaring mas mahusay na mag-load ng walong launch port. Totoo, para sa higit na kahusayan Kakailanganin na dagdagan ang mga buffer (pangunahin ang reordering buffer) para sa mas malaking posibilidad ng "independiyenteng" data.

Dinoble din ni Haswell ang throughput ng L1-L2, habang pinapanatili ang parehong mga halaga ng latency. Ang panukalang ito ay kailangan lang, dahil ang 32-byte na pagsulat at 16-byte na pagbabasa ay hindi magiging sapat dahil sa pagkakaroon ng walong launch port, pati na rin ang 256-bit AVX at FMA3.

| Sandy Bridge | Haswell | |

| L1i | 32k, 8-way | 32k, 8-way |

| L1d | 32k, 8-way | 32k, 8-way |

| Latency | 4 na hakbang | 4 na hakbang |

| Bilis ng pag-download | 32 byte/orasan | 64 byte/orasan |

| Bilis ng pagsulat | 16 byte/cycle | 32 byte/orasan |

| L2 | 256k, 8-way | 256k, 8-way |

| Latency | 11 bar | 11 bar |

| Bandwidth sa pagitan ng L2 at L1 | 32 byte/orasan | 64 byte/orasan |

| L1i TLB | 4k: 128, 4-way 2M/4M: 8/thread | 4k: 128, 4-way 2M/4M: 8/thread |

| L1d TLB | 4k: 128, 4-way 2M/4M: 7/thread 1G: 4, 4-way | 4k: 128, 4-way 2M/4M: 7/thread 1G: 4, 4-way |

| L2 TLB | 4k: 512, 4-way | 4k+2M ibinahagi: 1024, 8-way |

Nadagdagan ang TLB L2 sa 1024 na mga entry, at lumitaw ang suporta para sa dalawang-megabyte na pahina. Ang pagtaas sa TLB L2 ay nangangailangan din ng pagtaas ng pagkakaugnay mula apat hanggang walo.

Tulad ng para sa ikatlong antas ng cache, ang sitwasyon kasama nito ay hindi maliwanag: sa bagong processor, ang latency ng pag-access ay dapat tumaas dahil sa mga pagkalugi sa pag-synchronize, dahil ngayon ang L3 cache ay gumagana sa natural na dalas, at hindi sa dalas ng mga core ng processor, gaya ng dati. Bagama't ang pag-access ay ginagawa pa rin sa 32 bytes bawat ikot ng orasan. Sa kabilang banda, pinag-uusapan ng Intel ang tungkol sa mga pagbabago sa System Agent at mga pagpapahusay sa block ng Load Balancer, na maaari na ngayong magproseso ng maramihang mga kahilingan sa cache ng L3 nang magkatulad at paghiwalayin ang mga ito sa mga kahilingan sa data at hindi data. Ito ay dapat tumaas ang throughput ng L3 cache (ang ilang mga pagsubok ay nagpapatunay nito, ang L3 cache bandwidth ay bahagyang mas mataas kaysa sa IB).

Ang prinsipyo ng pagpapatakbo ng L3 cache sa Haswell ay medyo katulad sa Nehalem. Sa Nehalem, ang L3 cache ay matatagpuan sa Uncore at may sariling nakapirming dalas, habang sa SB ang L3 cache ay nakatali sa mga core ng processor - ang dalas nito ay naging katumbas ng dalas ng mga core ng processor. Dahil dito, lumitaw ang mga problema - halimbawa, kapag ang mga core ng processor ay gumana sa pinababang mga frequency kapag walang load (at ang LLC ay "nakatulog"), at ang GPU ay nangangailangan ng isang mataas na LLC PS. Ibig sabihin, limitado ang desisyong ito Pagganap ng GPU, at bukod pa, kinailangan na ilabas ang mga core ng processor sa idle state para lang magising ang LLC. Bagong processor upang mapabuti ang pagkonsumo ng kuryente at kahusayan Pagpapatakbo ng GPU sa mga sitwasyon sa itaas, ang L3 cache ay gumagana sa sarili nitong dalas. Ang mga solusyon sa mobile kaysa sa desktop ang dapat na makinabang nang husto mula sa solusyon na ito.

Ito ay nagkakahalaga na tandaan na ang mga laki ng cache ay may isang tiyak na pag-asa. Ang ikatlong antas ng cache ay dalawang megabytes bawat core, ang pangalawang antas ng cache ay 256 KB, na walong beses na mas mababa kaysa sa L3 volume bawat core. Ang dami ng unang antas ng cache, sa turn, ay walong beses na mas maliit kaysa sa L2 at 32 KB. Ang uop cache ay ganap na akma sa dependence na ito: ang dami nito na 1536 uops ay 7-9 beses na mas maliit kaysa sa L1 (imposibleng matukoy ito nang tumpak, dahil ang bit size ng isang uop ay hindi alam, at ang Intel ay malamang na hindi palawakin ang paksang ito. ). Sa turn, ang reordering buffer ng 168 uops ay eksaktong walong beses na mas maliit kaysa sa uop cache ng 1536 uops, bagaman, batay sa malawakang pagtaas ng mga buffer at queues, inaasahan ng isa ang pagtaas sa uop cache ng 14%, iyon ay, hanggang 1776. Kaya, ang mga volume ng buffer at cache ay may proporsyonal na laki. Marahil ito ay isa pang dahilan kung bakit hindi pinapataas ng Intel ang mga L1/L2 na cache, kung isasaalang-alang ang mga proporsyon sa mga volume na pinakamabisa sa mga tuntunin ng pagtaas ng pagganap sa bawat pagtaas ng lugar. Kapansin-pansin na ang mga processor na may built-in na top-end na graphics core ay may intermediate fast memory na may malawak na access bus, na nag-cache ng lahat ng kahilingan sa RAM - parehong processor at ang video accelerator. Ang dami ng memorya na ito ay 128 MB. Para sa mga core ng processor, kung ituturing natin ang memorya na ito bilang L4 cache, ang volume ay dapat na 64 megabytes, at sa pagdaragdag ng isang graphics core, ang paggamit ng 128 MB ay mukhang lohikal.

Tulad ng para sa memory controller, hindi ito nakatanggap ng pagtaas sa bilang ng mga channel o pagtaas sa dalas ng operasyon ng RAM, iyon ay, ito ay pareho pa rin ng memory controller na may dual-channel na pag-access sa dalas ng 1600 MHz. Ang desisyong ito ay mukhang medyo kakaiba, dahil ang paglipat mula sa SB hanggang IB ay nadagdagan ang dalas ng pagpapatakbo ng ICP mula 1333 MHz hanggang 1600 MHz, kahit na ito ay isang paglipat lamang ng arkitektura sa isang bagong teknikal na proseso. At ngayon mayroon kaming bagong arkitektura, habang ang dalas ng pagpapatakbo ng memorya ay nananatiling nasa parehong antas.

Mukhang mas kakaiba ito kung naaalala natin ang mga pagpapahusay sa graphics core - pagkatapos ng lahat, naaalala natin na kahit na ang low-end na HD2500 video card sa IB ay ganap na nagamit ang 25 GB/s bandwidth. Ngayon ang parehong pagganap ng CPU at pagganap ng graphics ay tumaas, habang ang bandwidth ng memorya ay nanatili sa parehong antas. Sa mas malawak na sukat, patuloy na pinapataas ng kakumpitensya ang memory bandwidth sa mga APU nito, at mas mataas ito kaysa sa Intel. Makatuwirang asahan na suportahan ni Haswell ang memorya na may dalas na 1866 MHz o 2133 MHz, na magpapataas ng bandwidth sa 30 at 34 GB/s, ayon sa pagkakabanggit.

Bilang resulta, ito Intel solusyon hindi lubos na malinaw. Una, ipinakilala ng kakumpitensya ang suporta para sa mas mabilis na memorya nang walang anumang mga problema. Pangalawa, ang halaga ng mga module ng memorya na tumatakbo sa dalas ng 1866 MHz ay hindi mas mataas kumpara sa 1600 MHz na mga module, at bukod pa, walang sinuman ang obligadong bumili ng 1866 MHz na memorya - ang pagpipilian ay nakasalalay sa gumagamit. Pangatlo, hindi maaaring magkaroon ng anumang mga problema sa suporta para sa hindi lamang 1866 MHz, kundi pati na rin sa 2133 MHz: mula nang ipahayag ang Haswell, ang mga talaan ng mundo para sa overclocking RAM ay naitakda, iyon ay, ang ICP ay maaaring makayanan ang higit pa kaysa doon nang wala. anumang problema mabilis na memorya. Pang-apat, ang linya ng server ng Xeon E5-2500 V2 (Ivy Bridge-EP) ay nag-aangkin ng suporta para sa 1866 MHz, ngunit ang Intel ay karaniwang nagpapakilala ng suporta para sa mas mabilis na mga pamantayan ng memorya sa merkado na ito nang mas huli kaysa sa mga solusyon sa desktop.

Sa prinsipyo, maaaring ipagpalagay ng isang tao na sa kawalan ng kumpetisyon, ang Intel ay hindi kailangang "ganun lang" na bumuo ng mga kalamnan nito at higit pang dagdagan ang higit na kahusayan nito, ngunit ang palagay na ito ay ganap na hindi tama, dahil ang pagtaas ng bandwidth ng memorya, bilang panuntunan, ay tumataas. ang pagganap ng pinagsamang graphics core at halos hindi nagpapataas ng pagganap ng processor. Kasabay nito, ang Intel ay nahuhuli pa rin sa AMD sa pagganap ng graphics, at sa mga nagdaang taon, ang Intel mismo ay nagbabayad ng higit at higit na pansin sa mga graphics, at ang rate ng pagpapabuti para dito ay mas mataas kaysa sa para sa core ng processor. Bilang karagdagan, kung umaasa tayo sa mga resulta ng pagsubok sa pinagsama-samang graphics core ng nakaraang henerasyon na HD4000, na nagpakita na ang pagtaas sa memory bandwidth ay humahantong sa pagtaas ng pagganap ng graphics nang hanggang 30%, at isinasaalang-alang din na ang bagong Ang graphics core HD4600 ay kapansin-pansing mas mabilis kaysa sa HD4000, kung gayon ang pagtitiwala sa pagganap ng graphics core mula sa PSP ay nagiging mas halata. Ang bagong graphics core ay mas mapipigilan ng "makitid" na memory bandwidth. Ang pagbubuod ng lahat ng mga katotohanan, ang desisyon ng Intel ay ganap na hindi maintindihan: ang kumpanya mismo ay "sinakal" ang mga graphics nito, ngunit ang pagtaas ng bandwidth ay maaaring mapabuti ang pagganap nito.

Pagbabalik sa arkitektura ng mga cache, itapon na lang natin ang isang pag-iisip sa walang bisa: dahil naidagdag ang isang intermediate cache (mop cache), kung gayon bakit hindi magdagdag ng isang intermediate data cache na halos 4-8 KB ang laki at may mas mababang pag-access latency sa pagitan ng L1d cache at executive device, tulad ng mula sa P4 (dahil ang konsepto ng uop cache ay kinuha mula sa Netburst)? Alalahanin na sa P4 ang intermediate data cache na ito ay may access time na dalawang clock cycle, at ang isang P4 cycle ay katumbas ng humigit-kumulang 0.75 clock cycle ng isang conventional processor, iyon ay, ang access time ay humigit-kumulang isa at kalahating clock cycle. Gayunpaman, marahil ay makikita natin muli ang isang bagay na katulad - Gustung-gusto ng Intel na alalahanin ang mga nakalimutang lumang bagay.

Tulad ng nakikita mo, karamihan sa arkitektura Mga pagbabago sa Intel naglalayong pataasin ang performance ng AVX/FMA3 code: kasama dito ang pagtaas ng cache throughput, pagtaas ng bilang ng mga port, at pagtaas ng upload/download rate sa execution path. Bilang resulta, ang pangunahing pakinabang ng pagganap ay dapat magmula sa software na nakasulat gamit ang AVX/FMA3. Sa prinsipyo, sa paghusga sa mga resulta ng pagsubok, tila ito ang kaso. Ang dry performance sa parehong dalas sa mga "lumang" application ay tumanggap ng pagtaas ng humigit-kumulang 10% kumpara sa nakaraang core, at ang mga application na nakasulat gamit ang mga bagong set ng pagtuturo ay nagpapakita ng pagtaas ng higit sa 30%. Kaya't ang mga benepisyo ng arkitektura ng Haswell ay ipapakita habang ang mga aplikasyon ay na-optimize para sa mga bagong set ng pagtuturo. Doon magiging halata ang superiority ni Haswell sa SB.

Ang pangunahing benepisyo mula sa isang makabuluhang bahagi ng mga pagbabago ay ang mga mobile device. Sila ay tutulungan at bagong diskarte sa L3 cache, at isang built-in na regulator ng boltahe, at mga bagong mode ng pagtulog, at mas mababang mga minimum na operating frequency ng mga core ng processor.

Konklusyon (bahagi ng processor)

Ano ang maaari mong asahan mula kay Haswell?

Dahil sa pagtaas ng bilang ng mga launch port, maaari mong asahan ang pagtaas ng IPC, kaya kaunting kalamangan ang bagong arkitektura ng Haswell sa ibabaw ng Sandy Bridge ay magkakaroon ng parehong dalas ngayon, kahit na may hindi na-optimize na software. Ang mga tagubilin sa AVX2/FMA3 ay ang pundasyon para sa hinaharap, at ang hinaharap na iyon ay nakasalalay sa mga developer ng software: kung mas mabilis nilang iangkop ang kanilang mga application, mas mabilis na makikita ng end user ang mga tagumpay sa pagganap. Gayunpaman, hindi mo dapat asahan ang paglago sa lahat at saanman: Ang mga tagubilin ng SIMD ay pangunahing ginagamit sa pagtatrabaho sa data ng multimedia at sa mga kalkulasyong pang-agham, kaya dapat asahan ang paglago ng pagganap sa mga gawaing ito. Ang pangunahing benepisyo mula sa pagtaas ng kahusayan sa enerhiya ay nasa mga mobile system, kung saan ang isyung ito ay talagang mahalaga. Kaya, ang dalawang pangunahing direksyon kung saan ang bagong arkitektura Intel Haswell Ang makabuluhang benepisyo ay isang pagtaas sa pagganap ng SIMD at isang pagtaas sa kahusayan sa enerhiya.

Tungkol sa kakayahang magamit ng mga bagong processor ng Haswell, sulit na suriin ang ilan iba't ibang mga pagpipilian kanilang mga aplikasyon: sa mga desktop computer, sa mga server, sa mga mobile na solusyon, para sa mga manlalaro, para sa mga overclocker.

Desktop

Ang pagkonsumo ng kuryente ay hindi isang pangunahing aspeto para sa isang desktop processor, kaya kahit na sa Europa na may mahal na kuryente, hindi malamang na sinuman ang lumipat sa Haswell mula sa mga nakaraang henerasyon dahil lamang dito. Bukod dito, ang TDP ng Haswell ay mas mataas kaysa sa IB, kaya ang matitipid ay magiging lamang sa kaso ng kaunting load. Kapag ang tanong ay iniharap sa ganitong paraan, walang pag-aalinlangan - hindi ito katumbas ng halaga.

Mula sa isang punto ng pagganap, ang paglipat ay hindi rin mukhang tulad ng isang kumikitang deal: ang maximum na pagtaas ng bilis sa mga gawain ng processor ay hindi na hihigit sa 10%. Ang paglipat sa Haswell mula sa Sandy Bridge o Ivy Bridge ay mabibigyang katwiran lamang kung plano mong gumamit ng mga application na may karampatang suporta para sa FMA3 at AVX2: Ang suporta ng FMA3 ay maaaring magbigay ng pagtaas sa ilang mga aplikasyon mula 30% hanggang 70%. Ang mga pagpapahusay na nauugnay sa virtualization at ang pagpapatupad ng transactional memory ay hindi gaanong interes at gamit para sa desktop.

Mga server at workstation

Isinasaalang-alang na ang mga server ay patuloy na nagpapatakbo ng 24 na oras sa isang araw at may medyo mataas na pare-parehong pagkarga sa processor, malamang na hindi mas mahusay si Haswell kaysa sa IB sa mga tuntunin ng purong pagkonsumo ng kuryente, bagama't maaari itong magbigay ng ilang pakinabang sa mga tuntunin ng pagganap sa bawat watt. Ang suporta sa AVX2/FMA3 ay malamang na hindi kapaki-pakinabang sa mga server, ngunit sa mga workstation na kasangkot sa mga siyentipikong kalkulasyon, ang suportang ito ay magiging napaka-kapaki-pakinabang - ngunit kung ang mga bagong tagubilin ay suportado sa software na ginamit. Ang memorya ng transaksyon ay isang kapaki-pakinabang na bagay, ngunit hindi rin palaging: maaari itong magbigay ng pagtaas sa mga multi-threaded na programa at sa mga programa na gumagana sa mga database, ngunit para sa epektibong paggamit kailangan din ang pag-optimize ng software.

Ngunit ang lahat ng mga pagpapahusay na nauugnay sa virtualization ay malamang na magkaroon ng magandang epekto, dahil ang mga virtual na kapaligiran ay ginagamit na ngayon nang napakaaktibo, at karamihan sa mga pisikal na server ay may ilang mga virtual. Bukod dito, ang pagkalat ng virtualization ay ipinaliwanag hindi lamang sa pamamagitan ng isang kapansin-pansing pagbawas sa mga gastos ng virtual na kapaligiran sa mga tuntunin ng pagganap, kundi pati na rin kahusayan sa ekonomiya: Ang naglalaman ng maraming virtual server sa isang pisikal na server ay mas mura at nagbibigay-daan sa mas mahusay na paggamit ng mga mapagkukunan, kabilang ang mga mapagkukunan ng processor.

So on merkado ng server Ang hitsura ni Haswell ay dapat na batiin nang positibo. Pagkatapos baguhin ang mga server batay sa Xeon E3-1200v1 at Xeon E3-1200v2 sa mga server na may Xeon E3-1200v3 (Haswell), agad kang makakatanggap ng pagtaas ng kahusayan, at pagkatapos na i-optimize ang software para sa AVX2/FMA3 at transactional memory, tataas ang performance. higit pa.

Mga solusyon sa mobile

Ang pangunahing benepisyo mula sa pagpapakilala ng Haswell sa mobile na segment, siyempre, ay nakasalalay sa lugar ng pinahusay na pagkonsumo ng kuryente. Sa paghusga sa pamamagitan ng mga presentasyon ng Intel, pati na rin ang mga resulta ng pagsubok na lumalabas na sa Internet, mayroon talagang isang epekto, at isang kapansin-pansin.

Sa mga tuntunin ng dalisay na pagganap, ang paglipat mula sa Ivy Bridge patungo sa Haswell ay tila hindi isang makatwirang gawain: ang netong kita ay dapat na medyo maliit, at ang mga pagpapabuti sa mga indibidwal na sangkap(ang parehong virtualization o multimedia na mga tagubilin) ay malamang na hindi makapagbigay ng malaki sa gumagamit ng isang mobile system, dahil bihira silang lumikha ng mga kapaligiran o kumplikadong pang-agham na kalkulasyon sa mga laptop at tablet.

Sa pangkalahatan, sa mga tuntunin ng pagganap ng processor, hindi ka dapat umasa ng marami, ngunit tiyak na hihilingin ng mga mobile system ang pagtaas sa pagganap ng graphics core. Samakatuwid, kung ang mga isyu sa pagkonsumo ng enerhiya ay hindi kritikal para sa iyo, hindi mo dapat sineseryoso na isaalang-alang ang pag-upgrade mula sa Sandy Bridge o Ivy Bridge - mas mahusay na ipagpatuloy ang pagpapatakbo ng mga umiiral na system hanggang sa sila ay maging ganap na hindi na ginagamit. Kung madalas kang nagtatrabaho sa mga baterya, ang Haswell ay maaaring magbigay ng isang makabuluhang pagtaas sa buhay ng baterya.

Mga manlalaro

Ang isyu ng pagkonsumo ng enerhiya sa mga manlalaro sa Russia, bilang panuntunan, ay hindi isang isyu - at bakit ito dapat kapag ang mga gaming video card ay kumonsumo ng 200 watts o higit pa? Hindi rin kailangan ng mga manlalaro ng virtualization at transactional memory. Ito ay hindi isang katotohanan na ang AVX2/FMA3 ay partikular na hihilingin para sa mga laro, bagama't maaaring maging kapaki-pakinabang ang mga ito sa mga kalkulasyon ng pisika. Ang nananatili ay ang dalisay na pagganap ng processor, at narito ang pagkakaiba sa parehong Ivy Bridge ay maliit. Bilang resulta, para sa kategoryang ito ng mga user ang direktang paglipat mula sa SB o IB patungong Haswell ay tila hindi rin nauugnay. Ngunit makatuwirang lumipat sa mga bagong processor mula sa Nehalem at Lynifield, at higit pa sa Conroe.

Mga overclocker

Para sa mga overclocker bagong processor(ngunit, siyempre, ang "naka-unlock" na K-bersyon lamang nito) ay maaaring maging kawili-wili, lalo na kung pinamamahalaan mo itong "i-scalp", iyon ay, alisin ang takip ng metal at direktang palamigin ang kristal. Kung hindi ito nagawa, ang mga resulta ng overclocking ay mukhang mas katamtaman kaysa sa Ivy Bridge. Dagdag pa, ang pinagsama-samang regulator ng boltahe ay maaaring maging isang limitasyon na kadahilanan. Magbasa pa tungkol dito

#XeonMadalas kapag pumipili ng single-processor server o workstation Ang tanong ay lumitaw kung aling processor ang gagamitin - isang server Xeon o isang regular na Core ix. Isinasaalang-alang na ang mga processor na ito ay binuo sa parehong mga core, ang pagpipilian ay madalas na nahuhulog sa mga desktop processor, na karaniwang may mas mababang gastos na may katulad na pagganap. Bakit ang Intel ay naglalabas ng mga processor ng Xeon E3? Alamin natin ito.

Mga pagtutukoy

Upang magsimula, kunin natin ang low-end na modelo ng Xeon processor mula sa kasalukuyang hanay ng modelo- Xeon E3-1220 V3. Ang magiging kalaban Core processor i5-4440. Ang parehong mga processor ay nakabatay sa Haswell core, may parehong base clock speed at katulad na mga presyo. Ang mga pagkakaiba sa pagitan ng dalawang processor na ito ay ipinakita sa talahanayan:Availability ng integrated graphics. Sa unang sulyap, ang Core i5 ay may kalamangan, ngunit ang lahat ng mga motherboard ng server ay may pinagsamang graphics card, na hindi kinakailangan. graphics chip sa processor, at ang mga workstation ay karaniwang hindi gumagamit ng pinagsamang mga graphics dahil sa kanilang medyo mababang pagganap.

Suporta sa ECC. Ang mataas na bilis at malaking halaga ng RAM ay nagpapataas ng posibilidad ng mga error sa software. Karaniwan, ang mga naturang error ay hindi nakikita, ngunit sa kabila nito, maaari silang humantong sa mga pagbabago sa data o pag-crash ng system. Kung para sa mga desktop computer Bagama't hindi mapanganib ang mga naturang error dahil sa kanilang bihirang pangyayari, hindi ito katanggap-tanggap sa mga server na nagpapatakbo sa buong orasan sa loob ng ilang taon. Upang iwasto ang mga ito, ginagamit ang teknolohiya ng ECC (error-correcting code), ang kahusayan nito ay 99.988%.

Thermal design power (TDP). Mahalaga, ang pagkonsumo ng kuryente ng processor sa maximum na pagkarga. Ang mga Xeon ay karaniwang may mas maliit na thermal envelope at mas matalinong mga algorithm sa pagtitipid ng kuryente, na sa huli ay nagreresulta sa mas mababang singil sa kuryente at mas mahusay na paglamig.

L3 cache. Ang cache ng memorya ay isang uri ng layer sa pagitan ng processor at RAM, na mayroong napaka mataas na bilis. Kung mas malaki ang laki ng cache, mas mabilis na tumatakbo ang processor, dahil kahit na napakabilis ng RAM ay mas mabagal kaysa sa memorya ng cache. Ang mga processor ng Xeon ay karaniwang may mas malalaking sukat ng cache, na ginagawa itong mas kanais-nais para sa mga application na masinsinang mapagkukunan.

Dalas / Dalas sa TurboBoost mode. Ang lahat ay simple dito - mas mataas ang dalas, mas mabilis na gumagana ang processor, lahat ng iba pang bagay ay pantay. Ang base frequency, iyon ay, ang dalas kung saan gumagana ang mga processor sa ilalim ng buong pagkarga, ay pareho, ngunit sa Turbo Boost, iyon ay, kapag nagtatrabaho sa mga application na hindi idinisenyo para sa mga multi-core na processor,mas mabilis si Xeon.

Suporta ng Intel TSX-NI. Ang Intel Transactional Synchronization Extensions New Instructions (Intel TSX-NI) ay isang add-on sa processor cache system na nag-o-optimize sa execution environment ng mga multi-threaded na application, ngunit, siyempre, kung ang mga application na ito ay gumagamit ng mga interface ng programming ng TSX-NI. Nagbibigay-daan sa iyo ang mga set ng pagtuturo ng TSX-NI na mas mahusay na ipatupad ang trabaho sa Big Data at mga database - sa mga kaso kung saan maraming mga thread ang nag-a-access sa parehong data at mga sitwasyon sa pagharang ng thread. Ang pag-access ng speculative data, na ipinapatupad sa TSX, ay nagbibigay-daan sa iyong bumuo ng mga naturang application nang mas mahusay at mas dynamic na sukatin ang pagganap kapag dinadagdagan ang bilang ng mga sabay-sabay na nai-execute na mga thread sa pamamagitan ng paglutas ng mga salungatan kapag ina-access ang nakabahaging data.

Pinagkakatiwalaang suporta sa Pagpapatupad. Intel Technology Pinapahusay ng Trusted Execution ang secure na command execution sa pamamagitan ng mga pagpapahusay ng hardware sa mga Intel processor at chipset. Ang teknolohiyang ito ay nagbibigay ng mga digital office platform na may mga security feature tulad ng measured application launch at secure command execution. Ito ay nakakamit sa pamamagitan ng paglikha ng isang kapaligiran kung saan ang mga application ay tumatakbo nang hiwalay mula sa iba pang mga application sa system.

Sa mga bentahe ng mas lumang mga processor ng Xeon, maaari kang magdagdag ng mas malaking kapasidad ng L3, hanggang 45 MB, higit pa mga core, hanggang 18, at higit pang sinusuportahang RAM, hanggang 768 GB bawat processor. Kasabay nito, ang pagkonsumo ay hindi lalampas sa 160 W. Sa unang sulyap, ito ay isang napakalaking halaga, gayunpaman, dahil ang pagganap ng naturang mga processor ay ilang beses na mas mataas kaysa sa pagganap ng parehong Xeon E3-1220 V3 na may TDP na 80 W, ang mga pagtitipid ay nagiging halata. Dapat ding tandaan na wala sa mga processor Pangunahing pamilya ay hindi sumusuporta sa multiprocessing, iyon ay, posibleng mag-install ng hindi hihigit sa isang processor sa isang computer. Karamihan sa mga application para sa mga server at workstation ay mahusay na sumusukat sa mga core, thread at pisikal na processor, kaya ang pag-install ng dalawang processor ay magbibigay ng halos dalawang beses na pagtaas sa pagganap.

Petsa: 2014-08-13 22:26

Bumalik noong 2007 kumpanya ng AMD naglabas ng bagong henerasyon ng mga processor ng Phenom. Ang mga processor na ito, tulad ng nangyari sa ibang pagkakataon, ay naglalaman ng error sa TLB block (translation look-aside buffer mabilis na conversion virtual address sa mga pisikal). Ang kumpanya ay walang pagpipilian ngunit upang malutas ang problemang ito sa pamamagitan ng isang patch sa anyo ng isang BIOS patch, ngunit binawasan nito ang pagganap ng processor ng halos 15%.