Organisasyon ng pahina virtual na memorya

Sa karamihan ng mga modernong operating system virtual na memorya nakaayos gamit ang page addressing. Ang RAM ay nahahati sa mga pahina: fixed-length na mga lugar ng memorya (halimbawa, 4096 bytes) na pinakamababang yunit inilalaan na memorya (iyon ay, kahit na ang isang kahilingan para sa 1 byte mula sa application ay hahantong sa paglalaan ng isang pahina ng memorya dito). Ina-access ng isang proseso ang memorya gamit ang isang virtual memory address, na naglalaman ng numero ng pahina at ang offset sa loob ng pahina. Kino-convert ng processor ang numero virtual na pahina sa address ng kaukulang pisikal na pahina nito gamit ang isang nag-uugnay na buffer ng pagsasalin. Kung nabigo siyang gawin ito, kinakailangan ang pag-access sa talahanayan ng pahina (ang tinatawag na Page Walk), na maaaring gawin ng mismong processor o ng operating system (depende sa arkitektura).

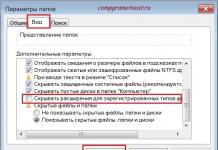

(slide No. 12)

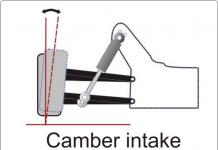

kanin. 16.4. Isang halimbawa ng organisasyon ng page.

Organisasyon ng pahina (paging) – isang diskarte sa pamamahala ng memorya kung saan:

Ang lohikal na memorya ay nahahati sa mga pahina– mga kaugnay na lugar parehong haba, kadalasang degree 2 (halimbawa, 512 salita);

ang pisikal na memorya ay naaayon na nahahati sa mga frame parehong sukat;

pamamahagi lohikal na memorya nangyayari sa katumpakan ng pahina;

· ang pisikal na memorya ng isang proseso ay maaaring hindi tuloy-tuloy;

Ang koneksyon sa pagitan ng lohikal at pisikal na memorya ng proseso ay isinasagawa gamit mga talahanayan ng pahina– ang istraktura ng system na inilaan sa proseso para sa mga broadcast kanyang lohikal na mga address sa pisikal.

Sa pagsasaayos ng pahina, ang OS ay nag-iimbak ng impormasyon tungkol sa lahat ng mga libreng frame. Dahil ang memorya ay inilalaan sa bawat pahina, posible ang panloob na pagkapira-piraso.

Ang mga layunin ng organisasyon ng pahina ay upang paganahin ang hindi magkadikit na pamamahagi pisikal na memorya para sa mga proseso, at palawakin din ang puwang ng lohikal na memorya.

Naka-on kanin. 16.4 Ang isang halimbawa ng organisasyon ng pahina ay ibinigay, na nagpapakita na, hindi katulad ng magkadikit na lohikal na memorya ng isang proseso, ang kaukulang mga frame ng pahina sa pangunahing memorya ay maaaring hindi magkadikit: ang lohikal na pahina 0 ay tumutugma sa frame 1, pahina 1 hanggang frame 4, pahina 2 hanggang frame 3, page 3 – frame 7.

(slide No. 13)

kanin. 16.5. Isang halimbawa ng organisasyon ng pahina sa mga bloke ng 4 na pahina.

Naka-on kanin. 16.5 ang isa pang posibleng halimbawa ng organisasyon ng pahina ay ibinigay: lohikal at pisikal na memorya ay nahahati sa mga bloke ng 4 na pahina sa isang hilera; Ang page table ay hindi nag-iimbak ng page number, ngunit ang page block number. Halimbawa, ang elemento 0 ng page table ay nag-iimbak ng block number 5, kung saan ang address ng simula ng block ay kinakalkula sa pamamagitan ng pag-multiply ng mga nilalaman ng page table na element sa block na laki na katumbas ng 4 (resulta - 20).

Pagpapatupad ng page table

Paggamit asosasyong memorya. Ang talahanayan ng pahina ay isang magkadikit na lugar ng pisikal na memorya. Ang sistema ay may page table base register (PTBR), itinuro ang talahanayan ng pahina at iniimbak ang haba nito.

Kaya, sa isang organisasyon ng pahina, ang anumang pag-access sa memorya ay hindi nangangailangan ng isa, ngunit dalawang pag-access sa memorya - isa sa talahanayan ng pahina, ang isa ay direkta sa data o utos. Ito ay ilang sagabal at hindi epektibo ng organisasyon ng page, kumpara sa higit pa mga simpleng pamamaraan pamamahala ng memorya.

(slide No. 14)

kanin. 16.3. Arkitektura ng pagsasalin ng address para sa paging.

Sa organisasyon ng pahina, ang lohikal na address ay pinoproseso ng system sa isang espesyal na paraan - bilang isang istraktura (p, d): ang pinakamataas na digit nito ay nagpapahiwatig numero ng pahina, juniors – offset sa loob ng pahina. Numero ng pahina (p) ay itinuturing bilang isang index sa talahanayan ng pahina, ang kaukulang elemento na naglalaman ng base address ng simula ng pahina sa pisikal na memorya. Offset sa loob ng pahina (d) ay idinagdag sa base address nito. Ang resulta ay isang pisikal na address na ipinapasa sa memory management device. Ang arkitektura ng pagsasalin ng address para sa paging ay ipinapakita sa kanin. 16.3.

(slide No. 15)

kanin. 16.7. Address translation scheme gamit ang associative memory.

Ang problema ng dalawang tawag ay malulutas sa pamamagitan ng pagpapakilala nauugnay na memorya (cache) ng mga pahina, tinatawag din translation lookaside buffer (TLB). Ang isang asosasyong memorya ay mahalagang isang nauugnay na listahan ng mga pares ng form: (numero ng pahina, numero ng frame). Ang pagganap nito ay makabuluhang mas mataas kaysa sa pangunahing memorya at mga rehistro.

Ang scheme ng pagsasalin ng address gamit ang nauugnay na memorya ay nagbabago: kung numero ng pahina mula sa lohikal na address ay matatagpuan sa associative memory, pagkatapos ay ang kaukulang elemento ay nakuha mula sa elemento nito numero ng frame. Kung ang numero ng pahina ay wala sa associative memory, ito ay pinili sa karaniwang paraan mula sa page table, ngunit ipinasok sa associative memory. Kaya, ang impormasyon tungkol sa mga pinaka-madalas na ginagamit na mga pahina ay naipon sa nauugnay na memorya.

Isang binagong scheme ng pagsasalin ng address gamit ang TLB ay inilalarawan kanin. 16.7.

Ang organisasyon ng memorya ng pahina ay ginagamit lamang sa protektadong mode, kung sa control register CR0 ang PG bit = 1.

Ang pangunahing paggamit ng paged address translation ay sa pagpapatupad ng virtual memory, na nagpapahintulot sa programmer na gumamit ng mas maraming memory space kaysa sa pisikal na pangunahing memorya.

Prinsipyo virtual na memorya Ipinapalagay na ang gumagamit, kapag naghahanda ng kanyang programa, ay hindi nakikipag-ugnayan sa isang pisikal na RAM, na aktwal na gumagana bilang bahagi ng computer at may ilang nakapirming kapasidad, ngunit may virtual (maliwanag) na single-level na memorya, ang kapasidad nito ay katumbas ng ang buong address space, na tinutukoy ng laki ng address bus (Lsha) computer:

Para sa 32-bit microprocessor:

Ang programmer ay mayroong isang address space na limitado lamang sa lapad ng address bus, anuman ang aktwal na kapasidad RAM computer at ang dami ng memory na ginagamit ng iba pang mga program na naproseso nang magkatulad sa isang multiprogram na computer.

Virtual memory, na nagbibigay sa programmer ng kakayahang mag-access ng napakalaking dami ng magkadikit na puwang ng address na ibinigay sa kanyang eksklusibong pagtatapon, ay may mga karaniwang katangian: byte-byte addressing, oras ng pag-access na maihahambing sa oras ng pag-access sa RAM.

Sa lahat ng mga yugto ng paghahanda ng programa, kabilang ang paglo-load sa memorya, ang programa ay kinakatawan sa mga virtual na address, at kapag ang isang utos ng makina ay naisakatuparan, ang mga virtual na address ay na-convert sa mga pisikal. Para sa bawat programa na naisakatuparan sa multiprogram mode, ang sarili nitong virtual memory ay nilikha. Ang bawat programa ay gumagamit ng parehong mga virtual na address mula sa zero hanggang sa pinakamalaki sa isang partikular na arkitektura.

Upang i-convert ang mga virtual na address sa mga pisikal, ang pisikal at virtual na memorya ay nahahati sa mga fixed-length na bloke na tinatawag mga pahina. Ang mga volume ng virtual at pisikal na mga pahina ay pareho. Ang mga pahina ng virtual at pisikal na memorya ay binibilang. Ang mga pahinang nawawala sa pisikal na memorya ay karaniwang naka-imbak sa panlabas na memorya. Nakapirming laki Ang lahat ng mga pahina ay nagbibigay-daan sa iyo upang i-load ang anumang nais na virtual na pahina sa anumang pisikal na pahina.

Gaya ng nabanggit sa itaas, na may paged memory, ang virtual (logical) address ay ang virtual page number at ang offset sa loob ng page na iyon. Sa turn, ang pisikal na address ay ang numero ng pisikal na pahina at ang offset sa loob nito.

Ang mga patakaran para sa pagsasalin ng mga virtual na numero ng pahina sa mga pisikal na numero ng pahina ay karaniwang tinutukoy sa anyo ng isang paging table. Ang ganitong mga talahanayan ay nabuo ng sistema ng pamamahala ng memorya at binago sa bawat oras na ang memorya ay muling inilalaan. operating system patuloy na sinusubaybayan ang estado ng mga virtual na pahina ng isang partikular na programa at tinutukoy kung ito ay nasa RAM, at kung gayon, sa anong partikular na lokasyon. Mga programa sa aplikasyon ay hindi apektado ng proseso ng paging at maaaring gamitin ang buong address space. Ang processor ay awtomatikong bumubuo ng isang espesyal na kaso ng hindi presensya kapag ang isang programa ay nag-access ng isang pahina na wala sa pisikal na memorya. Kapag pinoproseso ito espesyal na okasyon Ang OS ay naglo-load ng hiniling na pahina mula sa panlabas na memorya, nagpapadala ng ilang iba pang pahina sa disk kung kinakailangan (proseso ng pagpapalit).

Ang pagsasalin ng mga virtual na address sa mga pisikal ay inilalarawan sa Fig. 3.12.

kanin. 3.12. Ang prinsipyo ng pag-convert ng isang virtual na address ng pahina sa isang pisikal na address

Tingnan natin ang isang halimbawa ng pag-convert ng isang virtual na address ng pahina sa isang pisikal na address ng pahina. Hayaang gumamit ang computer ng paging address space ng V page = 1I at magkaroon ng RAM V RAM = 3 page. Hayaan ang apat na programa na sabay-sabay na isagawa sa isang computer, na mayroong sumusunod na bilang ng mga pahina: V A = 2, V B = 1, V C = 3, V D = 2. Ang paglipat sa pagitan ng mga programa ay nangyayari sa pamamagitan ng quantum time t k = 1. Ang oras ng pagpapatupad ng bawat pahina ng anumang programa ay t = 2t k. Naniniwala kami na ang mga pahina ng programa ay na-load sa RAM kung kinakailangan at, kung maaari, sa mga libreng lugar ng RAM. Kung ang lahat ng memorya ay inookupahan, kung gayon bagong pahina pinapalitan ang isa na hindi na-access sa loob ng mahabang panahon.

Sa ilalim ng ganitong mga kundisyon, ang talahanayan ng pag-load ng RAM at mga talahanayan ng conversion ng pahina para sa bawat programa ay magkakaroon ng form na ipinakita sa talahanayan. 3.2.

Sa talahanayan ng pamamahagi ng RAM, ang mga bilang ng mga pahinang aktibo sa isang naibigay na cycle ay naka-highlight. Sa mga talahanayan ng conversion ng page, ang mga gitling ay nagpapahiwatig ng mga sitwasyon kapag ang isang virtual na pahina ay wala sa RAM.

| Talahanayan 3.2. Isang halimbawa ng paglalaan ng memorya ng pahina sa isang multiprogram na computer | |||||||||||||||||

| Pahina | Mga bar | ||||||||||||||||

| Dynamic na pamamahagi RAM | |||||||||||||||||

| RAM 0 | JSC | JSC | JSC | GAWIN | GAWIN | GAWIN | CO | CO | CO | C1 | C1 | C1 | C1 | C1 | C1 | C1 | |

| B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D1 | D1 | D1 | D1 | D1 | D1 | |||

| C0 | C0 | C0 | B0 | B0 | B0 | A1 | A1 | A1 | A1 | A1 | A1 | C2 | C2 | ||||

| Paging table para sa programa A | |||||||||||||||||

| A 0 | - | - | - | - | - | - | - | - | - | - | - | ||||||

| - | - | - | - | - | - | - | - | - | - | ||||||||

| Paging table para sa programa B | |||||||||||||||||

| B 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| Paging table para sa programa C | |||||||||||||||||

| Mula sa 0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | |||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | - | ||||

| Paging table para sa programa D | |||||||||||||||||

| D0 | - | - | - | - | - | - | - | - | - | - | |||||||

| - | - | - | - | - | - | - | - | - | - |

Kung ang bawat pahina ay may dami ng 1000 addressable na mga cell, kung gayon, halimbawa, sa orasan 9, ang pag-access sa virtual address 1100 ng program A (virtual na pahina 1, ang offset ng pahina ay 100) ay magreresulta sa pag-access sa pisikal na address 2100 (pisikal na pahina 2, pisikal page offset kapareho ng sa virtual one, iyon ay, 100).

Isaalang-alang natin ngayon ang aplikasyon ng mga ito pangkalahatang mga prinsipyo conversion ng page address sa isang microprocessor na may IA-32 architecture na may laki ng page na 4 KB.

Ang batayan ng paging ay 32-bit linear na address, nakuha sa yugto ng pagbabago ng segment lohikal na address. Ang paging ay ginagawa kapag ang PG bit ay nakatakda sa 1 sa control register CR0.

Sa kasong ito, ang pinaka makabuluhang 20 bits linear na address aktwal na kumakatawan sa virtual na numero ng pahina. Gayunpaman, ang isang direktang one-step na conversion ng numerong ito sa isang pisikal na numero ng pahina ay nangangailangan ng isang talahanayan ng 2 20 elemento, bawat isa ay 4 na byte ang haba (20-bit na numero ng pahina at ilang karagdagang impormasyon), ibig sabihin, 4 MB. Sa isang multiprogramming na kapaligiran, ang naturang talahanayan ay maaaring kailanganin para sa bawat gawain. Ang talahanayan na ito ay dapat na permanenteng naka-imbak sa RAM upang hindi makabuluhang madagdagan ang oras ng pagbuo pisikal na address. Para sa mga layuning ito, kinakailangan na patuloy na magreserba ng isang makabuluhang bahagi ng kapasidad ng RAM, na halos imposible sa yugto ng paglitaw ng mga unang computer na nakabase sa MP na may arkitektura ng IA-32.

Sa halip, ang microprocessor ay gumagamit ng dalawang yugto ng paging ng address. Ang root page, na tinatawag direktoryo ng talahanayan ng pahina(KTS), naglalaman ng 1024 32-bit elemento ng direktoryo ng talahanayan ng pahina(ECTS - PDE page directory entry). Ang bawat isa sa kanila ay tumutugon sa isang subordinate talahanayan ng pahina(TS), iyon ay, hanggang 1024 slave page table ang pinapayagan sa kabuuan. Ang bawat talahanayan ng pahina ay naglalaman ng 1024 32-bit elemento ng talahanayan ng pahina(ETS - PTE page table entry), ang bawat isa ay tumutugon sa isang pisikal na pahina. Kaya, ang kabuuang bilang ng mga matutugunan na pisikal na pahina ay 2 20, iyon ay, ang buong virtual address space (4 KB * 220 elemento = 2 32 bytes). Ang bawat talahanayan ay sumasakop ng 1024 4 = 4 KB, iyon ay, eksaktong 1 pahina. Ang kabuuang sukat ng mga talahanayan na ginamit para sa paging ay hindi nabawasan, ngunit bahagyang tumaas dahil sa paggamit ng katalogo ng talahanayan ng pahina. Gayunpaman, una, halos palaging sa isang sistema ang laki na ito ay maaaring makabuluhang bawasan dahil sa ang katunayan na ang ilan mga linear na address ay hindi kailanman mabubuo (at ang impormasyong ito ay ibinigay mga talahanayan ng paglalarawan segment) at hindi kailangang gumawa ng page table para sa kanila. At pangalawa, tanging ang direktoryo ng talahanayan ng pahina at talahanayan ng pahina kasalukuyang tumatakbong programa. Pahinga mga talahanayan ng pahina maaaring pansamantalang maimbak sa panlabas na memorya.

kanin. 3.13. Linear sa pisikal na conversion ng pahina ng address

Kaya, ang conversion ng isang linear na address sa isang pisikal ay may form na ipinapakita sa Fig. 3.13.

Pinakamataas na 20 digit linear na address ay nahahati sa dalawang 10-bit na field: field mga numero ng item ng page table catalog at patlang mga numero ng elemento ng talahanayan ng pahina. Since direktoryo ng talahanayan ng pahina, at bawat isa talahanayan ng pahina sumasakop ng eksaktong 1 pahina at nakahanay sa isang hangganan ng pahina, pagkatapos ay ang low-order na 12 bits ng kanilang base address ay zero, at isang 20-bit na field ay sapat upang matukoy ang kanilang pisikal na address.

Para sa direktoryo ng talahanayan ng pahina ang 20-bit address nito ay nasa control register CR3. Ang CTS ay permanenteng nasa memorya at hindi nakikilahok sa pagpapalit.

Ang itaas na 20 bits ng pisikal na address mga talahanayan ng pahina ay nakuha mula sa ETS. Ang mga istruktura ng elemento ng CTS at ang elemento ng TS ay magkatulad (Larawan 3.14).

kanin. 3.14. Istraktura ng mga elemento ng katalogo ng talahanayan ng pahina at mga talahanayan ng pahina

Ang pinakamataas na 20 bits ng elemento ay nagbibigay base address mga talahanayan ng pahina(sa ECTS) o pisikal na pahina (sa ETS). Ang P, A, R/W at U/S bit ay may ilang partikular na pagkakatulad sa mga segment na descriptor ay may mga partikular na layunin;

Kaunting presensya Ipinapahiwatig ng P kung ang address ng isang frame ng pahina (talahanayan ng pahina o pahina ng memorya) ay nakamapa sa isang pahina sa pisikal na memorya. Kapag P = 1, ang page ay nasa RAM. Kapag P = 0, walang page sa memory, at ang pag-access sa page na ito ay nagdudulot ng page fault interrupt.

Access bit Ang A ay itinakda ng microprocessor na maglagay ng A = 1 kapag ina-access ang page frame na ito upang magsulat o magbasa ng impormasyon.

Bit ng pagbabago D (Dirty - "marumi") ay itinakda ng processor na katumbas ng 1 sa elemento ng ETS kapag sumusulat sa pahinang ito. Para sa mga entry sa direktoryo ng talahanayan ng pahina, ang halaga ng D bit ay hindi natukoy. Kapag naglo-load ng isang pahina sa memorya, ang operating system ay nagre-reset ng bit D. Kung, kapag kinakailangan upang i-unload ang isang pahina sa panlabas na memorya, lumalabas na D = 0 para dito, nangangahulugan ito na walang mga access sa pagsulat sa pahina sa memorya; eksaktong kopya, at hindi na kailangang aktwal na ilipat ang pahina mula sa memorya patungo sa disk. Makakatipid ito ng oras kapag nagpapalit.

Ang read-write bit na R/W at ang U/S bit (user/supervisor) ay tumutukoy sa mga karapatan sa pag-access sa page table o page para sa mga program na may iba't ibang antas ng pribilehiyo. May 2 antas lang ng mga pribilehiyo para sa mga page: antas ng superbisor (U/S = 0), na tumutugma sa halaga ng DPL ng segment 0, 1, 2, at antas ng user (U/S = 1), na tumutugma sa DPL = 3. Kung ang isang pahina ay hiniling na may antas ng pribilehiyo 3 (programa ng gumagamit), pagkatapos ay may halagang U/S = 0, hindi siya pinagkaitan ng access sa kaukulang talahanayan o pahina. Kung U/S = 1, pagkatapos ay kapag R/W = 0, ang pagbabasa lamang ng talahanayan o pahina ang pinapayagan, at kapag R/W = 1, ang parehong pagbabasa at pagsusulat ay pinapayagan.

Para sa mga kahilingang may mataas na pribilehiyo (system mga antas ng programa 0, 1, 2) ang pagsulat at pagbabasa ng mga talahanayan at pahina ay pinapayagan para sa anumang mga halaga ng U/S, R/W (Talahanayan 3.3).

Ang PWT at PCD bits ay ginagamit upang kontrolin ang pagpapatakbo ng cache memory sa panahon ng page addressing. PCD bit - huwag paganahin ang pag-cache ng pahina. Kapag ang PCD = 1, ang pag-cache ay hindi pinagana. PWT bit - bit sumulat muli mga pahina. Tinutukoy ang paraan para sa pag-update ng panlabas na cache (L2 cache). Kapag PWT = 1, ang pag-update ay isinasagawa gamit ang write-through na paraan (tulad ng para sa panloob na cache), kapag PWT = 0, gamit ang write-back na paraan.

Ang mga bits 9...11 sa ECTS at ETS ay nakalaan para sa operating system. Hindi kailanman ginagamit o binabago ng processor ang mga bit na ito. Maaaring gamitin ng mga developer ng OS ang mga bit na ito upang mag-imbak ng impormasyon sa pagtanda ng pahina, upang matukoy kung aling mga pahina ang dapat palitan mula sa panlabas na memorya, at para sa iba pang mga layunin.

Senior 10 digit linear na address kasama ang mga nilalaman ng control register CR3 matukoy ang kinakailangan elemento ng direktoryo ng talahanayan ng pahina. Ang susunod na 10 bits ng linear address ay naglalaman ng entry number sa napiling page table.

Dahil ang parehong ECTS at ETS ay 4 bytes ang haba, upang makuha ang offset ng simula ng isang elemento na nauugnay sa simula ng kaukulang talahanayan, ang bilang nito ay dapat na i-multiply sa 4.

Huling 12 digit linear na address naglalaman ng offset sa page. Kaya, ang kabuuan ng page offset at ang page base address na nakuha mula sa ETS ay nagbibigay ng pisikal na address ng byte na hinahanap.

Sa paged system, pangunahing at panlabas na memorya (pangunahin espasyo sa disk) ay nahahati sa mga bloke, o mga pahina, na may nakapirming haba. Ang bawat gumagamit ay binibigyan ng isang tiyak na bahagi ng espasyo ng address, na maaaring lumampas sa pangunahing memorya ng computer at na limitado lamang sa pamamagitan ng mga kakayahan sa pagtugon na likas sa sistema ng pagtuturo. Ang bahaging ito ng puwang ng address ay tinatawag na virtual memory ng gumagamit. Ang bawat salita sa virtual memory ng user ay tinutukoy ng isang virtual na address, na binubuo ng dalawang bahagi: ang mga high-order bit ng address ay itinuturing bilang page number, at ang low-order bits ay itinuturing bilang ang bilang ng salita (o byte) sa loob ng pahina.

Ang bawat elemento ng talahanayan ng pahina ay naglalaman ng isang pisikal na numero ng pahina sa pangunahing memorya at isang espesyal na tagapagpahiwatig. Ang isang estado ng tagapagpahiwatig na ito ay nagpapahiwatig ng pagkakaroon ng pahinang ito sa pangunahing memorya. Ang zero state ng indicator ay nangangahulugan na walang page sa RAM.

Ang paghahanap sa mga talahanayan ng pahina na matatagpuan sa pangunahing memorya at pag-load ng TLB ay maaaring gawin sa pamamagitan ng programming, o espesyal na hardware. Para sa layuning ito, ang processor ay nagbibigay ng karagdagang rehistro ng proteksyon na naglalaman ng isang page table descriptor o isang base-boundary na pares. Tinutukoy ng base ang address ng simula ng talahanayan ng pahina sa pangunahing memorya, at tinutukoy ng hangganan ang haba ng talahanayan ng pahina ng kaukulang programa.

Ang isang solusyon sa problema ng pagbabawas ng haba ng mga talahanayan ay batay sa pagpapakilala ng isang multi-level na organisasyon ng mga talahanayan. Ang isang espesyal na kaso ng multi-level na organisasyon ng mga talahanayan ay ang pagse-segment sa page organization ng memory. Ang pangangailangan na dagdagan ang puwang ng address ng gumagamit ay ipinaliwanag sa pamamagitan ng pagnanais na maiwasan ang pangangailangan na ilipat ang mga bahagi ng mga programa at data sa loob ng espasyo ng address, na kadalasang humahantong sa pagpapalit ng pangalan ng mga problema at malubhang kahirapan sa paghahati. pangkalahatang impormasyon sa pagitan ng maraming gawain.

Pag-segment ng memorya

Sa mga system na may memory segmentation, ang bawat salita sa address space ng user ay kinikilala ng isang virtual na address, na binubuo ng dalawang bahagi: ang mga high-order bit ng address ay itinuturing na segment number, at ang low-order bits ay itinuturing na ang bilang ng salita sa loob ng segment. Kasama ng segmentation, maaari ding gamitin ang paging memory organization. Sa kasong ito, ang virtual na address ng isang salita ay binubuo ng tatlong bahagi: ang mataas na pagkakasunud-sunod na mga bit ng address ay tumutukoy sa numero ng segment, ang mga gitnang bit ay tumutukoy sa numero ng pahina sa loob ng segment, at ang mababang pagkakasunud-sunod na mga bit ay tumutukoy sa numero ng salita sa loob ng pahina .

Tulad ng paging, kinakailangan upang matiyak na ang virtual address ay isinalin sa tunay na pisikal na address ng pangunahing memorya. Para sa layuning ito, ang operating system ay dapat bumuo ng isang talahanayan ng segment para sa bawat user. Ang bawat elemento ng talahanayan ng segment ay naglalaman ng isang descriptor (descriptor) ng segment (mga base field, hangganan at mga indicator ng access mode). Sa kawalan ng organisasyon ng pahina, tinutukoy ng base field ang address ng simula ng segment sa pangunahing memorya, at tinutukoy ng hangganan ang haba ng segment. Kung mayroong organisasyon ng pahina, ang base field; tinutukoy ang address ng simula ng talahanayan ng pahina ng isang partikular na segment, at ang hangganan - ang bilang ng mga pahina sa segment. Ang field ng indicator ng access mode ay ilang kumbinasyon ng read, write, at execute lock indicator.

ESPESYAL NA BAHAGI

Layunin at pag-andar sistema ng software

Ang binuo database ng Polyclinic ay inilaan para sa paggamit sa mga institusyong medikal. Ang pangunahing function ay ang pag-iimbak ng data at kadalian ng paghahanap para sa mga medikal na talaan ng mga pasyente sa klinika.

Pangunahing bagay:

1) mga pasyente;

2.2. Mga Kinakailangan sa System

Ang mga sumusunod na mapagkukunan ay kinakailangan para gumana ang database:

· Proseso ng Pentium 133 o mas mataas;

· minimum na halaga ng RAM - 32 MB;

· hard drive may lakas ng tunog libreng espasyo hindi bababa sa 100 MB;

· CD-ROM, keyboard, mouse.

Upang patakbuhin ang database na ito, kinakailangan ang Visual Fox Fox Pro 6 at operating system: Windows 98/ME/NT 4.0/2000/XP.

Ang mga pangunahing bagay nito sistema ng impormasyon:

· "Impormasyon tungkol sa mga doktor" - naglalaman ng impormasyon tungkol sa mga doktor;

· "Impormasyon ng Pasyente" - naglalaman ng personal na data ng pasyente;

· “Accounting for admissions and discharges” - naglalaman ng impormasyon tungkol sa diagnosis at oras ng pananatili ng mga pasyente sa ospital.

Pag-uugnay ng mga talahanayan

Pinapayagan ka ng Access 2007 na bumuo mga database ng relasyon data, mga indibidwal na talahanayan na maaaring magkaugnay.

Ang pinakasimple at pinakabihirang anyo ng relasyon sa pagitan ng mga talahanayan ay isang isa-sa-isang relasyon, kung saan para sa bawat tala sa isang talahanayan ay mayroong pinakamahusay na senaryo ng kaso isang kaugnay na tala sa isa pang talahanayan.

Higit na karaniwan ay ang isa-sa-maraming relasyon, kung saan para sa bawat tala sa isang talahanayan ay may isa, higit pa, o walang mga tala sa isa pang talahanayan.

Kadalasan kailangan mo ring harapin ang isang relasyon na marami-sa-maraming, kung saan walang mga paghihigpit sa hanay ng mga pares ng mga tala na kabilang sa relasyon. Ang ganitong uri ng relasyon ay hindi ginagamit sa Access. Dapat itong kinakatawan bilang dalawang one-to-many na relasyon.

Sa database ng Polyclinic, ang mga talahanayan ay nauugnay sa isa't isa ng dalawang isa-sa-maraming relasyon.

Mga kahilingan

Ang kahilingan ay espesyal na function, na nagpapahintulot sa iyo na mag-output mga kinakailangang field mula sa talahanayan, pati na rin magsagawa ng mga operasyon sa mga patlang na ito sa mode ng disenyo, halimbawa, pagkalkula ng kabuuan, pagpili ng mga patlang, pagkalkula ng average na kabuuan. Mayroong ilang mga uri ng mga query: piliin, magdagdag, tanggalin, i-update, query sa paggawa ng talahanayan, cross query. Maaaring gamitin ang query upang magsagawa ng mga kalkulasyon. Ang mga pag-andar ng istatistika ay ibinigay para sa mga layuning ito. Pag-andar ng istatistika itinakda sa linya ng pagpapatakbo ng Grupo.

Talahanayan 3 "Mga pag-andar at operasyong isinagawa"

Ang listahan ng mga query na ginamit sa database na ito ay ibinigay sa ibaba.

Query "Mga doktor at kanilang mga pasyente"

Ang query na "Mga doktor at kanilang mga pasyente" ay nagbibigay-daan sa iyo na ipakita ang mga pangalan ng mga doktor na nagtatrabaho sa isang partikular na medikal na espesyalidad.

Query "Oras na ginugol sa ospital"

Nagbibigay-daan sa iyo ang query na "Oras ng Pananatili sa Hospital" na malaman ang tagal ng pananatili ng isang pasyente sa ospital.

Query "Mga babaeng pasyente"

Ang query na "Mga Pasyenteng Babae" ay nagpapakita ng mga babaeng pasyente

Query "Mga pasyente na paulit-ulit na nakahiga"

Ang query na "Mga pasyente na na-admit sa ospital nang higit sa isang beses" ay nagpapakita ng mga pasyente na na-admit sa ospital nang higit sa isang beses.

Query "Mga retiradong pasyente"

Ang query na "Mga retiradong pasyente" ay nagpapakita ng lahat ng mga pasyente na umabot na sa edad ng pagreretiro.

Query "Pagpili ng espesyalidad ng doktor sa pamamagitan ng diagnosis"

Ang kahilingan na "Pagpili ng espesyalidad ng doktor sa pamamagitan ng diagnosis" ay nagbibigay-daan sa iyo upang matukoy ang isang doktor na dalubhasa sa isang partikular na sakit sa pamamagitan ng pagpasok ng diagnosis kapag pinapatakbo ang kahilingan.

Mga porma

Paggawa gamit ang data sa table mode ay may makabuluhang sagabal: kung mayroong masyadong maraming mga patlang, hindi sila magkasya sa screen at kailangan mong gumamit ng iba't ibang mga manipulasyon upang ma-optimize ang pagtatanghal: halimbawa, pag-alis ng ilang mga haligi, pagbabago ng kanilang posisyon.

Kapag nagawa mo na ang iyong database (at marahil isa o higit pang mga talahanayan), maaari kang lumikha ng mga form upang tingnan ang data sa isang mas maginhawang paraan. Ang form ay maaaring magsilbi bilang isang paraan ng pagprotekta sa database mula sa hindi kwalipikadong mga user, pati na rin ang isang screen na sumasangga sa kumpidensyal na impormasyon mula sa prying mata.

Ang anumang form ay binuo batay sa isang Access table o query. Ang mga pangalan ng patlang ay kinuha mula sa detalye ng talahanayan, at ang mga patlang sa form ay maaaring isaayos ayon sa gusto. Maaari kang bumuo ng ilang mga form batay sa isang talahanayan.

Sa Access 2007, mayroong ilang mga paraan upang lumikha ng mga form:

Talahanayan 4 Mga paraan upang lumikha ng mga form

Mayroong ilang mga uri ng mga autoform:

Form - Lumikha ng isang form upang magpasok ng data ng isang tala sa isang pagkakataon

Split Form - Gumawa ng split form na may table sa itaas at form sa ibaba para sa pagpasok ng data sa isang record na naka-highlight sa table.

Maramihang Mga Item - Lumikha ng isang form na nagpapakita ng mga tala sa isang talahanayan na ang bawat tala ay nasa sarili nitong hilera

Sa tuwing magbubukas ka ng naka-save na form, ina-update ang data sa talahanayan o query kung saan ginawa ang form. Tinitiyak nito na ang nilalaman ng form ay palaging tumutugma sa impormasyon sa mga talahanayan o query.

Ang listahan ng mga form na ginamit sa gawaing ito ay ibinigay sa ibaba:

Form ng medikal na kasaysayan

Ipinapakita ng form na "Medical History" ang data ng pasyente, diagnosis at petsa ng pagpasok sa ospital na may ganitong diagnosis.

Pangunahing button form

Ang form ng pangunahing pindutan ay idinisenyo upang buksan ang mga query sa database, mga form at mga ulat sa pamamagitan ng pag-click sa kaukulang pindutan sa lugar ng form ng pangunahing pindutan.

Form "Impormasyon tungkol sa mga doktor"

Ang form na "Impormasyon tungkol sa mga doktor" ay ipinakita sa isang ribbon form at ipinapakita ang pangalan at espesyalidad ng doktor.

Form ng Impormasyon ng Pasyente

Ang form ng Impormasyon ng Pasyente ay isang uri ng laso ng form na nagpapakita ng impormasyon ng pasyente.

Mga ulat

Ginagamit ang mga ulat upang ipakita ang data ng talahanayan o query sa isang format na madaling gamitin (may mga heading at numero ng pahina).

Karamihan sa impormasyon sa isang ulat ay nagmumula sa batayang talahanayan at query, na siyang mga pinagmumulan ng data para sa ulat. Ang ibang impormasyon ay ipinasok kapag nagdisenyo ka ng ulat. Maaari kang gumamit ng maraming talahanayan at query kapag gumagawa ng ulat.

Ang paggamit ng mga ulat ay may mga sumusunod na pakinabang:

· Ang data ay maaaring ipakita sa isang form na maginhawa para sa pagbabasa at pagsusuri;

· Binibigyang-daan ka ng ulat na paganahin at i-print mga graphic na bagay(halimbawa, mga diagram);

· nagbibigay ng kakayahang gumawa ng materyal na nakalimbag sa papel.

Ang mga ulat ay maaaring gawin sa dalawang paraan:

1) gamit ang report/auto-report wizard;

2) "manu-mano".

Iulat ang "Mga Doktor ayon sa espesyalidad"

Ang ulat na "Mga Doktor ayon sa espesyalidad" ay binuo sa anyo ng isang layout ng "istruktura" na may antas ng pagpapangkat ayon sa espesyalidad ng doktor at ipinapakita ang lahat ng mga doktor ng klinika ayon sa partikular na espesyalidad.

Iulat ang "Mga Pasyente-Mga Pensiyonado"

Ang ulat ng Mga Retiradong Pasyente ay nagpapakita ng lahat ng mga pasyente ng edad ng pagreretiro.

Iulat ang "Accounting para sa mga resibo at pahayag"

Ang ulat na "Accounting for admissions and discharges" ay ginawa gamit ang isang antas ng pagpapangkat ng data presentation ayon sa buong pangalan ng pasyente at nagbibigay-daan sa iyong tingnan ang data sa mga diagnosis, admission at discharges ng mga pasyente

Mga macro

Maginhawang bumuo ng mga macro upang i-automate ang mga simpleng proseso, tulad ng pagbubukas at pagsasara ng mga form at ulat, pagpapakita o pag-print ng mga dokumento, atbp. Kasama sa macro window ang apat na column: Macro name, Condition, Macro command, Arguments, Note.

Kapag gumagawa ng bagong macro, bilang default, ang mga column na Macro, Argument, at Note lang ang ipinapakita. Ang pagpapakita ng iba pang mga column ay nakatakda gamit ang mga opsyon sa Macro Names and Conditions mula sa Design menu. Tinutukoy ng column ng pangalan ng Macro ang pangalan ng macro na dapat tukuyin kung naglalaman ang window ng ilang macro. Sa column na Kundisyon, maglalagay ka ng kundisyon para sa pagpapatupad lamang ng bahagi ng macro. Inililista ng column ng Macro command ang mga aksyon na isasagawa sa kinakailangang pagkakasunod-sunod. Ang hanay ng Tala ay naglalaman ng komento tungkol sa programa at ginagawang mas malinaw ang macro text.

KONGKLUSYON

Kaya, sa panahon ng proseso ng disenyo ng database, maaari tayong makarating sa konklusyon na maayos na organisasyon Ang pag-iimbak at paglalahad ng data ay isang mahalagang bahagi para sa matagumpay na paggana ng isang database. Ang isang malaking papel sa pagbuo ng isang database sa MS Access ay nilalaro ng naturang kapaki-pakinabang na mga tampok, tulad ng paglikha ng mga query na nagbibigay-daan sa iyong piliin ang mga kinakailangang field mula sa isang malaking hanay ng data, pati na rin magsagawa ng aritmetika at lohikal na operasyon sa mga larangang ito.

Malaki ang papel na ginagampanan ng mga form sa pag-aayos ng mga database, dahil nilikha ang mga ito upang direktang palitan o dagdagan ang data sa mga talahanayan sa pamamagitan ng mga form mismo, at mas malinaw ding kinakatawan ng mga form ang impormasyong nakapaloob sa mga talahanayan. Ang mga ulat ay hindi mas mababa mahahalagang elemento sistema ng impormasyon, dahil sa pamamagitan ng paglikha ng mga ulat maaari kang mag-print ng data mula sa sistema ng impormasyon sa papel sa pamamagitan ng unang pagpili mga kinakailangang antas data grouping, na kung saan ay napaka-maginhawa kapag nagtatrabaho sa malalaking volume datos.

LISTAHAN NG MGA GINAMIT NA SANGGUNIAN

1. Petsa K. J. Panimula sa mga sistema ng database / Transl. mula sa Ingles ika-6 na ed. K.: Dialectics, 1999.

2. Zamulin A.V. Database at mga knowledge programming system. Novosibirsk: Agham. Sib. Dept., 2002.

3. Martin J. Organisasyon ng mga database sa mga sistema ng pag-compute. / Per. mula sa Ingles M.: Mir, 2000.

4. Romanov B. L., Kushnirenko A. S. dBase IV. Layunin, pag-andar, aplikasyon. M.: Radyo at mga database, 1999.

5. Ullman J. Mga Batayan ng mga sistema ng database. M.: Pananalapi at Istatistika, 2003.

6. Borodaev V. A., Kustov V. N. Mga bangko at database. Uch. allowance. L.: VIKI, 2000.

7. Kuznetsov S. D. Panimula sa DBMS: bahagi 4. // Database Management Systems, No. 4, 1999. - P. 114-122.

Ang kakanyahan ng organisasyon ng paging ay ang puwang ng address ay nahahati sa mga segment ng parehong haba (volume), na tinatawag na mga pahina, dahil maraming mga pahina, pagkatapos ay upang mag-imbak ng impormasyon, kailangan mong lumikha ng mga blitz para sa kanila. Ang talahanayan ng pahina ay nagtatatag ng isang sulat sa pagitan ng virtual na address at ng totoong address ng pahina, sa naturang pahina ang numero ng linya ay tumutukoy sa virtual na address, ang nilalaman ng linyang ito sa talahanayan ay nagpapahiwatig ng pisikal na address. Ang pangalan ng page ay ang unit ng memory allocation at deallocation, at ang page mechanism ay ginagamit din ng iba't ibang proseso para ma-access ang shared data at programs. Dynamic na library nakaimbak sa isang kopya at sa iba't ibang proseso tumutugma ang mga ito sa iba't ibang mga virtual na address, na ibinigay ng iba't ibang mga talahanayan ng pahina. Ang lahat ng memorya ay nahahati sa pantay na laki. Ang RAM ay inilalaan at pinalaya ng isang pahina sa isang pagkakataon, sa gayon ay inaalis ang pagkapira-piraso ng memorya. Isa, dalawa o tatlong antas ng page addressing ang ginagamit

Pag-address ng isang antas ng page. Ang lahat ng memorya ay nahahati sa mga pahina at ang impormasyon ay nakolekta sa isang talahanayan ng pahina, kung saan ang mga visual na address ng sunud-sunod na lohikal na mga pahina ay nakasulat.

Ang pamamaraang ito ng isang antas ng pagtugon para lamang sa malalaking 4MB na pahina ay ginagamit lamang ng OS, pasadyang mga application hindi sila gumagana sa mode na ito

Dalawang antas na pagtugon. Gumagamit ang bawat application ng Direktoryo ng Pahina at talahanayan ng pahina. Tinukoy ng direktoryo ang mga address ng mga talahanayan ng pahina. Ang buong address ay nahahati sa 3 bahagi

Tinutukoy ng A0 ang mga offset sa loob ng page

Tinutukoy ng A1 ang row number sa row table (maximum na 1024 row). Ang bawat naturang linya ay dapat maglaman ng address ng simula ng pahina. Ang laki ng mga pahina ay 4kb din, ibig sabihin, isang pahina.

Bilang resulta, ang naturang talahanayan ay maaaring tumukoy ng espasyo na 1024 na pahina o 4 MB. Kung kilala ang memorya para sa isang application, matutukoy mo ang bilang ng mga pahina.

Tinutukoy ng A2 ang numero ng linya sa direktoryo ng pahina, (hindi hihigit sa 1024) ang laki ay 4kb din. Tiyak na mayroong isang direktoryo sa memorya, at ang control yard nito ay dapat na naka-imbak sa rehistro ng CR2 Kapag pinagsama ang A0 at A2, maaari kang makakuha ng mga halaga ng offset sa loob ng pahina, ngunit sa isang mas malaking sukat.

Tatlong antas na pag-address ng pahina. Ang address ay nahahati sa 4 na bahagi

| A3 | A2 | A1 | A0 |

Ang laki ng talahanayan mismo ay nananatiling 4kb, ngunit ang laki ng hilera ay tumataas ng 2 beses.

Tinutukoy ng A3 ang isa sa 4 na talahanayan ng katalogo. Sa 3 antas ng pag-address ng page na magagamit mo malalaking pahina 2 MB na nauubos ang A1 A0. presensya o kawalan tiyak na memorya sinusubaybayan ang proseso mismo gamit ang isang interrupt na mekanismo. Ang memorya para sa mga code ng programa, ang data ay inilalaan ayon sa address ng pahina ng simula ng pahina, na isang maramihang haba nito kung ang ilang piraso ng data ay matatagpuan sa dulo ng pahina, ang mga bagong pahina ay nilikha. Kapag bumubuo ng mga application na kritikal sa memorya, kailangan mong malaman ang laki ng pahina at ihanay ang address ng simula ng pahina, kabilang ang pahina at direktoryo, ay palaging multiple ng laki ng pahina, at samakatuwid, sa alinman sa mga isinasaalang-alang na opsyon, ang Ang low-order na 12 bits ng address ng page ay libre. Ang isang talahanayan ay ginagamit upang mag-imbak ng karagdagang impormasyon tungkol sa isang pahina. Ang karagdagang impormasyon tungkol sa pahina ay nagpapahintulot sa iyo na magtakda: ang tanda ng uri ng pahina para sa pagsulat o pagbabasa, ang tanda ng pagkakaroon ng pahina sa memorya, ang antas ng mga pribilehiyo ng pahina, ang tanda na may mga pagbabago dito pahina (kinakailangan para sa pagtatasa ng integridad kung sakaling i-reset ito, isulat sa disk, itinakda ng pahina kapag ina-access ang pahina sa mode ng pag-record at na-reset pagsusuri ng programa) isang palatandaan kung na-access ang isang naibigay na pahina, mga mode ng paggamit ng cache. Kapag gumagamit ng malalaking talahanayan at mga pahina, ang linya ng katalogo ay nagpapahiwatig na ito ay tumutugma sa talahanayan a malaking mesa. Sa antas ng hardware, pinapayagan ka ng processor na gumamit ng mga pahina ng tatlong laki, magtakda ng mga mode ng pag-access at mga antas ng pribilehiyo. Kung wala sa memorya ang page, bubuo ang processor ng mga exception na pinoproseso ng OS.

Mga pagkilos ng exception handler:

1) Maghanap ng isang libreng pahina o alisin ang isang abala kung walang mga libre

2) I-load ang pahina sa memorya

3) Isulat ang address sa Page Table kung kinakailangan, gawin ang kinakailangang ...

4) I-refresh ang mga pahina ng cache

5) Bumalik sa utos ng pag-access ng memorya na naging sanhi ng pagpoproseso ng pagbubukod.

Pagse-set ng paging (5 hakbang + control registers)

Diskarte sa paglo-load at pagbabawas ng pahina

Kapag regular na gumagamit, kailangan mong lutasin ang mga sumusunod na katanungan:

1) Tukuyin kung alin ang kailangang alisin sa memorya

2) tukuyin kung aling mga pahina ang na-load

3) tukuyin ang mga paraan ng paglo-load ng pahina

Ang mga pahina ay tatanggalin sa memorya kung walang sapat na espasyo para sa kanila tunay na alaala. Ang mga pahina na inookupahan ng OS kernel ay hindi na-unload. Upang malutas ang isyu ng pag-unload ng pahina, ang mga sumusunod na diskarte ay ginagamit:

1) Pinakamainam na algorithm– para mag-unload ng page, pumili ng mga page na hindi nagkaroon ng higit sa isang access. Disadvantage 6: Kinakailangang malaman ang kasaysayan ng trabaho ng bawat talahanayan.

2) Algorithm na may paunang pagsusuri, ang mga pahina na dapat tawagan sa susunod na mga utos ng mga aktibong proseso ay sinusuri. Ang mga pahina na dapat gamitin pa ay hindi na-unload mula sa memorya. Mga disadvantage: kinakailangan ang pagsusuri sa proseso upang matukoy ang mga pahina na kailangan nila.

3) Random - ang talahanayan na ina-upload ay random na tinutukoy, na may impormasyon para sa kanilang paggamit o higit pa, ngunit posible na ang impormasyon ay maaaring magamit pa

4) Kronolohiko - ang mga ito ay ibinaba mula sa memorya nang eksakto sa pagkakasunud-sunod kung saan sila na-load. Mga disadvantages: maaaring kailanganin ang isang mesa.

5) Kronolohikal na pagkakasunud-sunod, isinasaalang-alang ang paggamit (List R..Paggamit)1 - isang pahina na hindi nagamit nang mahabang panahon ay pinili upang makilala ang mga naturang pahina, hindi isang pila ang nabuo, ngunit isang listahan ng mga ginamit na talahanayan. Ito ay ginagamit upang magsulat sa dulo ng naturang file; Disadvantage: ang pahina na kailangan sa susunod na hakbang sa pagpapatupad ay maaaring i-unload. Ito ay kadalasang ginagamit sa mga modernong operating system.

Ang gumaganang hanay ng mga pahina ay ang hanay ng mga pahina na ginagamit ng programa upang suriin ang iba't ibang mga diskarte sa pamamahala ng pahina at suriin ang pagiging epektibo ng pagpaplano ng memorya. Ang anumang programa ay maaaring isagawa habang ang hanay ng pahina nito ay nasa memorya. May mga global at lokal na pamamaraan pamamahala ng pahina.

Ang lokal na pamamaraan ay nagbibigay-daan para sa bawat proseso na mailaan ayon sa gumaganang set nito, at ang page management algorithm ay inilalapat sa bawat programa sa loob ng working set nito.

Pandaigdigang pamamaraan - nagmamay-ari ng buong hanay, inilalaan kung kinakailangan, anuman ang aplikasyon kung saan ang mga pahinang ito ay inilalaan (para sa lahat ng mga aplikasyon ay ginagamit ang isang sentralisadong mekanismo ng pamamahala). Sa kasong ito, kailangan itong itago sa camou application na kinabibilangan nito.

Ang pagdulas ay isang sitwasyon na nagpapahiwatig malaking loading mga sistema, ibig sabihin, mayroon malaking bilang Ang mga proseso at kakulangan ng pisikal na memorya ay humahantong sa isang makabuluhang pagbawas sa pagiging produktibo. Mga paraan upang labanan ang pagkadulas:

1) Pagtaas ng dami ng pisikal na memorya

2) Mga limitasyon sa bilang ng mga aktibong proseso

3) Pagbabawas ng kinakailangang halaga ng memorya na inilalaan para sa proseso

4) Mga espesyal na algorithm para sa pagpili ng mga pahina.

Mga mekanismo ng pamamahala ng memorya

Upang gumana sa memorya, 3 pangunahing mekanismo ang ginagamit

1. Virtual memory para sa pagtatrabaho sa malalaking volume

2. Pagma-map ng mga file sa memorya (kailangan mo ng mabilis na pagproseso o random na pagproseso, pati na rin ang paglikha ng memorya na ibinabahagi sa pagitan ng mga proseso)

3. "Heaps" - mekanismo ng paglalaan maliliit na volume memorya ng aplikasyon

Paggamit ng virtual memory – para maglaan ng memory region (malaking halaga ng memory), gamitin ang function

LPVOID VirtualAlloc(

LPVOID lpAdress, // panimulang address ng inilaan na lugar (nakahanay sa 64kb na hangganan, kung nakahanay ang memorya, dapat na nakahanay ang address sa simula ng pahina, ang unang paglalaan ng memorya ay may mga NULL na halaga)

DWORD lpSize, // laki ng inilalaan na memorya sa KB (rehiyon), kung ang unang parameter ay NULL pagkatapos ito ay tataas sa hangganan ng pahina

DWORD flAllcocationType, // uri ng pagpapatakbo ng alokasyon (iisa man o kumbinasyon ng mga flag) Talahanayan ng Bondarenko 6.1 exe attribute ay hindi suportado

Ibalik ang mga halaga: kung ang pamantayan ay natupad, pagkatapos ay ang memorya ng address, kung ang mga error, pagkatapos ay ang walang laman na halaga. Sa pisikal na memorya ito ay ginagamit tulad nito: una ang isang malaking rehiyon ay inilalaan, at pagkatapos ay ang bloke nito ay tinatawag.. Ang komunikasyon sa pisikal na memorya ay isinasagawa para sa isang maliit na lugar kung saan ito ay kinakailangan. Sa kasong ito, ang pahina ay maaaring nasa sumusunod na estado: libre (ang pahina ay hindi nakalaan o naka-link), nakalaan o naka-link. Kung ang pahina ay nasa isang libreng estado, ang function na iyon ay maaaring magbigkis Kung ang pahina ay nakalaan, nangangahulugan ito na ang pahinang ito ay hindi magagamit ng iba pang mga pag-andar at wala pang pisikal na address. Ang function ay maaaring mag-link ng isang nakareserbang pahina, ngunit hindi ito maipareserba muli. Ang vrtualfree function ay maaaring magbakante ng mga nakareserbang pahina. Kung ang page ay nasa isang naka-link na estado, kung gayon

Ang system ay nagsisimula at nagrereserba, kapag sinusubukang i-access ang naturang memorya, pagkatapos makumpleto ang proseso, ang OS ay nagpapalaya sa lahat ng mga pahina na nakatalaga dito. Maaaring mag-rebind ang VirtualAlloc function. Ang pisikal na memorya na nauugnay sa mga partikular na pahina ay maaaring mapalaya gamit ang virtualFree function. Para sa pangmatagalang imbakan ng memorya, mas mahusay na maglaan ng mga address sa mga pahina. Sa kasong ito, ang NULL ay ipinapasa sa address at ang MEM_RESERVE, MEM_TOP_DOWN/ na mga flag ay nakatakdang ireserba para sa rehiyon, inirerekumenda na itakda ang pinaka-pangkalahatang katangian ng proteksyon. Kapag naglalaan ng virtual memory, maaari mong itakda ang lahat ng mga katangian ng proteksyon maliban sa mga nauugnay sa pisikal na memorya: PAGE_WRITECOPY, PAGE_EXECUTE_WRITECOPY, PAGE_GUARD, PAGE_NOCACHE.

Maaari mong ilaan hindi ang buong lugar ng pisikal na memorya, isang bahagi lamang. Kung ang laki ng inilalaang memorya ay tumutugma sa laki ng nauugnay na memorya, hindi mo maaaring tawagan ang function nang dalawang beses, ngunit itakda ang MEM_COMMIT|MEM_RESERVE na mga flag. Upang ibalik ang pisikal na memorya, ang mshkgfdaccus function ay ginagamit kasama ang parameter na memorya ng start address, laki ng seksyon at MEM_DECOMMIT, kung ang laki ay tinukoy bilang laki 0, pagkatapos ay ang lahat ng memorya ay napalaya, kung ang mga pag-access ay nangyari sa memorya, ang isang error ay nangyayari. Mayroong 3 mga pagpipilian para sa pagpapalaya ng mga pahina

1. Ipinapalagay na ang isang talaan ay tumutugma sa isang pahina;

2. Lumikha ng isang busy write bitmap

3. Sa istruktura, maaari kang magdagdag ng field ng trabaho na tatanggap ng tama o mali

Ang isang programa na may mababang priyoridad ay maaaring magsagawa ng pagkolekta ng basura at palayain ang memorya para sa mga walang laman na entry kung kinakailangan, ang mga katangian ng proteksyon ay maaaring mabago gamit ang function

BOOL virtualProtect(

LPVOID lpAdress,//

DWORD flNewProtect,//bagong katangian ng proteksyon

DWORD lpflOldProtect//

Bilang isang patakaran, ang mga pahina na hindi nagamit nang mahabang panahon ay pinaalis. Upang harangan ang mga pahina, gamitin ang function

LPVOID lpAdress,//

Bilang default, ang proseso ay maaaring mag-block ng maximum na 30 mga pahina kung higit pa ang kinakailangan, isang intermediate na aksyon ang ginagamit. Ang ViruaUnLock function ay ginagamit para sa pag-unlock. Kapag na-verify ang proseso, awtomatikong ia-unblock ang mga naka-block na page.

Bondarenko heap (lumilikha ng isang kahulugan ng inilalaan, pagkuha at pag-alis ng mga bloke)

microprocessor:Ang programmer ay nasa kanyang pagtatapon puwang ng address, limitado lamang sa bit na kapasidad ng address bus, anuman ang aktwal na kapasidad ng RAM ng computer at ang dami ng memory na ginagamit ng iba pang mga program na naproseso nang magkatulad sa isang multiprogram na computer.

Virtual memory, na nagbibigay ng kakayahan para sa programmer na ma-access ang napakalaking dami ng magkadikit na address space na ibinigay sa kanyang eksklusibong pagtatapon, ay may mga karaniwang katangian: byte addressing, oras ng pag-access na maihahambing sa oras ng pag-access sa RAM.

Sa lahat ng yugto ng paghahanda ng programa, kabilang ang pag-load sa memorya, programa lilitaw sa mga virtual na address, at kapag nagpapatupad lamang ng utos ng makina mga virtual na address ay na-convert sa mga pisikal. Para sa bawat programa na naisakatuparan sa multiprogram mode, ang sarili nito virtual na memorya. Ang bawat programa ay gumagamit ng pareho mga virtual na address mula sa zero hanggang sa pinakamalaki sa isang partikular na arkitektura.

Upang i-convert ang mga virtual na address sa pisikal na pisikal at virtual na memorya ay nahahati sa fixed-length na mga bloke na tinatawag mga pahina. Ang mga volume ng virtual at pisikal na mga pahina ay pareho. Ang mga pahina ng virtual at pisikal na memorya ay binibilang. Ang mga pahinang nawawala sa pisikal na memorya ay karaniwang nakaimbak sa panlabas na memorya. Ang nakapirming laki ng lahat ng mga pahina ay nagbibigay-daan sa iyo upang i-load ang anumang nais na virtual na pahina sa anumang pisikal na pahina.

Tulad ng nabanggit sa itaas, na may isang paged na representasyon ng memorya, ang virtual ( lohikal) address kumakatawan sa numero virtual na pahina at ang offset sa loob ng pahinang iyon. Sa turn, pisikal na address- ito ang numero pisikal na pahina at ang pag-aalis dito.

Mga panuntunan para sa pag-convert ng mga virtual na numero ng pahina sa mga numero pisikal na mga pahina karaniwang ibinibigay sa anyo ng talahanayan conversion ng pahina. Ang ganitong mga talahanayan ay nabuo ng sistema ng pamamahala ng memorya at binago sa bawat oras na ang memorya ay muling inilalaan. operating system patuloy na sinusubaybayan ang estado ng mga virtual na pahina ng isang partikular na programa at tinutukoy kung ito ay nasa RAM, at kung gayon, sa anong partikular na lokasyon. Ang mga application program ay hindi nakakaapekto sa proseso at maaaring gamitin ng lahat puwang ng address. Ang processor ay awtomatikong bumubuo ng isang espesyal na kaso ng hindi presensya kapag ang isang programa ay nag-access ng isang pahina na wala sa pisikal na memorya. Kapag pinangangasiwaan ang espesyal na kaso na ito, nilo-load ng OS ang hiniling na pahina mula sa panlabas na memorya, na opsyonal na nagpapadala ng iba pang pahina sa disk (proseso ng pagpapalit).

Ang pagsasalin ng mga virtual na address sa mga pisikal ay inilalarawan sa Fig. 3.12.

kanin. 3.12.

Tingnan natin ang isang halimbawa ng pagsasalin ng address virtual na pahina sa pisikal na pahina. Hayaan ang computer na gamitin puwang ng address, na kinabibilangan ng paging na may dami ng V pages = 1I, at may RAM V RAM = 3 pages. Hayaang tumakbo ang apat na programa nang sabay-sabay sa isang computer na mayroong sumusunod na bilang ng mga pahina: V A = 2, V B = 1, V C = 3, V D = 2. Ang paglipat sa pagitan ng mga programa ay nangyayari pagkatapos ng quantum time t k = 1. lead time bawat pahina ng anumang programa ay t = 2t k . Naniniwala kami na ang mga pahina ng programa ay na-load sa RAM kung kinakailangan at, kung maaari, sa mga libreng lugar ng RAM. Kung ang lahat ng memorya ay inookupahan, pagkatapos ay papalitan ng isang bagong pahina ang isa na hindi pa na-access sa pinakamahabang panahon.

Sa ilalim ng ganitong mga kondisyon, ang RAM load table at mga talahanayan conversion ng pahina para sa bawat programa ay magkakaroon ng form na ipinakita sa talahanayan. 3.2.

Sa talahanayan ng pamamahagi ng RAM, ang mga bilang ng mga pahinang aktibo sa isang naibigay na cycle ay naka-highlight. Sa mga mesa conversion ng pahina Ang mga gitling ay nagpapahiwatig ng mga sitwasyon kung saan ito virtual na pahina nawawala sa RAM.

| Isang halimbawa ng paglalaan ng memorya ng pahina sa isang multiprogram na computer | Pahina | |||||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Mga bar | ||||||||||||||||

| Dynamic na paglalaan ng memorya | RAM 0 | RAM 0 | RAM 0 | JSC | JSC | JSC | GAWIN | GAWIN | GAWIN | CO | CO | CO | CO | CO | CO | CO |

| 1 | C1 | C1 | C1 | B0 | B0 | B0 | A0 | A0 | A0 | D0 | D0 | D0 | D0 | D0 | D0 | |

| 2 | D1 | D1 | D1 | C1 | C1 | C1 | C0 | C0 | C0 | C0 | C0 | C0 | A1 | A1 | ||

| C2 conversion ng pahina mesa | ||||||||||||||||

| para sa programa A | 0 | 0 | - | - | 1 | 1 | 1 | - | - | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | 2 | 2 | 2 | 2 | 2 | 2 | - | - |

| C2 conversion ng pahina A 0 | ||||||||||||||||

| para sa programa B | - | 1 | 1 | 1 | - | 2 | 2 | 2 | - | - | - | - | - | - | - | - |

| C2 conversion ng pahina B 0 | ||||||||||||||||

| para sa programa C | - | - | 2 | 2 | 2 | - | 0 | 0 | 0 | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | - | - | - | - | - | - | - | - | - | - | - | - | - | - | 2 | 2 |

| C2 conversion ng pahina mula sa 0 | ||||||||||||||||

| para sa programa D | - | - | - | 0 | 0 | 0 | - | 1 | 1 | 1 | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | - | 1 | 1 | 1 | 1 | 1 | 1 |

D0 Kung ang bawat pahina ay may dami ng 1000 na addressable na mga cell, kung gayon, halimbawa, sa cycle 9, access sa virtual na address virtual na pahina 1100 program A ( 1, ang page offset ay 100) ay magreresulta sa isang tawag sa 2100 ( pisikal na address pisikal na pahina 2, offset in pisikal na pahina

kapareho ng sa virtual, iyon ay, 100). Isaalang-alang natin ngayon ang aplikasyon ng mga pangkalahatang prinsipyong ito pagsasalin ng address ng pahina V microprocessor

na may arkitektura ng IA-32 na may laki ng pahina na 4 KB. conversion ng pahina batayan linear na address, nakuha sa yugto ng pagbabago ng segment lohikal na address. nagsisilbing 32-bit Pag-convert ng pahina

Sa kasong ito, ang pinaka makabuluhang 20 bits linear na address naisakatuparan kapag ang PG bit value = 1 sa control register CR0. virtual na pahina aktwal na kumakatawan sa isang numero pisikal na pahina. Gayunpaman, sa isang direktang one-step na conversion ng numerong ito sa numero isang talahanayan ng 2 20 elemento ang kailangan, bawat 4 na byte ang haba (20-bit na numero ng pahina kasama ang ilang karagdagang impormasyon), ibig sabihin, 4 MB. Sa isang multiprogramming na kapaligiran, ang naturang talahanayan ay maaaring kailanganin para sa bawat gawain. Ang talahanayan na ito ay dapat na permanenteng naka-imbak sa RAM upang hindi makabuluhang madagdagan ang oras ng pagbuo pisikal na address

Sa halip, ang microprocessor ay gumagamit ng dalawang yugto pagsasalin ng address ng pahina. Ang root page, na tinatawag direktoryo ng talahanayan ng pahina(KTS), naglalaman ng 1024 32-bit elemento ng direktoryo ng talahanayan ng pahina(ECTS - Entry ng direktoryo ng pahina ng PDE). Ang bawat isa sa kanila ay tumutugon sa isang subordinate talahanayan ng pahina(TS), ibig sabihin, isang kabuuang hanggang 1024 ang pinapayagan mga subordinate na talahanayan mga pahina. Ang bawat talahanayan ng pahina ay naglalaman ng 1024 32-bit elemento ng talahanayan ng pahina(ETS - pahina ng PTE pagpasok sa mesa), na ang bawat isa ay tumutugon sa isang pisikal na pahina. Kaya, ang kabuuang bilang ng mga address pisikal na mga pahina katumbas ng 2 20, ibig sabihin, lahat ay virtual puwang ng address(4 KB * 2 20 elemento = 2 32 byte). Ang bawat talahanayan ay sumasakop sa 1024 * 4 = 4 KB, iyon ay, eksaktong 1 pahina. Kabuuang sukat ng mga talahanayan na ginamit para sa conversion ng pahina, hindi bumaba, ngunit bahagyang tumaas dahil sa paggamit ng direktoryo ng talahanayan ng pahina. Gayunpaman, una, halos palaging sa isang sistema ang laki na ito ay maaaring makabuluhang bawasan dahil sa ang katunayan na ang ilan mga linear na address ay hindi kailanman mabubuo (at ang impormasyong ito ay ibinigay mga talahanayan ng paglalarawan segment) at hindi kailangang gumawa ng page table para sa kanila. At pangalawa, tanging ang direktoryo ng talahanayan ng pahina at talahanayan ng pahina kasalukuyang tumatakbong programa. Pahinga mga talahanayan ng pahina maaaring pansamantalang maimbak sa panlabas na memorya.

kanin. 3.13.

Kaya, ang conversion ng isang linear na address sa isang pisikal ay may form na ipinapakita sa Fig. 3.13.

Pinakamataas na 20 digit linear na address ay nahahati sa dalawang 10-bit na field: field mga numero ng item ng page table catalog at patlang mga numero ng elemento ng talahanayan ng pahina. Since direktoryo ng talahanayan ng pahina, at bawat isa talahanayan ng pahina sumasakop ng eksaktong 1 pahina at nakahanay sa isang hangganan ng pahina, pagkatapos ay ang mababang-order na 12 bits ng kanilang base address ay zero, at upang matukoy ang kanilang isang talahanayan ng 2 20 elemento ang kailangan, bawat 4 na byte ang haba (20-bit na numero ng pahina kasama ang ilang karagdagang impormasyon), ibig sabihin, 4 MB. Sa isang multiprogramming na kapaligiran, ang naturang talahanayan ay maaaring kailanganin para sa bawat gawain. Ang talahanayan na ito ay dapat na permanenteng naka-imbak sa RAM upang hindi makabuluhang madagdagan ang oras ng pagbuo Ang isang 20-bit na field ay sapat.

Para sa direktoryo ng talahanayan ng pahina ang 20-bit address nito ay nasa rehistro ng kontrol CR3. Ang CTS ay permanenteng nasa memorya at hindi nakikilahok sa pagpapalit.

Pinakamataas na 20 digit isang talahanayan ng 2 20 elemento ang kailangan, bawat 4 na byte ang haba (20-bit na numero ng pahina kasama ang ilang karagdagang impormasyon), ibig sabihin, 4 MB. Sa isang multiprogramming na kapaligiran, ang naturang talahanayan ay maaaring kailanganin para sa bawat gawain. Ang talahanayan na ito ay dapat na permanenteng naka-imbak sa RAM upang hindi makabuluhang madagdagan ang oras ng pagbuo mga talahanayan ng pahina ay nakuha mula sa ETS. Ang mga istruktura ng elemento ng CTS at ang elemento ng TS ay magkatulad (Larawan 3.14).

kanin. 3.14.

Ang pinakamahalagang 20 bits ng elemento ay nagbibigay ng base address mga talahanayan ng pahina(sa ECTS) o pisikal na pahina(sa ETS). Ang P, A, R/W at U/S bits ay may ilang partikular na pagkakatulad sa mga segment na descriptor ay may mga partikular na layunin;