DAC na may pulse width modulation

Serial switched capacitor DAC

Mga parallel na DAC

DAC na may summation ng weight currents

DAC sa kasalukuyang mga mapagkukunan

Ang pagbuo ng output signal sa anyo ng boltahe

Parallel switched capacitor DAC

DAC na may pagsusuma ng boltahe

Mga Interface ng D/A Converter

Serial Input DAC

Parallel Input DAC

Aplikasyon ng DAC

Pangangasiwa ng mga pinirmahang numero

Mga multiplier at divider ng mga function

Mga attenuator at integrator sa mga DAC

Direktang digital signal synthesis system

Mga parameter ng DAC

Digital-to-analog converter

Ang isang digital-to-analog converter (DAC) ay idinisenyo upang i-convert ang isang numero, karaniwang tinutukoy bilang isang binary code, sa isang boltahe o kasalukuyang proporsyonal sa halaga ng digital code. Ang circuitry ng mga digital-to-analog converter ay lubhang magkakaibang. Sa Fig. Ipinapakita ng Figure 1 ang isang scheme ng pag-uuri ng DAC ayon sa mga katangian ng circuit nito. Bilang karagdagan, ang mga IC ng mga digital-to-analog converter ay inuri ayon sa sumusunod na pamantayan:

Sa pamamagitan ng uri ng output signal: na may kasalukuyang output at boltahe na output

Sa pamamagitan ng uri ng digital na interface: na may serial input at may parallel na input ng input code

Sa bilang ng mga DAC sa chip: single-channel at multi-channel

Sa bilis: katamtaman at mataas na bilis

kanin. 1. Pag-uuri ng DAC

DAC na may summation ng weight currents

Karamihan sa mga parallel na DAC circuit ay nakabatay sa kabuuan ng mga alon, ang lakas ng bawat isa ay proporsyonal sa bigat ng digital binary bit, at tanging ang mga bit na alon na ang halaga ay katumbas ng 1 ay dapat isama Halimbawa, ipagpalagay na gusto mo upang i-convert ang isang apat na bit na binary code sa isang analog kasalukuyang signal. Ang bigat ng ikaapat, pinaka makabuluhang digit (MSB) ay 2 3 =8, ang ikatlong digit ay 2 2 =4, ang pangalawa ay 2 1 =2, at ang hindi bababa sa makabuluhang digit ay 2 0 =1. Kung ang bigat ng MZR ako MZR =1 mA, pagkatapos ako SZR =8 mA, at ang pinakamataas na kasalukuyang output ng converter ako output max = 15 mA at tumutugma sa code 1111 2. Ito ay malinaw na ang code 1001 2, halimbawa, ay tumutugma sa ako out = 9 mA, atbp. Dahil dito, kinakailangan na bumuo ng isang circuit na nagsisiguro sa pagbuo at paglipat ng tumpak na pagtimbang ng mga alon ayon sa ibinigay na mga batas. Ang pinakasimpleng diagram na nagpapatupad ng prinsipyong ito ay ipinapakita sa Fig. 3.

SA  Ang mga resistensya ng mga resistors ay pinili upang kapag ang mga switch ay sarado, ang isang kasalukuyang naaayon sa bigat ng paglabas ay dumadaloy sa kanila. Dapat na sarado ang susi kapag ang katumbas na bit ng input word ay katumbas ng isa. Ang kasalukuyang output ay tinutukoy ng kaugnayan

Ang mga resistensya ng mga resistors ay pinili upang kapag ang mga switch ay sarado, ang isang kasalukuyang naaayon sa bigat ng paglabas ay dumadaloy sa kanila. Dapat na sarado ang susi kapag ang katumbas na bit ng input word ay katumbas ng isa. Ang kasalukuyang output ay tinutukoy ng kaugnayan ![]()

Sa isang mataas na bit na kapasidad ng DAC, ang kasalukuyang-setting resistors ay dapat na tumugma sa mataas na katumpakan. Ang pinaka mahigpit na mga kinakailangan sa katumpakan ay ipinapataw sa mga resistor ng pinakamataas na mga numero, dahil ang pagkalat ng mga alon sa kanila ay hindi dapat lumampas sa kasalukuyang ng mababang-order na digit. Samakatuwid, ang paglaban ay kumalat sa k-th digit ay dapat na mas mababa sa

R/R=2 – k

Mula sa kondisyong ito ay sumusunod na ang pagkalat ng paglaban ng risistor, halimbawa, sa ikaapat na digit ay hindi dapat lumampas sa 3%, at sa ika-10 na digit - 0.05%, atbp.

Ang itinuturing na pamamaraan, para sa lahat ng pagiging simple nito, ay may isang buong grupo ng mga disadvantages. Una, para sa iba't ibang mga input code, ang kasalukuyang natupok mula sa reference voltage source (RPS) ay magiging iba, at ito ay makakaapekto sa halaga ng output voltage RES. Pangalawa, ang mga halaga ng paglaban ng mga resistor ng timbang ay maaaring mag-iba ng libu-libong beses, at ito ay napakahirap na ipatupad ang mga resistor na ito sa mga semiconductor IC. Bilang karagdagan, ang paglaban ng mga high-order na resistors sa mga multi-bit na DAC ay maaaring maihambing sa paglaban ng saradong switch, at ito ay hahantong sa isang error sa conversion. Pangatlo, sa circuit na ito, ang makabuluhang boltahe ay inilalapat sa mga bukas na switch, na nagpapalubha sa kanilang pagtatayo.

Ang mga pagkukulang na ito ay inalis sa AD7520 DAC circuit (domestic analogue ng 572PA1), na binuo ng Analog Devices noong 1973, na ngayon ay mahalagang pamantayan sa industriya (maraming mga serial DAC na modelo ang ginawa ayon dito). Ang ipinahiwatig na diagram ay ipinapakita sa Fig. 4. Ang mga MOS transistors ay ginagamit dito bilang mga switch.

kanin. 4. DAC circuit na may mga switch at pare-pareho ang impedance matrix

Sa circuit na ito, ang pagtatakda ng mga weighting coefficient ng mga yugto ng converter ay isinasagawa sa pamamagitan ng sunud-sunod na paghahati ng reference na boltahe gamit ang isang resistive matrix ng pare-pareho ang impedance. Ang pangunahing elemento ng naturang matrix ay isang boltahe divider (Larawan 5), na dapat matugunan ang sumusunod na kondisyon: kung ito ay puno ng paglaban R n, pagkatapos ay ang input impedance nito R dapat ding kunin ng inx ang halaga R n. Chain weakening coefficient = U 2 /U 1 sa load na ito ay dapat may tinukoy na halaga. Kapag natugunan ang mga kundisyong ito, nakukuha namin ang mga sumusunod na expression para sa mga pagtutol:

alinsunod sa Fig. 4.

Dahil sa anumang posisyon ng mga switch S k ikinonekta nila ang mas mababang mga terminal ng mga resistors sa karaniwang circuit bus, ang reference na mapagkukunan ng boltahe ay puno ng isang pare-pareho na impedance ng input R sa = R. Tinitiyak nito na ang reference na boltahe ay nananatiling hindi nagbabago para sa anumang DAC input code.

Ayon sa Fig. 4, ang output currents ng circuit ay tinutukoy ng mga relasyon

|

|

|

|

at ang kasalukuyang input

|

|

Dahil ang mas mababang mga terminal ng resistors 2 R matrice para sa anumang switch state S k konektado sa karaniwang circuit bus sa pamamagitan ng mababang pagtutol ng mga saradong switch, ang mga boltahe sa mga switch ay palaging maliit, sa loob ng ilang millivolts. Pinapasimple nito ang pagbuo ng mga switch at control circuit at pinapayagan ang paggamit ng mga reference na boltahe mula sa isang malawak na hanay, kabilang ang iba't ibang mga polaridad. Dahil ang kasalukuyang output ng DAC ay nakasalalay sa U op linear (tingnan ang (8)), ang mga converter ng ganitong uri ay maaaring gamitin upang i-multiply ang isang analog signal (paglalapat nito sa reference na input ng boltahe) sa pamamagitan ng isang digital code. Ang mga naturang DAC ay tinatawag pagpaparami(MDAC).

Ang katumpakan ng circuit na ito ay nababawasan ng katotohanan na para sa mga high-bit na DAC, kinakailangan upang tumugma sa paglaban R 0 switch na may discharge currents. Ito ay lalong mahalaga para sa mga high-order na key. Halimbawa, sa 10-bit AD7520 DAC, ang mga pangunahing MOSFET ng anim na pinakamahalagang bit ay ginawang iba sa lugar at ang kanilang resistensya R 0 ay tumataas ayon sa binary code (20, 40, 80, ..., 640 Ohm). Sa ganitong paraan, ang pagbaba ng boltahe sa mga switch ng unang anim na bit ay equalized (hanggang sa 10 mV), na nagsisiguro ng monotonicity at linearity ng DAC transient response. Ang 12-bit na DAC 572PA2 ay may differential nonlinearity na hanggang 0.025% (1 LSB).

Aplikasyon

Ang DAC ay ginagamit sa tuwing kinakailangan upang i-convert ang isang signal mula sa isang digital na representasyon sa isang analogue, halimbawa, sa mga CD player (Audio CD).

Mga uri ng DAC

Ang pinakakaraniwang uri ng mga electronic DAC ay:

- Pulse width modulator- ang pinakasimpleng uri ng DAC. Ang isang matatag na pinagmumulan ng kasalukuyang o boltahe ay pana-panahong naka-on para sa isang oras na proporsyonal sa digital code na kino-convert, pagkatapos ay ang resultang pulse sequence ay sinasala ng isang analog low-pass na filter. Ang pamamaraang ito ay kadalasang ginagamit upang kontrolin ang bilis ng mga de-koryenteng motor, at nagiging popular din sa Hi-Fi audio equipment;

- Oversampling DAC, tulad ng mga delta-sigma DAC, ay batay sa variable pulse density. Nagbibigay-daan sa iyo ang oversampling na gumamit ng DAC na may mas mababang bit depth upang makamit ang mas mataas na bit depth ng huling conversion; Kadalasan ang isang delta-sigma DAC ay itinayo batay sa isang simpleng one-bit na DAC, na halos linear. Ang isang low-bit na DAC ay tumatanggap ng pulse signal na may pulso density modulated(na may pare-parehong tagal ng pulso, ngunit may variable na duty cycle), na nilikha gamit ang negatibong feedback. Ang negatibong feedback ay gumaganap bilang isang high-pass na filter para sa quantization noise.

- Uri ng pagtimbang DAC, kung saan ang bawat bit ng na-convert na binary code ay tumutugma sa isang risistor o kasalukuyang pinagmumulan na konektado sa isang karaniwang summation point. Ang pinagmulan ng kasalukuyang (conductivity ng risistor) ay proporsyonal sa bigat ng bit kung saan ito tumutugma. Kaya, ang lahat ng di-zero bits ng code ay idinagdag sa timbang. Ang pamamaraan ng pagtimbang ay isa sa pinakamabilis, ngunit ito ay nailalarawan sa mababang katumpakan dahil sa pangangailangan para sa isang hanay ng maraming iba't ibang mga mapagkukunan ng katumpakan o resistors at variable impedance. Para sa kadahilanang ito, ang pagtimbang ng mga DAC ay may maximum na lapad na walong bits;

- Hagdan DAC(chain R-2R circuit). Sa R-2R-DAC, ang mga halaga ay nilikha sa isang espesyal na circuit na binubuo ng mga resistors na may mga resistensya R At 2R, na tinatawag na pare-pareho ang impedance matrix, na may dalawang uri ng pagsasama: direktang - kasalukuyang matrix at kabaligtaran - boltahe matrix. Ang paggamit ng magkatulad na resistors ay maaaring makabuluhang mapabuti ang katumpakan kumpara sa isang maginoo na pagtimbang ng DAC, dahil ito ay medyo simple upang makabuo ng isang hanay ng mga elemento ng katumpakan na may parehong mga parameter. Ang mga DAC ng uri ng R-2R ay nagbibigay-daan sa iyo na itulak pabalik ang mga limitasyon sa bit depth. Sa laser trimming ng mga resistors sa isang substrate, ang isang katumpakan ng 20-22 bits ay nakamit. Karamihan sa oras ng conversion ay ginugugol sa operational amplifier, kaya dapat ito ay mas mabilis hangga't maaari. Ang bilis ng DAC ay ilang microseconds o mas kaunti (iyon ay, nanoseconds);

Mga katangian

Ang mga DAC ay matatagpuan sa simula ng analog path ng anumang system, kaya ang mga parameter ng DAC ay higit na tinutukoy ang mga parameter ng buong system sa kabuuan. Ang mga sumusunod ay ang pinakamahalagang katangian ng isang DAC.

- Pinakamataas na sampling rate- ang pinakamataas na dalas kung saan maaaring gumana ang DAC, na gumagawa ng tamang resulta sa output. Ayon sa Nyquist-Shannon theorem (kilala rin bilang Kotelnikov theorem), upang wastong makagawa ng analog signal mula sa isang digital form, ang sampling frequency ay dapat na hindi bababa sa dalawang beses ang maximum frequency sa signal spectrum. Halimbawa, upang kopyahin ang buong saklaw ng dalas ng audio na naririnig ng tao, ang spectrum nito ay umaabot hanggang 20 kHz, kinakailangan na ang signal ng audio ay ma-sample sa dalas na hindi bababa sa 40 kHz. Itinatakda ng pamantayang Audio CD ang audio sampling rate sa 44.1 kHz; Upang muling gawin ang signal na ito kakailanganin mo ng isang DAC na may kakayahang gumana sa dalas na ito. Ang murang computer sound card ay may sampling rate na 48 kHz. Ang mga signal na na-sample sa iba pang mga frequency ay na-resampling sa 48 kHz, na bahagyang nagpapababa sa kalidad ng signal.

- Monotone- ang kakayahan ng DAC na taasan ang analog output signal kapag tumaas ang input code.

- THD+N(kabuuang harmonic distortion + ingay) - isang sukatan ng distortion at ingay na ipinakilala sa signal ng DAC. Ipinahayag bilang isang porsyento ng harmonic power at ingay sa output signal. Isang mahalagang parameter para sa mga small-signal na DAC application.

- Dynamic na hanay- ang ratio ng pinakamalaki at pinakamaliit na signal na maaaring kopyahin ng DAC, na ipinahayag sa mga decibel. Ang parameter na ito ay nauugnay sa bit depth at noise threshold.

- Mga static na katangian:

- DNL (differential nonlinearity) - nailalarawan kung gaano kalaki ang pagkakaiba ng analog signal increment na nakuha sa pamamagitan ng pagtaas ng code ng 1 least significant bit (LSB) sa tamang halaga;

- INL (integral nonlinearity) - nailalarawan kung gaano naiiba ang katangian ng paglipat ng DAC mula sa perpektong isa. Ang perpektong katangian ay mahigpit na linear; Ipinapakita ng INL kung gaano kalayo ang boltahe sa output ng DAC para sa isang ibinigay na code mula sa linear na katangian; ipinahayag sa minimum na sahod;

- makakuha;

- pagkiling.

- Mga katangian ng dalas:

- SNDR (signal-to-noise ratio + distortion) - nailalarawan sa decibel ang ratio ng output signal power sa kabuuang lakas ng ingay at harmonic distortion;

- HDi (i-th harmonic coefficient) - nailalarawan ang ratio ng i-th harmonic sa pangunahing harmonic;

- Ang THD (harmonic distortion factor) ay ang ratio ng kabuuang kapangyarihan ng lahat ng harmonics (maliban sa una) sa kapangyarihan ng unang harmonic.

Tingnan din

Panitikan

- Jean M. Rabai, Anantha Chandrakasan, Borivozh Nikolic. Mga digital integrated circuit. Paraan ng Disenyo = Digital Integrated Circuits. - 2nd ed. - M.: Williams, 2007. - 912 p. - ISBN 0-13-090996-3

- Mingliang Liu. Demystifying Switched-Capacitor Circuits. ISBN 0-75-067907-7.

- Phillip E. Allen, Douglas R. Holberg. CMOS Analog Circuit Design. ISBN 0-19-511644-5.

Mga link

- Digital-to-analog converters (DACs), theory at operating principles sa website ng Microelectronics Market

- Mga digital-to-analog na converter para sa mga digital signal processing application

- Ipinapaliwanag ng Mga Pagsukat ng INL/DNL para sa mga High-Speed ADC kung paano kinakalkula ang INL at DNL

- Alexey Stakhov. Fibonacci Computer Part 1, Part 2, Part 3 // PCweek.ru, 2002

- Ipinaliwanag ng R-2R Ladder DAC na naglalaman ng mga schematics

| Mga microcontroller | |||||

|---|---|---|---|---|---|

| Arkitektura |

| ||||

Lektura Blg. 3

"Analog-to-digital at digital-to-analog na conversion."

Sa mga microprocessor system, ang papel ng isang pulse element ay ginagampanan ng isang analog-to-digital converter (ADC), at ang papel ng isang extrapolator ay ginagampanan ng isang digital-to-analog converter (DAC).

Analogue sa Digital Conversion binubuo ng pag-convert ng impormasyong nasa isang analog signal sa isang digital code . Digital-to-analog na conversion ay idinisenyo upang maisagawa ang kabaligtaran na gawain, i.e. i-convert ang isang numero na kinakatawan bilang isang digital code sa isang katumbas na analog signal.

Ang mga ADC, bilang panuntunan, ay naka-install sa mga circuit ng feedback ng mga digital control system upang i-convert ang mga analog feedback signal sa mga code na nakikita ng digital na bahagi ng system. yun. Ang mga ADC ay gumaganap ng ilang function, gaya ng: time sampling, level quantization, encoding. Ang isang pangkalahatang block diagram ng ADC ay ipinapakita sa Fig. 3.1.

Ang isang signal sa anyo ng kasalukuyang o boltahe ay ibinibigay sa input ng ADC, na binibilang ayon sa antas sa panahon ng proseso ng conversion. Ang perpektong static na katangian ng isang 3-bit ADC ay ipinapakita sa Fig. 3.2.

|

Ang mga signal ng input ay maaaring tumagal ng anumang halaga sa saklaw mula sa - Umax kay Umax , at ang mga output ay tumutugma sa walong (2 3) discrete level. Ang halaga ng input boltahe kung saan ang isang paglipat ay nangyayari mula sa isang halaga ng ADC output code patungo sa isa pang katabing halaga ay tinatawag boltahe ng paglipat ng intercode. Ang pagkakaiba sa pagitan ng dalawang magkatabing halaga ng mga transisyon ng intercode ay tinatawag hakbang ng quantization o yunit ng hindi bababa sa makabuluhang bit (LSB).Ang panimulang punto ng mga katangian ng pagbabago ay ang punto na tinukoy ng halaga ng input signal, na tinukoy bilang

![]() (3.1),

(3.1),

kung saan ang U 0.1 – boltahe ng unang intercode transition, U LSB - hakbang ng quantization ( LSB – Least Significant Bit ).

![]() (3.2).

(3.2).

ang conversion ay tumutugma sa input boltahe na tinutukoy ng kaugnayan Ang saklaw ng boltahe ng input ng ADC ay limitado sa U 0.1 at U N-1,N tinawag.

(3.3).

saklaw ng boltahe ng input Saklaw ng boltahe ng input at halaga ng LSB N

(3.4).

-bit ADC at DAC ay konektado sa pamamagitan ng ratio

(3.5)

U 0.1 at U N-1,N Boltahe ( buong sukat na boltahe FSR – Buong Saklaw na Saklaw

(3.6),

). Karaniwan, ang parameter na ito ay tinutukoy ng antas ng output ng reference na pinagmumulan ng boltahe na konektado sa ADC. Ang laki ng quantization step o unit ng hindi bababa sa makabuluhang digit i.e. katumbas ng

![]() (3.7).

(3.7).

at ang halaga ng yunit ng pinakamahalagang digit Tulad ng makikita mula sa Fig. 3.2, sa panahon ng proseso ng conversion, ang isang error ay nangyayari na hindi lalampas sa kalahati ng halaga ng hindi bababa sa makabuluhang bit.

U LSB /2. Mayroong iba't ibang mga paraan ng analog-to-digital na conversion, na naiiba sa katumpakan at bilis. Sa karamihan ng mga kaso, ang mga katangiang ito ay magkasalungat sa isa't isa. Sa kasalukuyan, ang mga uri ng mga nagko-convert gaya ng mga ADC ng sunud-sunod na pagtatantya (bitwise balancing), pagsasama-sama ng mga ADC, parallel ( Flash

) ADC, “sigma-delta” ADC, atbp.

Ang mga pangunahing elemento ng device ay isang comparator (K), isang digital-to-analog converter (DAC) at isang logic control circuit. Ang prinsipyo ng conversion ay batay sa isang sunud-sunod na paghahambing ng antas ng signal ng input na may mga antas ng signal na naaayon sa iba't ibang kumbinasyon ng output code at ang pagbuo ng resultang code batay sa mga resulta ng mga paghahambing. Ang pagkakasunud-sunod ng mga inihambing na code ay nakakatugon sa panuntunan ng halves. Sa simula ng conversion, ang DAC input code ay nakatakda sa isang estado kung saan ang lahat ng mga bit maliban sa pinakamahalaga ay 0, at ang pinakamahalaga ay 1. Sa kumbinasyong ito, ang isang boltahe na katumbas ng kalahati ng saklaw ng boltahe ng input ay nabuo sa ang output ng DAC. Ang boltahe na ito ay inihambing sa input boltahe sa comparator. Kung ang input signal ay mas malaki kaysa sa signal na nagmumula sa DAC, kung gayon ang pinaka makabuluhang bit ng output code ay nakatakda sa 1, kung hindi, ito ay ire-reset sa 0. Sa susunod na clock cycle, ang code na bahagyang nabuo sa paraang ito ay muli. natanggap sa input ng DAC, ang susunod na bit ay nakatakda sa isa at ang paghahambing ay nauulit mismo. Nagpapatuloy ang proseso hanggang sa maikumpara ang hindi bababa sa makabuluhang bit. yun. upang bumuo Saklaw ng boltahe ng input at halaga ng LSB -bit na output code na kinakailangan Saklaw ng boltahe ng input at halaga ng LSB magkaparehong mga siklo ng paghahambing sa elementarya. Nangangahulugan ito na, ang iba pang mga bagay ay pantay, ang pagganap ng naturang ADC ay bumababa habang tumataas ang bit capacity nito. Ang mga panloob na elemento ng sunud-sunod na approximation ADC (DAC at comparator) ay dapat na may katumpakan na mas mahusay kaysa sa kalahati ng hindi bababa sa makabuluhang bit ng ADC.

Block diagram ng parallel ( Mayroong iba't ibang mga paraan ng analog-to-digital na conversion, na naiiba sa katumpakan at bilis. Sa karamihan ng mga kaso, ang mga katangiang ito ay magkasalungat sa isa't isa. Sa kasalukuyan, ang mga uri ng mga nagko-convert gaya ng mga ADC ng sunud-sunod na pagtatantya (bitwise balancing), pagsasama-sama ng mga ADC, parallel ( ) Ang ADC ay ipinapakita sa Fig. 3.4.

Sa kasong ito, ang input boltahe ay ibinibigay para sa paghahambing sa mga input ng parehong pangalan kaagad Saklaw ng boltahe ng input at halaga ng LSB -1 kumpare. Ang mga kabaligtaran na input ng mga comparator ay binibigyan ng mga signal mula sa isang high-precision na divider ng boltahe, na konektado sa isang reference na pinagmulan ng boltahe. Sa kasong ito, ang mga boltahe mula sa mga output ng divider ay pantay na ipinamamahagi kasama ang buong hanay ng mga pagbabago sa signal ng input. Ang priyoridad na encoder ay bumubuo ng isang digital na output signal na naaayon sa pinakamataas na comparator na may output signal na naka-activate. yun. para masiguro Saklaw ng boltahe ng input at halaga ng LSB -kailangan ng bit na conversion 2 N divider resistors at 2 N -1 tagapaghambing. Isa ito sa pinakamabilis na paraan ng conversion. Gayunpaman, na may malaking kapasidad ay nangangailangan ito ng malalaking gastos sa hardware. Ang katumpakan ng lahat ng divider at comparator resistors ay dapat na mas mahusay kaysa sa kalahati ng halaga ng LSB.

Ang block diagram ng double integration ADC ay ipinapakita sa Fig. 3.5.

|

Ang mga pangunahing elemento ng system ay isang analog switch na binubuo ng mga susi TK 1, TK 2, TK 3, integrator I, comparator K at counter C. Ang proseso ng conversion ay binubuo ng tatlong yugto (Larawan 3.6).

|

Sa unang yugto ang susi ay sarado S.W. 1, at ang natitirang mga key ay bukas. Sa pamamagitan ng saradong susi S.W. 1, ang input boltahe ay inilalapat sa isang integrator, na nagsasama ng input signal sa isang nakapirming agwat ng oras. Pagkatapos ng agwat ng oras na ito, ang antas ng signal ng output ng integrator ay proporsyonal sa halaga ng signal ng input. Sa ikalawang yugto ng pagbabago, ang susi S.W. 1 bumukas at ang susi S.W. 2 ay nagsasara, at isang senyales mula sa reference na pinagmumulan ng boltahe ay ibinibigay sa input ng integrator. Ang kapasitor ng integrator ay pinalabas mula sa boltahe na naipon sa unang pagitan ng conversion sa isang pare-parehong rate na proporsyonal sa boltahe ng sanggunian. Ang yugtong ito ay nagpapatuloy hanggang ang integrator output boltahe ay bumaba sa zero, tulad ng ipinahiwatig ng output ng comparator, na naghahambing sa integrator signal sa zero. Ang tagal ng ikalawang yugto ay proporsyonal sa input boltahe ng converter. Sa buong ikalawang yugto, ang mga high-frequency pulse na may naka-calibrate na frequency ay ipinapadala sa counter. yun. pagkatapos ng ikalawang yugto, ang mga digital meter reading ay proporsyonal sa input boltahe. Gamit ang pamamaraang ito, ang napakahusay na katumpakan ay maaaring makamit nang hindi naglalagay ng mataas na pangangailangan sa katumpakan at katatagan ng mga bahagi. Sa partikular, ang katatagan ng integrator capacitance ay maaaring hindi mataas, dahil ang mga cycle ng charge at discharge ay nangyayari sa isang rate na inversely proportional sa capacitance. Bukod dito, ang comparator drift at offset error ay binabayaran sa pamamagitan ng pagsisimula at pagtatapos ng bawat hakbang ng conversion sa parehong boltahe. Upang mapabuti ang katumpakan, ang ikatlong yugto ng conversion ay ginagamit, kapag ang integrator ay nag-input sa pamamagitan ng isang susi S.W. 3 isang zero signal ang ibinibigay. Dahil ang parehong integrator at comparator ay ginagamit sa hakbang na ito, ang pagbabawas ng output error value sa zero mula sa kasunod na pagsukat ay nagreresulta sa kabayaran para sa mga error na nauugnay sa mga sukat na malapit sa zero. Ang mga mahigpit na kinakailangan ay hindi ipinapataw kahit na sa dalas ng mga pulso ng orasan na dumarating sa counter, dahil isang nakapirming agwat ng oras sa unang yugto ng conversion ay nabuo mula sa parehong mga pulso. Ang mga mahigpit na kinakailangan ay ipinapataw lamang sa kasalukuyang discharge, i.e. sa reference na pinagmumulan ng boltahe. Ang kawalan ng paraan ng conversion na ito ay ang mababang pagganap nito.

Ang mga ADC ay nailalarawan sa pamamagitan ng isang bilang ng mga parameter na ginagawang posible na pumili ng isang partikular na aparato batay sa mga kinakailangan para sa system. Ang lahat ng mga parameter ng ADC ay maaaring nahahati sa dalawang grupo: static at dynamic. Tinutukoy ng una ang mga katangian ng katumpakan ng device kapag nagtatrabaho nang may pare-pareho o dahan-dahang pagbabago ng input signal, at ang huli ay nagpapakilala sa pagganap ng device bilang pagpapanatili ng katumpakan habang tumataas ang dalas ng input signal.

Ang antas ng quantization na nasa paligid ng zero ng input signal ay tumutugma sa inter-code transition voltages na -0.5 U LSB at 0.5 U LSB (ang una ay nangyayari lamang sa kaso ng isang bipolar input signal). Gayunpaman, sa mga totoong device, ang mga intercode na transisyon na boltahe na ito ay maaaring magkaiba sa mga ideal na halagang ito. Ang paglihis ng mga aktwal na antas ng mga boltahe ng paglipat ng intercode na ito mula sa kanilang mga ideal na halaga ay tinatawag bipolar zero offset error ( Bipolar Zero Error ) At unipolar zero offset error ( Zero Offset Error ) ayon sa pagkakabanggit. Para sa mga saklaw ng bipolar na conversion, kadalasang ginagamit ang zero offset na error, at para sa mga unipolar na hanay ng conversion, kadalasang ginagamit ang unipolar offset error. Ang error na ito ay humahantong sa isang parallel shift ng tunay na katangian ng pagbabagong-anyo na may kaugnayan sa perpektong katangian kasama ang abscissa axis (Larawan 3.7).

|

Paglihis ng antas ng signal ng input na tumutugma sa huling paglipat ng intercode mula sa perpektong halaga nito U FSR -1.5 U LSB , tinawag buong sukat na error ( Error sa Buong Scale).

ratio ng conversion ng ADC ay tinatawag na padaplis ng anggulo ng pagkahilig ng tuwid na linya na iginuhit sa simula at pagtatapos na mga punto ng tunay na katangian ng pagbabago. Ang pagkakaiba sa pagitan ng aktwal at perpektong mga halaga ng koepisyent ng conversion ay tinatawag error sa conversion factor ( Makakuha ng Error ) (Larawan 3.7) Kabilang dito ang mga error sa dulo ng sukat, ngunit hindi kasama ang mga error sa zero ng sukat. Para sa unipolar range ito ay tinukoy bilang ang pagkakaiba sa pagitan ng full scale error at unipolar zero offset error, at para sa bipolar range ito ay tinukoy bilang ang pagkakaiba sa pagitan ng full scale error at bipolar zero offset error. Sa katunayan, sa anumang kaso, ito ay isang paglihis ng perpektong distansya sa pagitan ng huli at unang intercode transition (katumbas ng U FSR -2 U LSB ) mula sa tunay na halaga nito.

Maaaring mabayaran ang zero offset at gain error sa pamamagitan ng pagsasaayos sa ADC preamplifier. Upang gawin ito, kailangan mong magkaroon ng isang voltmeter na may katumpakan na hindi mas masahol pa kaysa sa 0.1 U LSB . Upang matiyak ang kalayaan ng dalawang error na ito, itama muna ang zero offset error at pagkatapos ay ang conversion coefficient error.Upang itama ang ADC zero offset error, kailangan mong:

1. Itakda ang input boltahe nang eksakto sa 0.5 U LSB;

2. Ayusin ang ADC pre-amplifier offset hanggang sa lumipat ang ADC sa estado na 00…01.

Upang itama ang error ng conversion factor ito ay kinakailangan:

1. Itakda ang input boltahe nang eksakto sa antas U FSR -1.5 U LSB ;

2. Ayusin ang gain ng ADC pre-amplifier hanggang sa lumipat ang ADC sa state 11…1.

Dahil sa di-kasakdalan ng mga elemento ng ADC circuit, ang mga hakbang sa iba't ibang punto ng mga katangian ng ADC ay naiiba sa bawat isa sa magnitude at hindi pantay. U LSB (Larawan 3.8).

|

Ang paglihis ng distansya sa pagitan ng mga midpoint ng dalawang magkatabing real quantization na hakbang mula sa ideal na halaga ng quantization step U LSB tinawag pagkakaibang nonlinearity (DNL – Differential Nonlinearity). Kung DNL mas malaki kaysa o katumbas ng U LSB , kung gayon ang ADC ay maaaring may tinatawag na "mga nawawalang code" (Larawan 3.3). Ito ay nangangailangan ng isang lokal na matalim na pagbabago sa ADC transmission coefficient, na sa mga closed-loop control system ay maaaring humantong sa pagkawala ng katatagan.

Para sa mga application na iyon kung saan mahalagang mapanatili ang output signal na may ibinigay na katumpakan, mahalagang tumugma ang mga ADC output code sa mga inter-code na boltahe ng transition nang mas malapit hangga't maaari. Ang pinakamataas na paglihis ng gitna ng hakbang ng quantization sa tunay na katangian ng ADC mula sa linearized na katangian ay tinatawag integral nonlinearity (INL – Integral Nonlinearity) orelatibong katumpakan (Relative Accuracy) ADC (Larawan 3.9).

|

Ang linearized na katangian ay iginuhit sa pamamagitan ng mga matinding punto ng tunay na katangian ng pagbabago, pagkatapos na ma-calibrate ang mga ito, i.e. Ang zero offset at conversion factor na error ay inalis na.

Halos imposibleng mabayaran ang mga pagkakamali sa kaugalian at integral na nonlinearity gamit ang mga simpleng paraan.

Resolusyon ng ADC ( Resolusyon ) ay ang kapalit ng maximum na bilang ng mga kumbinasyon ng code sa output ng ADC

(3.8).

Tinutukoy ng parameter na ito kung anong pinakamababang antas ng signal ng input (na may kaugnayan sa buong signal ng amplitude) na maaaring makita ng ADC.

Ang katumpakan at paglutas ay dalawang malayang katangian. Ang Resolution ay gumaganap ng isang mapagpasyang papel kapag ito ay mahalaga upang magbigay ng isang ibinigay na dynamic na hanay ng input signal. Ang katumpakan ay kritikal kapag kinakailangan upang mapanatili ang kinokontrol na variable sa isang naibigay na antas na may isang nakapirming katumpakan.

Dynamic na hanay ng ADC (DR - Dynamic na Saklaw ) ay ang ratio ng pinakamataas na pinaghihinalaang antas ng boltahe ng input sa pinakamababa, na ipinahayag sa dB

![]() (3.9).

(3.9).

Tinutukoy ng parameter na ito ang maximum na dami ng impormasyon na kayang ipadala ng ADC. Kaya, para sa isang 12-bit ADC DR =72 dB.

Ang mga katangian ng mga totoong ADC ay naiiba sa mga katangian ng mga ideal na device dahil sa mga hindi perpektong elemento ng tunay na device. Isaalang-alang natin ang ilang mga parameter na nagpapakilala sa mga tunay na ADC.

Signal-to-noise ratio(SNR – Signal to Noise Ratio ) ay ang ratio ng rms value ng input sinusoidal signal sa rms value ng ingay, na tinukoy bilang kabuuan ng lahat ng iba pang spectral na bahagi hanggang sa kalahati ng sampling frequency, hindi kasama ang DC component. Para sa perpekto Saklaw ng boltahe ng input at halaga ng LSB -bit ADC na bumubuo lamang ng ingay ng quantization SNR , na ipinahayag sa mga decibel, ay maaaring tukuyin bilang

(3.10),

(3.10),

kung saan si N – ADC bit na kapasidad. Kaya, para sa isang 12-bit na perpektong ADC SNR =74 dB. Ang halagang ito ay mas malaki kaysa sa dynamic na hanay ng parehong ADC dahil Ang pinakamababang antas ng nakikitang signal ay dapat na mas mataas kaysa sa antas ng ingay. Isinasaalang-alang lamang ng formula na ito ang ingay ng quantization at hindi isinasaalang-alang ang iba pang pinagmumulan ng ingay na umiiral sa mga totoong ADC. Samakatuwid, ang mga halaga SNR para sa mga tunay na ADC ito ay karaniwang mas mababa kaysa sa ideal. Karaniwang halaga SNR para sa isang tunay na 12-bit ADC ay 68-70 dB.

Kung ang input signal ay may mas kaunting swing U FSR , pagkatapos ay kailangang ayusin ang huling formula

(3.11),

kung saan ang KOS ay ang pagpapalambing ng input signal, na ipinahayag sa dB. Kaya, kung ang input signal ng isang 12-bit ADC ay may amplitude na 10 beses na mas mababa sa kalahati ng buong sukat na boltahe, kung gayon ang KOS = -20 dB at SNR =74 dB – 20 dB = 54 dB.

Tunay na halaga SNR maaaring gamitin para sa pagtukoy ng epektibong bilang ng mga bits ng ADC( ENOB – Epektibong Bilang ng mga Bit ). Ito ay tinutukoy ng formula

![]() (3.12).

(3.12).

Ang tagapagpahiwatig na ito ay maaaring makilala ang aktwal na mapagpasyang kakayahan ng isang tunay na ADC Kaya, isang 12-bit na ADC kung saan SNR =68 dB para sa isang signal na may KOS = -20 dB ay talagang 7-bit ( ENOB =7.68). halaga ng ENOB malakas na nakasalalay sa dalas ng input signal, i.e. Ang epektibong bit capacity ng ADC ay bumababa sa pagtaas ng dalas.

Kabuuang harmonic distortion ( THD – Total Harmonic Distortion ) ay ang ratio ng kabuuan ng mga halaga ng root-mean-square ng lahat ng mas mataas na harmonic sa root-mean-square na halaga ng pangunahing harmonic

(3.13),

(3.13),

saan n karaniwang limitado sa antas 6 o 9. Ang parameter na ito ay nagpapakilala sa antas ng harmonic distortion ng ADC output signal kumpara sa input. THD tumataas sa dalas ng input signal.

Buong power frequency band ( FPBW – Full Power Bandwidth ) ay ang pinakamataas na peak-to-peak frequency ng input signal kung saan ang amplitude ng reconstructed na pangunahing bahagi ay bumaba nang hindi hihigit sa 3 dB. Habang tumataas ang dalas ng signal ng pag-input, ang mga analog circuit ng ADC ay wala nang oras upang iproseso ang mga pagbabago nito nang may ibinigay na katumpakan, na humahantong sa pagbaba sa koepisyent ng conversion ng ADC sa mataas na mga frequency.

Oras ng pag-aayos (Oras ng Pag-aayos ) ay ang oras na kinakailangan para maabot ng ADC ang na-rate na katumpakan nito pagkatapos mailapat ang isang hakbang na signal na may amplitude na katumbas ng buong saklaw ng input signal sa input nito. Limitado ang parameter na ito dahil sa finite speed ng iba't ibang ADC node.

Dahil sa iba't ibang uri ng mga error, ang mga katangian ng isang tunay na ADC ay nonlinear. Kung ang isang signal na ang spectrum ay binubuo ng dalawang harmonic ay inilapat sa input ng isang aparato na may mga nonlinearities f a at f b , pagkatapos ay sa spectrum ng output signal ng naturang device, bilang karagdagan sa pangunahing harmonics, magkakaroon ng intermodulation subharmonics na may mga frequency, kung saan m, n =1,2,3,... Pangalawang order subharmonics ay f a + f b , f a - f b , ang ikatlong order na subharmonic ay 2 f a + f b , 2 f a - f b , f a +2 f b , f a -2 f b . Kung ang input sinusoids ay may katulad na mga frequency, na matatagpuan malapit sa itaas na gilid ng passband, kung gayon ang pangalawang-order na subharmonics ay malayo sa input sinusoids at matatagpuan sa mas mababang frequency na rehiyon, habang ang ikatlong-order na subharmonics ay may mga frequency na malapit sa mga frequency ng input.

Intermodulation distortion factor ( Intermodulatin Distortion ) ay ang ratio ng kabuuan ng root-mean-square na mga halaga ng intermodulation subharmonics ng isang tiyak na pagkakasunud-sunod sa kabuuan ng root-mean-square na mga halaga ng mga pangunahing harmonika, na ipinahayag sa dB

(3.14).

(3.14).

Ang anumang analog-to-digital na paraan ng conversion ay nangangailangan ng ilang tiyak na oras upang makumpleto. Sa ilalim Oras ng conversion ng ADC ( Oras ng Conversion ) ay tumutukoy sa agwat ng oras mula sa sandaling dumating ang analog signal sa input ng ADC hanggang sa lumitaw ang kaukulang output code. Kung ang input signal ng ADC ay nagbabago sa paglipas ng panahon, pagkatapos ay ang may hangganan na oras ng conversion ng ADC ay humahantong sa hitsura ng tinatawag na. error sa aperture(Larawan 3.10).

|

Dumarating ang signal ng pagsisimula ng conversion sa sandaling ito t 0 , at ang output code ay lilitaw sa sandaling ito t 1 . Sa panahong ito, nagawang magbago ng input signal ayon sa halagaD U . Lumilitaw ang kawalan ng katiyakan: anong antas ng halaga ng signal ng input ang nasa hanay U 0 – U 0 + D U tumutugma sa output code na ito. Upang mapanatili ang katumpakan ng conversion sa antas ng pagkakaisa ng hindi bababa sa makabuluhang bit, kinakailangan na sa panahon ng conversion ang pagbabago sa halaga ng signal sa input ng ADC ay dapat na hindi hihigit sa halaga ng isa sa pinakamaliit. makabuluhang bit

![]() (3.15).

(3.15).

Ang pagbabago sa antas ng signal sa panahon ng conversion ay maaaring tinatayang kalkulahin bilang

(3.16),

(3.16),

kung saan ang Uin – ADC input boltahe, Tc – oras ng conversion. Ang pagpapalit ng (3.16) sa (3.15) ay nakukuha natin

![]() (3.17).

(3.17).

Kung ang input ay sinusoidal signal na may dalas f

![]() (3.18),

(3.18),

kung gayon ang derivative nito ay magiging pantay

![]() (3.19).

(3.19).

Ito ay tumatagal sa pinakamataas na halaga nito kapag ang cosine ay katumbas ng 1. Ang pagpapalit ng (3.9) sa (3.7) na ito ay nasa isip, makukuha natin

![]() , o

, o

(3.20)

Ang finite conversion time ng ADC ay humahantong sa pangangailangan na limitahan ang rate ng pagbabago ng input signal. Para mabawasan ang aperture error, atbp. upang pahinain ang limitasyon sa rate ng pagbabago ng signal ng input ng ADC sa input ng converter, ang tinatawag na "sampling-storage device" (SSD) ( Subaybayan/Hawain ang Yunit ). Ang isang pinasimple na diagram ng UVH ay ipinapakita sa Fig. 3.11.

|

Ang device na ito ay may dalawang operating mode: sampling mode at latching mode. Ang sampling mode ay tumutugma sa saradong estado ng key S.W. . Sa mode na ito, inuulit ng output voltage ng UVH ang input voltage nito. Ang latching mode ay isinaaktibo sa pamamagitan ng isang command mula sa opening key S.W. . Sa kasong ito, ang koneksyon sa pagitan ng input at output ng UVH ay nagambala, at ang output signal ay pinananatili sa isang pare-parehong antas na naaayon sa antas ng input signal sa oras na natanggap ang fixation command dahil sa singil na naipon sa kapasitor. Kaya, kung ang isang hold na command ay ibinigay kaagad bago ang simula ng ADC conversion, ang output signal ng UVH ay pananatilihin sa isang pare-parehong antas sa buong buong oras ng conversion. Pagkatapos makumpleto ang conversion, ang UVH ay muling ililipat sa sampling mode. Ang operasyon ng isang tunay na UVH ay medyo naiiba sa perpektong kaso na inilarawan (Larawan 3.12).

|

![]() (3.21),

(3.21),

saan f - dalas ng signal ng input, tA – halaga ng aperture na kawalan ng katiyakan.

Sa mga totoong UVH, ang output signal ay hindi maaaring manatiling ganap na hindi nagbabago sa panahon ng isang may hangganang oras ng conversion. Ang kapasitor ay unti-unting ilalabas ng maliit na input current ng output buffer. Upang mapanatili ang kinakailangang katumpakan, kinakailangan na sa panahon ng conversion ang singil ng kapasitor ay hindi nagbabago ng higit sa 0.5 U LSB.

Digital-to-analog converter ay karaniwang naka-install sa output ng isang microprocessor system upang i-convert ang mga output code nito sa isang analog signal na ibinibigay sa isang tuluy-tuloy na control object. Ang perpektong static na katangian ng isang 3-bit na DAC ay ipinapakita sa Fig. 3.13.

|

Katangiang panimulang punto tinukoy bilang ang punto na tumutugma sa unang (zero) input code U 00…0 . Katangian ng endpoint tinukoy bilang ang punto na naaayon sa huling input code U 11…1 . Ang mga kahulugan ng hanay ng boltahe ng output, hindi bababa sa makabuluhang bit ng quantization unit, zero offset error, at conversion coefficient error ay katulad ng mga kaukulang katangian ng ADC.

Mula sa punto ng view ng istrukturang organisasyon, ang mga DAC ay may mas kaunting iba't ibang mga opsyon para sa paggawa ng isang converter. Ang pangunahing istraktura ng DAC ay ang tinatawag na. “kadena R -2 R diagram” (Larawan 3.14).

Madaling ipakita na ang input current ng circuit ay Ako sa = U REF / R , at ang mga agos ng sunud-sunod na mga link sa chain ay ayon sa pagkakabanggit Ako sa /2, ako sa /4, ako sa /8 atbp. Upang i-convert ang input digital code sa isang output current, sapat na upang kolektahin ang lahat ng mga alon ng mga armas na naaayon sa mga yunit sa input code sa output point ng converter (Fig. 3.15).

|

Kung ang isang operational amplifier ay konektado sa output point ng converter, kung gayon ang output boltahe ay maaaring matukoy bilang

![]() (3.22),

(3.22),

kung saan si K – input digital code, Saklaw ng boltahe ng input at halaga ng LSB – DAC bit depth.

Ang lahat ng umiiral na DAC ay nahahati sa dalawang malalaking grupo: DAC na may kasalukuyang output at DAC na may boltahe na output. Ang pagkakaiba sa pagitan ng mga ito ay namamalagi sa kawalan o pagkakaroon ng isang pangwakas na yugto sa isang operational amplifier sa DAC chip. Ang mga DAC na may boltahe na output ay mas kumpletong mga device at nangangailangan ng mas kaunting karagdagang mga bahagi upang gumana. Gayunpaman, ang huling yugto, kasama ang mga parameter ng forestry circuit, ay tumutukoy sa mga dynamic at katumpakan na mga parameter ng DAC. Ang pagpapatupad ng isang tumpak, high-speed operational amplifier sa parehong chip bilang isang DAC ay kadalasang mahirap. Samakatuwid, karamihan sa mga high-speed DAC ay may kasalukuyang output.

Differential nonlinearity para sa isang DAC ay tinukoy bilang ang paglihis ng distansya sa pagitan ng dalawang katabing antas ng output analog signal mula sa perpektong halaga U LSB . Ang isang malaking halaga ng differential nonlinearity ay maaaring maging sanhi ng DAC na maging non-monotonic. Nangangahulugan ito na ang pagtaas sa digital code ay hahantong sa pagbaba sa output signal sa ilang bahagi ng katangian (Larawan 3.16). Ito ay maaaring humantong sa hindi gustong henerasyon sa system.

|

Integral nonlinearity para sa isang DAC, na tinukoy bilang ang pinakamalaking paglihis ng antas ng signal ng analog na output mula sa isang tuwid na linya na iginuhit sa pamamagitan ng mga puntos na tumutugma sa una at huling code pagkatapos na maiayos ang mga ito.

Oras ng pag-aayos Ang DAC ay tinukoy bilang ang oras kung kailan ang output signal ng DAC ay itatatag sa isang naibigay na antas na may error na hindi hihigit sa 0.5 U LSB pagkatapos mabago ang input code mula sa value na 00...0 hanggang sa value na 11...1. Kung ang DAC ay may mga rehistro ng input, kung gayon ang isang tiyak na bahagi ng oras ng pag-aayos ay dahil sa nakapirming pagkaantala sa pagpasa ng mga digital na signal, at ang natitirang bahagi lamang ay dahil sa pagkawalang-kilos ng DAC circuit mismo. Samakatuwid, ang oras ng pag-aayos ay karaniwang sinusukat hindi mula sa sandaling dumating ang isang bagong code sa input ng DAC, ngunit mula sa sandaling nagsimulang magbago ang output signal, na tumutugma sa bagong code, hanggang sa ang output signal ay maitatag nang may katumpakan. 0.5U LSB (Larawan 3.17).

|

Sa kasong ito, tinutukoy ng oras ng pag-aayos ang maximum na dalas ng sampling ng DAC

(3.23),

saan t S - oras ng pagtatatag.

Ang input digital circuits ng DAC ay may hangganan na bilis. Bilang karagdagan, ang bilis ng pagpapalaganap ng mga signal na naaayon sa iba't ibang mga bit ng input code ay hindi pareho dahil sa pagkakaiba-iba sa mga parameter ng mga elemento at mga tampok ng circuit. Bilang resulta nito, ang mga braso ng DAC ladder circuit ay hindi lumilipat nang sabay-sabay kapag dumating ang isang bagong code, ngunit may ilang pagkaantala na nauugnay sa bawat isa. Ito ay humahantong sa katotohanan na sa diagram ng output boltahe ng DAC, kapag lumilipat mula sa isang steady-state na halaga patungo sa isa pa, ang mga surges ng iba't ibang mga amplitude at direksyon ay sinusunod (Fig. 3.18).

|

|

Ayon sa operating algorithm, ang DAC ay isang zero-order extrapolator, ang dalas na tugon na maaaring kinakatawan ng expression

(3.24),

(3.24),

saan w s – dalas ng sampling. Ang amplitude-frequency na tugon ng DAC ay ipinapakita sa Fig. 3.20.

|

Tulad ng makikita, sa dalas ng 0.5w s ang reconstructed signal ay pinahina ng 3.92 dB kumpara sa mga low-frequency na bahagi ng signal. Kaya, mayroong isang bahagyang pagbaluktot ng spectrum ng muling itinayong signal. Sa karamihan ng mga kaso, ang maliit na pagbaluktot na ito ay hindi gaanong nakakaapekto sa pagganap ng system. Gayunpaman, sa mga kaso kung saan kinakailangan ang pagtaas ng linearity ng mga spectral na katangian ng system (halimbawa, sa mga audio processing system), upang i-level ang resultang spectrum sa output ng DAC, kinakailangan na mag-install ng isang espesyal na filter ng pagpapanumbalik na may dalas na tugon ng yung tipong x/sin(x).

Analog-to-digital converter(ADC, English Analog-to-digital converter, ADC) ay isang device na nagko-convert ng input analog signal sa discrete code (digital signal). Ang reverse conversion ay ginagawa gamit ang isang DAC (Digital to Analog Converter, DAC).

Karaniwan, ang ADC ay isang elektronikong aparato na nagko-convert ng boltahe sa binary digital code. Gayunpaman, ang ilang mga non-electronic na device na may digital na output ay dapat ding uriin bilang mga ADC, gaya ng ilang uri ng angle-to-code converter. Ang pinakasimpleng single-bit binary ADC ay ang comparator.

Pahintulot

Ang resolution ng isang ADC—ang pinakamababang pagbabago sa magnitude ng isang analog signal na maaaring ma-convert ng isang ibinigay na ADC—ay nauugnay sa bit capacity nito. Sa kaso ng isang solong pagsukat nang hindi isinasaalang-alang ang ingay, ang resolusyon ay direktang tinutukoy ng bit na kapasidad ng ADC.

Ang kapasidad ng ADC ay nagpapakilala sa bilang ng mga discrete value na maaaring gawin ng converter sa output. Sa binary ADCs ito ay sinusukat sa bits, sa ternary ADCs ito ay sinusukat sa trits. Halimbawa, ang isang binary 8-bit ADC ay may kakayahang gumawa ng 256 discrete values (0...255), dahil , ang isang ternary 8-bit ADC ay may kakayahang gumawa ng 6561 discrete values, since .

Ang resolution ng boltahe ay katumbas ng pagkakaiba sa pagitan ng mga boltahe na tumutugma sa maximum at minimum na output code, na hinati sa bilang ng mga discrete value ng output. Halimbawa:

Saklaw ng input = 0 hanggang 10 volts

Binary ADC na kapasidad 12 bits: 212 = 4096 na antas ng quantization

Binary ADC voltage resolution: (10-0)/4096 = 0.00244 volts = 2.44 mV

Bit capacity ng ternary ADC 12 trit: 312 = 531,441 quantization level

Resolution ng boltahe ng Ternary ADC: (10-0)/531441 = 0.0188 mV = 18.8 µV

Saklaw ng input = −10 hanggang +10 volts

Binary ADC capacity 14 bits: 214 = 16384 quantization level

Resolusyon ng boltahe ng binary ADC: (10-(-10))/16384 = 20/16384 = 0.00122 volts = 1.22 mV

Bit capacity ng ternary ADC 14 trit: 314 = 4,782,969 na antas ng quantization

Resolusyon ng boltahe ng Ternary ADC: (10-(-10))/4782969 = 0.00418 mV = 4.18 µV

Sa pagsasagawa, ang resolution ng isang ADC ay nililimitahan ng signal-to-noise ratio ng input signal. Kapag ang intensity ng ingay sa input ng ADC ay mataas, ang pagkakaiba sa pagitan ng mga katabing antas ng signal ng input ay nagiging imposible, iyon ay, ang resolution ay lumalala. Sa kasong ito, ang aktwal na makakamit na resolusyon ay inilalarawan ng epektibong bilang ng mga bit (ENOB), na mas mababa sa aktwal na kapasidad ng bit ng ADC. Kapag nagko-convert ng napakaingay na signal, ang mga low-order bit ng output code ay halos walang silbi, dahil naglalaman ang mga ito ng ingay. Upang makamit ang ipinahayag na bit depth, ang S/N ratio ng input signal ay dapat na humigit-kumulang 6 dB para sa bawat bit ng bit depth (6 dB ay tumutugma sa apat na beses na pagbabago sa antas ng signal).

Mga Uri ng Conversion

Ayon sa paraan ng mga algorithm na ginamit, ang mga ADC ay nahahati sa:

Sequential direktang paghahanap

Sunud-sunod na approximation

Serial na may sigma-delta modulation

Parallel solong yugto

Parallel na dalawa o higit pang yugto (conveyor)

Ang katangian ng paglipat ng isang ADC ay ang pagdepende ng katumbas ng numero ng output binary code sa magnitude ng input analog signal. Pinag-uusapan nila ang mga linear at nonlinear na ADC. Ang dibisyong ito ay may kondisyon. Ang parehong mga katangian ng paghahatid ay stepped. Ngunit para sa mga "linear" na ADC, palaging posible na gumuhit ng isang tuwid na linya upang ang lahat ng mga punto ng katangian ng paglipat ay naaayon sa mga halaga ng input delta*2^k (kung saan ang delta ay ang sampling na hakbang, ang k ay nasa hanay na 0. .N, kung saan ang N ay ang ADC bit depth) ay katumbas ng layo mula dito.

Katumpakan

Mayroong ilang mga pinagmumulan ng ADC error. Ang mga error sa quantization at (ipagpalagay na ang ADC ay dapat na linear) na mga nonlinearity ay likas sa anumang analog-to-digital na conversion. Bilang karagdagan, may mga tinatawag na aperture error na bunga ng jitter ng clock generator;

Ang mga error na ito ay sinusukat sa mga unit na tinatawag na LSB - least significant bit. Sa halimbawa sa itaas ng isang 8-bit binary ADC, ang error sa 1 LSB ay 1/256 ng buong saklaw ng signal, iyon ay, 0.4%, sa 5-trit ternary ADC, ang error sa 1 LSB ay 1/243 ng buong saklaw ng signal, iyon ay 0.412%, sa isang 8-trite ternary ADC, ang error sa 1 LSB ay 1/6561, iyon ay, 0.015%.

Mga uri ng ADC

Ang mga pangunahing pamamaraan para sa pagbuo ng mga electronic ADC ay nakalista sa ibaba:

Direktang conversion na ADC:

Ang mga parallel na direktang conversion na ADC, na ganap na magkatulad na mga ADC, ay naglalaman ng isang comparator para sa bawat discrete input signal level. Sa anumang oras, ang mga comparator lamang na tumutugma sa mga antas sa ibaba ng antas ng signal ng input ang gumagawa ng labis na signal sa kanilang output. Ang mga signal mula sa lahat ng mga comparator ay direktang napupunta sa isang parallel register, pagkatapos ay ang code ay naproseso sa software, o sa isang hardware logic encoder, na bumubuo ng kinakailangang digital code sa hardware depende sa code sa input ng encoder. Ang data mula sa encoder ay naitala sa isang parallel na rehistro. Ang sampling rate ng parallel ADCs, sa pangkalahatan, ay nakasalalay sa mga katangian ng hardware ng analog at logic elements, pati na rin sa kinakailangang sampling rate.

Ang mga parallel na direktang conversion na ADC ay ang pinakamabilis, ngunit kadalasan ay may resolusyon na hindi hihigit sa 8 bits, dahil nangangailangan sila ng malalaking gastos sa hardware (mga comparator). Ang mga ADC ng ganitong uri ay may napakalaking laki ng chip, mataas na kapasidad ng input, at maaaring makagawa ng mga panandaliang error sa output. Kadalasang ginagamit para sa video o iba pang mga signal na may mataas na dalas, malawak din itong ginagamit sa industriya upang subaybayan ang mabilis na pagbabago ng mga proseso sa real time.

Ang pagpapatakbo ng pipeline ng mga ADC ay ginagamit sa mga parallel-serial na ADC ng direktang conversion, sa kaibahan sa karaniwang mode ng pagpapatakbo ng mga parallel-serial na ADC ng direktang conversion, kung saan ang data ay ipinadala pagkatapos ng kumpletong conversion sa pagpapatakbo ng pipeline, ang data ng mga bahagyang conversion ay ipinadala sa sandaling ito ay handa na hanggang sa katapusan ng ganap na conversion.

Ang sunud-sunod na approximation ADC, o bit-balanced ADC, ay naglalaman ng comparator, auxiliary DAC, at sunud-sunod na approximation register. Ang ADC ay nagko-convert ng analog signal sa isang digital na signal sa N hakbang, kung saan ang N ay ang ADC bit depth. Sa bawat hakbang, ang isang bit ng nais na digital na halaga ay tinutukoy, simula sa SZR at nagtatapos sa LZR. Ang pagkakasunud-sunod ng mga aksyon upang matukoy ang susunod na bit ay ang mga sumusunod. Ang auxiliary DAC ay nakatakda sa isang analog na halaga na nabuo mula sa mga bit na natukoy na sa mga nakaraang hakbang; ang bit na dapat matukoy sa hakbang na ito ay nakatakda sa 1, ang mas mababang mga bit ay nakatakda sa 0. Ang halaga na nakuha sa auxiliary DAC ay inihambing sa input analog value. Kung ang halaga ng input signal ay mas malaki kaysa sa halaga sa auxiliary DAC, kung gayon ang bit na matutukoy ay makakakuha ng halaga 1, kung hindi man 0. Kaya, ang pagtukoy sa panghuling digital na halaga ay kahawig ng isang binary na paghahanap. Ang ganitong uri ng ADC ay may parehong mataas na bilis at mahusay na resolution. Gayunpaman, sa kawalan ng isang storage sampling device, ang error ay magiging mas malaki (isipin na pagkatapos ng pinakamalaking digit ay na-digitize, ang signal ay nagsimulang magbago).

Ang differential encoding ADCs (delta-encoded ADCs) ay naglalaman ng reverse counter, ang code kung saan ipinapadala sa auxiliary DAC. Ang input signal at ang signal mula sa auxiliary DAC ay inihambing gamit ang isang comparator. Salamat sa negatibong feedback mula sa comparator sa counter, ang code sa counter ay patuloy na nagbabago upang ang signal mula sa auxiliary DAC ay naiiba hangga't maaari mula sa input signal. Pagkaraan ng ilang oras, ang pagkakaiba ng signal ay nagiging mas mababa sa minimum na halaga, at ang counter code ay binabasa bilang ang output digital signal ng ADC. Ang mga ADC ng ganitong uri ay may napakalaking saklaw ng signal ng input at mataas na resolution, ngunit ang oras ng conversion ay depende sa input signal, bagama't ito ay limitado mula sa itaas. Sa pinakamasamang kaso, ang oras ng conversion ay katumbas ng Tmax=(2q)/fс, kung saan ang q ay ang kapasidad ng bit ng ADC, ang fс ay ang dalas ng generator ng counter clock. Ang mga differential encoding ADC ay karaniwang isang magandang pagpipilian para sa pag-digitize ng mga real-world na signal, dahil ang karamihan sa mga signal sa mga pisikal na system ay hindi madaling kapitan ng mga biglaang pagbabago. Gumagamit ang ilang ADC ng pinagsamang diskarte: differential encoding at sunud-sunod na approximation; ito ay gumagana lalo na sa mga kaso kung saan ang mga high-frequency na bahagi sa signal ay kilala na medyo maliit.

Ang paghahambing ng mga ADC na may sawtooth signal (ang ilang mga ADC ng ganitong uri ay tinatawag na Integrating ADCs, kasama rin nila ang serial counting ADCs) ay naglalaman ng sawtooth voltage generator (sa isang serial counting ADC isang step voltage generator na binubuo ng isang counter at isang DAC), isang comparator at isang time counter. Ang signal ng sawtooth ay linearly tumataas mula sa ibaba hanggang sa itaas na antas, pagkatapos ay mabilis na bumaba sa mas mababang antas. Sa sandaling magsimula ang pagtaas, magsisimula ang counter ng oras. Kapag ang ramp signal ay umabot sa input signal level, ang comparator ay na-trigger at hihinto ang counter; ang halaga ay binabasa mula sa counter at ibinibigay sa ADC output. Ang ganitong uri ng ADC ay ang pinakasimpleng istraktura at naglalaman ng pinakamababang bilang ng mga elemento. Kasabay nito, ang pinakasimpleng mga ADC ng ganitong uri ay medyo mababa ang katumpakan at sensitibo sa temperatura at iba pang mga panlabas na parameter. Upang madagdagan ang katumpakan, ang ramp generator ay maaaring itayo batay sa isang counter at isang auxiliary DAC, ngunit ang istraktura na ito ay walang iba pang mga pakinabang kumpara sa sunud-sunod na approximation ADC at differential encoding ADC.

Ang mga ADC na may charge balancing (kabilang dito ang mga ADC na may two-stage integration, ADC na may multi-stage integration, at ilang iba pa) ay naglalaman ng stable current generator, comparator, current integrator, clock generator, at pulse counter. Nagaganap ang pagbabago sa dalawang yugto (pagsasama-sama ng dalawang yugto). Sa unang yugto, ang halaga ng boltahe ng input ay na-convert sa isang kasalukuyang (proporsyonal sa boltahe ng input), na ibinibigay sa kasalukuyang integrator, ang singil na kung saan sa simula ay zero. Ang prosesong ito ay tumatagal ng isang oras TN, kung saan ang T ay ang panahon ng generator ng orasan, ang N ay isang pare-pareho (isang malaking integer na tumutukoy sa oras ng akumulasyon ng singil). Pagkatapos ng oras na ito, ang input ng integrator ay hindi nakakonekta mula sa input ng ADC at nakakonekta sa isang stable na kasalukuyang generator. Ang polarity ng generator ay tulad na binabawasan nito ang singil na naipon sa integrator. Ang proseso ng paglabas ay nagpapatuloy hanggang ang singil sa integrator ay bumaba sa zero. Ang oras ng paglabas ay sinusukat sa pamamagitan ng pagbibilang ng mga pulso ng orasan mula sa sandaling magsimula ang discharge hanggang sa umabot sa zero charge ang integrator. Ang kinakalkula na bilang ng mga pulso ng orasan ay ang ADC output code. Maaaring ipakita na ang bilang ng mga pulso n, binibilang sa oras ng paglabas, ay katumbas ng: n=UinN(RI0)−1, kung saan ang Uin ay ang input boltahe ng ADC, N ay ang bilang ng mga pulso ng yugto ng akumulasyon (tinukoy sa itaas), ang R ay ang paglaban ng risistor na nagko-convert ng input boltahe sa kasalukuyang, ang I0 ay ang halaga ng kasalukuyang mula sa stable na kasalukuyang generator, na naglalabas ng integrator sa ikalawang yugto. Kaya, ang mga potensyal na hindi matatag na mga parameter ng system (pangunahin ang kapasidad ng integrator capacitor) ay hindi kasama sa panghuling pagpapahayag. Ito ay isang kinahinatnan ng dalawang yugto na proseso: ang mga pagkakamaling ipinakilala sa una at ikalawang yugto ay kapwa ibinabawas. Walang mahigpit na mga kinakailangan kahit na para sa pangmatagalang katatagan ng generator ng orasan at boltahe ng bias ng comparator: ang mga parameter na ito ay dapat na matatag lamang sa maikling panahon, iyon ay, sa bawat conversion (hindi hihigit sa 2TN). Sa katunayan, ang prinsipyo ng dalawang yugto ng pagsasama ay nagpapahintulot sa ratio ng dalawang analog na dami (input at reference na kasalukuyang) na direktang ma-convert sa isang ratio ng mga numeric code (n at N sa mga terminong tinukoy sa itaas) na halos walang karagdagang mga error na ipinakilala. Ang karaniwang lapad ng ganitong uri ng ADC ay 10 hanggang 18 bits. Ang karagdagang bentahe ay ang kakayahang bumuo ng mga converter na hindi sensitibo sa pana-panahong interference (halimbawa, interference mula sa mains supply) dahil sa tumpak na pagsasama ng input signal sa isang nakapirming agwat ng oras. Ang kawalan ng ganitong uri ng ADC ay ang mababang bilis ng conversion. Ang mga charge balancing ADC ay ginagamit sa mataas na katumpakan na mga instrumento sa pagsukat.

ADC na may intermediate na conversion sa rate ng pag-uulit ng pulso. Ang signal mula sa sensor ay dumadaan sa isang level converter at pagkatapos ay sa pamamagitan ng isang voltage-frequency converter. Kaya, ang input ng logic circuit mismo ay tumatanggap ng isang senyas na ang katangian ay ang dalas lamang ng pulso. Ang lohikal na counter ay tumatanggap ng mga pulso na ito bilang input sa panahon ng sampling, sa gayon ay gumagawa sa pagtatapos ng oras ng pagsa-sample ng isang kumbinasyon ng code sa numerong katumbas ng bilang ng mga pulso na natanggap ng converter sa panahon ng sampling. Ang mga naturang ADC ay medyo mabagal at hindi masyadong tumpak, ngunit gayunpaman ay napakasimpleng ipatupad at samakatuwid ay may mababang halaga.

Ang mga Sigma-delta ADC (tinatawag ding delta-sigma ADC) ay nagsasagawa ng analog-to-digital na conversion sa isang sampling rate nang maraming beses na mas mataas kaysa sa kinakailangan at, sa pamamagitan ng pag-filter, iiwan lamang ang nais na spectral band sa signal.

Ang mga non-electronic na ADC ay karaniwang itinayo sa parehong mga prinsipyo.

Mga komersyal na ADC

Bilang isang patakaran, ang mga ito ay ginawa sa anyo ng mga microcircuits.

Para sa karamihan ng mga ADC, ang bit depth ay mula 6 hanggang 24 bits, at ang sampling frequency ay hanggang 1 MHz. Available din ang mga Mega- at gigahertz ADC (Pebrero 2002). Ang mga Megahertz ADC ay kinakailangan sa mga digital video camera, mga video capture device, at mga digital TV tuner upang i-digitize ang kumpletong signal ng video. Ang mga komersyal na ADC ay karaniwang may output error na ±0.5 hanggang ±1.5 LSB.

Ang isa sa mga kadahilanan na nagpapataas ng halaga ng mga chips ay ang bilang ng mga pin, dahil pinipilit nilang maging mas malaki ang chip package, at ang bawat pin ay dapat na nakakabit sa die. Upang bawasan ang bilang ng mga pin, ang mga ADC na tumatakbo sa mababang sampling rate ay kadalasang mayroong serial interface. Ang paggamit ng ADC na may serial interface ay kadalasang nagbibigay-daan para sa mas mataas na densidad ng packing at mas maliit na lugar ng board.

Kadalasan ang mga ADC chips ay may ilang mga analog input na konektado sa loob ng chip sa isang solong ADC sa pamamagitan ng isang analog multiplexer. Maaaring kabilang sa iba't ibang modelo ng ADC ang mga sample-and-hold na device, instrumentation amplifier, o high-voltage differential input at iba pang katulad na mga circuit.

Iba pang mga Aplikasyon

Ginagamit ang analog-to-digital na conversion saanman kailangang matanggap at maproseso ang analog signal sa digital form.

Ang mga espesyal na video ADC ay ginagamit sa mga computer TV tuner, video input card, at video camera para sa pag-digitize ng mga signal ng video. Ang mikropono at line audio input ng mga computer ay konektado sa isang audio ADC.

Ang mga ADC ay isang mahalagang bahagi ng mga sistema ng pagkuha ng data.

Ang mga sunud-sunod na approximation ADC na may kapasidad na 8-12 bits at sigma-delta ADCs na may kapasidad na 16-24 bits ay binuo sa single-chip microcontrollers.

Ang mga napakabilis na ADC ay kailangan sa mga digital oscilloscope (parallel at pipeline ADC ang ginagamit)

Ang mga modernong kaliskis ay gumagamit ng mga ADC na may resolusyon na hanggang 24 bits, na direktang nagko-convert ng signal mula sa strain gauge sensor (sigma-delta ADC).

Ang mga ADC ay bahagi ng mga radio modem at iba pang mga radio data transmission device, kung saan ginagamit ang mga ito kasama ng isang DSP processor bilang isang demodulator.

Ang mga napakabilis na ADC ay ginagamit sa mga base station antenna system (sa tinatawag na SMART antenna) at sa mga radar antenna array.

Digital-to-analog converter (DAC) - isang aparato para sa pag-convert ng isang digital (karaniwang binary) code sa isang analog signal (kasalukuyan, boltahe o singil). Ang mga digital-to-analog converter ay ang interface sa pagitan ng discrete digital world at analog signal.

Ang isang analog-to-digital converter (ADC) ay nagsasagawa ng reverse operation.

Ang isang audio DAC ay karaniwang tumatanggap ng digital signal sa pulse-code modulation (PCM, pulse-code modulation) bilang input nito. Ang gawain ng pag-convert ng iba't ibang mga naka-compress na format sa PCM ay ginagawa ng kani-kanilang mga codec.

Aplikasyon

Ang DAC ay ginagamit sa tuwing kinakailangan upang i-convert ang isang signal mula sa isang digital na representasyon sa isang analogue, halimbawa, sa mga CD player (Audio CD).

Mga uri ng DAC

Ang pinakakaraniwang uri ng mga electronic DAC ay:

Ang pulse width modulator ay ang pinakasimpleng uri ng DAC. Ang isang matatag na pinagmumulan ng kasalukuyang o boltahe ay pana-panahong naka-on para sa isang oras na proporsyonal sa digital code na kino-convert, pagkatapos ay ang resultang pulse sequence ay sinasala ng isang analog low-pass na filter. Ang pamamaraang ito ay kadalasang ginagamit upang kontrolin ang bilis ng mga de-koryenteng motor, at nagiging popular din sa Hi-Fi audio;

Ang mga oversampling na DAC, tulad ng mga delta-sigma DAC, ay batay sa variable pulse density. Nagbibigay-daan sa iyo ang oversampling na gumamit ng DAC na may mas mababang bit depth upang makamit ang mas mataas na bit depth ng huling conversion; Kadalasan ang isang delta-sigma DAC ay itinayo batay sa isang simpleng one-bit na DAC, na halos linear. Ang low-bit na DAC ay tumatanggap ng pulse signal na may modulated pulse density (na may pare-parehong tagal ng pulso, ngunit may variable na duty cycle), na nilikha gamit ang negatibong feedback. Ang negatibong feedback ay gumaganap bilang isang high-pass na filter para sa quantization noise.

Karamihan sa mga malalaking-bit na DAC (higit sa 16 bits) ay binuo sa prinsipyong ito dahil sa mataas na linearity nito at mababang gastos. Ang bilis ng delta-sigma DAC ay umabot sa daan-daang libong sample bawat segundo, ang bit depth ay hanggang 24 bits. Upang makabuo ng pulse density modulated signal, maaaring gumamit ng simpleng first order o mas mataas na order delta-sigma modulator gaya ng MASH (Multi stage noise SHAping). Ang pagpapataas sa dalas ng resampling ay nagpapalambot sa mga kinakailangan para sa output na low-pass na filter at pinapabuti ang pagsugpo ng ingay sa quantization;

Isang weighing-type na DAC kung saan ang bawat bit ng binary code ay tumutugma sa isang risistor o kasalukuyang source na konektado sa isang karaniwang summing point. Ang pinagmulan ng kasalukuyang (conductivity ng risistor) ay proporsyonal sa bigat ng bit kung saan ito tumutugma. Kaya, ang lahat ng di-zero bits ng code ay idinagdag sa timbang. Ang pamamaraan ng pagtimbang ay isa sa pinakamabilis, ngunit ito ay nailalarawan sa mababang katumpakan dahil sa pangangailangan para sa isang hanay ng maraming iba't ibang mga mapagkukunan ng katumpakan o resistors at variable impedance. Para sa kadahilanang ito, ang pagtimbang ng mga DAC ay may maximum na lapad na walong bits;

Uri ng hagdan DAC (R-2R chain circuit). Sa R-2R-DAC, ang mga halaga ay nilikha sa isang espesyal na circuit na binubuo ng mga resistors na may mga resistensya R at 2R, na tinatawag na isang pare-parehong impedance matrix, na may dalawang uri ng koneksyon: direktang - kasalukuyang matrix at kabaligtaran - boltahe matrix. Ang paggamit ng magkatulad na resistors ay maaaring makabuluhang mapabuti ang katumpakan kumpara sa isang maginoo na pagtimbang ng DAC, dahil ito ay medyo simple upang makabuo ng isang hanay ng mga elemento ng katumpakan na may parehong mga parameter. Ang mga DAC ng uri ng R-2R ay nagbibigay-daan sa iyo na itulak pabalik ang mga limitasyon sa bit depth. Sa laser trimming ng mga resistors sa isang substrate, ang isang katumpakan ng 20-22 bits ay nakamit. Karamihan sa oras ng conversion ay ginugugol sa operational amplifier, kaya dapat ito ay mas mabilis hangga't maaari. Ang bilis ng DAC ay ilang microseconds o mas kaunti (iyon ay, nanoseconds);

Mga katangianAng mga DAC ay matatagpuan sa simula ng analog path ng anumang system, kaya ang mga parameter ng DAC ay higit na tinutukoy ang mga parameter ng buong system sa kabuuan. Ang mga sumusunod ay ang pinakamahalagang katangian ng isang DAC.

Ang bit depth ay ang bilang ng iba't ibang antas ng output signal na maaaring kopyahin ng DAC. Karaniwang tinukoy sa mga bit; ang bilang ng mga bit ay ang base 2 logarithm ng bilang ng mga antas. Halimbawa, ang isang one-bit na DAC ay maaaring magparami ng dalawang () na antas, at ang isang walong-bit ay maaaring magparami ng 256 () na antas. Ang lalim ng bit ay malapit na nauugnay sa epektibong bilang ng mga bit (ENOB, Effective Number of Bits), na nagpapakita ng aktwal na resolution na makakamit sa isang ibinigay na DAC.

Ang maximum sampling frequency ay ang maximum frequency kung saan maaaring gumana ang DAC, na gumagawa ng tamang resulta sa output. Ayon sa Nyquist-Shannon theorem (kilala rin bilang Kotelnikov theorem), upang wastong makagawa ng analog signal mula sa isang digital form, ang sampling frequency ay dapat na hindi bababa sa dalawang beses ang maximum frequency sa signal spectrum. Halimbawa, upang kopyahin ang buong saklaw ng dalas ng audio na naririnig ng tao, ang spectrum nito ay umaabot hanggang 20 kHz, kinakailangan na ang signal ng audio ay ma-sample sa dalas na hindi bababa sa 40 kHz. Itinatakda ng pamantayang Audio CD ang audio sampling rate sa 44.1 kHz; Upang muling gawin ang signal na ito kakailanganin mo ng isang DAC na may kakayahang gumana sa dalas na ito. Ang murang computer sound card ay may sampling rate na 48 kHz. Ang mga signal na na-sample sa iba pang mga frequency ay na-resampling sa 48 kHz, na bahagyang nagpapababa sa kalidad ng signal.

Ang monotonicity ay ang pag-aari ng isang DAC upang mapataas ang analog output signal habang tumataas ang input code.

Ang THD+N (kabuuang harmonic distortion + noise) ay isang sukatan ng distortion at ingay na ipinapasok sa signal ng DAC. Ipinahayag bilang isang porsyento ng harmonic power at ingay sa output signal. Isang mahalagang parameter para sa mga small-signal na DAC application.

Ang dinamikong hanay ay ang ratio ng pinakamalaki at pinakamaliit na signal na maaaring kopyahin ng isang DAC, na ipinahayag sa mga decibel. Ang parameter na ito ay nauugnay sa bit depth at noise threshold.

Mga static na katangian:

DNL (differential nonlinearity) - nailalarawan kung gaano kalaki ang pagkakaiba ng analog signal increment na nakuha sa pamamagitan ng pagtaas ng code ng 1 least significant bit (LSB) sa tamang halaga;

INL (integral nonlinearity) - nailalarawan kung gaano naiiba ang katangian ng paglipat ng DAC mula sa perpektong isa. Ang perpektong katangian ay mahigpit na linear; Ipinapakita ng INL kung gaano kalayo ang boltahe sa output ng DAC para sa isang ibinigay na code mula sa linear na katangian; ipinahayag sa minimum na sahod;

makakuha;

pagkiling.

Mga katangian ng dalas:

SNDR (signal-to-noise + distortion ratio) - nailalarawan sa decibel ang ratio ng output signal power sa kabuuang lakas ng ingay at harmonic distortion;

HDi (i-th harmonic coefficient) - nailalarawan ang ratio ng i-th harmonic sa pangunahing harmonic;

THD (harmonic distortion factor) - ang ratio ng kabuuang kapangyarihan ng lahat ng harmonics (maliban sa una) sa kapangyarihan ng unang harmonic

Ministri ng Edukasyon at Agham ng Ukraine

Odessa National Maritime Academy

Kagawaran ng Marine Electronics

sa disiplina na "Mga sistema para sa pagkolekta at pagproseso ng telemetric na impormasyon"

"Mga digital-to-analog converter"

Nakumpleto:

set ng FEM at RE

pangkat 3131

Strukov S.M.

Sinuri: Art. guro

Kudelkin I.N.

Odessa – 2007

1. Panimula

2. Pangkalahatang impormasyon

3. Mga Serial na DAC

4. Parallel DACs

5. Paglalapat ng DAC

6. Mga parameter ng DAC

7. Listahan ng mga ginamit na panitikan

PANIMULA

Ang mga kamakailang dekada ay dahil sa malawakang pagpapakilala ng microelectronics at computer technology sa pambansang ekonomiya, ang pagpapalitan ng impormasyon na sinisiguro ng linear analog at digital converters (ADC at DAC).

Ang modernong yugto ay nailalarawan sa pamamagitan ng malaki at ultra-large integrated circuit na mga DAC at ADC na may mataas na mga parameter ng pagganap: bilis, maliliit na error, multi-bit. Ang pagsasama ng isang LSI DAC at ADC bilang isang solong, functionally complete unit ay lubos na pinasimple ang kanilang pagpapatupad sa mga device at installation na ginagamit kapwa sa siyentipikong pananaliksik at sa industriya at naging posible na mabilis na makipagpalitan ng impormasyon sa pagitan ng mga analog at digital na device.

Pangkalahatang impormasyon

Ang isang digital-to-analog converter (DAC) ay idinisenyo upang i-convert ang isang numero, karaniwang tinutukoy bilang isang binary code, sa isang boltahe o kasalukuyang proporsyonal sa halaga ng digital code. Ang circuitry ng mga digital-to-analog converter ay lubhang magkakaibang. Sa Fig. Ipinapakita ng Figure 1 ang isang scheme ng pag-uuri ng DAC ayon sa mga katangian ng circuit nito. Bilang karagdagan, ang mga IC ng mga digital-to-analog converter ay inuri ayon sa sumusunod na pamantayan:

o Sa pamamagitan ng uri ng output signal: na may kasalukuyang output at boltahe na output.

o Sa pamamagitan ng uri ng digital interface: na may serial input at may parallel na input ng input code.

o Sa bilang ng mga DAC sa chip: single-channel at multi-channel.

o Sa bilis: katamtaman at mataas na bilis.

kanin. 1. Pag-uuri ng DAC

Mga SERIAL DAC

DAC na may pulse width modulation

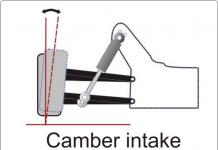

Kadalasan, ang isang DAC ay bahagi ng mga microprocessor system. Sa kasong ito, kung hindi kinakailangan ang mataas na bilis, ang digital-to-analog na conversion ay napakadaling magawa gamit ang pulse width modulation (PWM). Ang DAC circuit na may PWM ay ipinapakita sa Fig. 1a.

kanin. 1. DAC na may pulse width modulation

Ang digital-to-analog na conversion ay pinakasimpleng organisado kung ang microcontroller ay may built-in na pulse-width na function ng conversion (halimbawa, AT90S8515 mula sa Atmel o 87C51GB mula sa Intel). Kinokontrol ng output ng PWM ang switch S. Depende sa tinukoy na lalim ng conversion bit (para sa AT90S8515 controller, 8, 9 at 10 bit mode ay posible), ang controller, gamit ang timer/counter nito, ay bumubuo ng isang sequence ng mga pulso, ang kamag-anak na tagal kung saan g = t At / T ay tinutukoy ng kaugnayan

saan Saklaw ng boltahe ng input at halaga ng LSB- conversion bit depth, at D- na-convert na code. Ang isang low-pass na filter ay nagpapakinis sa mga pulso, na nagha-highlight sa average na halaga ng boltahe. Bilang isang resulta, ang output boltahe ng converter

Ang itinuturing na circuit ay nagbibigay ng halos perpektong linearity ng conversion at hindi naglalaman ng mga elemento ng katumpakan (maliban sa reference na pinagmulan ng boltahe). Ang pangunahing kawalan nito ay ang mababang pagganap.

Serial switched capacitor DAC

Ang PWM DAC circuit na tinalakay sa itaas ay unang nagko-convert ng digital code sa isang time interval, na nabuo gamit ang isang binary counter quantum sa pamamagitan ng quantum, upang makakuha ng Saklaw ng boltahe ng input at halaga ng LSB- Kinakailangan ang 2 bit na conversion N dami ng oras (cycles). Ang serial DAC circuit na ipinapakita sa Fig. 2 ay nagbibigay-daan sa digital-to-analog na conversion na maisagawa sa mas kaunting mga cycle ng orasan.

Sa circuit na ito, ang mga kapasidad ng kapasitor ay SA 1 at SA 2 ay pantay. Bago magsimula ang ikot ng conversion, ang kapasitor SA 2 ay pinalabas gamit ang isang susi S 4. Ang input binary word ay tinukoy bilang serial code. Ang conversion nito ay isinasagawa nang sunud-sunod, simula sa hindi bababa sa makabuluhang digit d 0 . Ang bawat ikot ng conversion ay binubuo ng dalawang kalahating ikot. Sa unang kalahating cycle ang kapasitor SA 1 singil sa reference na boltahe U op sa d 0 =1 sa pamamagitan ng pagsasara ng susi S 1 o discharges sa zero sa d 0 =0 sa pamamagitan ng pagsasara ng susi S 2. Sa ikalawang kalahating cycle na nakabukas ang mga susi S 1 ,S 2 at S 4 na susi ang pagsasara S 3, na nagiging sanhi ng paghati sa singil sa kalahati sa pagitan SA 1 at SA 2. Bilang resulta nakukuha namin

U 1 (0)=U labas (0)=( d 0 /2)U op

Habang nasa capacitor SA 2 singil ay pinananatili, capacitor charging procedure SA Dapat ulitin ang 1 para sa susunod na digit d 1 input na salita. Pagkatapos ng isang bagong recharge cycle, ang boltahe sa mga capacitor ay magiging

Ang pagbabagong-anyo ay ginagawa sa parehong paraan para sa natitirang mga piraso ng salita. Bilang resulta para sa Saklaw ng boltahe ng input at halaga ng LSB-bit DAC output boltahe ay magiging katumbas ng

Kung nais mong i-save ang resulta ng conversion para sa anumang mahabang panahon, dapat mong ikonekta ang isang UVH sa output ng circuit. Pagkatapos ng pagtatapos ng cycle ng conversion, dapat kang magsagawa ng sampling cycle, ilipat ang UVH sa storage mode at simulan muli ang conversion.

Kaya, binabago ng ipinakita na circuit ang input code sa 2 Saklaw ng boltahe ng input at halaga ng LSB quanta, na mas mababa kaysa sa PWM DAC. Dito, dalawang katugmang maliit na capacitor lamang ang kinakailangan. Ang pagsasaayos ng analog na bahagi ng circuit ay hindi nakasalalay sa bit depth ng na-convert na code. Gayunpaman, sa mga tuntunin ng pagganap, ang isang serial DAC ay makabuluhang mas mababa sa parallel na digital-to-analog na mga converter, na naglilimita sa saklaw ng aplikasyon nito.

Karamihan sa mga parallel na DAC circuit ay nakabatay sa kabuuan ng mga alon, ang lakas ng bawat isa ay proporsyonal sa bigat ng digital binary bit, at tanging ang mga bit na alon na ang halaga ay katumbas ng 1 ay dapat isama Halimbawa, ipagpalagay na gusto mo upang i-convert ang isang apat na bit na binary code sa isang analog kasalukuyang signal. Ang bigat ng ikaapat, pinaka makabuluhang digit (MSD) ay magiging 2 3 =8, ang ikatlong digit - 2 2 =4, ang pangalawa - 2 1 =2 at ang least significant (LSB) - 2 0 =1. Kung ang bigat ng SZR I MZR = 1 mA, kung gayon ang I SZR = 8 mA, at ang pinakamataas na kasalukuyang output ng converter I out.max = 15 mA at tumutugma sa code 1111 2. Malinaw na ang code 1001 2, halimbawa, ay tumutugma sa I out = 9 mA, atbp. Dahil dito, kinakailangan na bumuo ng isang circuit na nagsisiguro sa pagbuo at paglipat ng tumpak na pagtimbang ng mga alon ayon sa ibinigay na mga batas. Ang pinakasimpleng diagram na nagpapatupad ng prinsipyong ito ay ipinapakita sa Fig. 3.

Ang paglaban ng mga resistors ay pinili upang kapag ang mga switch ay sarado, ang isang kasalukuyang naaayon sa bigat ng discharge ay dumadaloy sa kanila. Dapat na sarado ang susi kapag ang katumbas na bit ng input word ay katumbas ng isa. Ang kasalukuyang output ay tinutukoy ng kaugnayan

![]()

Sa isang mataas na bit na kapasidad ng DAC, ang kasalukuyang-setting resistors ay dapat na tumugma sa mataas na katumpakan. Ang pinaka mahigpit na mga kinakailangan sa katumpakan ay ipinapataw sa mga resistor ng pinakamataas na mga numero, dahil ang pagkalat ng mga alon sa kanila ay hindi dapat lumampas sa kasalukuyang ng mababang-order na digit. Samakatuwid, ang pagkalat ng paglaban sa kth discharge ay dapat na mas mababa kaysa

Mula sa kondisyong ito ay sumusunod na ang pagkalat ng paglaban ng risistor, halimbawa, sa ika-apat na digit ay hindi dapat lumampas sa 3%, at sa ika-10 na digit - 0.05%, atbp.

Ang itinuturing na pamamaraan, para sa lahat ng pagiging simple nito, ay may isang buong grupo ng mga disadvantages. Una, para sa iba't ibang mga input code, ang kasalukuyang natupok mula sa reference voltage source (RPS) ay magiging iba, at ito ay makakaapekto sa halaga ng output voltage RES. Pangalawa, ang mga halaga ng paglaban ng mga resistor ng timbang ay maaaring mag-iba ng libu-libong beses, at ito ay napakahirap na ipatupad ang mga resistor na ito sa mga semiconductor IC. Bilang karagdagan, ang paglaban ng mga high-order na resistors sa mga multi-bit na DAC ay maaaring maihambing sa paglaban ng saradong switch, at ito ay hahantong sa isang error sa conversion. Pangatlo, sa circuit na ito, ang makabuluhang boltahe ay inilalapat sa mga bukas na switch, na nagpapalubha sa kanilang pagtatayo.

Ang mga pagkukulang na ito ay inalis sa AD7520 DAC circuit (domestic analogue ng 572PA1), na binuo ng Analog Devices noong 1973, na ngayon ay mahalagang pamantayan sa industriya (maraming mga serial DAC na modelo ang ginawa ayon dito). Ang ipinahiwatig na diagram ay ipinapakita sa Fig. 4. Ang mga MOS transistors ay ginagamit dito bilang mga switch.

kanin. 4. DAC circuit na may mga switch at pare-pareho ang impedance matrix