การพัฒนารถโดยสาร พีซีไอ (Peripheral Component Interconnect - การเชื่อมต่อส่วนประกอบภายนอก) เริ่มขึ้นในฤดูใบไม้ผลิปี 1991 โดยเป็นโครงการภายในของ Intel Corporation หรือกลุ่มความสนใจพิเศษที่จัดโดย Intel Corporation เปิดตัวในเดือนมิถุนายน 1992 บัส PCI(รีลีส 0.1) เนื่องจากรถโดยสารรุ่นต่อไปซึ่งไม่สามารถรักษาความเข้ากันได้กับรถโดยสารรุ่นก่อนๆ ได้ มีคุณสมบัติหลายประการที่ทำให้สามารถครองตำแหน่งที่โดดเด่นในตลาดพีซีได้ในระยะเวลาอันสั้น โดยผลักดันคู่แข่งจำนวนมากออกไป สิ่งสำคัญคือสถาปัตยกรรมแบบเปิด ทุกคนสามารถเข้าถึงได้ และความเป็นอิสระจากบัสโปรเซสเซอร์

กลุ่มความสนใจพิเศษกำลังพัฒนา PCI สำหรับใช้ในระบบที่มีโปรเซสเซอร์ Pentium ผู้เชี่ยวชาญได้ตั้งเป้าหมายในการพัฒนาโซลูชันราคาประหยัดที่จะช่วยให้พวกเขาตระหนักถึงความสามารถของโปรเซสเซอร์ 486/Pentium/P6 เจเนอเรชันใหม่ได้อย่างเต็มที่ การพัฒนาดำเนินการ "ตั้งแต่เริ่มต้น" และไม่ใช่ความพยายามที่จะติดตั้ง "แพตช์" ใหม่ โซลูชั่นที่มีอยู่- อันเป็นผลมาจากการทำงานในเดือนพฤษภาคม พ.ศ. 2536 มีเวอร์ชันที่ทันสมัยปรากฏขึ้น - เวอร์ชัน PCI 2.0 ซึ่งกลายเป็นมาตรฐานโดยพฤตินัยในหมู่ บัสคอมพิวเตอร์ วัตถุประสงค์ทั่วไป- ที่จริงแล้วรถบัสคันนี้ไม่ใช่รถท้องถิ่นเพราะว่า มันไม่ได้เชื่อมต่อโดยตรงกับบัสระบบ แต่ใช้ Host Bridge (บริดจ์หลัก) ในการเชื่อมต่อ เช่นเดียวกับ Peer-to-Peer Bridge (เพียร์บริดจ์) ซึ่งออกแบบมาเพื่อเชื่อมต่อบัส PCI สองตัว เหนือสิ่งอื่นใด PCI เองก็เป็นสะพานเชื่อมระหว่าง ISA และบัสโปรเซสเซอร์

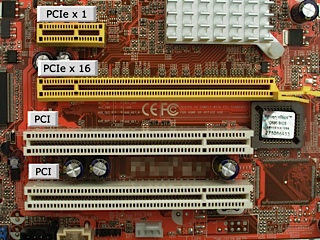

การปรากฏตัวของบัส PCI ในตลาดถือเป็นการปฏิวัติเล็กน้อย การ์ดเอ็กซ์แพนชันที่หลากหลายที่ใช้บัส PCI นั้นยอดเยี่ยมมากจนไม่มีประโยชน์ที่จะแสดงรายการเหล่านี้ มาตรฐาน PCI มีการ์ดสามประเภทขึ้นอยู่กับแหล่งจ่ายไฟ:

5V – สำหรับคอมพิวเตอร์เดสก์ท็อป

3.3V – สำหรับคอมพิวเตอร์แล็ปท็อป

บอร์ดสากลสามารถทำงานบนคอมพิวเตอร์ทั้งสองประเภทได้

เป็นบัสแยกต่างหาก แยกออกจากโปรเซสเซอร์ แต่ยังคงเข้าถึงหน่วยความจำหลักได้

ไม่ขึ้นอยู่กับโปรเซสเซอร์ เพราะ นักพัฒนาของ Intel ต่างจาก VLB ที่ละทิ้งการใช้บัสโปรเซสเซอร์และทำงานร่วมกับโปรเซสเซอร์ผ่านตัวควบคุมพิเศษที่เรียกว่า ยาง "ชั้นลอย"

ด้วยโซลูชันนี้ บัสจึงสามารถทำงานคู่ขนานกับบัสโปรเซสเซอร์ได้โดยไม่ต้องหันไปร้องขอ ตัวอย่างเช่น โปรเซสเซอร์ทำงานร่วมกับแคชหรือ หน่วยความจำระบบและในเวลานี้ข้อมูลจะถูกเขียนลงในฮาร์ดไดรฟ์ผ่านเครือข่าย ในความเป็นจริงสิ่งนี้ใช้งานไม่ได้ แต่โหลดบัสโปรเซสเซอร์ลดลงอย่างมาก นอกจากนี้ มาตรฐานบัสยังได้รับการประกาศให้เปิดและโอนไปยัง PCI Special Interest Group ซึ่งยังคงทำงานเพื่อปรับปรุงบัสต่อไป (ปัจจุบัน R2.1 พร้อมใช้งานแล้ว)

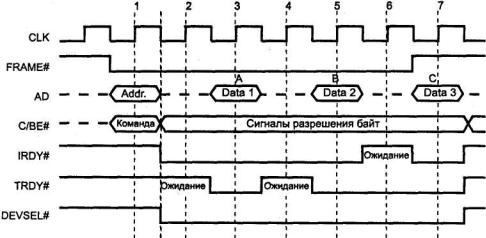

บนบัส PCI การส่งสัญญาณใดๆ จะเกิดขึ้นในลักษณะแพ็กเก็ต โดยแต่ละแพ็กเก็ตจะถูกแบ่งออกเป็นเฟส แพ็กเก็ตเริ่มต้นด้วยเฟสที่อยู่ ซึ่งมักจะตามด้วยเฟสข้อมูลตั้งแต่หนึ่งเฟสขึ้นไป จำนวนเฟสข้อมูลในแพ็กเก็ตสามารถไม่มีกำหนด แต่ถูกจำกัดโดยตัวจับเวลาที่กำหนด เวลาสูงสุดในระหว่างที่รถบัสสามารถใช้อุปกรณ์ได้ อุปกรณ์ที่เชื่อมต่อแต่ละเครื่องจะมีตัวจับเวลาดังกล่าว และสามารถตั้งค่าได้ระหว่างการกำหนดค่า ผู้ตัดสินใช้เพื่อจัดระเบียบงานการถ่ายโอนข้อมูล ความจริงก็คือบนบัสสามารถมีอุปกรณ์ได้สองประเภท - มาสเตอร์ (ตัวเริ่มต้น, มาสเตอร์, มาสเตอร์) ของบัสและทาส ต้นแบบจะควบคุมบัสและเริ่มการถ่ายโอนข้อมูลไปยังปลายทาง เช่น สเลฟ หลักหรือทาสอาจเป็นอุปกรณ์ใดๆ ที่เชื่อมต่อกับบัส และลำดับชั้นนี้เปลี่ยนแปลงตลอดเวลาขึ้นอยู่กับอุปกรณ์ที่ขออนุญาตจากผู้ตัดสินบัสเพื่อถ่ายโอนข้อมูลและใคร ชิปเซ็ตหรือที่เรียกว่า North Bridge มีหน้าที่รับผิดชอบการทำงานของบัส PCI โดยปราศจากข้อขัดแย้ง แต่ชีวิตไม่ได้หยุดอยู่ที่ PCI การปรับปรุงการ์ดแสดงผลอย่างต่อเนื่องส่งผลให้พารามิเตอร์ทางกายภาพของบัส PCI ไม่เพียงพอซึ่งนำไปสู่การเกิดขึ้นของ AGP

บัส PCI เป็นแบบซิงโครนัส 32 บิต (นอกจากนี้ยังมีเวอร์ชัน 64 บิตซึ่งจะไม่ได้รับการพิจารณาเนื่องจากเนื่องจาก ค่าใช้จ่ายสูงใช้เฉพาะในเวิร์กสเตชันและเซิร์ฟเวอร์ราคาแพงเท่านั้น) บัสสามารถทำงานแบบอะซิงโครนัสจากโปรเซสเซอร์ด้วยความถี่ปกติที่ 25 MHz, 30 MHz และ 33 MHz โดยให้ทรูพุต (โดยใช้โหมดการถ่ายโอนข้อมูลแพ็คเก็ต) ที่ 133 Mb/s เมื่อความเร็วโปรเซสเซอร์เพิ่มขึ้น ความถี่บัส PCI อาจคงที่และเป็นเพียงเศษเสี้ยวของบัส FSB บัสรองรับจำนวนช่องและ/หรือเป็นสองเท่า อุปกรณ์ต่อพ่วงเปรียบเทียบกับ VLB - ห้ารายการขึ้นไป โดยไม่มีข้อจำกัดด้านความถี่หรือการบัฟเฟอร์

คุณสมบัติอื่นๆ ทำให้ PCI ใช้งานง่ายขึ้น เทคโนโลยี Plug and Play ช่วยให้ผู้ผลิตกำหนดค่าอุปกรณ์ต่อพ่วงได้โดยอัตโนมัติ โดยไม่ต้องตั้งค่าที่อยู่ IRQ, DMA และ I/O ผ่านจัมเปอร์ นอกจากนี้ บัสยังรองรับ IRQ ที่แชร์ระหว่างอุปกรณ์หลายตัวรวมถึงอุปกรณ์ของตัวเองด้วย ระบบของตัวเองขัดจังหวะ (ซ่อนอยู่หลังการกำหนด #A, #B, #C และ #D)

โปรเซสเซอร์สามารถเชื่อมต่อกับช่อง PCI หลายช่องผ่านบริดจ์ (PCI Bridge) ให้ความสามารถในการถ่ายโอนข้อมูลพร้อมกันระหว่างช่อง PCI อิสระ คุณสมบัติที่สำคัญบัสเป็นการนำหลักการบัสมาสเตอร์มาใช้ ซึ่งอนุญาตให้การ์ดเอ็กซ์แพนชันแลกเปลี่ยนข้อมูลกับหน่วยความจำโดยไม่ต้องเข้าถึงโปรเซสเซอร์ ควบคุม บัส-PCI บัสการควบคุมอุปกรณ์ที่อนุญาตให้ใช้บนบัสเพื่อควบคุมและทำการถ่ายโอนข้อมูลโดยตรงโดยไม่ต้องมีส่วนร่วมของโปรเซสเซอร์ ส่งผลให้เวลาในการตอบสนองและโหลดของโปรเซสเซอร์ลดลง

เพื่อลดจำนวนตัวนำในบัส PCI จะใช้หลักการของมัลติเพล็กซ์ข้อมูลนั่นคือที่อยู่และข้อมูลจะถูกส่งสลับกันบนเส้นฟิสิคัลเดียวกัน อุปกรณ์ PCI มีการติดตั้งตัวจับเวลาซึ่งกำหนดระยะเวลาสูงสุดที่อุปกรณ์สามารถครอบครองบัสได้

เครื่องมือรองรับการกำหนดค่าอัตโนมัติของอุปกรณ์ PCI (การเลือกคำขอขัดจังหวะ, ช่อง DMA) ไบออสเมนบอร์ดบอร์ดตามมาตรฐาน Plug&Play ข้อมูลจำเพาะ PCI 2.2 ในปัจจุบันให้การสนับสนุนการ์ดเอ็กซ์แพนชันที่มีแรงดันไฟฟ้าทั้ง 3.3 และ 5V และประเภทของการ์ดจะถูกกำหนดโดยตำแหน่งของคีย์ในตัวเชื่อมต่อ หากการ์ด PCI มีรอยบากหลักสองช่อง แสดงว่ารองรับตัวเลือกสล็อตใดๆ ก็ตาม แต่หากมีรอยบากใกล้กับด้านหน้าบอร์ดเพียงรอยเดียว การ์ดใบนี้ก็จะมีแรงดันไฟฟ้าเพียง 3.3V เท่านั้น เมื่อรอยบากตั้งอยู่ใกล้กับด้านหลัง การ์ดจะเป็น 5V

คุณสมบัติหลักของรถบัส:

การแลกเปลี่ยนข้อมูลแบบซิงโครนัส 32 บิตหรือ 64 บิต (ปัจจุบันบัส 64 บิตใช้เฉพาะในระบบอัลฟ่าและเซิร์ฟเวอร์ตาม โปรเซสเซอร์อินเทล Xeon แต่โดยหลักการแล้วมันคืออนาคต) ในกรณีนี้ เพื่อลดจำนวนผู้ติดต่อ (และต้นทุน) จะใช้มัลติเพล็กซ์นั่นคือที่อยู่และข้อมูลจะถูกส่งผ่านบรรทัดเดียวกัน

รองรับลอจิก 5 V และ 3.3 V (มีตัวเลือกแรงดันไฟฟ้า 2 แบบ - 5 และ 3.3 V) ขั้วต่อสำหรับบอร์ด 5 และ 3.3 V ตำแหน่งของปุ่มต่างกัน ไม่สามารถเสียบการ์ด 3.3V เข้ากับขั้วต่อ 5V ได้ (และในทางกลับกัน) นอกจากนี้ยังมีบอร์ดสากลที่รองรับแรงดันไฟฟ้าทั้งสองอีกด้วย ควรสังเกตว่า 66 MHz รองรับลอจิก 3.3 V เท่านั้น

ความถี่การทำงานของบัส 33 MHz หรือ 66 MHz (ในเวอร์ชัน 2.1) ส่วนหลังทำได้ที่ 3.3 V และ 2 ตัวเลือกสำหรับความกว้างบัสข้อมูล/ที่อยู่ - 32 บิตและ 64 บิต ความถี่ดังกล่าวทำให้สามารถให้บริการได้ หลากหลายแบนด์วิดธ์ (ใช้โหมดถ่ายภาพต่อเนื่อง): 132 Mb/s ที่ 32 บิต/33 MHz; 264 เมกะไบต์/วินาทีที่ 32 บิต/66MHz; 264 เมกะไบต์/วินาทีที่ 64 บิต/33MHz; 528 เมกะไบต์/วินาที ที่ 64 บิต/66MHz ในเวลาเดียวกัน เพื่อให้บัสทำงานที่ความถี่ 66 MHz จำเป็นที่อุปกรณ์ต่อพ่วงทั้งหมดจะทำงานที่ความถี่นี้ สามารถมีได้หลายส่วนโดยเชื่อมต่อกันผ่านทางสะพาน เซ็กเมนต์สามารถรวมกันเป็นโทโพโลยีต่างๆ (ต้นไม้ ดาว ฯลฯ)

ขั้วต่อจะคล้ายกับ MCA/VLB แต่ยาวกว่าเล็กน้อย (124 พิน) ตัวเชื่อมต่อ 64 บิตมีส่วน 64 พินเพิ่มเติมพร้อมคีย์ของตัวเอง ตัวเชื่อมต่อและการ์ดทั้งหมดแบ่งออกเป็นระดับสัญญาณที่รองรับ 5 V 3.3 V และสากล สองประเภทแรกจะต้องสอดคล้องกัน สามารถวางการ์ดสากลในช่องใดก็ได้ นอกจากนี้ยังมีส่วนขยาย MediaBus สำหรับบัส PCI ที่ ASUSTek แนะนำสำหรับการเชื่อมต่อ การ์ดเสียง- ตัวเชื่อมต่อเพิ่มเติมที่อยู่ด้านหลังสล็อต PCI มีสัญญาณบัส ISA

รองรับการคูณบัสมาสเตอร์อย่างเต็มที่ (เช่น หลาย ฮาร์ดคอนโทรลเลอร์ดิสก์สามารถทำงานบนบัสได้พร้อมกัน)

การสนับสนุนแคชการเขียนกลับและการเขียนผ่าน

การกำหนดค่าอัตโนมัติของการ์ดเอ็กซ์แพนชันเมื่อมีการจ่ายไฟ

ข้อมูลจำเพาะของบัสช่วยให้คุณสามารถรวมฟังก์ชั่นได้มากถึงแปดฟังก์ชั่นในการ์ดเดียว (เช่นวิดีโอ + เสียง ฯลฯ )

บัสช่วยให้คุณติดตั้งสล็อตขยายได้สูงสุด 4 ช่อง แต่เป็นไปได้ที่จะใช้บริดจ์ PCI-PCI เพื่อเพิ่มจำนวนการ์ดเอ็กซ์แพนชัน

อุปกรณ์ PCI มีตัวจับเวลาซึ่งใช้ในการกำหนดเวลาสูงสุดที่อุปกรณ์สามารถครอบครองบัสได้

เมื่อพัฒนารถบัส สถาปัตยกรรมของรถบัสก็รวมเอาขั้นสูงไว้ด้วย โซลูชั่นทางเทคนิคทำให้สามารถเพิ่มปริมาณงานได้ บัสรองรับวิธีการถ่ายโอนข้อมูลที่เรียกว่า "linear burst" วิธีนี้จะถือว่าแพ็กเก็ตข้อมูลถูกอ่าน (หรือเขียน) "เป็นชิ้นเดียว" นั่นคือที่อยู่จะเพิ่มขึ้นโดยอัตโนมัติสำหรับไบต์ถัดไป โดยปกติแล้ว สิ่งนี้จะเพิ่มความเร็วในการส่งข้อมูลโดยการลดจำนวนที่อยู่ที่ส่ง

บัส PCI เป็นพื้นฐานที่ใช้สร้างสถาปัตยกรรมพีซี Microsoft/Intel Plug and Play ข้อมูลจำเพาะของบัส PCI กำหนดทรัพยากรสามประเภท: สองประเภททั่วไป (ช่วงหน่วยความจำและช่วง I/O ตามที่เรียกว่า บริษัทไมโครซอฟต์) และพื้นที่การกำหนดค่า - "พื้นที่การกำหนดค่า"

ตามมาตรฐาน พินบัส PCI จะแบ่งออกเป็นแบบบังคับ (จำเป็น) และแบบเสริม (ไม่บังคับ) ต้องมีพินบังคับอยู่ในรายการใดรายการหนึ่ง ขั้วต่อ PCIและแผนที่

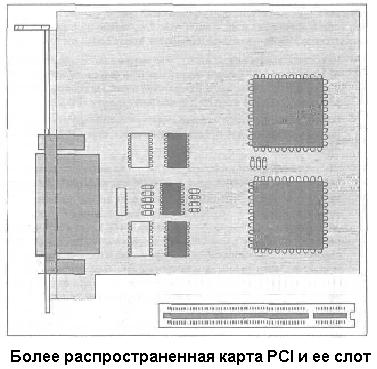

การ์ด PCI (Peripheral Component Interconnect) เช่น การ์ด ISA ก็มีส่วนยื่นเล็กๆ สองอันที่ด้านล่างเช่นกัน ความแตกต่างที่สำคัญระหว่างการ์ด PCL และการ์ด ISA 16 บิต:

| ^ การกำหนดพินสล็อต PCI |

|||||

| ตัวเลข | สัญญาณ (ด้านบัดกรี) | สัญญาณ (ด้านการติดตั้ง) | ตัวเลข | สัญญาณ (ด้านบัดกรี) | สัญญาณ (ด้านการติดตั้ง) |

| 1 | TRST# | -12V | 48 | จีเอ็นดี | AD10 |

| 2 | +12V | ทีซีเค | 49 | AD09 | จีเอ็นดี |

| 3 | ทีเอ็มเอส | จีเอ็นดี | 50 | GND/5V | GND/5V |

| 4 | ทีดีไอ | ทีดีโอ | 51 | GND/5V | GND/5V |

| 5 | +5V | +5V | 52 | C/BE0 | AD08 |

| 6 | อินต้า# | +5V | 53 | +3.3V | AD07 |

| 7 | INTC# | INTB# | 54 | AD06 | +3.3V |

| 8 | +5V | INTD# | 55 | AD04 | AD05 |

| 9 | ที่สงวนไว้ | PRSNT1# | 56 | จีเอ็นดี | AD03 |

| 10 | +5V | ที่สงวนไว้ | 57 | AD02 | จีเอ็นดี |

| 11 | ที่สงวนไว้ | PRSNT2 | 58 | AD00 | AD01 |

| 12 | GND/3.3V | GND/3.3V | 59 | +5V | +5V |

| 13 | GND/3.3V | GND/3.3V | 60 | REQ64# | ACK64# |

| 14 | ที่สงวนไว้ | ที่สงวนไว้ | 61 | +5V | +5V |

| 15 | RST# | จีเอ็นดี | 62 | +5V | +5V |

| 16 | +5V | ซีแอลเค | 63 | จีเอ็นดี | ที่สงวนไว้ |

| 17 | จีเอ็นที# | จีเอ็นดี | 64 | ซี/บีอี7# | จีเอ็นดี |

| 18 | จีเอ็นดี | คำขอ# | 65 | C/BE5# | C/BE6# |

| 19 | ที่สงวนไว้ | +5V | 66 | +5V | C/BE4# |

| 20 | AD30 | AD31 | 67 | พาร์64 | จีเอ็นดี |

| 21 | +3.3V | ค.ศ. 29 | 68 | ค.ศ. 62 | ก63 |

| 22 | ค.ศ. 28 | จีเอ็นดี | 69 | จีเอ็นดี | ก61 |

| 23 | ค.ศ. 26 | ค.ศ. 27 | 70 | AD60 | +5V |

| 24 | จีเอ็นดี | ค.ศ. 25 | 71 | ค.ศ.58 | ค.ศ.59 |

| 25 | ค.ศ. 24 | +3.3V | 72 | จีเอ็นดี | ค.ศ.57 |

| 26 | ไอดเซล | ซี/บี3# | 73 | พ.ศ. 56 | จีเอ็นดี |

| 27 | +3.3V | ค.ศ. 23 | 74 | ค.ศ.54 | พ.ศ. 55 |

| 28 | ค.ศ. 22 | จีเอ็นดี | 75 | +5V | ค.ศ.53 |

| 29 | ค.ศ. 20 | ค.ศ. 21 | 76 | ค.ศ. 52 | จีเอ็นดี |

| 30 | จีเอ็นดี | ค.ศ. 19 | 77 | AD50 | ค.ศ.51 |

| 31 | ค.ศ. 18 | +3.3V | 78 | จีเอ็นดี | ค.ศ.49 |

| 32 | ค.ศ.16 | ค.ศ. 17 | 79 | ค.ศ.48 | จีเอ็นดี |

| 33 | 3.3V | C/BE2#80 | 80 | ค.ศ.46 | ค.ศ.47 |

| 34 | กรอบ# | จีเอ็นดี | 81 | จีเอ็นดี | ค.45 |

| 35 | จีเอ็นดี | ไออาร์ดี้# | 82 | ค.ศ.44 | จีเอ็นดี |

| 36 | TRDY# | 3.3V | 83 | ค.ศ.42 | ค.ศ.43 |

| 37 | จีเอ็นดี | การพัฒนา# | 84 | +5V | ค.ศ.41 |

| 38 | หยุด# | จีเอ็นดี | 85 | AD40 | จีเอ็นดี |

| 39 | +3.3V | ล็อค# | 86 | ค.38 | ค.39 |

| 40 | สโดน | เปอร์ # | 87 | จีเอ็นดี | ค.37 |

| 41 | เอสบีโอ# | +3.3V | 88 | ค.ศ.36 | +5V |

| 42 | จีเอ็นดี | เซิร์ฟเวอร์# | 89 | ค.34 | AD35 |

| 43 | พาร์ | +3.3V | 90 | จีเอ็นดี | ค.33 |

| 44 | ค.ศ.15 | ซี/บีอี1 | 91 | AD32 | จีเอ็นดี |

| 45 | +3.3V | ค.ศ. 14 | 92 | ที่สงวนไว้ | ที่สงวนไว้ |

| 46 | ค.ศ.13 | จีเอ็นดี | 93 | จีเอ็นดี | ที่สงวนไว้ |

| 47 | ค.ศ.11 | ค.ศ.12 | 94 | ที่สงวนไว้ | จีเอ็นดี |

ปัจจุบันการ์ดส่วนใหญ่เป็นการ์ด PCI

การใส่เฝือกไปด้วย โปรเซสเซอร์เพนเทียมเสริมด้วยข้อได้เปรียบเหนือคู่แข่งอย่างเห็นได้ชัด ทำให้ PCI ชนะสงครามรถบัสและกลายเป็นมาตรฐานที่โดดเด่นในปี 1994 ตั้งแต่นั้นเป็นต้นมา อุปกรณ์ต่อพ่วงเกือบทั้งหมดก็เริ่มตั้งแต่ตัวควบคุม ฮาร์ดไดรฟ์และการ์ดเสียงไปยังการ์ดวิดีโอและ การ์ดเครือข่ายอิงตามบัส PCI

พร้อมจำหน่าย อาร์เรย์ RAID, Gigabit Ethernet และอุปกรณ์แบนด์วิธสูงอื่นๆ บนระบบแบนด์วิธระดับผู้บริโภค ความสามารถของ PCIความเร็ว 133 MB/s ยังไม่เพียงพอ

ผู้ผลิตชิปเซ็ตคาดการณ์ถึงข้อจำกัดเหล่านี้และทำการเปลี่ยนแปลงต่างๆ กับผลิตภัณฑ์ของตนเพื่อลดภาระบางส่วนจากบัส PCI

ก่อนปี 1997 ระบบย่อยกราฟิกโหลดบัส PCI มากที่สุด การเปิดตัว AGP (Accelerated Graphics Port) พร้อมด้วยชิปเซ็ต Intel 440LX มีจุดประสงค์สองประการ: เพื่อเพิ่ม ประสิทธิภาพกราฟิกและลบข้อมูลกราฟิกออกจากบัส PCI เพราะ ข้อมูลกราฟิกเริ่มส่งสัญญาณผ่าน "บัส" อื่น (อันที่จริงพอร์ต AGP ไม่สามารถเรียกว่าบัสได้เนื่องจากรองรับเพียงอุปกรณ์เดียว) บัส PCI ที่โอเวอร์โหลดก็สามารถปล่อยให้ทำงานกับอุปกรณ์อื่นได้

อย่างไรก็ตาม AGP เป็นเพียงก้าวแรกในการลดภาระบนบัส PCI หลังจากนี้ ผู้ผลิตชิปเซ็ตต้องออกแบบการเชื่อมต่อระหว่างสะพานเหนือและใต้ใหม่ ชิปเซ็ตเก่าเช่น สายอินเทล 440 ใช้บัส PCI สำหรับการสื่อสารระหว่างบริดจ์ บัส PCI ไม่เพียงต้องถ่ายโอนข้อมูลระหว่างบริดจ์เท่านั้น แต่ยังให้บริการอุปกรณ์ PCI อื่นๆ ด้วย รวมถึง IDE, Super I/O (ขนานและ พอร์ตอนุกรม, PS/2) รวมถึง USB เพื่อแก้ไขสถานการณ์ Intel VIA และ SiS เริ่มใช้สายความเร็วสูงพิเศษเพื่อเชื่อมต่อบริดจ์เหนือและใต้ จากนั้นถ่ายโอน IDE, Super I/O และ USB ไปยังสายเฉพาะของตนเองไปยังบริดจ์ใต้

ในที่สุด ในเดือนเมษายน Intel ได้ประกาศสถาปัตยกรรม CSA ที่รองรับ สะพานเหนือชิปเซ็ต i875/i865 กำลังถอดออก อีเธอร์เน็ตกิกะบิตจากบัส PCI

แม้ว่า AGP, CSA, Intel Hub Link, VIA V-Link และ SiS MuTIOL สามารถเรียกได้ว่าเป็นโซลูชันที่ประสบความสำเร็จในการบรรเทาภาระบนบัส PCI แต่ก็เป็นเพียงเหตุการณ์สำคัญระดับกลางเท่านั้น

ตำแหน่งที่โดดเด่นในตลาดพีซีนั้นถูกครอบครองโดยระบบที่อิงจาก ยางพีซีไอ(การเชื่อมต่อส่วนประกอบต่อพ่วง - ปฏิสัมพันธ์ของส่วนประกอบต่อพ่วง) นี้ อินเตอร์เฟซถูกเสนอ โดยอินเทลในปีพ.ศ. 2535 (มาตรฐาน พีซีไอ 2.0 - ในปี 1993) เพื่อเป็นทางเลือกแทนท้องถิ่น ยางวีแอลบี/วีแอลบี2. ควรสังเกตว่าผู้พัฒนารายนี้ อินเตอร์เฟซตำแหน่ง พีซีไอไม่ใช่ในระดับท้องถิ่น แต่เป็นระดับกลาง ยาง(รถบัสชั้นลอย) เพราะ เธอไม่ได้ ยางโปรเซสเซอร์ เพราะ ยางพีซีไอไม่ใช่โปรเซสเซอร์เฉพาะและสามารถใช้กับโปรเซสเซอร์อื่นได้ ยางพีซีไอได้รับการปรับให้เข้ากับโปรเซสเซอร์เช่น Alpha, MIPS, PowerPC และ SPARC อย่างแน่นอน พีซีไอแทนที่ NuBus บนแพลตฟอร์ม Apple Macintosh

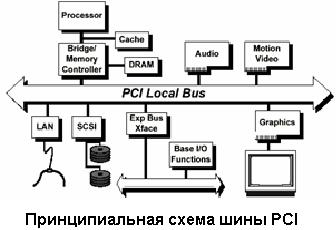

ยางอส, EISA หรือ MCA สามารถควบคุมได้ ยางพีซีไอโดยใช้อินเทอร์เฟซบริดจ์ (รูปที่ 14.3) ซึ่งช่วยให้คุณติดตั้งบอร์ดอุปกรณ์ I/O ด้วยระบบอื่นได้ อินเทอร์เฟซ- ตัวอย่างเช่นใน ชิปเซ็ตอินเทล Triton ใช้ชิป PIIX 1) นอกเหนือจากคอนโทรลเลอร์ IDE แล้วยังมีบริดจ์สำหรับ ยางอส.

¶ ข้าว. 14.3.ระบบที่ใช้ PCI

มีสามตัวเลือกบอร์ด พีซีไอ: มีระดับสัญญาณ 3.3 V มีระดับสัญญาณ 5 V และสากล กุญแจในช่องช่วยให้แน่ใจว่าบอร์ดที่มีระดับสัญญาณเดียวและไม่สามารถเปลี่ยนได้จะไม่ถูกเสียบเข้าไปในช่องที่มีระดับสัญญาณต่างกันโดยไม่ตั้งใจ บอร์ดลดแรงดันไฟฟ้าส่วนใหญ่จะใช้ในคอมพิวเตอร์พกพา

มีการใช้งานแบบ 32 บิตและ 64 บิต ยางพีซีไอ- การใช้งานแบบ 64 บิตใช้ตัวเชื่อมต่อพร้อมส่วนเพิ่มเติม การ์ด 32 บิตและ 64 บิตสามารถติดตั้งในสล็อต 64 บิตและ 32 บิตและในทางกลับกัน บอร์ดและ ยางระบุประเภทตัวเชื่อมต่อและทำงานอย่างถูกต้อง เมื่อติดตั้งการ์ด 64 บิตลงในสล็อต 32 บิต พินที่เหลือจะไม่ถูกใช้และยื่นออกมาเลยขั้วต่อ

บน ยางพีซีไอที่อยู่และข้อมูลสัญญาณเป็นแบบมัลติเพล็กซ์ ดังนั้นแต่ละ 32 หรือ 64 บิตต้องใช้บัสสองรอบในการส่ง: หนึ่งรอบสำหรับส่งที่อยู่และอีกหนึ่งรอบในการส่งข้อมูล อย่างไรก็ตามก็เป็นไปได้เช่นกัน โหมดแบตช์ซึ่งหลังจากหนึ่งรอบการถ่ายโอนที่อยู่ จะอนุญาตให้มีการถ่ายโอนข้อมูลได้สูงสุดสี่รอบ (สูงสุด 16 ไบต์ใน PCI-32) หลังจากนั้นควรส่งอุปกรณ์ คำขอใหม่เพื่อการบำรุงรักษาและควบคุมกลับคืนมา ยาง(และดำเนินการวนรอบที่อยู่) นั่นเป็นเหตุผล ยาง PCI-32 ที่โอเวอร์คล็อกที่ 33 MHz มีความเร็วการถ่ายโอนปกติสูงสุดประมาณ 66 MB/s (รอบบัสสองรอบในการถ่ายโอน 4 ไบต์) และความเร็วการถ่ายโอนต่อเนื่องสูงสุดประมาณ 105 MB/s

พีซีไอรองรับขั้นตอนการเข้าถึงหน่วยความจำโดยตรงของอุปกรณ์หลัก ยาง(bus mastering DMA) แม้ว่าการใช้งานบางอย่าง พีซีไออาจไม่มีคุณลักษณะนี้สำหรับตัวเชื่อมต่อทั้งหมด พีซีไอ- โปรเซสเซอร์สามารถทำงานแบบขนานกับอุปกรณ์ต่อพ่วงที่เป็นอุปกรณ์หลักได้ ยาง.

นอกจากนี้ค่าธรรมเนียม พีซีไอสนับสนุน:

การกำหนดค่า Plug&Play อัตโนมัติ (ไม่จำเป็นต้องกำหนดที่อยู่ส่วนขยาย BIOS ด้วยตนเอง)

การแบ่งปันอินเตอร์รัปต์ (โดยที่สามารถใช้หมายเลขอินเตอร์รัปต์เดียวกันได้ อุปกรณ์ที่แตกต่างกัน);

ความเท่าเทียมกันของสัญญาณ ยางข้อมูลและที่อยู่ ยาง;

หน่วยความจำการกำหนดค่าตั้งแต่ 64 ถึง 256 ไบต์ ( รหัสผู้ผลิต, รหัสอุปกรณ์, รหัสคลาสอุปกรณ์ (ฟังก์ชัน) ฯลฯ)

คอมพิวเตอร์ส่วนบุคคลอาจมีบัสตั้งแต่สองตัวขึ้นไป พีซีไอ- แต่ละ ยางจัดการสะพานของคุณ พีซีไอซึ่งช่วยให้คุณติดตั้งบอร์ดเพิ่มเติมลงในคอมพิวเตอร์ของคุณได้ พีซีไอ(สูงสุด 16 - กล่าวถึงข้อจำกัด) ถ้าการควบคุมเป็นอันดับสอง ยางพีซีไอดำเนินการตั้งแต่ครั้งแรก ยางจากนั้นสิ่งนี้เรียกว่าแบบเรียงซ้อนหรือแบบลำดับชั้น ในกรณีนี้สิ่งแรก ยางจะรับภาระของวินาทีด้วย ยาง- หากบริหารจัดการกันคนละอย่าง ยางพีซีไอดำเนินการโดยตรงจาก ยางโปรเซสเซอร์ ซึ่งเรียกว่ารูปแบบเพียร์ทูเพียร์ มักจะเป็นสะพาน พีซีไอยังทำหน้าที่ของตัวควบคุมหน่วยความจำแคชภายนอก ตัวควบคุมหน่วยความจำหลัก และจัดเตรียมอินเทอร์เฟซกับโปรเซสเซอร์ ในระบบที่ใช้ Pentium II/III ฟังก์ชันเหล่านี้จะถูกกระจายระหว่างสองบริดจ์: "North Bridge" และ "South Bridge" ซึ่งเกิดจากการมีระบบความเร็วสูงเพิ่มเติม อินเตอร์เฟซเพื่อเชื่อมต่อการ์ดแสดงผล ( เอจีพี).

เวอร์ชันปรับปรุงเปิดตัวในปี 1995 อินเตอร์เฟซ-พีซีไอ 2.1 ซึ่งมีคุณสมบัติดังต่อไปนี้:

รองรับนาฬิกา ยาง 66 เมกะเฮิรตซ์;

MTT (Multi-Transaction Timer) อนุญาตให้อุปกรณ์ DMA ค้างไว้ ยางสำหรับ "ไม่สม่ำเสมอ" การส่งแพ็กเก็ตและไม่จำเป็นต้องแสวงหาสิทธิ์ในการควบคุมซ้ำอีก ยางซึ่งมีประโยชน์อย่างยิ่งเมื่อส่งข้อมูลวิดีโอ

Passive Release อนุญาตให้อุปกรณ์ที่เข้าถึงหน่วยความจำโดยตรงผ่าน ยาง พีซีไอส่งข้อมูลในขณะที่กำลังส่งข้อมูลผ่าน ยาง อส(โดยปกติจะส่งผลให้มีการปิดกั้นการส่งสัญญาณผ่าน ยาง พีซีไอเนื่องจากมันถูกใช้เพื่อเชื่อมต่อ โปรเซสเซอร์กลางถึง ยาง อส);

การทำธุรกรรมล่าช้า พีซีไออนุญาตให้ส่งข้อมูลอุปกรณ์หลักไป ยาง พีซีไอได้รับลำดับความสำคัญมากกว่าข้อมูลที่อยู่ในคิวสำหรับการส่งข้อมูล พีซีไอบน อส(ซึ่งจะแชร์ในภายหลัง);

ปรับปรุงประสิทธิภาพการเขียนโดยจัดเตรียมชิปเซ็ต PCI ให้มีบัฟเฟอร์ขนาดใหญ่ขึ้น เพื่อให้ธุรกรรมสามารถเข้าคิวได้เมื่อใด ยาง พีซีไอไม่ว่าง และมีการสะสมของไบต์ คำ และ doublewords ซึ่งสามารถรวมกันเป็นการดำเนินการเขียนขนาด 8 ไบต์เดียวได้

ตั้งแต่ปี 2005 ในพีซีที่ใช้ Pentium 4 แทน พีซีไอใช้ระบบใหม่ อินเตอร์เฟซ-พีซีไอ เอ็กซ์เพรส .

พีซีไอ - ยาง

PCI (Peripheral Component Interconnect bus) เป็นบัสสำหรับเชื่อมต่ออุปกรณ์ต่อพ่วง มีการใช้กันอย่างแพร่หลายสำหรับระบบ Pentium แต่ยังใช้กับโปรเซสเซอร์ 486 ตัวด้วย ความถี่บัสตั้งแต่ 20 ถึง 33 MHz ความเร็วสูงสุดตามทฤษฎี 132/264 MB/s สำหรับ 32/64 บิต ในเมนบอร์ดสมัยใหม่ ความถี่บนบัส PCI ถูกตั้งค่าเป็น 1/2 ความถี่อินพุตของโปรเซสเซอร์ เช่น ที่ความถี่ 66 MHz PCI จะเป็น 33 MHz ที่ 75 MHz - 37.5 MHz

มีเวอร์ชันที่มีแหล่งจ่ายไฟ 5V, 3.3V และสากล (พร้อมสวิตช์ +VI/O เส้นจาก 5V เป็น 3.3V) ปุ่มคือแถวที่ขาดหายไปของหน้าสัมผัส 12, 13 และ 50, 51 สำหรับช่องที่มีแหล่งจ่ายไฟ 5V ปุ่มจะอยู่ที่ตำแหน่งของหน้าสัมผัส 50, 51 สำหรับ 3.3 V - 12, 13 และสำหรับสากล หนึ่ง - สองปุ่ม: 12, 13 และ 50. 51. สล็อต 32 บิตลงท้ายด้วยหน้าสัมผัส A62/B62 สล็อต 64 บิตลงท้ายด้วย A94/B94

สล็อต PCI นั้นเพียงพอในตัวเองสำหรับเชื่อมต่อคอนโทรลเลอร์ใดๆ บนเมนบอร์ด และสามารถอยู่ร่วมกับบัส I/O อื่นๆ ได้

บัส PCI เป็นบัสแรกในสถาปัตยกรรม IBM PC ที่ไม่เฉพาะเจาะจงกับสถาปัตยกรรมนั้น ไม่ขึ้นอยู่กับโปรเซสเซอร์ และใช้ในคอมพิวเตอร์ Macintosh เป็นต้น

ส่วนประกอบต่างจากบัสอื่นๆ ตรงที่ส่วนประกอบต่างๆ จะอยู่ที่พื้นผิวด้านซ้ายของบอร์ดอะแดปเตอร์ PCI ด้วยเหตุนี้ สล็อต PCI ชั้นนอกสุดจึงมักจะแชร์พื้นที่กับสล็อต ISA ที่อยู่ติดกัน (สล็อตที่ใช้ร่วมกัน)

โปรเซสเซอร์สามารถเชื่อมต่อกับช่อง PCI หลายช่องผ่านบริดจ์ที่เรียกว่า (PCI Bridge) ซึ่งให้ความสามารถในการถ่ายโอนข้อมูลพร้อมกันระหว่างช่อง PCI อิสระ

การกำหนดค่าอุปกรณ์อัตโนมัติ (การเลือกคำขอขัดจังหวะ, ช่อง DMA) ได้รับการสนับสนุนโดย BIOS ของเมนบอร์ดในลักษณะเดียวกับมาตรฐาน Plug & Play

มาตรฐาน PCI กำหนดพื้นที่การกำหนดค่าสำหรับแต่ละสล็อตที่มีรีจิสเตอร์ 8 บิตสูงสุด 256 ตัว ซึ่งไม่ได้กำหนดให้กับพื้นที่หน่วยความจำหรือพื้นที่ I/O เข้าถึงได้ผ่านวงจรบัสการอ่านการกำหนดค่าและการเขียนการกำหนดค่าพิเศษ ซึ่งสร้างขึ้นโดยคอนโทรลเลอร์เมื่อโปรเซสเซอร์เข้าถึงรีจิสเตอร์คอนโทรลเลอร์บัส PCI ที่อยู่ในพื้นที่ I/O

PCI กำหนดอุปกรณ์หลักสองประเภท - ตัวเริ่มต้น (ตาม GOST - ต้นแบบ) เช่น อุปกรณ์ที่ได้รับอนุญาตจากผู้ตัดสินบัสให้ยึดอุปกรณ์ดังกล่าวและอุปกรณ์ปลายทาง ซึ่งเป็นเป้าหมายที่ผู้ริเริ่มดำเนินการรอบการแลกเปลี่ยนข้อมูล

รองรับอุปกรณ์ PCI แบบ hot-swappable ซึ่งเรียกในมาตรฐานว่า PCI Hot-Plug การเข้าสู่ฟังก์ชันนี้จะทำให้คุณสามารถเพิ่ม/ลบได้ การ์ด PCIโดยไม่ต้องปิดคอมพิวเตอร์ คุณลักษณะนี้จำเป็นอย่างยิ่งสำหรับแพลตฟอร์มเซิร์ฟเวอร์

ระบบการจัดการพลังงานสำหรับอุปกรณ์บนบัส PCI ช่วยให้คุณจัดการการใช้พลังงานของทั้งคู่ได้ PCI ภายนอกบอร์ดและอุปกรณ์ที่ติดตั้งอยู่ในเมนบอร์ด กลไกการควบคุมได้รับการปรับให้เป็นมาตรฐาน ACPI เพื่ออำนวยความสะดวกในการจัดการการใช้พลังงานของอุปกรณ์ PCI โดยระบบปฏิบัติการ

ข้อกำหนดสำหรับการใช้งานการออกแบบบอร์ด PCI ได้รับการเสริมและปรับปรุง

สัญญาณบัส PCI

เครื่องหมาย - (ลบ) หน้าชื่อสัญญาณหมายความว่าระดับที่ใช้งานอยู่ของสัญญาณนี้เป็นศูนย์ตรรกะ การกำหนด (XX:0) หมายถึงกลุ่มของสัญญาณที่มีตัวเลขตั้งแต่ 0 ถึง XX

ค.ศ(31:0) - ที่อยู่แบบมัลติเพล็กซ์/บัสข้อมูล ที่อยู่จะถูกส่งผ่านสัญญาณ FRAME และข้อมูลจะถูกส่งในรอบสัญญาณนาฬิกาต่อมา

-ค/ พ.ศ(3:0) - คำสั่ง/สิทธิ์ในการเข้าถึงไบต์ คำสั่งที่กำหนดประเภทของวงจรบัสถัดไป (หน่วยความจำแบบอ่าน-เขียน, I/O หรือการกำหนดค่าการอ่าน/เขียน, การยืนยันการขัดจังหวะ ฯลฯ) จะถูกระบุด้วยรหัสสี่บิตในเฟสที่อยู่ของสัญญาณ - FRAME

-กรอบ- ตัวบ่งชี้เฟสที่อยู่ (มิฉะนั้น - การส่งข้อมูล)

-เดฟเซล- การเลือกอุปกรณ์ปลายทางโดยผู้ริเริ่ม

-IRDY- ความพร้อมของผู้ริเริ่มในการแลกเปลี่ยนข้อมูล

-TRDY- ความพร้อมของอุปกรณ์ปลายทางในการแลกเปลี่ยนข้อมูล

-หยุด- คำขอจากอุปกรณ์ปลายทางไปยังผู้ริเริ่มเพื่อหยุดธุรกรรมปัจจุบัน

-ล็อค- ใช้เพื่อติดตั้ง บำรุงรักษา และปลดล็อคทรัพยากรบน PCI

-GNT(3 0) - การอนุญาตให้นายใช้รถโดยสาร

พาร์- บิตพาริตีทั่วไปสำหรับเส้น ค.ศ(31:0) และ ซี/บี {3:0}.

-ความเท่าเทียมกัน- สัญญาณข้อผิดพลาดของพาริตี (จากอุปกรณ์ที่ตรวจพบ)

-พส- รีเซ็ตอุปกรณ์ทั้งหมด

ไอดเซล- การเลือกอุปกรณ์ปลายทางในรอบการอ่านและเขียนการกำหนดค่า

-เซอร์ - ข้อผิดพลาดของระบบถูกเปิดใช้งานโดยอุปกรณ์ PCI ใดๆ และทำให้เกิดการขัดจังหวะตัวประมวลผลที่ปกปิดได้ (NMI)

-REQ64- ขอแลกเปลี่ยน 64 บิต

-ASK64- การยืนยันการแลกเปลี่ยน 64 บิต

-INTR A,B,C,D- สายคำขอขัดจังหวะถูกส่งไปยังสาย IRQ ที่มีอยู่ ไบออสคอมพิวเตอร์- ร้องขอโดย ระดับต่ำอนุญาตให้ใช้สายขัดจังหวะร่วมกัน

นาฬิกา- สัญญาณการซิงโครไนซ์ที่ความถี่สัญญาณนาฬิกาบัส

นาฬิกาทดสอบ, -TSTRES, TestDO, TestDI- สัญญาณสำหรับการทดสอบอะแดปเตอร์ผ่านอินเทอร์เฟซ JTAG (โดยปกติจะไม่ใช้กับเมนบอร์ด)

TSTMSLCT- ถ่ายโอนไปยังโหมดการทดสอบ

ขั้วต่อบัส PCI

| แถวบี | ตัวเลข | แถวเอ | แถวบี | ตัวเลข | แถวเอ |

| -12 โวลต์ | 1 | -TSTRES | -ค/บี 3 | 26 | ไอดเซล |

| ทดสอบนาฬิกา | 2 | +12 บ | ค.ศ. 23 | 27 | +3.3 โวลต์ |

| จีเอ็นดี | 3 | TSTMSLCT | จีเอ็นดี | 28 | ค.ศ. 22 |

| ทดสอบดีโอ | 4 | ทดสอบดีโอ | ค.ศ. 21 | 29 | ค.ศ. 20 |

| +5 บ | 5 | +5 บ | ค.ศ. 19 | 30 | จีเอ็นดี |

| +5 บ | 6 | -INTR เอ | +3.3 โวลต์ | 31 | ค.ศ. 18 |

| -INTR บี | 7 | -INTR ซี | ค.ศ. 17 | 32 | ค.ศ. 16 |

| -INTR D | 8 | +5 บ | -ซี/บี 2 | 33 | +3.3 โวลต์ |

| -PRSNT1 | 9 | ที่สงวนไว้ | จีเอ็นดี | 34 | -กรอบ |

| ที่สงวนไว้ | 10 | +วี/โอ | -IRDY | 35 | จีเอ็นดี |

| -PRSNT2 | 11 | ที่สงวนไว้ | +3.3 โวลต์ | 36 | -TRDY |

| GND/คีย์ | 12 | GND/คีย์ | -เดฟเซล | 37 | จีเอ็นดี |

| GND/คีย์ | 13 | GND/คีย์ | จีเอ็นดี | 38 | -หยุด |

| ที่สงวนไว้ | 14 | ที่สงวนไว้ | -ล็อค | 39 | +3.3 โวลต์ |

| จีเอ็นดี | 15 | -พส | ความเท่าเทียมกัน | 40 | สโดน |

| นาฬิกา | 16 | +วี/โอ | +3.3 โวลต์ | 41 | -เอสบีออฟ |

| จีเอ็นดี | 17 | -GNT | SysERR | 42 | จีเอ็นดี |

| -REQ | 18 | จีเอ็นดี | +3.3 โวลต์ | 43 | พาร์ |

| +วี ไอ/โอ | 19 | ที่สงวนไว้ | -ค/บี 1 | 44 | ค.ศ. 15 |

| ค.ศ. 31 | 20 | ค.ศ. 30 | ค.ศ. 14 | 45 | +3.3 โวลต์ |

| ค.ศ. 29 | 21 | +3.3 โวลต์ | จีเอ็นดี | 46 | ค.ศ. 13 |

| จีเอ็นดี | 22 | ค.ศ. 28 | ค.ศ. 12 | 47 | ค.ศ. 11 |

| ค.ศ. 27 | 23 | ค.ศ. 26 | ค.ศ. 10 | 48 | จีเอ็นดี |

| ค.ศ. 25 | 24 | จีเอ็นดี | จีเอ็นดี | 49 | ค.ศ. 9 |

| +3.3 โวลต์ | 25 | ค.ศ. 24 | GND/คีย์ | 50** | GND/คีย์ |

| GND/คีย์ | 51**** | GND/คีย์ | จีเอ็นดี | 73 | ค.ศ. 56 |

| ค.ศ. 8 | 52 | -ค/พ.ศ. 0 | ค.ศ. 55 | 74 | ค.ศ. 54 |

| ค.ศ. 7 | 53 | +3.3 โวลต์ | ค.ศ. 53 | 75 | +วี/โอ |

| +3.3 โวลต์ | 54 | ค.ศ. 6 | จีเอ็นดี | 76 | ค.ศ. 52 |

| ค.ศ. 5 | 55 | ค.ศ. 4 | ค.ศ. 51 | 77 | ค.ศ. 50 |

| ค.ศ. 3 | 56 | จีเอ็นดี | ค.ศ. 49 | 78 | จีเอ็นดี |

| จีเอ็นดี | 57 | ค.ศ. 2 | +วี/โอ | 79 | ค.ศ. 48 |

| ค.ศ. 1 | 58 | โฆษณา 0 | ค.ศ. 47 | 80 | ค.ศ. 46 |

| +วี/โอ | 59 | +วี/โอ | ค.ศ. 45 | 81 | จีเอ็นดี |

| - อัก 64 | 60 | -REQ64 | จีเอ็นดี | 82 | ค.ศ. 44 |

| +5 บ | 61 | +5B | ค.ศ. 43 | 83 | ค.ศ. 42 |

| +5 บ | 62 | +5B | ค.ศ. 41 | 84 | +วี/โอ |

| จุดสิ้นสุดของตัวเชื่อมต่อ 32 บิต | จีเอ็นดี | 85 | ค.ศ. 40 | ||

| ค.ศ. 39 | 86 | ค.ศ. 38 | |||

| ที่สงวนไว้ | 63 | จีเอ็นดี | ค.ศ. 37 | 87 | จีเอ็นดี |

| จีเอ็นดี | 64 | -ค/บี 7 | +วี/โอ | 88 | ค.ศ. 36 |

| -ค/พ.ศ | 65 | - ค/บี 5 | ค.ศ. 35 | 89 | ค.ศ. 34 |

| -ค/พ.ศ | 66 | +วี/โอ | ค.ศ. 33 | 90 | จีเอ็นดี |

| จีเอ็นดี | 67 | พาร์ 64 | จีเอ็นดี | 91 | ค.ศ. 32 |

| ค.ศ. 63 | 68 | ค.ศ. 62 | ที่สงวนไว้ | 92 | ที่สงวนไว้ |

| ค.ศ. 61 | 69 | จีเอ็นดี | ที่สงวนไว้ | 93 | จีเอ็นดี |

| +วี/โอ | 70 | ค.ศ. 60 | จีเอ็นดี | 94 | ที่สงวนไว้ |

| ค.ศ. 59 | 71 | ค.ศ. 58 | จุดสิ้นสุดของตัวเชื่อมต่อ 64 บิต | ||

| ค.ศ. 57 | 72 | จีเอ็นดี | |||

*12, 13 - ปุ่มสำหรับ 3.3V

**50.51 - กุญแจสำหรับ 5V

รอบรถบัส

สัญญาณ C/BE (C/BE3 ถึง C/BE0) ในระหว่างขั้นตอนการถ่ายโอนที่อยู่จะกำหนดประเภทของรอบการถ่ายโอนข้อมูล

| ซี/บี | ทีม |

| 0000 | รับทราบขัดจังหวะ |

| 0001 | รอบพิเศษ |

| 0010 | อ่าน I/O (อ่านพอร์ต) |

| 0011 | การเขียน I/O (การเขียนพอร์ต) |

| 0100 | ที่สงวนไว้ |

| 0101 | ที่สงวนไว้ |

| 0110 | หน่วยความจำอ่าน |

| 0111 | หน่วยความจำเขียน |

| 1000 | ที่สงวนไว้ |

| 1001 | ที่สงวนไว้ |

| 1010 | อ่านการกำหนดค่า |

| 1011 | เขียนการกำหนดค่า |

| 1100 | อ่านหน่วยความจำหลายรายการ |

| 1101 | วงจรที่อยู่คู่ |

| 1110 | บรรทัดการอ่านหน่วยความจำ |

| 1111 | หน่วยความจำเขียนและทำให้ใช้งานไม่ได้ |

รับทราบการขัดจังหวะ (0000)

ตัวควบคุมอินเทอร์รัปต์จะจดจำสัญญาณ INTA โดยอัตโนมัติและตอบสนองโดยการส่งเวกเตอร์อินเทอร์รัปต์บนบัส AD

รอบพิเศษ (0001)

อ่านพอร์ต (0010) และเขียนไปยังพอร์ต (0011)

พอร์ต I/O บนบัส PCI อาจเป็น 8 หรือ 16 บิต แม้ว่ามาตรฐานบัส PCI เองจะอนุญาตให้มีพื้นที่แอดเดรส 32 บิตก็ตาม ทั้งนี้ก็เพราะว่าในเครื่องคอมพิวเตอร์ด้วย สถาปัตยกรรมอินเทล x86 ที่อยู่พอร์ตต้องมีได้ไม่เกิน 16 บิต ในตอนนี้ ที่อยู่พอร์ต 16 บิตไม่สามารถใช้งานได้ เนื่องจากการ์ดบนบัส ISAC:\www\doc2html\work\bestreferat-93864-13927654724498\input\isabus.htm สามารถถอดรหัสได้เพียง 10 บิตเท่านั้น

พื้นที่ที่อยู่การกำหนดค่ามีอยู่ตามที่อยู่พอร์ต 0x0CF8 (ที่อยู่) และ 0x0CFC (ข้อมูล) และต้องเขียนที่อยู่ก่อน

อ่านหน่วยความจำ (0110) และเขียนหน่วยความจำ (0111)

AD บัสส่งที่อยู่เป็นคำคู่ (สี่ไบต์) ไม่จำเป็นต้องถอดรหัสสัญญาณ AD0 และ AD1 ความถูกต้องของข้อมูลถูกกำหนดโดยสัญญาณ C/BE

อ่านการกำหนดค่า (1010) และเขียนข้อมูลการกำหนดค่า (1011)

การดำเนินการเหล่านี้ดำเนินการสำหรับพื้นที่การกำหนดค่าการ์ด PCI ขนาดของพื้นที่การกำหนดค่าคือ 256 ไบต์ และคุณสามารถอ่าน/เขียนได้เฉพาะในกริดแบบ 32 บิตเท่านั้น เช่น คำสองคำ ดังนั้นต้องตั้งค่า AD0 และ AD1 เป็น 0 AD2-7 มีที่อยู่คำคู่ AD8-10 ใช้เพื่อเลือกอุปกรณ์ที่สามารถระบุตำแหน่งได้ และบรรทัดที่อยู่ที่เหลือจะถูกละเว้น

รอบที่อยู่คู่ (1101)

จำเป็นต้องมีวงจรที่อยู่คู่หากจำเป็นต้องถ่ายโอนที่อยู่ 64 บิตในเวอร์ชัน PCI ด้วยตารางที่อยู่ 32 บิต ในรอบแรก ไบต์ต่ำสี่ไบต์ของที่อยู่จะถูกส่ง จากนั้นไบต์สูงสี่ไบต์ ในการวนรอบที่สอง จำเป็นต้องส่งคำสั่งที่กำหนดประเภทของอุปกรณ์ที่มีการตั้งค่าที่อยู่ (พอร์ต I/O, หน่วยความจำ ฯลฯ) PCI เองรองรับที่อยู่ 64 บิตสำหรับพอร์ต I/O แต่ในพีซีที่ใช้โปรเซสเซอร์สถาปัตยกรรม Intel พื้นที่ที่อยู่ดังกล่าวไม่ได้รับการสนับสนุน (โปรเซสเซอร์เองไม่อนุญาต)

ในฤดูร้อนปี 2542 สมาคม PCI SIG ได้นำข้อกำหนดสำหรับบัส PCI - PCI-X เวอร์ชันใหม่มาใช้ แม้จะยอดเยี่ยมก็ตาม พารามิเตอร์ทางเทคนิคบัสใหม่ได้รับการพัฒนาภายใต้สายตาที่ไม่เชื่อของ Intel ซึ่งกำลังพัฒนาบัส NGIO ของตัวเองอย่างแข็งขัน จนถึงขณะนี้อินเทอร์เฟซเกือบทั้งหมดที่พัฒนาโดย Intel (AGP, PCI, USB) ได้รับการยอมรับจากอุตสาหกรรมคอมพิวเตอร์ มุมมองอย่างเป็นทางการของ Intel เกี่ยวกับ PCI-X มีดังนี้: PCI-X เป็นบัสที่ดี แต่อายุการใช้งานจะสั้น - มีชีวิตอยู่ เพราะเมื่อเราพัฒนาและอนุมัติ NGIO แล้ว PCI-X จะออกจากตลาด โดยสูญเสีย NGIO ในแง่ของโอกาสและประสิทธิภาพ เวลาจะบอกได้ว่าใครจะเป็นผู้ชนะ แต่ก็ชัดเจนว่าเป็นเช่นนั้นเท่านั้น รองรับ PCI-X Intel สามารถพบการกระจายอย่างกว้างขวางในชิปเซ็ตของตน

การมีส่วนร่วมอย่างแข็งขันดังกล่าว บริษัทขนาดใหญ่ในฐานะที่เป็น IBM, Compaq, Hewlett-Packard ในการพัฒนา PCI-X อย่างไรก็ตามทำให้บัสใหม่มีโอกาสประสบความสำเร็จอย่างมากและนอกจากนี้การนำข้อกำหนด PCI-X มาใช้ในขณะที่ NGIO ยังอยู่ในการพัฒนาก็บ่งบอกถึงความโปรดปรานของมัน

ความแตกต่างที่สำคัญระหว่าง PCI-X และ PCI:

· ความถี่สัญญาณนาฬิการถโดยสารที่มีความถี่สูงสุด 133 MHz

· สามารถใช้ช่องต่างๆ ได้ ความเร็วที่แตกต่างกันการแลกเปลี่ยนข้อมูล มาตรฐานมี 1 ช่องความถี่ 133 MHz, 2 ช่อง 100 MHz ส่วนที่เหลือสามารถใช้ช่องความถี่ 33 และ 66 MHz

· เวลาที่จัดสรรสำหรับการดำเนินการใน PCI-X ลดลงอย่างมาก (เวลาทั้งหมดในหน่วยนาโนวินาที)

| พารามิเตอร์ | PCI-X 133 เมกะเฮิรตซ์ | PCI-X 100 เมกะเฮิรตซ์ | PCI-X ความเร็ว 66 เมกะเฮิรตซ์ | PCI ปกติ 66 MHz | PCI ปกติ 33 MHz |

| ทีวี (สูงสุด) | 3.8 | 3.8 | 3.8 | 6 | 11 |

| ทพร็อพ | 2.0 | 4.5 | 9.5 | 5 | 10 |

| เอียง | 0.5 | 0.5 | 0.5 | 1 | 2 |

| สึ | 1.2 | 1.2 | 1.2 | 3 | 7 |

| ทีไซค์ | 7.5 | 10 | 15 | 15 | 30 |

| ถือ | 0 | 0 | 0 | 1 | 2 |

ขั้นพื้นฐาน ความแตกต่างในการทำงานทำเป็นตาราง:

| ความเป็นไปได้ | พีซีไอ | เอจีพี1.0 | AGP2.0 | PCI-X |

| เป็นไปตามมาตรฐาน PCI | ใช่ | เลขที่ | เลขที่ | ใช่ |

| ความเร็วบัส 100 MHz | เลขที่ | เลขที่ | เลขที่ | ใช่ |

| ความเร็วบัส 133 MHz | เลขที่ | 66 ดีดีอาร์ | 66 ดีดีอาร์ | ใช่ |

| ความเร็วบัส 266 MHz | เลขที่ | เลขที่ | 66 คิวดีอาร์ | เลขที่ |

| ความกว้างบัสข้อมูล | 32/64 | 32 | 32 | 64 |

| ความกว้างของบัสแอดเดรส | 32/64 | 32/36/64 | 32/47/64 | 64 |

| ความเร็วสูงสุดแลกเปลี่ยน MBytes/s | 533 | 533 | 1064 | 1064 |

| ค่าเผื่อหลายสล็อต | ใช่ | เลขที่ | เลขที่ | ใช่ |

| โทโพโลยีแบบลำดับชั้น | ใช่ | เลขที่ | เลขที่ | ใช่ |

| ธุรกรรมที่ไม่สอดคล้องกัน | เลขที่ | ใช่ | ใช่ | ใช่ |

| ตัวระบุอุปกรณ์และบัส (ช่วยให้คุณสามารถปรับพารามิเตอร์การสื่อสารให้เหมาะสม) | เลขที่ | เลขที่ | เลขที่ | ใช่ |

หมายเหตุ:

DDR - อัตราข้อมูลสองเท่า - ความเร็วการถ่ายโอนข้อมูลเป็นสองเท่า

QDR - อัตราข้อมูลสี่เท่า - ความเร็วการถ่ายโอนข้อมูลสี่เท่า

ยาง PCI ขนาดกะทัดรัด(cPCI) ได้รับการพัฒนาตามข้อกำหนด PCI เวอร์ชัน 2.1 บัสนี้แตกต่างจาก PCI ทั่วไป จำนวนมากช่องที่รองรับสำหรับบัสหนึ่งตัว: 8 ต่อ 4 ด้วยเหตุนี้จึงมีสัญญาณคำขอใหม่ 4 คู่และการควบคุมบัสปรากฏขึ้น บัสรองรับการแลกเปลี่ยนแบบ 32 บิตและ 64 บิต (ด้วยความละเอียดของแต่ละไบต์) ที่ความถี่บัสสูงสุด 33 MHz ปริมาณงานคือ 133 Mb/s สำหรับ 32 บิต และ 266 Mb/s สำหรับ 64 บิต (ในช่วงกลางของรอบแพ็กเก็ต) นอกจากนี้ยังสามารถทำงานที่ความถี่ 66 MHz และประสิทธิภาพเพิ่มขึ้นเป็นสองเท่า บัสรองรับข้อกำหนด PnP - กลไกการระบุและการกำหนดค่าอัตโนมัติทั้งหมดที่มีอยู่ใน PCI ทำงานได้ นอกจากนี้ บัสยังสามารถใช้การกำหนดที่อยู่ทางภูมิศาสตร์ ซึ่งที่อยู่ของโมดูล (ที่ตอบสนองระหว่างการเข้าถึงโปรแกรม) จะถูกกำหนดโดยตำแหน่งในเฟรม

เพื่อจุดประสงค์นี้ ตัวเชื่อมต่อ J1 มีหน้าสัมผัส GA0...GA4 โดยการสลับไปที่กราวด์สำหรับแต่ละช่อง จึงสามารถตั้งค่าที่อยู่ไบนารีได้ การกำหนดที่อยู่ทางภูมิศาสตร์ทำให้คุณสามารถจัดเรียงโมดูลประเภทเดียวกันใหม่ได้โดยไม่ต้องกังวลกับการกำหนดค่าที่อยู่ ( ทางเลือกที่ดีระบบ PnP - ที่นี่โมดูลจะ "ยืนหยัด" ในที่อยู่เดียวกันเสมอซึ่งจะไม่สับสนหากไม่มีการแทรกแซงทางกายภาพ) ตามโครงสร้างแล้ว การ์ด PCI ขนาดกะทัดรัดคือ Eurocard สูง 3U (100 x 160 มม.) พร้อมขั้วต่อหนึ่งตัว หรือ 6U (233 x 160 มม.) พร้อมขั้วต่อสองตัว ตัวเชื่อมต่อ - ตัวเชื่อมต่อพิน 7 แถวที่มีระยะห่างระหว่างหน้าสัมผัส 2 มม. บนแบ็คเพลน - ปลั๊ก บนโมดูล - ซ็อกเก็ต หน้าสัมผัสของตัวเชื่อมต่อมีความยาวต่างกัน: หน้าสัมผัสที่ยาวกว่าของวงจรไฟฟ้าจะเชื่อมต่อไว้ก่อนหน้านี้เมื่อติดตั้งโมดูล และจะตัดการเชื่อมต่อในภายหลังเมื่อถอดออกมากกว่าหน้าสัมผัสสัญญาณ

โซลูชันนี้วางรากฐานสำหรับการดำเนินการตามความเป็นไปได้ในการเปลี่ยนโมดูลแบบ "ร้อน" ตัวบัสเองใช้ตัวเชื่อมต่อเพียงตัวเดียว (J1) และไม่ใช่เวอร์ชัน 32 บิตทั้งหมด - ผู้ติดต่อบางส่วนได้รับการจัดสรรเพื่อใช้ตามดุลยพินิจของผู้ใช้ บัส 64 บิตใช้ตัวเชื่อมต่อทั้งหมด หนึ่งที่นั่งบนแบ็คเพลนสงวนไว้สำหรับตัวควบคุมบัส ซึ่งถูกกำหนดให้ทำหน้าที่อนุญาโตตุลาการและการซิงโครไนซ์ บนขั้วต่อจะใช้บัส จำนวนที่มากขึ้นติดต่อมากกว่าคนอื่นๆ สำหรับบอร์ดขนาดใหญ่ ตัวเชื่อมต่อ J2 จะถูกปล่อยให้ใช้งานตามดุลยพินิจของผู้ใช้ (ผู้พัฒนา) และสามารถติดตั้งตัวเชื่อมต่อ 95 พิน J3 ระหว่างตัวเชื่อมต่อ J1 และ J2 ได้ การออกแบบขั้วต่อทำให้ J2 สามารถใช้การดัดแปลงเฉพาะได้ ซึ่งอาจรวมถึงหน้าจอแยกและปุ่มทางกล เป็นต้น ยางมีมาให้ด้วย แหล่งข้อมูลอิสระจ่ายไฟ +5 V, +3.3 V และ +/-12 V.

การปฏิวัติระบบจัดเก็บข้อมูลสมัยใหม่เป็นไปไม่ได้หากไม่มีการพัฒนาอินเทอร์เฟซที่ดิสก์เชื่อมต่อกับระบบ หนึ่งใน "ฮีโร่" หลักของส่วนหน้านี้คือบัส PCI Express ไดรฟ์ความเร็วสูงในปัจจุบันใช้งานได้ด้วย อินเตอร์เฟซ PCIe Gen2 x4 ให้ความเร็วสูงถึง 20 Gb/s แต่ก็ไม่ได้เป็นเช่นนั้นเสมอไป

จุดเริ่มต้นของ “ยาง” ยุคใหม่ค่ะ คอมพิวเตอร์ส่วนบุคคลควรพิจารณาปี 2525 ในส่วนลึกของไอบีเอ็มถือกำเนิดขึ้น คอมพิวเตอร์เครื่องใหม่หนึ่งใน คุณสมบัติที่โดดเด่นซึ่งเป็นความเปิดกว้างของสถาปัตยกรรม คอมพิวเตอร์ถูกเรียกว่าพีซีและสื่อสารกับ โลกภายนอกมันอยู่บนอินเทอร์เฟซใหม่ทั้งหมดซึ่งเรียกว่า Industry Standard Architecture หรือ ISA ยางรุ่นนี้สามารถทำงานกับข้อมูล 8 บิตที่ความถี่ 4.77 MHz หลังจากนั้นมีตัวเลือก 16 และ 32 บิตปรากฏขึ้นทำงานได้มากยิ่งขึ้น ความถี่สูง- มาก วงจรง่ายๆอินเทอร์เฟซนี้เป็นแรงผลักดันในการพัฒนามวลชน บอร์ดภายนอกการขยายตัว และเราสามารถพูดได้ว่าอะไรกันแน่ โปรโตคอลแบบเปิดรถบัสภายนอกกลายเป็นหนึ่งในสาเหตุหลักที่ทำให้สถาปัตยกรรมใหม่ประสบความสำเร็จในขณะนั้น

ไม่น่าแปลกใจเลยที่ ISA ยังคงความนิยมมาเป็นเวลานาน และถึงแม้ตอนนี้พวกเขาจะขายได้ในราคาที่ค่อนข้างสูงก็ตาม เมนบอร์ดด้วยการสนับสนุนของบัสนี้ - มีการเชื่อมต่ออุปกรณ์ที่ไม่สามารถถูกแทนที่ได้มากเกินไป

ตาม ISA ได้มีการพัฒนาอินเทอร์เฟซอนุพันธ์จำนวนหนึ่ง เริ่มต้นด้วย PCMCIA และลงท้ายด้วย ATA (โดยพื้นฐานแล้วเป็นชุดย่อยที่เรียบง่ายของอินเทอร์เฟซ ISA) ตัวเลือกบัสเร่งได้รับการพัฒนา: EISA (32 บิต, 8 MHz) และ VESA Local Bus (ใช้เพื่อเชื่อมต่ออะแดปเตอร์วิดีโอ)

เมื่อเวลาผ่านไป IBM สูญเสียบทบาทผู้นำในการพัฒนาพีซี ดังนั้นวิศวกรจึงทำงานกับอินเทอร์เฟซรุ่นต่อไปอยู่แล้ว อินเทล- ในช่วงต้นยุค 90... ได้รับการพัฒนา มาตรฐานใหม่เรียกว่า Peripheral Component Interconnect หรือ PCI ในปี 1992 มาตรฐาน PCI แรกเริ่มเห็นแสงสว่าง และในขณะเดียวกันก็มีการก่อตั้ง PCI Special Interest Group ซึ่งเป็นองค์กรที่อุทิศตนเพื่อการพัฒนาและส่งเสริมมาตรฐานนี้ มาตรฐานนี้ได้รับการประกาศว่าเปิด ดังนั้นใครๆ ก็สามารถพัฒนาอุปกรณ์ PCI ได้โดยไม่ต้องจ่ายค่าลิขสิทธิ์

เวอร์ชันแรกของบัสรองรับ 32 และ 64 บิต ทำงานที่ความถี่ 33 เมกะเฮิรตซ์ และตามทฤษฎีแล้ว ให้ความเร็วสูงสุด 133 Mb/s (ในทางปฏิบัติประมาณ 80 Mb/s)

หลังจากเริ่มต้นชัยชนะจากตลาดเซิร์ฟเวอร์ มาตรฐานใหม่ไม่ได้พิชิตเดสก์ท็อปพีซีในทันที หนึ่งในผู้บุกเบิกการใช้งานคือ บริษัทแอปเปิ้ลซึ่งละทิ้งอินเทอร์เฟซ NuBus ในผลิตภัณฑ์ของตนในปี 95-96

อินเทอร์เฟซใหม่ได้รับความนิยมสูงสุดในปี 1995 พร้อมกับเวอร์ชัน 2.1 (เรียกอีกอย่างว่า " รถบัสขนาน PCI") การแก้ไขนี้หมายถึงการทำงานที่ความถี่ 66 MHz และความเร็วการถ่ายโอนสูงสุด 533 MB/s (สำหรับเวอร์ชัน 64 บิต) การใช้งาน PCI ปรากฏขึ้นสำหรับแพลตฟอร์มที่มีโปรเซสเซอร์ Alpha, MIPS, PowerPC, SPARC ฯลฯ

อย่างไรก็ตาม หนึ่งในนวัตกรรมหลักของ PCI คือความสามารถในการกำหนดค่าพารามิเตอร์ของอุปกรณ์โดยอัตโนมัติ Intel เรียกว่าเทคโนโลยีนี้ Plug-n-Play และด้วยการใช้งานซอฟต์แวร์ที่ "เสถียร" ผลิตภัณฑ์ของไมโครซอฟต์เทคโนโลยีนี้ได้กลายเป็นเป้าหมายของเรื่องตลกและเกร็ดเล็กเกร็ดน้อยมากมาย

บัส PCI-X ซึ่งส่วนใหญ่ใช้ในเซิร์ฟเวอร์ ถือได้ว่าเป็นความพยายามในการพัฒนาเทคโนโลยีอย่างกว้างขวาง เวอร์ชันแรกของมาตรฐานนี้ทำงานที่ความถี่ 100 และ 133 MHz และยังแนะนำกลไกการทำธุรกรรมแยกต่างหากเพื่อเพิ่มประสิทธิภาพการทำงานของการ์ดหลายใบ ปัจจุบันบางครั้งมีการใช้บัส PCI-X 2.0 ซึ่งให้การทำงานที่ความถี่ 266 และ 533 MHz

ในปี 2547 มีการเปิดตัวมาตรฐานใหม่ซึ่งคำนึงถึงปัญหาทั้งหมดของ PCI ยางใหม่ได้รับชื่อ PCI Express หรือเพียงแค่ PCIe (สิ่งสำคัญคืออย่าสับสนกับ PCI-X) เทคโนโลยีใหม่เสนอวิธีแก้ปัญหาที่น่าสนใจมากมาย

มีการควบคุมความสมบูรณ์สำหรับข้อมูลที่ส่ง

- QoS ให้แบนด์วิธที่รับประกันสำหรับอุปกรณ์ที่เชื่อมต่อ

- มีการจัดการพลังงานของอุปกรณ์ที่เชื่อมต่อและความสามารถในการถอดเปลี่ยนได้ทันที

ข้อแตกต่างที่สำคัญคือ PCIe ไม่ได้ใช้โทโพโลยี "บัส" แต่เป็นโทโพโลยี "สตาร์" นั่นคือแต่ละอุปกรณ์เชื่อมต่อกับสวิตช์ด้วยสายแยกกัน

ปริมาณงาน PCIe ลิงก์เดียวของเวอร์ชันแรกคือ 4 Gbps ในทั้งสองทิศทาง ความเร็วสูงสุดในมาตรฐาน PCIe เวอร์ชัน 4 (อยู่ระหว่างการพัฒนาและวางแผนเปิดตัวในปี 2558) อยู่ที่ 1,024 Gbit/s อย่างที่คุณเห็น PCIe มีอัตรากำไรขั้นต้นที่ดีในพารามิเตอร์นี้ แม้ว่าจะไม่จำเป็นต้องผ่อนคลาย แต่คู่แข่งก็ไม่หลับ

เมื่อเร็วๆ นี้ Jeremy Werner หนึ่งในผู้อำนวยการอาวุโสของ Flash Technologies (SandForce) ที่ LSI ให้สัมภาษณ์ที่น่าสนใจมากเกี่ยวกับ PCIe และ SSD คุณสามารถอ่านเป็นภาษาอังกฤษได้เต็มรูปแบบ แต่ฉันจะเล่าแนวคิดหนึ่งที่ดูน่าสนใจเป็นพิเศษให้ฉันฟังโดยย่อ:

ความเร็วสูงสุด อินเทอร์เฟซที่ทันสมัย SATA คือ 6 Gbit/s ในขณะที่ SATA เป็นฮาล์ฟดูเพล็กซ์ กล่าวคือ ไม่สามารถส่งและรับข้อมูลพร้อมกันได้ PCIe Gen 2 ที่ไม่หายากนักพร้อมช่องทางการถ่ายโอนข้อมูล 4 เลนให้ความเร็วสูงสุด 20 Gbit/s ต่อ โหมดดูเพล็กซ์เต็มรูปแบบ- ในความเป็นจริง PCIe เร็วขึ้นประมาณ 7 เท่า แต่เป็นแบบดั้งเดิม ฮาร์ดไดรฟ์พวกเขาไม่ต้องการอัตราข้อมูลเหล่านั้น ขณะนี้มีเพียง SSD เท่านั้นที่สามารถให้ความเร็วที่เพียงพอสำหรับ ใช้งานได้เต็มที่อินเทอร์เฟซความเร็วสูง

การผสมผสานระหว่างอินเทอร์เฟซ M.2 และที่เก็บข้อมูลแฟลชความเร็วสูงดูเหมือนจะเป็นการเปิดตัวในอนาคต ระบบย่อยของดิสก์จะไม่ใช่ปัญหาคอขวดในพีซีอีกต่อไป ตัวอย่างที่โดดเด่นสามารถให้บริการได้ คอมพิวเตอร์แอปเปิ้ล- บริษัทในฐานะผู้เล่นในกลุ่มพรีเมียม สามารถทดลองใช้โซลูชันใหม่ๆ ได้ และกลับกลายเป็นว่าประสบความสำเร็จอย่างมากในแง่ของประสิทธิภาพ แต่เนื่องจากราคาถูกฮาร์ดไดรฟ์แบบเดิมและอินเทอร์เฟซ SATA จึงไม่ยอมแพ้ง่ายๆดังนั้นการเริ่มต้นอนาคตที่สดใสจึงต้องรอเพียงเล็กน้อย

♦ MEMR# (MRDC#) - อ่านหน่วยความจำในพื้นที่ใดก็ได้สูงสุด 16 MB

♦ OWS# (SRDY#, NOWS#, ENDXFR) - ทำให้วงจรปัจจุบันสั้นลงตามความคิดริเริ่มของอุปกรณ์ที่ระบุที่อยู่

♦ MASTER* (MASTER 16#) - คำขอจากอุปกรณ์ที่ใช้ช่อง DMA 16 บิตสำหรับการควบคุมบัส เมื่อได้รับการยอมรับจาก DACK แล้ว Bus-Master ก็สามารถยึดรถบัสได้

บนรถบัส EISA ผู้ติดต่อเพิ่มเติมสล็อต (ไม่มีให้บริการสำหรับการ์ด ISA) มีการขยายข้อมูลและแอดเดรสบัสสูงสุด 32 บิตรวมถึงชุดสัญญาณที่รับประกันการส่งข้อมูลในโหมดซิงโครนัสพร้อมความเป็นไปได้ของรอบการระเบิด

6.2. บัส PCI

โลคัลบัส PCI (Peripheral Component Interconnect) - บัสเชื่อมต่อส่วนประกอบต่อพ่วงเป็นบัสขยายหลัก คอมพิวเตอร์สมัยใหม่- ได้รับการออกแบบโดยคำนึงถึง Pentium แต่ยังทำงานได้ดีกับโปรเซสเซอร์ 486 ปัจจุบัน PCI เป็นบัสขยายที่ได้มาตรฐาน ประสิทธิภาพสูง และเชื่อถือได้ PCI 1.0 เวอร์ชันแรกปรากฏในปี 1992 PCI 2.0 (1993) แนะนำข้อกำหนดสำหรับตัวเชื่อมต่อและการ์ดเอ็กซ์แพนชัน เวอร์ชัน 2.1 (1995) เปิดตัวความถี่ 66 MHz ปัจจุบันข้อกำหนด PCI 2.2 มีผลบังคับใช้ (ธันวาคม 2541) ซึ่งชี้แจงและชี้แจงข้อกำหนดบางประการของเวอร์ชันก่อนหน้า 2.1 คำอธิบายนี้อิงตามข้อความของมาตรฐาน PCI Local Bus Specification ฉบับแก้ไข 2.2" ลงวันที่ 17 ธันวาคม พ.ศ. 2541 เผยแพร่โดย PCI SIG (กลุ่มความสนใจพิเศษ)

ในตอนแรก บัส PCI ถูกนำมาใช้เป็นส่วนขยาย (บัสชั้นลอย) ให้กับระบบที่มีบัส ISA หลัก ต่อมากลายเป็นบัสกลาง: เชื่อมต่อกับบัสระบบโปรเซสเซอร์โดยบริดจ์ประสิทธิภาพสูง (“สะพานเหนือ”) ซึ่ง เป็นส่วนหนึ่งของชิปเซ็ต เมนบอร์ด- บัสขยาย I/O ที่เหลือ (ISA/EISA หรือ MCA) รวมถึงบัส X-BUS ที่มีลักษณะคล้าย ISA ในเครื่องและอินเทอร์เฟซ LPC ซึ่งชิปบอร์ดระบบเชื่อมต่ออยู่ (ROM BIOS, ตัวควบคุมการขัดจังหวะ, แป้นพิมพ์, DMA พอร์ต , COM และ LPT, NGMD และ "สิ่งเล็กน้อย") อื่น ๆ เชื่อมต่อกับบัส PCI ผ่านทางบริดจ์ "ใต้" ในมาเธอร์บอร์ดสมัยใหม่ที่มีสถาปัตยกรรมฮับ บัส PCI ได้ถูกย้ายไปยังบริเวณรอบนอก โดยไม่กระทบต่อพลังของช่องทางการสื่อสารกับโปรเซสเซอร์และหน่วยความจำ แต่ยังไม่มีการโหลดอุปกรณ์บนรถโดยสารอื่นๆ ที่มีการจราจรติดขัด

บัสเป็นแบบซิงโครนัส - สัญญาณทั้งหมดจะถูกจับโดยขอบบวก (ขอบ) ของสัญญาณ CLK ความถี่การซิงโครไนซ์ที่กำหนดคือ 33 MHz หากจำเป็น สามารถลดความถี่ลงได้ (บนเครื่องที่มีโปรเซสเซอร์ 486 จะใช้ความถี่ 20-33 MHz) ในหลายกรณี ความถี่สามารถโอเวอร์คล็อกได้สำเร็จเป็น 41.5 MHz (ครึ่งหนึ่งของความถี่ปกติ) บัสระบบ 83 เมกะเฮิรตซ์) ตั้งแต่เวอร์ชัน 2.1 เป็นต้นไป สามารถเพิ่มความถี่เป็น 66 MHz ได้โดยได้รับความยินยอมจากอุปกรณ์ทั้งหมดบนบัส ความกว้างที่กำหนดของบัสข้อมูลคือ 32 บิต ข้อมูลจำเพาะยังระบุส่วนขยายของความกว้างบิตเป็น 64 บิต ที่ความถี่บัส 33 MHz ปริมาณงานตามทฤษฎีสูงถึง 132 MB/s สำหรับบัส 32 บิต และ 264 MB/s สำหรับบัส 64 บิต ที่ความถี่การซิงโครไนซ์ 66 MHz - 264 และ 528 ตามลำดับ อย่างไรก็ตาม ค่าสูงสุดเหล่านี้จะเข้าถึงได้เฉพาะในระหว่างการส่งแพ็กเก็ต และเนื่องจากโอเวอร์เฮดของโปรโตคอล ปริมาณงานบัสเฉลี่ยทั้งหมด (สำหรับมาสเตอร์ทั้งหมด) จึงต่ำกว่า

กับ อุปกรณ์ PCIโปรเซสเซอร์สามารถสื่อสารกับคำสั่งในการเข้าถึงหน่วยความจำและพอร์ต I/O ที่ส่งไปยังพื้นที่ที่จัดสรรให้กับแต่ละอุปกรณ์ดังกล่าวในระหว่างการกำหนดค่า อุปกรณ์สามารถสร้างคำขอขัดจังหวะที่ปกปิดได้และไม่สามารถปกปิดได้ ไม่มีแนวคิดเกี่ยวกับแชนเนล DMA สำหรับบัส PCI แต่บัสเอเจนต์เองสามารถทำหน้าที่เป็นมาสเตอร์ได้ ซึ่งรองรับการแลกเปลี่ยนประสิทธิภาพสูงกับหน่วยความจำ (และไม่เพียงเท่านั้น) โดยไม่ต้องใช้ทรัพยากร

โปรเซสเซอร์กลาง ตัวอย่างเช่น การแลกเปลี่ยนสามารถเกิดขึ้นได้ โหมดดีเอ็มเอด้วยอุปกรณ์ AT A ที่เชื่อมต่อกับตัวควบคุม PCI IDE (ดูข้อ 9.2.1) ข้อกำหนด PCI กำหนดให้อุปกรณ์สามารถย้ายทรัพยากรที่ถูกครอบครองทั้งหมดภายในพื้นที่ที่อยู่ที่มีอยู่ ช่วยให้สามารถจัดสรรทรัพยากรโดยไม่มีข้อขัดแย้งในอุปกรณ์ (ฟังก์ชัน) ต่างๆ ในการควบคุมอุปกรณ์ ขอแนะนำให้ใช้เซลล์หน่วยความจำแทนพอร์ต I/O ทุกครั้งที่เป็นไปได้ สิ่งเดียวกัน อุปกรณ์ที่ใช้งานได้สามารถกำหนดค่าได้หลายวิธี โดยแมปรีจิสเตอร์กับพื้นที่หน่วยความจำหรือพื้นที่ I/O ผู้ขับขี่สามารถกำหนดได้ การตั้งค่าปัจจุบันโดยการอ่านเนื้อหาในทะเบียน ที่อยู่ฐานอุปกรณ์ - เครื่องหมายของช่องว่าง I/O จะเป็นค่าเดียวของบิต 0 (ดูข้อ 6.2.12) ไดรเวอร์ยังสามารถกำหนดหมายเลขคำขอขัดจังหวะที่อุปกรณ์ใช้ได้อีกด้วย

6.2.1. การกำหนดที่อยู่อุปกรณ์ PCI

สำหรับบัส PCI มีการใช้ลำดับชั้นของแนวคิดการกำหนดที่อยู่: บัส อุปกรณ์ ฟังก์ชัน แนวคิดเหล่านี้จะปรากฏเฉพาะเมื่อเข้าถึงรีจิสเตอร์พื้นที่การกำหนดค่า (ดูหัวข้อ 6.2.12) รีจิสเตอร์เหล่านี้เข้าถึงได้ในขั้นตอนการกำหนดค่า โดยนับอุปกรณ์ที่ตรวจพบอีกครั้ง จัดสรรทรัพยากรที่ไม่ทับซ้อนกันให้กับอุปกรณ์เหล่านั้น (พื้นที่หน่วยความจำและพื้นที่ I/O) และกำหนดหมายเลขขัดจังหวะฮาร์ดแวร์ อีกด้วย ทำงานประจำอุปกรณ์จะตอบสนองต่อคำขอตามหน่วยความจำและที่อยู่ I/O ที่กำหนดไว้ โดยจะสื่อสารกับโมดูลซอฟต์แวร์ที่เกี่ยวข้อง ที่อยู่เหล่านี้ได้รับจากบัส AD เมื่อเริ่มต้นธุรกรรมแต่ละรายการ เส้น IDSEL แยกใช้เพื่อเข้าถึงพื้นที่การกำหนดค่า อุปกรณ์ PCI คือชิปหรือการ์ดเอ็กซ์แพนชันที่เชื่อมต่อกับหนึ่งในบัส PCI และใช้สาย IDSEL เฉพาะที่เป็นของบัสนี้เพื่อระบุตัวตน อุปกรณ์สามารถเป็นมัลติฟังก์ชั่นได้นั่นคือประกอบด้วยฟังก์ชั่นที่เรียกว่ามากมาย (ตั้งแต่ 1 ถึง 8) แต่ละฟังก์ชันได้รับการจัดสรรพื้นที่การกำหนดค่า 256 ไบต์ (ดูหัวข้อ 6.2.12) อุปกรณ์มัลติฟังก์ชั่นควรตอบสนองต่อรอบการกำหนดค่าด้วยหมายเลขฟังก์ชันซึ่งมีพื้นที่การกำหนดค่าอยู่เท่านั้น ในกรณีนี้ ต้องมีหมายเลขฟังก์ชัน 0 โดยนักพัฒนาอุปกรณ์จะกำหนดหมายเลขของฟังก์ชันอื่นตามอำเภอใจ (ในช่วง 1-7) อุปกรณ์ธรรมดา (ฟังก์ชันเดียว) ขึ้นอยู่กับการใช้งาน สามารถตอบสนองหมายเลขฟังก์ชันใดๆ หรือเฉพาะฟังก์ชันหมายเลข 0 เท่านั้น

บัส PCI คือชุดของสายสัญญาณ (ดูหัวข้อ 6.2.2) เชื่อมต่อโดยตรงกับพินอินเทอร์เฟซของกลุ่มอุปกรณ์ (ช่องเสียบ, ไมโครวงจรบนแผงระบบ) ระบบอาจมีบัส PCI หลายตัวเชื่อมต่อกันด้วยบริดจ์ PCI (ดูข้อ 6.2.10) บริดจ์จะแยกสัญญาณอินเทอร์เฟซของบัสหนึ่งออกจากกันด้วยระบบไฟฟ้า โดยเชื่อมต่อสัญญาณเหล่านั้นอย่างมีเหตุผล สะพานหลักเชื่อมต่อบัสหลักเข้ากับแกนระบบ (โปรเซสเซอร์และหน่วยความจำ) รถบัสแต่ละคันมีหมายเลขรถบัสของตัวเอง (หมายเลขบัส PCI) ยางมีหมายเลขตามลำดับ รถบัสหลักมีหมายเลขเป็นศูนย์

จากมุมมองของการกำหนดค่า หน่วยที่กำหนดแอดเดรสขั้นต่ำของลำดับชั้นนี้คือฟังก์ชัน ของเธอ ที่อยู่แบบเต็มประกอบด้วยสามส่วน: หมายเลขบัส หมายเลขอุปกรณ์ และหมายเลขฟังก์ชัน รูปแบบย่อของการระบุรูปแบบ RSY:1:2 (เช่น ในข้อความ Unix OS) หมายถึงฟังก์ชัน 2 ของอุปกรณ์ 1 ที่เชื่อมต่อกับบัส PCI หลัก (0)

บัส PCI ใช้การกำหนดที่อยู่ทางภูมิศาสตร์ - หมายเลขอุปกรณ์ถูกกำหนดโดยตำแหน่งของการเชื่อมต่อ หมายเลขอุปกรณ์ (หมายเลขอุปกรณ์หรือ dev) ถูกกำหนดโดยสายบัส AD ซึ่งสายสัญญาณ IDSEL ของช่องนี้เชื่อมต่ออยู่: kADU - devO(MOCT),AD12-devl,...AD31 -dev20 ในบริเวณใกล้เคียง สล็อต PCIตามกฎแล้ว

ใช้หมายเลขอุปกรณ์ใกล้เคียง การกำหนดหมายเลขจะถูกกำหนดโดยผู้พัฒนามาเธอร์บอร์ด (หรือแบ็คเพลนแบบพาสซีฟในคอมพิวเตอร์อุตสาหกรรม) บ่อยครั้งเพื่อ

สล็อตใช้หมายเลขอุปกรณ์จากมากไปน้อยเริ่มต้นจาก 20 กลุ่มของสล็อตที่อยู่ติดกันสามารถเชื่อมต่อกับรถโดยสารที่แตกต่างกัน บนบัส PCI แต่ละตัว หมายเลขของอุปกรณ์มีความเป็นอิสระ (อาจมีอุปกรณ์ที่มีหมายเลข dev เหมือนกัน แต่ ตัวเลขที่แตกต่างกันยาง) อุปกรณ์ PCI ที่รวมอยู่ในเมนบอร์ดใช้ระบบที่อยู่เดียวกัน หมายเลขของพวกเขา "บัดกรีแน่น" ในขณะที่ที่อยู่ของเอ็กซ์แพนชันการ์ดสามารถเปลี่ยนได้โดยการย้ายไปยังช่องอื่น การ์ด PCI หนึ่งใบสามารถมีอุปกรณ์บัสเดียวเท่านั้นที่เชื่อมต่อ เนื่องจากมีสาย IDSEL เพียงเส้นเดียวเท่านั้นที่ถูกจัดสรรไว้ในสล็อต หากวางอุปกรณ์หลายตัวบนการ์ด (เช่น 4 พอร์ต การ์ดอีเทอร์เน็ต) จากนั้นคุณจะต้องติดตั้งบริดจ์ไว้

นี่เป็นอุปกรณ์ PCI ซึ่งเข้าถึงได้ผ่านสาย IDSEL ที่จัดสรรให้กับการ์ดนี้ บริดจ์นี้จะจัดระเบียบบัส PCI เพิ่มเติมบนการ์ด ซึ่งสามารถเชื่อมต่ออุปกรณ์จำนวนมากได้

จากมุมมองของการเข้าถึงหน่วยความจำและพื้นที่ I/O ที่อยู่ทางภูมิศาสตร์ (หมายเลขบัสและอุปกรณ์) นั้นไม่แยแส (ไม่คำนึงถึงความแตกต่างด้านประสิทธิภาพที่เกี่ยวข้องกับอุปกรณ์ที่เชื่อมต่อกับบัส PCI ที่แตกต่างกัน) อย่างไรก็ตาม หมายเลขอุปกรณ์จะกำหนดจำนวนบรรทัดคำขอขัดจังหวะที่อุปกรณ์สามารถใช้ได้ สำหรับข้อมูลเพิ่มเติม โปรดดูย่อหน้าที่ 6.2.6 ที่นี่ เราทราบว่าบนบัสเดียวกัน อุปกรณ์ที่มีตัวเลขต่างกัน 4 จะใช้บรรทัดขัดจังหวะเดียวกัน ความสามารถในการกำหนดเส้นทางไปยังสายขัดจังหวะที่แตกต่างกันสามารถปรากฏได้ก็ต่อเมื่ออยู่บนรถบัสที่แตกต่างกัน (ขึ้นอยู่กับเมนบอร์ด)

คุณสามารถทราบจำนวนอุปกรณ์และสายการขัดจังหวะที่พวกเขาได้รับบนบอร์ดเฉพาะได้: ติดตั้งอุปกรณ์หนึ่งเครื่อง การ์ด PCIลงในแต่ละช่องทีละช่อง (โดยปิดเครื่อง) และดูข้อความอุปกรณ์ PCI ที่ตรวจพบซึ่งแสดงขึ้นเมื่อสิ้นสุดการทดสอบ POST ข้อความเหล่านี้จะรวมถึงอุปกรณ์ PCI ที่ติดตั้งบนเมนบอร์ดโดยตรงด้วย (และไม่ได้ปิดใช้งานโดยพารามิเตอร์การตั้งค่า CMOS)

แต่เพื่อไม่ให้มีภาพลวงตาของความเรียบง่ายและโปร่งใส เราจึงสังเกตว่า “ฉลาดเป็นพิเศษ” ระบบปฏิบัติการ(Windows) ไม่พอใจกับการกำหนดหมายเลขขัดจังหวะที่ได้รับและเปลี่ยนแปลงได้ตามดุลยพินิจของตนเอง (ซึ่งจะไม่ส่งผลกระทบต่อการแยกบรรทัดในทางใดทางหนึ่ง)

6.2.2. โปรโตคอลบัส PCI

แต่ละธุรกรรม (การแลกเปลี่ยนบนบัส) เกี่ยวข้องกับอุปกรณ์สองเครื่อง - ผู้ริเริ่มการแลกเปลี่ยนหรือที่เรียกว่าอุปกรณ์หลัก และอุปกรณ์เป้าหมายหรือที่เรียกว่าทาส บัส PCI ถือว่าธุรกรรมทั้งหมดเป็นแพ็กเก็ต: แต่ละธุรกรรมเริ่มต้นด้วยเฟสที่อยู่ ซึ่งสามารถตามด้วยเฟสข้อมูลตั้งแต่หนึ่งเฟสขึ้นไป องค์ประกอบและวัตถุประสงค์ของสัญญาณอินเทอร์เฟซบัสแสดงไว้ในตาราง 1 6.11.

ตารางที่ 6.11. สัญญาณบัส PCI | ||

วัตถุประสงค์ | ||

ที่อยู่/ข้อมูล - ที่อยู่แบบมัลติเพล็กซ์/บัสข้อมูล เมื่อเริ่มต้นการทำธุรกรรม ที่อยู่จะถูกส่งไปยัง |

||

ข้อมูลรอบถัดไป | ||

Command/Byte Enable - คำสั่ง/สิทธิ์ในการเข้าถึงไบต์ คำสั่งที่กำหนดประเภทของคิว |

||

วงจรบัส ระบุด้วยรหัสสี่บิตในเฟสที่อยู่ | ||

กรอบ. การแนะนำสัญญาณถือเป็นจุดเริ่มต้นของการทำธุรกรรม (เฟสที่อยู่) การลบสัญญาณบ่งชี้ว่า |

||

วงจรข้อมูลที่ตามมาจะเป็นรอบสุดท้ายในธุรกรรม |

||

เลือกอุปกรณ์- อุปกรณ์ที่เลือก (การตอบสนองของ CP ต่อธุรกรรมที่จ่าหน้าถึงมัน) |

||

Initiator Ready - ความพร้อมของอุปกรณ์หลักสำหรับการแลกเปลี่ยนข้อมูล |

||

Target Ready - ความพร้อมของศูนย์ควบคุมสำหรับการแลกเปลี่ยนข้อมูล | ||

ขอให้มาสเตอร์หยุดการทำธุรกรรมปัจจุบัน |

||

สัญญาณการจับบัสเพื่อให้แน่ใจว่าการทำงานสอดคล้องกัน ใช้สำหรับสร้างสะพานนั่นเอง |

||

จำเป็นต้องมีธุรกรรม PCI หลายรายการเพื่อให้การดำเนินการเดียวเสร็จสมบูรณ์ |

||

Request - คำขอจากอุปกรณ์หลักเพื่อยึดรถบัส | ||

Grant - มอบการควบคุมบัสให้กับมาสเตอร์ |

||

ความเท่าเทียมกัน - บิตความเท่าเทียมกันทั่วไปสำหรับบรรทัด AD และ C/BE# |

||

PRSNT# ปัจจุบัน - ตัวบ่งชี้สถานะของบอร์ดที่เข้ารหัสคำขอการใช้พลังงาน บนการ์ดเอ็กซ์แพนชัน เส้น LED หนึ่งหรือสองเส้นเชื่อมต่อกับบัส GND ซึ่งเมนบอร์ดตรวจจับได้

รีเซ็ต - รีเซ็ตการลงทะเบียนทั้งหมดเป็นสถานะเริ่มต้น |

|

การเลือกอุปกรณ์เริ่มต้น - การเลือกอุปกรณ์ในรอบการกำหนดค่า |

|

การอ่านและการเขียน |

|

ข้อผิดพลาดของระบบ - ข้อผิดพลาดของระบบ ข้อผิดพลาดพาริตีที่อยู่ของข้อมูลในลูปพิเศษหรืออื่นๆ |

|

ข้อผิดพลาดร้ายแรงที่ตรวจพบโดยอุปกรณ์ เปิดใช้งานโดยอุปกรณ์ PCI และสาเหตุ |

|

คำขอ 64 บิต - คำขอการแลกเปลี่ยน 64 บิต สัญญาณเข้า 64 บิต |

|

ตัวเริ่มต้น มันจะเกิดขึ้นพร้อมกับสัญญาณ FRAME* ระหว่างการรีเซ็ตเสร็จสมบูรณ์ (สัญญาณ |

|

RST*) จะส่งสัญญาณไปยังอุปกรณ์ 64 บิตที่เชื่อมต่อกับบัส 64 บิต ถ้าเป็น 64 บิต |

|

หากอุปกรณ์ตรวจไม่พบสัญญาณนี้ จะต้องกำหนดค่าใหม่เป็นโหมด 32 บิตโดยการปิดใช้งาน |

|

วงจรบัฟเฟอร์ไบต์สูง |

|

การยืนยันการแลกเปลี่ยน 64 บิต สัญญาณถูกป้อนเข้าโดย CPU 64 บิต ซึ่งรับรู้ที่อยู่ของมันพร้อมๆ กัน |

|

การพัฒนา* การไม่มีการยืนยันนี้จะบังคับให้ผู้ริเริ่มทำการแลกเปลี่ยนแบบ 32 บิต |

INTA#, INTB*, Interrupt A, B, C, D - อินเทอร์รัปต์บรรทัดคำขอ, ระดับความไว, INTC#, INTD* ระดับแอ็คทีฟ - ต่ำ ซึ่งช่วยให้สามารถแยก (แบ่งปัน) ของบรรทัดได้

วัตถุประสงค์ | ||

Snoop Done - ส่งสัญญาณว่าวงจร Snoop เสร็จสมบูรณ์สำหรับธุรกรรมปัจจุบัน ระดับต่ำบ่งชี้ |

||

ความไม่สมบูรณ์ของวงจรการตรวจสอบการเชื่อมโยงกันของหน่วยความจำแคช สัญญาณเสริม ใช้เท่านั้น |

||

อุปกรณ์และบัสที่มีหน่วยความจำแคช |

||

Snoop Backoff - การเข้าถึงหน่วยความจำปัจจุบันของผู้สมัครสมาชิกบัส |

||

ไปยังบรรทัดแคชที่แก้ไข สัญญาณเสริม ใช้โดยสมาชิกบนบัสที่แคชได้เท่านั้น |

||

หน่วยความจำพร้อมอัลกอริธึมการเขียนกลับ |

||

นาฬิกาทดสอบ - การซิงโครไนซ์อินเทอร์เฟซการทดสอบ JTAG |

||

ทดสอบการป้อนข้อมูล - ข้อมูลอินพุตอินเทอร์เฟซการทดสอบ JTAG |

||

ทดสอบข้อมูลเอาต์พุต - ข้อมูลเอาต์พุตอินเทอร์เฟซทดสอบ JTAG |

||

ทดสอบ เลือกโหมด- การเลือกโหมดสำหรับอินเทอร์เฟซการทดสอบ JTAG |

||

ทดสอบลอจิกรีเซ็ต - รีเซ็ตลอจิกทดสอบ |

||

ในช่วงเวลาใดก็ตาม บัสสามารถควบคุมได้โดยอุปกรณ์หลักเพียงตัวเดียวเท่านั้น ซึ่งได้รับสิทธิ์ในการดำเนินการดังกล่าวจากผู้ชี้ขาด อุปกรณ์หลักแต่ละตัวจะมีสัญญาณคู่กัน - REQ# เพื่อร้องขอการควบคุมบัส และ GNT* เพื่อยืนยันว่าได้รับการควบคุมบัสแล้ว อุปกรณ์สามารถเริ่มธุรกรรมได้ (ตั้งค่าสัญญาณ FRAME*) เมื่อสัญญาณ GNT* ที่ได้รับทำงานอยู่เท่านั้น การลบสัญญาณ GNT* จะป้องกันไม่ให้อุปกรณ์เริ่มธุรกรรมถัดไป และภายใต้เงื่อนไขบางประการ (ดูด้านล่าง) จะทำให้อุปกรณ์ยุติธุรกรรมปัจจุบัน การอนุญาโตตุลาการคำขอใช้บัสได้รับการจัดการโดยโหนดพิเศษที่รวมอยู่ในชิปเซ็ตของเมนบอร์ด แผนการจัดลำดับความสำคัญ (แบบตายตัว แบบพบกันหมด แบบรวม) จะถูกกำหนดโดยโปรแกรมผู้ชี้ขาด

เส้น AD แบบมัลติเพล็กซ์ทั่วไปใช้สำหรับที่อยู่และข้อมูล บรรทัด C/BE แบบมัลติเพล็กซ์สี่บรรทัดให้การเข้ารหัสคำสั่งในเฟสที่อยู่และความละเอียดไบต์ในเฟสข้อมูล เมื่อเริ่มต้นธุรกรรม อุปกรณ์หลักจะเปิดใช้งานสัญญาณ FRAME* ส่งที่อยู่เป้าหมายผ่านบัส AD และข้อมูลผ่านบรรทัด C/BE#

เกี่ยวกับประเภทธุรกรรม (คำสั่ง) ศูนย์ควบคุมที่ได้รับการตอบสนองจะตอบสนองต่อสัญญาณ DEVSEL* อุปกรณ์หลักบ่งบอกถึงความพร้อมในการแลกเปลี่ยนข้อมูลกับสัญญาณ IRDY# โดยสามารถตั้งค่าความพร้อมนี้ได้ก่อนรับ DEVSEL* เมื่อศูนย์ควบคุมพร้อมที่จะแลกเปลี่ยนข้อมูล ศูนย์จะตั้งค่าสัญญาณ TRDY* ข้อมูลจะถูกส่งบนบัส AD เฉพาะเมื่อมีสัญญาณ IRDY# และ TRDY* ปรากฏพร้อมกันเท่านั้น ด้วยความช่วยเหลือของสัญญาณเหล่านี้ อุปกรณ์หลักและศูนย์ควบคุมจะประสานความเร็วกันโดยแนะนำรอบการรอ ในรูป รูปที่ 6.7 แสดงแผนภาพเวลาของการแลกเปลี่ยนซึ่งทั้งอุปกรณ์หลักและศูนย์ควบคุมเข้าสู่รอบการรอ หากทั้งคู่ป้อนสัญญาณที่พร้อมเมื่อสิ้นสุดเฟสที่อยู่และไม่ได้ลบออกจนกว่าจะสิ้นสุดการแลกเปลี่ยน จากนั้นในแต่ละรอบสัญญาณนาฬิกาหลังจากเฟสที่อยู่จะมีการส่งข้อมูล 32 บิต ซึ่งจะให้ประสิทธิภาพการแลกเปลี่ยนสูงสุด

จำนวนเฟสข้อมูลในแพ็กเก็ตไม่ได้ระบุอย่างชัดเจน แต่ก่อนเฟสข้อมูลสุดท้าย อุปกรณ์หลัก เมื่อใส่สัญญาณ IRDY* จะลบสัญญาณ FRAME* ออก ในการทำธุรกรรมครั้งเดียว สัญญาณ FRAME* จะทำงานเพียงรอบสัญญาณนาฬิกาเดียวเท่านั้น หากอุปกรณ์ไม่รองรับธุรกรรมแบตช์ในโหมดทาส อุปกรณ์จะต้องขอให้ยุติธุรกรรมแบตช์ในระหว่างเฟสข้อมูลแรก (โดยการป้อนสัญญาณ STOP* ในเวลาเดียวกันกับ TRDY*) เพื่อตอบสนองต่อสิ่งนี้ อุปกรณ์หลักจะยุติการทำงาน ธุรกรรมนี้และจะดำเนินการแลกเปลี่ยนธุรกรรมครั้งต่อไปด้วยมูลค่าที่อยู่ใหม่ต่อไป หลังจากเฟสข้อมูลสุดท้าย อุปกรณ์โฮสต์จะลบสัญญาณ IRDY# และบัสจะเข้าสู่สถานะว่าง (PCI Idle) - ทั้งสัญญาณ FRAME* และ IRDY# อยู่ในสถานะแพสซีฟ ผู้ริเริ่มสามารถเริ่มธุรกรรมถัดไปโดยไม่มีช่วงพักโดยการเข้าสู่ FRAME* พร้อมกับถอน IRDY# ธุรกรรมที่อยู่ติดกันอย่างรวดเร็ว (Fast Back-to-Back) สามารถแก้ไขได้ที่ศูนย์กลางแห่งเดียวหรือแห่งอื่น ประเภทแรกรองรับโดยอุปกรณ์ PCI ทั้งหมดที่ทำหน้าที่เป็นหน่วยควบคุมกลาง การสนับสนุนประเภทที่สอง (เป็นทางเลือก) จะแสดงด้วยบิต 7 ของการลงทะเบียนสถานะ (ดูหัวข้อ 6.2.12) ผู้ริเริ่มจะได้รับอนุญาต (ถ้าทำได้) เพื่อใช้ธุรกรรมที่ต่อเนื่องกันอย่างรวดเร็วกับอุปกรณ์ต่างๆ (บิต 9 ของรีจิสเตอร์คำสั่ง) เฉพาะในกรณีที่ตัวแทนบัสทั้งหมดอนุญาตให้มีการโทรที่รวดเร็ว

ข้าว. 6.7. วงจรการสื่อสารบนบัส PCI

บัสช่วยให้คุณลดพลังงาน (กระแส) ที่ใช้โดยอุปกรณ์ โดยต้นทุนของประสิทธิภาพที่ลดลง โดยใช้การสลับบรรทัด AD และ PAR ทีละขั้นตอน (การก้าวที่อยู่/ข้อมูล) มีสองตัวเลือกที่เป็นไปได้ที่นี่

ผู้ให้ข้อมูลที่ถูกต้อง (FRAME# ในเฟสที่อยู่, IRDY# หรือ TRDY# ในเฟสข้อมูล) ในช่วงสองสามรอบสัญญาณนาฬิกาเหล่านี้ สัญญาณจะ "คืบคลาน" ไปยังค่าที่ต้องการที่กระแสไฟต่ำลง

♦ Discrete Stepping - Shaper ปกติจะไม่ถูกทริกเกอร์ทั้งหมดในคราวเดียว แต่เป็นกลุ่ม (เช่น ไบต์ต่อไบต์) ในแต่ละรอบสัญญาณนาฬิกาทีละกลุ่ม ในเวลาเดียวกัน กระแสไฟกระชากจะลดลง เนื่องจากมีการเปลี่ยนไดรเวอร์น้อยลงในเวลาเดียวกัน