Habari za jumla

Ukweli kwamba Intel inakusudia kuhamisha kwa utaratibu kazi zilizotekelezwa hapo awali katika seti za mantiki kwa processor ikawa wazi zaidi ya miaka miwili iliyopita. Wasindikaji wa kwanza walio na usanifu mdogo wa Nehalem - Bloomfield - walipata kidhibiti cha kumbukumbu kilichojengwa. Katika kizazi kijacho, Lynnfield, mtawala wa basi aliongezwa kwa mtawala wa kumbukumbu PCI Express. Kisha, huko Clarkdale, msingi wa picha uliojengwa ulionekana kwenye processor, ingawa ilitekelezwa na kioo tofauti cha semiconductor. Sandy Bridge huweka miguso ya mwisho kwenye muunganisho huu thabiti - vichakataji vilivyo na usanifu mpya mpya vitakuwa na kila kitu mara moja kwenye chip moja: cores za kichakataji, msingi wa michoro, kidhibiti kumbukumbu na kidhibiti basi cha PCI Express.

Eneo la fuwele za semiconductor za Sandy Bridge litakuwa takriban mita za mraba 225. mm, yaani, shukrani kwa kisasa 32 nm mchakato wa kiteknolojia fuwele hii itakuwa ndogo hata kuliko kioo cha vichakataji vya quad-core Bloomfield na Lynnfield au Gulftown ya sita-msingi.

Hakuna maelewano katika suala la utendakazi katika Sandy Bridge. Muundo wa jumla wa wasindikaji unadhani uwepo wa vichaka viwili au vinne vinavyoungwa mkono na teknolojia ya Hyper-Threading, kashe ya ngazi ya tatu ya hadi 8 MB, kidhibiti cha kumbukumbu cha DDR3 cha njia mbili, msaada kwa njia 16 za PCI Express 2.0 na uwepo wa msingi wa kisasa wa DirectX 10.1. Hiyo ni, wasindikaji wa kizazi kipya wana kila kitu wanachohitaji kufanya katika sehemu tofauti za soko, ikiwa ni pamoja na wale wa juu.

Kinyume na hali ya nyuma ya ujumuishaji katika Sandy Bridge, maboresho makubwa yamefanywa katika kiwango cha chini. Usanifu mdogo wa cores za kompyuta umefanywa upya kwa kiasi kikubwa; wamepokea maboresho kadhaa, shukrani ambayo wasindikaji wapya watakuwa haraka zaidi kuliko watangulizi wao, hata wakati wa kufanya kazi kwa kasi ya saa sawa. Wakati huo huo, maboresho yalifanywa ili kupunguza uzalishaji wa joto, ili Sandy Bridge iweze kufanya kazi kwa masafa ya juu. Kwa kuongeza, katika ngazi ya usanifu wa microarchitectural, wasindikaji wameongeza msaada kwa seti mpya ya maelekezo ya vector AVX (Advanced Vector Extensions), ambayo itakuwa muhimu kwa kutekeleza idadi ya multimedia, algorithms ya kifedha au kisayansi. Tofauti ya msingi kati ya AVX na seti za awali za maagizo ya vector katika familia ya SSE ni ongezeko la upana wa operand kutoka kwa bits 128 hadi 256, ili kwa kazi nyingi watafanya iwezekanavyo kusindika kiasi kikubwa cha data kwa gharama za chini. Kwa hivyo, Daraja la Mchanga linaweza kutambuliwa kama hatua muhimu mbele katika pande kadhaa kwa wakati mmoja, ambayo inatoa misingi ya kauli za kupendeza zaidi kuhusu bidhaa hii ya kuahidi.

Kwa kuzindua Sandy Bridge mapema mwaka ujao, Intel inatarajia kushinda haraka idadi kubwa ya sehemu za bei. Kwa hivyo, mwanzoni mwa mwaka, anuwai ya Core i3, Core i5 na Core i7 na usanifu mpya, gharama. chaguzi mbalimbali ambayo itakuwa kati ya $100 hadi $300. Na baadaye mwaka wa 2011, marekebisho ya bei nafuu yatawasilishwa.

Kulingana na data inayopatikana, tangazo la kundi la kwanza la wawakilishi wa familia ya Sandy Bridge limepangwa Januari 5, na kuanza kwa mauzo yao ni Januari 9. Siku hii, orodha ya bei ya kampuni itajazwa tena na miundo ifuatayo ya quad-core iliyoundwa kwa ajili ya kompyuta za mezani:

Ikumbukwe kwamba kwa kuongeza hapo juu Mifano ya Intel pia itatoa darasa zima la vichakataji vya Sandy Bridge vinavyotumia nishati kwenye simu na eneo-kazi. Kwa kuzingatia matoleo yanayolenga eneo-kazi, tunaweza pia kuripoti Daraja kadhaa za Mchanga zitakazozinduliwa mnamo Januari 5 na TDP za kawaida za 65, 45, na 35 W.

Kwa hivyo, kitengo cha bei pekee ambacho kitabaki kutawaliwa na wasindikaji wa Nehalem kwa muda mrefu ni CPU za gharama kubwa, ambapo wasindikaji wa LGA1366 Bloomfiled na Gulftown wataendelea kunukuliwa katika mwaka mzima ujao. Uingizwaji wao unaweza kutokea mapema zaidi ya mwisho wa 2011, wakati Intel inatayarisha na kurekebisha jukwaa lake la kuahidi la LGA2011 la kompyuta za mezani. Tofauti maalum za processor "zinazoshtakiwa". Sandy Bridge-E, ambayo itatolewa kama sehemu ya jukwaa hili, itaweza kutoa wanaopenda hadi cores 8 za kompyuta, kashe ya 16-MB L3, kidhibiti cha kumbukumbu cha njia nne, njia 32 za PCI Express 2.0 na "vizuri" vingine ambavyo mtu anaweza. ndoto tu ya leo. Walakini, haya ni matarajio ya mbali; toleo la kwanza la Sandy Bridge litakuwa msingi wa jukwaa la kawaida zaidi, lakini bado jipya.

Ingawa Sandy Bridge haikuanzisha nodi zozote mpya ikilinganishwa na Clarkdale, kizazi kipya cha wasindikaji kitakuja sokoni pamoja na jukwaa la LGA1155. Kwa bahati mbaya, haiendani na LGA1156, kumaanisha wasindikaji wapya watahitaji matumizi ya bodi maalum za mama na tundu maalum la processor.

Pamoja na Sandy Bridge, familia ya chipsets mpya pia itatumika, uti wa mgongo ambao utakuwa chipset ya Intel P67 inayotumiwa kwa kawaida na chipset ya mfumo inayoungwa mkono kwa michoro ya Intel H67. Kama vile chipsets za wasindikaji wa LGA1156, P67 na H67 ni rahisi sana: baada ya kuhamisha kazi za daraja la kaskazini kwa processor, zinajumuisha chip moja - daraja la kusini na seti ya kawaida ya sifa. Kwa kuongeza utangamano wa Sandy Bridge kipengele kikuu Bidhaa hizi mpya zitasaidia bandari mbili za SATA zenye kipimo data cha 6 Gbit/s.

Kwa bahati mbaya, hakuna msaada wa USB3 katika chipsets mpya, lakini bila shaka, idadi kubwa ya bodi za mama za LGA1155 zitakuwa na bandari zinazolingana kutekelezwa kupitia vidhibiti vya ziada. Hali hiyo hiyo inatumika kwa basi ya PCI - kukosekana kwa kidhibiti cha kawaida kinacholingana kama sehemu ya seti mpya za mantiki ya mfumo haimaanishi kabisa kwamba jadi. Viunganishi vya PCI itatoweka kwenye ubao wa mama.

Licha ya ukweli kwamba bado kuna muda uliobaki kabla ya kutangazwa kwa wasindikaji halisi na usanifu mdogo wa Sandy Bridge na jukwaa la LGA1155, taarifa zilizopo hutuwezesha kufanya utabiri maalum sana kuhusu utendaji wa mifumo ya baadaye. Kwa hivyo, wakati wa kulinganisha wasindikaji wa Sandy Bridge na Lynnfield, ambao wana idadi sawa ya cores na hufanya kazi kwa kasi ya saa sawa, microarchitecture mpya hutoa 5-10% ya juu ya utendaji halisi.

Utendaji kulingana na inpai.com.cn. Ikilinganishwa

vichakataji quad-core katika 3.4 GHz

Wakati huo huo, matumizi ya nguvu ya wasindikaji wa Sandy Bridge ni takriban 20% chini, yaani, kwa suala la utendaji kwa wati, CPU mpya zimepiga hatua mbele. Na, kwa njia, ikiwa tutazingatia kwamba masafa ya saa ya mifano ya Sandy Bridge huzidi masafa ya wasindikaji sawa wa Lynnfield kwa karibu 10%, basi tunaweza kusema kwa ujumla kwamba jukwaa lote la LGA1155 litakuwa kasi zaidi kuliko jukwaa la awali la LGA1156. angalau 25%. Nambari hii inaweza kutumika kama mwongozo wa tathmini ya juu juu ya thamani ya vitendo ya usanifu mpya, ikiwa utafunga macho yako ili kuona maboresho ya kina kama vile msingi wa michoro ulioboreshwa na usaidizi wa seti mpya za maagizo za AES-NI na AVX.

Chimbuko la Utendaji wa Juu

Mabadiliko mengi ya usanifu kwa njia ambayo wahandisi Intel Iliwezekana kufikia ongezeko la utendaji wa processor wakati kupunguza matumizi yao ya nguvu na uharibifu wa joto, ambayo ilikuwa, kusema kidogo, zisizotarajiwa. Ukweli ni kwamba Sandy Bridge haikuwa tu maendeleo zaidi ya mageuzi ya Nehalem - ilitumia idadi ya mawazo yaliyokopwa kutoka kwa mradi unaoonekana kushindwa Pentium 4. Ndiyo, ndiyo, ingawa usanifu mdogo wa NetBurst ulikataliwa kwa muda mrefu na Intel kutokana na hali yake isiyo ya kiuchumi. baadhi ya vipengele vya utendaji Wasindikaji wa Pentium 4 sasa inaweza kupatikana katika Core i3, Core i5 na Core i7. Na inashangaza sana kwamba mikopo ya Sandy Bridge kutoka kwa usanifu mdogo wa miaka kumi haitumiki tu kuboresha utendaji, lakini pia kupunguza uharibifu wa joto.Mabadiliko makubwa katika usanifu mdogo wa Sandy Bridge huanza tayari katika hatua za awali za bomba - katika hatua ya kuweka maagizo ya x86 katika uendeshaji rahisi wa processor. Kitengo cha kusimbua mkondo wa maagizo ya pembejeo yenyewe kinabakia sawa na katika Nehalem - hutoa usindikaji wa hadi maagizo 4 kwa kila mzunguko wa saa na inasaidia teknolojia za Micro-Fusion na Macro-Fusion, ambayo hufanya mtiririko wa maagizo ya pato kuwa sawa zaidi kwa suala la ugumu wa utekelezaji wake. Walakini, katika usanifu mpya wa usanifu, maagizo yaliyowekwa katika maagizo madogo ya processor hayaelekezwi tu kwa hatua inayofuata ya usindikaji, pia huhifadhiwa. Kwa maneno mengine, pamoja na kashe ya kawaida ya maagizo ya kiwango cha 32 KB, ambayo ni sifa ya karibu kichakataji chochote cha x86, Sandy Bridge imeongeza kashe nyingine ya ziada ya "ngazi ya sifuri" - kashe ya matokeo ya kusimbua. Cache hii ni rejeleo la kwanza la usanifu mdogo wa NetBurst, kwa sababu kutoka kwa mtazamo wa kanuni za jumla za utendakazi, ni analog ya moja kwa moja ya Kashe ya Ufuatiliaji ya Utekelezaji isiyoweza kukumbukwa.

Akiba ya matokeo ya kusimbua ina kiasi cha takriban 6 KB na inaweza kubeba hadi maelekezo madogo ya elfu moja na nusu, ambayo inafanya kuwa msaada mkubwa kwa avkodare. Ukweli ni kwamba sasa, ikiwa avkodare hutambua maagizo yaliyotafsiriwa hapo awali katika mkondo wa amri ya pembejeo kwenye cache, mara moja huwabadilisha na maagizo madogo ya ndani bila decoding mpya. Uwepo wa kache ya matokeo ya kusimbua hukuruhusu kupunguza kwa kiasi kikubwa mzigo kwenye decoder, ambayo ni sehemu inayotumia nishati ya processor. Kulingana na Intel, cache hii ya ziada ni muhimu kuhusu 80% ya muda, ambayo inafuta mashaka yoyote juu ya ufanisi wake. Kwa kuongeza, wakati wa kutofanya kazi, avkodare katika Sandy Bridge imezimwa, ambayo inatoa mchango mkubwa katika kupunguza matumizi ya nguvu ya wasindikaji hawa.

Uboreshaji wa pili muhimu kwa hatua za awali za bomba ni kuboresha kitengo cha utabiri wa tawi. Umuhimu wa uendeshaji sahihi wa node hii ni vigumu kuzingatia, kwa sababu kila utabiri usio sahihi wa tawi husababisha haja ya kuacha na kuweka upya bomba kabisa. Kwa hivyo, makosa ya utabiri hayajumuisha tu kupungua kwa utendakazi, lakini pia hitaji la nishati ya ziada ili kujaza tena kisafirishaji. Ni lazima kusema kuwa katika wasindikaji wake wa hivi karibuni Intel imeweza kufikia ufanisi wa juu sana wa kitengo hiki. Hata hivyo, katika Sandy Bridge, vihifadhi vyote vinavyohifadhi anwani za mabadiliko na historia yao viliundwa upya ili kushikanisha maelezo yaliyomo. Kwa hivyo, bila kuongeza ukubwa wa miundo ya data ambayo kitengo cha utabiri wa tawi hufanya kazi, Intel iliweza kufikia uhifadhi wa historia ya kina ya tawi. Na hii ilikuwa na matokeo chanya kwenye utendakazi wa kitabiri, ambacho utendakazi wake unahusiana moja kwa moja na kiasi cha maelezo ya takwimu inayotumia kuhusu mabadiliko ya masharti yanayofanywa. Inakadiriwa kuwa idadi ya matawi yaliyotabiriwa kwa usahihi imeongezeka katika Sandy Bridge ikilinganishwa na mtangulizi wake kwa zaidi ya 5%.

Lakini mabadiliko ya kuvutia zaidi yaliathiri kitengo cha kupanga upya maagizo, ambayo ni nodi muhimu ya wasindikaji wote wa Out-of-Order. Ni hapa ambapo uhusiano wa usanifu mdogo wa Sandy Bridge na NetBurst unaonekana wazi zaidi - wahandisi wa Intel walirudisha faili ya rejista ya kimwili kwa processor yao mpya, ambayo ilifutwa huko Core na Nehalem kwa ajili ya faili ya kati, tofauti ya rejista. Kiini cha mabadiliko ni kwamba ikiwa hapo awali, wakati wa kupanga upya maagizo madogo, nakala kamili za rejista walizotumia kwa kila maagizo yaliyosindika zilihifadhiwa kwenye buffer, sasa marejeleo tu ya kusajili maadili yaliyohifadhiwa kwenye faili ya rejista ya mwili hutumiwa. Njia hii sio tu kuondokana na uhamisho wa data usiohitajika, lakini pia huondoa marudio mengi ya yaliyomo kwenye rejista, ambayo huhifadhi nafasi katika faili ya rejista.

Kwa hivyo, kitengo cha utekelezaji wa amri ya nje ya vichakataji Sandy Bridge kinaweza kuweka hadi maelekezo madogo 168 "yakionekana," wakati katika vichakataji vya Nehalem ni maagizo madogo 128 pekee yaliwekwa kwenye bafa ya kupanga upya. Kwa kuongeza, baadhi ya akiba ya nishati hupatikana. Walakini, kubadilisha maadili ya rejista na marejeleo ya maadili haya pia kuna upande mbaya - bomba la utekelezaji hupata hatua za ziada zinazohitajika kwa viashiria vya kukatiza.

Lakini kwa upande wa Sandy Bridge, kwa ujumla, watengenezaji hawakuwa na chaguo lingine. Kichakataji hiki kinatanguliza maagizo mapya ya AVX ambayo yanafanya kazi kwenye rejista za 256-bit, uhamishaji mwingi ambao maadili yake yataleta mabadiliko makubwa. Na wahandisi walichukua uangalifu maalum ili kuhakikisha kuwa amri mpya zinatekelezwa katika usanifu mdogo wa Sandy Bridge kwa kasi nzuri. Utendaji wa juu wakati wa kufanya kazi nao ni ufunguo wa kukubalika kwao na watengenezaji wa programu, kwa kuwa tu katika kesi hii wanaweza kuongeza kiwango cha usawa na kupita katika mahesabu ya vector.

Maagizo ya AVX yenyewe ni maendeleo zaidi ya SSE, kupanua uwezo kidogo wa shughuli za kawaida za vector SIMD kwa uendeshaji wa 256-bit. Mbali na hilo, seti mpya inaruhusu shughuli zifanyike kwa fomu isiyo ya uharibifu, yaani, bila kupoteza data ya awali katika rejista. Shukrani kwa mali hizi, seti ya maagizo ya AVX, pamoja na uboreshaji mdogo wa usanifu, inaweza pia kuchukuliwa kuwa ubunifu unaolenga kuongeza utendaji na kuokoa nishati, kwa kuwa utekelezaji wao utarahisisha algorithms nyingi na kufanya kazi zaidi kwa kutumia. idadi ndogo amri Maagizo ya AVX yanafaa kwa matumizi ya medianuwai, kisayansi na kifedha yanayoelea-point-intensive.

Ili kutekeleza maagizo ya 256-bit kwa ufanisi, vitendaji vya processor viliundwa upya maalum. Kiini cha mabadiliko ni kwamba kufanya kazi na data 256-bit, actuators 128-bit ni pamoja katika jozi. Na kwa kuzingatia kwamba kila moja ya bandari tatu za utekelezaji za Sandy Bridge (kama Nehalem) ina vifaa vya kufanya kazi wakati huo huo na aina tatu za data - 64-bit, 128-bit integer au 128-bit halisi - mchanganyiko wa jozi wa vifaa vya SIMD ndani ya bandari moja inaonekana. kama suluhisho la asili kabisa na la busara. Na, muhimu zaidi, ugawaji upya kama huo wa rasilimali haudhuru matokeo ya jumla ya kitengo cha utekelezaji cha processor.

Mtazamo wa Sandy Bridge katika kufanya kazi na maagizo ya vekta 256 uliwalazimisha watengenezaji wasindikaji kufikiria juu ya kuongeza utendakazi. vifaa vya kazi kupakia na kupakua data. Bandari tatu za kufanya kazi na data ambazo zilitekelezwa huko Nehalem zilihamia Sandy Bridge. Lakini ili kuongeza ufanisi wao, wahandisi waliunganisha bandari mbili ambazo hapo awali zilikusudiwa kuhifadhi anwani na kupakia data. Sasa zimekuwa sawa na zote mbili zinaweza kupakia anwani na data, au kupakia anwani. Bandari ya tatu bado haijabadilishwa na imekusudiwa kuhifadhi data. Kwa kuzingatia kwamba kila bandari ina uwezo wa kupitisha hadi baiti 16 kwa kila mzunguko, jumla ya upitishaji wa kashe ya data ya kiwango cha kwanza katika usanifu mpya umeongezeka kwa 50%. Kwa hivyo, wasindikaji walio na usanifu mdogo wa Sandy Bridge wanaweza kupakia hadi baiti 32 za data na kuhifadhi baiti 16 za data kwa kila mzunguko wa saa.

Kwa kulinganisha ubunifu wote ulioelezwa, tunaona kwamba usanifu mdogo wa cores za kompyuta katika wasindikaji wa Sandy Bridge umebadilika zaidi kuliko kwa kiasi kikubwa. Ubunifu ulioletwa, bila shaka, ni karibu kabisa na ukweli kwamba wasindikaji hawa wanaweza kuhusishwa sio na uboreshaji rahisi wa vikwazo vya Nehalem, lakini kwa usindikaji mbaya sana.

Mbinu mpya za ujumuishaji

Pamoja na maendeleo ya usanifu wa Nehalem, Intel ilianza kuchukua hatua halisi kuelekea kuongeza kiwango cha ushirikiano wa wasindikaji wake. Walianza kuhamisha mfululizo vitengo vya kazi ambavyo hapo awali vilikuwa haki ya seti ya mantiki: mtawala wa kumbukumbu, Mdhibiti wa PCI Express, msingi wa michoro. Pia, cache ya ngazi ya tatu iliongezwa kwa processor. Kwa maneno mengine, processor imekuwa sio tu "kituo cha kompyuta" cha ndani, lakini mkusanyiko wa kundi kubwa la vitalu vya tata tofauti.

Bila shaka, muungano kama huo una mengi vipengele vyema na hukuruhusu kuongeza tija kwa kupunguza ucheleweshaji katika ubadilishanaji wa data. Hata hivyo, zaidi ya vitalu tofauti vilivyopo katika processor, inakuwa vigumu zaidi kutekeleza mahusiano kati yao kwenye ngazi ya umeme. Na tatizo kubwa zaidi katika suala hili ni uunganisho wa cache ya L3 iliyoshirikiwa na cores ya processor, hasa kwa kuzingatia matarajio ya ongezeko zaidi la idadi yao. Kwa maneno mengine, wakati wa kufanya kazi kwenye usanifu mdogo wa wasindikaji wa Sandy Bridge, watengenezaji walilazimika kufikiria kwa uzito juu ya kuandaa mpango wa mwingiliano rahisi kati ya vitengo vya kazi vilivyo kwenye processor. Muunganisho wa kawaida uliotumika hapo awali unaweza kutumika katika Nehalem mbili, nne na sita, lakini kwa muundo wa kichakataji wa msimu na kiasi kikubwa Haifai tena kwa punje tofauti.

Kwa kweli, hii tayari imezingatiwa katika wasindikaji wa seva-nane Nehalem-EX, ambapo kanuni ya uunganisho kati ya cores za kompyuta na cache ya L3 ilitumiwa. teknolojia mpya. Teknolojia hii, ambayo imefanikiwa kuhamia Sandy Bridge, ni basi ya pete. Katika wasindikaji wa hali ya juu, cores za kompyuta, cache, msingi wa graphics na vipengele vya northbridge vinajumuishwa na basi maalum ya pete yenye itifaki ya QPI, ambayo imefanya iwezekanavyo kupunguza kwa kiasi kikubwa idadi ya miunganisho ya intra-processor inayohitajika kwa ishara za uelekezaji.

Ili kutekeleza kwa ufanisi mwingiliano wa vitalu vya kazi vya processor na cache ya ngazi ya tatu kupitia basi ya pete, katika wasindikaji wa Sandy Bridge imegawanywa katika mabenki sawa ya 2 MB kila mmoja. Muundo wa awali unafikiri kwamba idadi ya mabenki haya inafanana na idadi ya cores ya processor. Lakini kwa madhumuni ya uuzaji, bila kuathiri uadilifu wa kache, benki zinaweza kukatwa kutoka kwa basi, na hivyo kupunguza saizi ya jumla ya kache. Kila moja ya mabenki ya kumbukumbu ya cache inadhibitiwa na msuluhishi wake mwenyewe, lakini wakati huo huo wote wanafanya kazi kwa ushirikiano wa karibu - habari haijarudiwa ndani yao. Kugawanyika katika mabenki haimaanishi kugawanya cache ya L3, inakuwezesha tu kuongeza matokeo yake, ambayo kwa matokeo hupimwa na ongezeko la idadi ya cores na, ipasavyo, mabenki. Kwa mfano, kutokana na kwamba upana wa "pete" inayotumiwa kwa uhamisho wa data ni 32 byte, kilele cha L3 cache bandwidth ya processor quad-core inayofanya kazi kwa 3.4 GHz ni 435.2 GB / s.

Basi ya pete ni nzuri sio tu kwa uzani wake kwani idadi ya cores za processor huongezeka. Kwa kuzingatia kwamba wakati wa kubadilishana habari kando ya "pete" njia fupi zaidi hutumiwa, latency ya cache L3 pia imepungua. Sasa ni mizunguko 26-31, wakati kache ya Nehalem L3 ilitoa utulivu wa mizunguko 35-40. Hata hivyo, inapaswa kuzingatiwa kuwa kumbukumbu yote ya cache katika Sandy Bridge inafanya kazi kwa mzunguko wa processor, yaani, imekuwa haraka kutokana na hili pia.

Faida nyingine iliyoletwa na basi ya pete ni kwamba ilifanya iwezekanavyo kuunganisha msingi wa graphics uliounganishwa kwenye processor kwa njia za kawaida za uhamisho wa data. Hiyo ni, graphics katika Sandy Bridge hufanya kazi na kumbukumbu sio moja kwa moja, lakini sawa na cores za processor - kupitia cache ya ngazi ya tatu. Hii huongeza utendakazi wake na pia hupunguza uharibifu ambao michoro iliyounganishwa inaweza kusababisha kwa utendakazi wa jumla wa mfumo kwa kushindana kwa basi la kumbukumbu lenye viini vya kuchakata.

Msingi wa graphics hupata vipengele vipya

Kuonekana kwa msingi wa michoro katika kichakataji si jambo geni; wasindikaji wa familia ya Clarkdale walio na Intel HD Graphics GPU wamekuwa sokoni kwa karibu mwaka mmoja. Lakini katika Sandy Bridge, michoro na cores za kompyuta hatimaye zimekuwa marafiki; ziko kwenye chip sawa cha semiconductor na zimeunganishwa na basi ya kawaida ya pete ambayo rasilimali zingine zote za kichakataji hutumiwa kwa usawa. Urekebishaji huu wa usanifu, ambao ulileta msingi wa graphics karibu na mtawala wa kumbukumbu na kuweka uwezo wake wote wa cache ya ngazi ya tatu, ulikuwa na athari nzuri juu ya utendaji. Walakini, kama viini vya kompyuta, msingi wa picha umepokea maboresho mengine muhimu, shukrani ambayo ni ya kizazi kijacho.

Kwa ujumla, usanifu wa msingi wa graphics haujawa tofauti kabisa: bado unategemea wasindikaji 12 wa mtendaji (shader). Walakini, watengenezaji waliweza karibu mara mbili ya utendaji wao kwenye idadi ya shughuli, na kwa kuongezea, walipata usawa ulioboreshwa katika kazi zao. Shukrani kwa mabadiliko yaliyofanywa, msaada wa Shader Model 4.1 na DirectX 10.1 iliongezwa kwa sifa za msingi mpya wa graphics.

Kwa kuwa msingi wa graphics ulihamia kwenye kioo cha semiconductor ya 32-nm, iliwezekana kuongeza bila maumivu mzunguko wa saa yake, ambayo inaweza kufikia hadi 1.35 GHz. Kama matokeo ya vitendo hivi vyote, picha za Sandy Bridge katika programu halisi zitalinganishwa kwa kasi na kadi za video tofauti. ngazi ya kuingia. Intel hata alifikiria juu ya kutekeleza skrini nzima ya kupinga-aliasing kwa kutumia msingi wake wa kuahidi wa michoro! Kwa maneno mengine, Sandy Bridge ina kila nafasi ya kuwa jumuishi yenye tija zaidi suluhisho la picha, ambayo itaweza kukanyaga nafasi za kadi za video zisizo na maana katika anuwai ya bei ya chini. Ingawa, kwa kweli, AMD na NVIDIA, kama hoja ya kupinga, hakika itasisitiza ukosefu wa msaada kwa DirectX 11, ambayo inaweza kuwa muhimu sio tu. michezo ya hivi punde, lakini pia, kwa mfano, programu zinazotumia DirectCompute, kama vile vivinjari vya mtandao vya kesho.

Walakini, jambo hilo halikuwa mdogo katika kuboresha tu usanifu wa msingi wa graphics uliopo. Vitalu vipya maalum vimeongezwa kwenye sehemu ya picha ya Sandy Bridge, iliyoundwa kwa ajili ya kusimbua na kusimba mitiririko ya video katika umbizo maarufu la MPEG2, VC1 na AVC.

Bila shaka, leo hutashangaza mtu yeyote aliye na usimbaji video wa maunzi; msingi wa michoro ya Clarkdale pia unaweza kuifanya. Walakini, hapo awali operesheni hii ilipewa wasindikaji wa shader, lakini sasa inashughulikiwa na kitengo tofauti cha kazi. Lengo la ugawaji upya huu wa majukumu ni upatanifu mpya na video ya 3D; kwa msingi mpya wa picha, usimbaji maunzi wa stereo 3D Blu-ray au mtiririko wa MVC hauleti tatizo lolote.

Nyongeza ya kuvutia zaidi ilikuwa kodeki ya maunzi inayoweza kusimba mtiririko wa video katika umbizo la AVC. Kwa vitendo, hii inamaanisha kuwa msingi wa michoro wa Sandy Bridge una nyenzo zote zinazohitajika ili kutekeleza upitishaji wa video kwa utendakazi wa hali ya juu bila kutumia nguvu za jadi za uchakataji. Ambayo, kwa kweli, kutokana na matumizi makubwa ya wasindikaji wa Intel, hakika itatumiwa kwa ufanisi na watengenezaji wa programu. Aidha, vitalu usimbaji wa maunzi na decoding pia inaweza kutumika katika mifumo kulingana na Intel P67 chipset, yaani, kwa kutumia nje discrete graphics kadi.

Sio lazima utafute mifano maalum: inajulikana kuwa msaada wa uwezo mpya wa media wa Sandy Bridge utakuwepo katika bidhaa maarufu kama vile ArcSoft MediaConverter, Corel DVD Factory, CyberLink MediaEspresso, Movavi Video Converter, Roxio Creator, n.k. . Na, kwa njia, wakati wa kutumia vitengo vya media titika vya msingi wa picha za Sandy Bridge kwa kupitisha video, wasindikaji wa shader hubaki bila mzigo, ambao hakuna mtu anayejisumbua kuunganisha kwenye mchakato. usindikaji wa ziada video au athari maalum.

KATIKA mifano mbalimbali wasindikaji wenye usanifu mdogo wa Sandy Bridge, msingi wa graphics utakuwepo katika matoleo mawili: Intel HD Graphics 2000 na Intel HD Graphics 3000. Tofauti ni katika idadi ya wasindikaji wa utekelezaji (shader). Mfano wa zamani wa msingi wa graphics, ambao umekusudiwa ufumbuzi wa simu na wasindikaji wakubwa wa sehemu ya "desktop" watakuwa na vitengo vyote 12 vya utekelezaji, wakati tofauti iliyorahisishwa ya msingi huu, Intel HD Graphics 2000, ina maudhui na vitengo sita tu. Pia, mzunguko wa Intel HD Graphics 2000 utakuwa chini kidogo. Lakini vipengele vya kuvutia zaidi vya GPU - encoder ya vifaa na decoder - itakuwa kikamilifu katika matoleo yote mawili.

Northbridge kwa njia mpya - wakala wa mfumo

Sehemu moja tu ya kazi ya wasindikaji wa Sandy Bridge ilibaki bila kuchunguzwa - kinachojulikana wakala wa mfumo, ambayo inachanganya vidhibiti vya miingiliano ya processor ya nje: PCI Express, DMI, kumbukumbu na miingiliano ya kuonyesha. Kwa kweli, katika mtu wa wakala wa mfumo tuna takriban kitu sawa ambacho kiliitwa Uncore katika vichakataji vya Nehalem. Hata hivyo, wakala wa mfumo katika Sandy Bridge bado si analogi kamili ya Uncore. Haijumuishi kache ya L3, ambayo katika usanifu mpya hufanya kama kitengo tofauti cha kazi kinachofanya kazi kwa mzunguko wa processor. Tofauti nyingine kati ya wakala wa mfumo ni kwamba ubadilishanaji wa data kati yake na processor na cores za michoro, na vile vile na kashe ya kiwango cha tatu, hufanyika kupitia basi moja ya pete inayounganisha vyombo vyote kwenye Sandy Bridge.

Akizungumzia kuhusu ubunifu unaopatikana katika wakala wa mfumo, kwanza kabisa ningependa kusema juu ya uboreshaji wa muda mrefu wa mtawala wa kumbukumbu. Katika vichakataji vya Westmere (Clarkdale), kidhibiti kumbukumbu pamoja na msingi wa michoro hakikufanya vizuri. upande bora. Katika Sandy Bridge, urekebishaji huu hatimaye umeondolewa; kidhibiti kipya cha kumbukumbu angalau sio polepole kuliko kidhibiti kumbukumbu cha vichakataji vya Lynnfield. Wakati huo huo, mtawala anaunga mkono njia mbili za DDR3 SDRAM: rasmi - DDR3-1067 au DDR3-1333, lakini kwa kweli wasindikaji wa Sandy Bridge wana seti ya vizidishi vinavyoruhusu kumbukumbu kufungwa kwa masafa ya 1600, 1866 na 2133. MHz.

Unaweza kufikiria kiwango cha takriban cha utendaji wa mtawala wa kumbukumbu ya Sandy Bridge, kwa mfano, kulingana na matokeo yaliyopo ya mtihani wa Aida64.

Kulingana na xfastest.com. Upimaji ulifanyika kwenye Core i7-2400 na

kumbukumbu ya njia mbili DDR3-1600 na muda 7-7-7-21-1T

Ucheleweshaji wa mfumo mdogo wa kumbukumbu katika mfumo ulio na kichakataji cha Sandy Bridge unageuka kuwa kulinganishwa na ucheleweshaji wa jukwaa sawa na vichakataji vya LGA1156 Core i7. Wakati huo huo, CPU mpya zinafaidika waziwazi katika suala la upitishaji wa mfumo mdogo wa kumbukumbu.

Kidhibiti cha basi cha PCIE katika Sandy Bridge ni sawa na kidhibiti sawa cha vichakataji vya LGA1156. Inaauni njia 16 za PCI Express 2.0, ambazo zinaweza kuunganishwa katika basi moja la PCIE 16x au mabasi mawili ya PCIE 8x. Ndiyo maana jukwaa la zamani la LGA1366 halitapoteza umuhimu wake na kutolewa kwa mifumo ya LGA1155: itaendelea kuwa chaguo pekee ambayo inakuwezesha kukusanya mifumo ndogo ya video ya kasi kamili ambayo inachanganya GPU kadhaa zilizounganishwa na basi ya PCIE yenye upeo wa juu.

Mabadiliko muhimu pia yametokea katika suala la violesura vinavyotumika. Kiini cha graphics cha wasindikaji wapya kitaweza kutumia toleo la HDMI 1.4, kipengele muhimu ambacho ni usaidizi wa maambukizi ya picha ya 3D.

Usimamizi wa nguvu na overclocking

Sehemu nyingine muhimu ya wakala wa mfumo wa Sandy Bridge, pamoja na vidhibiti vya kiolesura cha nje, ni PCU (Kitengo cha Kudhibiti Nguvu). Kama vile vichakataji vya Nehalem, kitengo hiki ni kidhibiti kidogo kinachoweza kuratibiwa ambacho hukusanya taarifa kuhusu halijoto na matumizi ya sasa ya nodi mbalimbali za vichakataji na kina uwezo wa kudhibiti masafa na usambazaji wa voltage zao kwa maingiliano. PCU hutekeleza kazi zote za kuokoa nishati na hali ya turbo, ambayo iliendelezwa zaidi katika Sandy Bridge.Moduli zote za kazi zinazounda vichakataji vya Sandy Bridge zimegawanywa katika vikoa vitatu vinavyotumia saa ya mzunguko wa kujitegemea na mzunguko wa uunganisho wa nguvu. Kikoa cha kwanza na kuu kinachanganya cores za processor na cache ya L3, ambayo inaendelea frequency moja na mvutano. Kikoa cha pili ni msingi wa graphics, ambao hutumia mzunguko wake mwenyewe. Kikoa cha tatu ni wakala wa mfumo yenyewe.

Mgawanyiko huu uliruhusu wahandisi kutekeleza Njia Iliyoboreshwa ya Intel SpeedStep na Kuongeza Turbo wakati huo huo na kwa kujitegemea kwa graphics na cores processor. Mbinu kama hiyo tayari imetumika katika wasindikaji wa simu Arrandale, lakini huko ilifanya kazi kwa njia rahisi, kupitia dereva. Katika Sandy Bridge inatekelezwa kikamilifu suluhisho la vifaa, ambayo inadhibiti mzunguko wa cores za kompyuta na graphics kwa njia iliyounganishwa, kwa kuzingatia matumizi yao ya sasa. Hii inakuwezesha kupata overclocking mbaya zaidi ya cores processor, kutekelezwa kwa njia ya turbo mode, wakati graphics msingi ni wavivu, na kinyume chake - overclocking muhimu ya msingi graphics wakati cores kompyuta si kubeba kikamilifu. Ukali wa hali ya turbo katika Sandy Bridge ni rahisi kutathmini kwa ukweli kwamba mzunguko wa processor unaweza kuongezeka kwa hatua nne kuhusiana na ilikadiriwa frequency, na tofauti katika mzunguko wa msingi wa graphics inaweza kufikia hatua sita hadi saba.

Walakini, hii sio uvumbuzi wote ndani Teknolojia ya Turbo Kuongeza. Faida yake utekelezaji mpya Pia iko katika ukweli kwamba PCU ina uwezo wa kudhibiti masafa kwa akili zaidi, kwa kuzingatia joto halisi la vipengele vya processor, na si tu matumizi yao ya nguvu. Hii ina maana kwamba wakati processor inafanya kazi chini ya hali nzuri ya joto, matumizi yake ya nguvu yanaruhusiwa kuzidi kikomo cha TDP.

Wakati wa kazi ya kawaida ya kila siku, mzigo wa processor hubadilika. Msindikaji hutumia muda mwingi katika majimbo ya kuokoa nishati, na utendaji wa juu unahitajika kwa muda mfupi tu. Wakati wa vipindi vile, inapokanzwa kwa processor haina wakati wa kufikia maadili yoyote makubwa - inertia inayotolewa na conductivity ya mafuta ya baridi huathiri. PCU inayodhibiti masafa katika Sandy Bridge inaamini kwa kufaa kuwa hakuna kitu kibaya kitakachotokea ikiwa wakati kama huo kichakataji kitazidiwa zaidi kuliko thamani ya nadharia ya uondoaji joto inavyoweza kuruhusu kinadharia. Wakati joto la processor linapoanza kukaribia maadili muhimu, mzunguko utapungua kwa maadili salama.

Hii husababisha kiotomatiki manufaa kutoka kwa mtazamo wa kufikia utendakazi wa juu zaidi kwa kutumia upoaji wa hali ya juu katika mifumo inayotegemea Sandy Bridge. Lakini usijidanganye - muda wa juu wa operesheni katika hali ya "zaidi ya TDP" ni mdogo na vifaa hadi sekunde 25.

Kuhusu overclocking ya kawaida, iliyofanywa mbinu za jadi, basi mabadiliko ya kardinali yanatungojea hapa, ambayo haiwezekani kupokea kwa shauku na overclockers. Mizizi ya uovu wote iko katika tamaa sawa ya ushirikiano - katika majukwaa ya LGA1155, Intel ilihamisha jenereta ya mzunguko wa msingi kwenye seti ya mantiki ya mfumo. Walakini, haikuwa hii ambayo ilisababisha matokeo mabaya kwa overclocking ya jadi, lakini ukweli kwamba jenereta ya mzunguko ikawa pekee na hutumiwa kuzalisha masafa yote katika mfumo. Kama unavyojua, sio mabasi na vidhibiti vyote vinavyoshughulikia overclocking vizuri. Kwa mfano, wakati wa kuongeza mzunguko wa basi wa PCI Express au kasi Uendeshaji wa USB au vidhibiti vya SATA, kutokuwa na utulivu kunaweza kutokea haraka sana. Na ni jambo hili ambalo litakuwa kikwazo kikubwa wakati wa kujaribu kuongeza mzunguko processor ya kati kwa kuongeza kasi ya jenereta ya mzunguko wa msingi.

Ukweli ni kama ifuatavyo. Masafa ya saa ya msingi inayotumika katika vichakataji vya Sandy Bridge imewekwa kuwa 100 MHz. Jenereta yenyewe hukuruhusu kubadilisha maadili ya masafa haya ndani ya anuwai kubwa na hata kwa nyongeza za 0.1 MHz. Walakini, majaribio ya kuiongeza haraka sana yanaingia katika kutokuwa na utulivu au kutofanya kazi kwa mfumo. Kwa hivyo, hatujui uzoefu wowote wa mafanikio katika kuongeza mzunguko wa msingi zaidi ya 105 MHz. Kwa maneno mengine, njia ya jadi na iliyojaribiwa kwa muda wa overclocking kwa kuongeza mzunguko wa jenereta ya saa katika mifumo kulingana na Sandy Bridge inashindwa na hairuhusu overclocking kuzidi frivolous 5%.

Kwa hivyo chaguo pekee la maana la kuzidisha vichakataji vya LGA1155 ni kuongeza sababu yao ya kuzidisha. Miongoni mwa mifano ya Sandy Bridge ambayo Intel itatoa kwa wateja, kutakuwa na bidhaa maalum ambazo hazina multiplier iliyofungwa na inaweza, kwa nadharia, kuwa overclocked hadi 5.7 GHz (57 ni thamani ya juu ya multiplier iliyojengwa katika usanifu mdogo). Walakini, wasindikaji kama hao, ambao watateuliwa na kiambishi tamati "K" katika nambari ya kichakataji, itaainishwa kama ya juu. kitengo cha bei na wakati huo huo watakuwa na gharama kidogo zaidi kuliko wenzao wa kawaida.

Kwa watumiaji wa mifano ya kawaida ya CPU, overclocking ndogo ya bandia itatolewa - wasindikaji vile pia wataruhusu ongezeko la sababu ya kuzidisha, lakini kwa si zaidi ya hatua 4 zinazohusiana na thamani ya kawaida. Kwa kuongezea, tunazungumza haswa juu ya kupindukia; kubadilisha kizidishi haitaathiri kwa njia yoyote teknolojia ya Turbo Boost, ambayo, pamoja na kuongezeka kwa masafa ya mwongozo, pia itaongeza moja kwa moja yake. Kwa kuongeza, katika wasindikaji wake wote, Intel haitapunguza vizidishi vinavyoamua mzunguko wa msingi wa graphics na kumbukumbu. Hiyo ni, overclocking msingi graphics na kumbukumbu itakuwa inapatikana katika mifumo na marekebisho yoyote Sandy Bridge - wote overclocking na mara kwa mara.

Walakini, overclockers haziwezekani kuzingatia fidia hii ya kutosha, kwa hivyo uwezekano mkubwa watakuwa na nia ya wasindikaji waliofunguliwa - Core i5-2500K na Core i7-2600K. Zaidi ya hayo, habari inayopatikana kuhusu uwezo wao wa masafa inaonekana ya kutia moyo sana. Kwa mfano, kuna ushahidi wa utendaji thabiti wa Core i7-2600K wakati wa overclocked na hadi 5.0 GHz na baridi ya hewa.

data ya windwithme, http://itbbs.pconline.com.cn/diy/12120702.html

Matokeo yaliyoelezwa yalipatikana kwa kutumia kibaridi cha Prolimatech Mega Shadow Deluxe Edition na kuongeza voltage ya msingi ya processor hadi 1.45 V. Bila shaka, ongezeko kubwa kama hilo la voltage haliwezekani kufaa kwa matumizi ya kila siku, lakini tunaamini kuwa katika masafa ya takriban Vichakataji vya 4.8 GHz Sandy Bridge vitafanya kazi kwa hali ya 24/7 bila shaka wanaweza.

Hebu tujumuishe

Tukirejea mwanzo wa makala haya, ningependa kukukumbusha kwamba Intel inaweka Sandy Bridge kama "toki" kama sehemu ya mkakati wake wa "tiki-tock". Hii ina maana kwamba, kwa mujibu wa mtengenezaji, processor hii ni carrier wa microarchitecture mpya. Wakati huo huo, kuchunguza muundo wake, hatukupata mawazo yoyote mapya ambayo yangepiga mawazo. Kwa kweli, kuna uboreshaji mdogo tu, ufufuo wa teknolojia za zamani za mafanikio na ushirikiano zaidi. Je, ni jambo la busara kuzungumza juu ya kizazi kipya cha wasindikaji katika kesi hii, au je, Bridge Bridge inapaswa kuzingatiwa tu kama Nehalem iliyobadilishwa?

Na hapa hatuna shaka - tunakubaliana kikamilifu na maoni ya Intel. Wasindikaji wa Sandy Bridge ni kielelezo bora cha kuibuka kwa ubora mpya kutokana na mkusanyiko wa mabadiliko ya kiasi. Ubunifu mwingi katika usanifu mdogo wa cores za kompyuta, nyongeza ya msaada kwa maagizo ya 256-bit AVX, msingi wa picha ulioboreshwa, kuonekana kwa vitengo vya vifaa vya usimbuaji wa video na kusimbua, kashe mpya ya L3, basi ya pete, mfumo wa akili. wakala, teknolojia kali zaidi ya Turbo Boost na kuongezeka kwa masafa ya saa - hiyo yote ni Binafsi, hii inaweza kuonekana kama kitu kidogo, lakini kwa jumla hutoa bidhaa ambayo imeboreshwa kimsingi. Zaidi ya hayo, ubora wake unaonekana kabisa - inaweza kuonekana wazi katika ukweli kwamba Sandy Bridge imekuwa kwa kasi zaidi kuliko watangulizi wake, wakati inabaki ndani ya mfuko huo wa joto.

Bila shaka, tunaposema "kwa kiasi kikubwa," hatuna maana ya ongezeko kubwa la kasi. Hata hivyo, kwa kubadilisha mfumo wa LGA1156 wa Lynnfield au Clarkdale kwa kuweka bei sawa ya ubao mama wa LGA1155 na kichakataji cha Sandy Bridge, unaweza kutarajia angalau ongezeko la 25% la utendakazi katika programu zote zinazotegemea vichakataji.

Hata hivyo, pia kuna aina fulani za matatizo ambapo Sandy Bridge itakuwa utaratibu wa ukubwa bora kuliko watangulizi wake kutokana na vitalu vipya vya miundo. Kwanza kabisa, ongezeko kubwa la utendaji linatarajiwa katika huduma nyingi za kupitisha video, kwa mahitaji ambayo codecs maalum za vifaa na decoders zimeongezwa kwa CPU mpya. Pia, algoriti za media titika, kriptografia, kisayansi au kifedha kwa kutumia seti mpya za maagizo za AES-NI na AVX zitaweza kufanya kazi kwa kasi zaidi kwenye CPU mpya. Kwa kweli, faida hizi zote zitawezekana kupata tu na uboreshaji maalum wa programu, lakini inaonekana kwamba hautalazimika kungojea kwa muda mrefu, kwani wahandisi wa Intel wamefanya kila juhudi kuhakikisha kuwa uvumbuzi ni rahisi kwa watengenezaji.

Watumiaji hao ambao wanakusudia kutumia msingi wa michoro iliyojengwa pia watafaidika sana kutoka kwa jukwaa jipya. Ikilinganishwa na toleo la awali la Picha za Intel HD, imekuwa haraka sana, ambayo wamiliki wa laptops za baadaye kulingana na Sandy Bridge na jukwaa jipya Mto Huron. Na ikiwa wasindikaji wapya wamepangwa kutumika kama sehemu ya kompyuta za nyumbani au HTPC, msingi wa graphics uliojengwa utafurahishwa na usaidizi wa interface ya HDMI 1.4, ambayo inakuwezesha kusambaza picha za 3D kwa vifaa vya nje.

Kwa ujumla, inaonekana kuwa kuna hasara moja tu kubwa katika Sandy Bridge - matatizo na overclocking. Na ikiwa wanunuzi wa wasindikaji katika kitengo cha bei ya juu wanaweza, kwa kulipa ziada kidogo, kupata processor isiyofunguliwa ya overclocking-kirafiki, basi kati ya wasindikaji wa bei nafuu zaidi ya $ 200 hakutakuwa na chaguzi hizo. Kwa hivyo jukwaa la LGA1155 litaashiria mwelekeo mwingine - Intel inataka kupunguza uwezo wa overclocking wa wasindikaji wa gharama nafuu. Walakini, hii haiwezekani kuwa na athari kubwa juu ya umaarufu wa overclocking kama jambo - wafuasi wa vifaa vya kufanya kazi hadi kikomo cha uwezo wake watakubaliwa kwa furaha kati ya wafuasi wake na AMD, ambayo mwaka huu ni kwa sababu ya kutolewa bidhaa yake mwenyewe. si chini ya epoch-making kuliko Sandy Bridge - Bulldozer.

Hatimaye, Intel imetangaza rasmi wasindikaji wapya wanaoendesha usanifu mpya. Kwa watu wengi, "tangazo la Sandy Bridge" ni maneno tu, lakini kwa kiasi kikubwa, kizazi cha Intel Core ll ni, ikiwa sio enzi mpya, basi angalau sasisho la karibu soko zima la processor.

Hapo awali iliripotiwa kuwa wasindikaji saba tu watazinduliwa, lakini kwenye ukurasa muhimu zaidi ark.intel.com habari kuhusu bidhaa zote mpya tayari imeonekana. Kulikuwa na wasindikaji kadhaa zaidi, au tuseme marekebisho yao (katika mabano nilionyesha bei ya takriban - ni kiasi gani kila processor katika kundi la vipande 1000 ingegharimu):

Rununu:

Intel Core i5-2510E (~$266)Intel Core i5-2520M

Intel Core i5-2537M

Intel Core i5-2540M

Ulinganisho wa kina wa kuona wa vichakataji vya simu vya Intel Core i5 vya kizazi cha pili.

Intel Core i7-2617M

Intel Core i7-2620M

Intel Core i7-2629M

Intel Core i7-2649M

Intel Core i7-2657M

Intel Core i7-2710QE (~$378)

Intel Core i7-2720QM

Intel Core i7-2820QM

Toleo la Intel Core i7-2920XM Uliokithiri

Ulinganisho wa kina wa kuona wa vichakataji vya simu vya Intel Core i7 vya kizazi cha pili.

Kompyuta kibao:

Intel Core i3-2100 (~$117)Intel Core i3-2100T

Intel Core i3-2120 ($138)

Ulinganisho wa kuona, wa kina wa vichakataji vya mezani vya Intel Core i3 vya kizazi cha pili.

Intel Core i5-2300 (~$177)

Intel Core i5-2390T

Intel Core i5-2400S

Intel Core i5-2400 (~$184)

Intel Core i5-2500K (~$216)

Intel Core i5-2500T

Intel Core i5-2500S

Intel Core i5-2500 (~205$)

Ulinganisho wa kuona, wa kina wa vichakataji vya mezani vya Intel Core i5 vya kizazi cha pili.

Intel Core i7-2600K (~$317)

Intel Core i7-2600S

Intel Core i7-2600 (~$294)

Ulinganisho wa kuona, wa kina wa vichakataji vya mezani vya Intel Core i7 vya kizazi cha pili.

Kama unavyoona, majina ya mfano sasa yana nambari nne kwa jina - hii inafanywa ili kuzuia kuchanganyikiwa na wasindikaji wa kizazi kilichopita. Msururu iligeuka kuwa kamili na ya kimantiki - safu ya kuvutia zaidi ya i7 imetenganishwa wazi na i5 na uwepo wa teknolojia. Hyper Threading na kuongeza ukubwa wa kashe. Na wasindikaji wa familia ya i3 hutofautiana na i5 sio tu kwa idadi ndogo ya cores, lakini pia kwa ukosefu wa teknolojia. Kuongeza Turbo.

Pengine pia umeona barua katika majina ya wasindikaji, bila ambayo mstari ulipunguzwa sana. Kwa hivyo hapa kuna barua S Na T kuzungumza juu ya kupunguza matumizi ya nguvu, na KWA – kizidishi cha bure.

Muundo unaoonekana wa wasindikaji wapya:

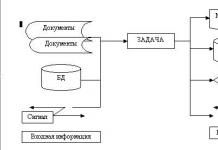

Kama unaweza kuona, kwa kuongeza picha na cores za kompyuta, kumbukumbu ya kashe na kidhibiti cha kumbukumbu, kuna kinachojulikana. Wakala wa Mfumo- vitu vingi hutupwa huko, kwa mfano, vidhibiti vya kumbukumbu vya DDR3 na PCI-Express 2.0, mfano wa usimamizi wa nguvu na vizuizi ambavyo vinawajibika kwa kiwango cha vifaa kwa uendeshaji wa GPU iliyojengwa na kwa pato la picha wakati iko. kutumika.

Vipengele vyote vya "msingi" (ikiwa ni pamoja na processor ya graphics) vinaunganishwa na basi ya pete ya kasi ya juu na upatikanaji kamili wa cache ya L3, kutokana na ambayo kasi ya kubadilishana data katika processor yenyewe imeongezeka; Kinachovutia ni kwamba mbinu hii inakuwezesha kuongeza utendaji katika siku zijazo, kwa kuongeza tu idadi ya cores zilizoongezwa kwenye basi. Ingawa hata sasa kila kitu kinaahidi kuwa bora - ikilinganishwa na wasindikaji wa kizazi kilichopita, utendaji wa mpya ni mzuri zaidi na, kulingana na mtengenezaji, katika kazi nyingi inaweza kuonyesha ongezeko la 30-50% la kasi ya utekelezaji wa kazi. !

Ikiwa ungependa kujua zaidi kuhusu usanifu mpya, basi kwa Kirusi ninaweza kupendekeza makala hizi tatu - , , .

Wasindikaji wapya wametengenezwa kabisa kulingana na teknolojia ya mchakato wa 32nm na kwa mara ya kwanza wana usanifu mdogo "unaoonekana" ambao unachanganya bora katika darasa. nguvu ya kompyuta na teknolojia ya usindikaji wa michoro ya 3D kwenye chip moja. Kuna ubunifu mwingi sana katika michoro ya Sandy Bridge, inayolenga zaidi kuongeza utendaji wakati wa kufanya kazi na 3D. Mtu anaweza kubishana kwa muda mrefu juu ya "kuweka" mfumo wa video uliojumuishwa, lakini hakuna suluhisho lingine kama hilo. Lakini kuna slaidi hii kutoka kwa uwasilishaji rasmi, ambayo inadai kuwa inakubalika, pamoja na bidhaa za rununu (laptops):

Ninazungumza kwa sehemu juu ya teknolojia mpya za kizazi cha pili cha wasindikaji wa Intel Core, kwa hivyo sitajirudia. Nitazingatia maendeleo tu Intel Insider, ambaye mwonekano wake wengi walishangaa. Kama ninavyoelewa, hii itakuwa aina ya duka ambayo itawapa wamiliki wa kompyuta ufikiaji wa filamu ufafanuzi wa juu, moja kwa moja kutoka kwa waundaji wa filamu hizi - kitu ambacho hapo awali kilionekana muda tu baada ya kutangazwa na kuonekana kwa diski za DVD au Blu-ray. Ili kuonyesha kipengele hiki, Makamu wa Rais wa Intel Muli Eden(Mooly Eden) walioalikwa jukwaani Kevin Tsujiharu(Kevin Tsujihara), Rais wa Warner Home Entertainment Group. Nanukuu:

« Warner Bros. hupata mifumo ya kibinafsi jukwaa linalotumika sana na lililoenea zaidi la kuwasilisha maudhui ya burudani ya hali ya juu, na sasa Intel inafanya jukwaa kuwa la kuaminika na salama zaidi. Kuanzia sasa na kuendelea, kwa usaidizi wa duka la WBSshop, pamoja na washirika wetu kama vile CinemaNow, tutaweza kuwapa watumiaji wa Kompyuta matoleo mapya na filamu kutoka kwa orodha yetu katika ubora wa kweli wa HD."- Muli Eden alionyesha kazi ya teknolojia hii kwa kutumia mfano wa filamu "Inception". Kwa ushirikiano na studio zinazoongoza za tasnia na kampuni kubwa za media (kama vile Best Buy CinemaNow, Hungama Digital Media Entertainment, Burudani ya Picha, Sonic Solutions, Warner Bros. Digital Distribution na zingine), Intel inaunda mfumo salama na usio na uharamia (vifaa) kwa ajili ya. usambazaji, uhifadhi na uchezaji wa video ya ubora wa juu.

« Warner Bros. hupata mifumo ya kibinafsi jukwaa linalotumika sana na lililoenea zaidi la kuwasilisha maudhui ya burudani ya hali ya juu, na sasa Intel inafanya jukwaa kuwa la kuaminika na salama zaidi. Kuanzia sasa na kuendelea, kwa usaidizi wa duka la WBSshop, pamoja na washirika wetu kama vile CinemaNow, tutaweza kuwapa watumiaji wa Kompyuta matoleo mapya na filamu kutoka kwa orodha yetu katika ubora wa kweli wa HD."- Muli Eden alionyesha kazi ya teknolojia hii kwa kutumia mfano wa filamu "Inception". Kwa ushirikiano na studio zinazoongoza za tasnia na kampuni kubwa za media (kama vile Best Buy CinemaNow, Hungama Digital Media Entertainment, Burudani ya Picha, Sonic Solutions, Warner Bros. Digital Distribution na zingine), Intel inaunda mfumo salama na usio na uharamia (vifaa) kwa ajili ya. usambazaji, uhifadhi na uchezaji wa video ya ubora wa juu.

Uendeshaji wa teknolojia iliyotajwa hapo juu itaendana na maendeleo mawili yasiyo ya chini ya kuvutia, ambayo pia yapo katika mifano yote ya wasindikaji wa kizazi kipya. Ninazungumza juu ya (Intel WiDi 2.0) na Intel InTru 3-D. Ya kwanza imeundwa kwa ajili ya upitishaji wa video wa HD bila waya (inayosaidia maazimio hadi 1080p), ya pili imeundwa kwa ajili ya kuonyesha maudhui ya stereo kwenye vichunguzi au TV za ubora wa juu kupitia muunganisho. HDMI 1.4.

Kazi mbili zaidi ambazo sikupata mahali pazuri zaidi katika kifungu - Viendelezi vya Intel Advanced Vector(AVX). Usaidizi wa kichakataji kwa amri hizi huboresha kasi ya programu zinazotumia data nyingi kama vile vihariri vya sauti na programu kwa uhariri wa picha wa kitaalamu.

... Na Video ya Usawazishaji wa Haraka ya Intel- Shukrani kwa kufanya kazi pamoja Na makampuni ya programu kama vile CyberLink, Corel na ArcSoft, kampuni kubwa ya kichakataji imeweza kuongeza utendakazi wa kazi hii (kubadilisha msimbo kati ya umbizo la H.264 na MPEG-2) kwa mara 17 ikilinganishwa na utendakazi wa kizazi cha awali cha michoro jumuishi.

Hebu sema kuna wasindikaji - jinsi ya kutumia? Hiyo ni kweli - pamoja nao, chipsets mpya (seti za mantiki) pia zilitangazwa, ambazo ni wawakilishi wa safu ya "sitini". Inavyoonekana, seti mbili tu zimehifadhiwa kwa watumiaji wenye kiu ya bidhaa mpya, hizi ni Intel H67 Na Intel P67, ambayo bodi nyingi mpya za mama zitajengwa. H67 ina uwezo wa kufanya kazi na msingi wa video uliounganishwa kwenye processor, wakati P67 ina vifaa vya Kurekebisha Utendaji kwa overclocking processor. Wasindikaji wote watafanya kazi kwenye soketi mpya, 1155 .

Ninafurahi kwamba wasindikaji wapya wanaonekana kuendana na soketi za processor za Intel na usanifu wa kizazi kijacho. Pamoja hii itakuwa muhimu kama watumiaji wa kawaida, na watengenezaji ambao hawatalazimika kuunda upya na kuunda vifaa vipya.

Kwa jumla, Intel ilianzisha zaidi ya chipsi 20, chipsets na adapta zisizotumia waya, ikijumuisha vichakataji vipya vya Intel Core i7, i5 na i3, chipsets za Intel 6 Series na adapta za Intel Centrino Wi-Fi na WiMAX. Mbali na zile zilizotajwa hapo juu, "beji" zifuatazo zinaweza kuonekana kwenye soko:

Mwaka huu, zaidi ya mifano 500 ya kompyuta za mezani na kompyuta ndogo kutoka kwa chapa zinazoongoza ulimwenguni zinatarajiwa kutolewa kwenye vichakataji vipya.

Na hatimaye, kwa mara nyingine tena video ya kupendeza, ikiwa mtu yeyote hajaiona:

![]()

Je, ubora wa Core i ya kwanza (Nehalem na, mwaka wa 2009, Westmere) juu ya CPU za wapinzani ni mwisho? Hali hiyo inawakumbusha kidogo mwaka wa kwanza baada ya kutolewa kwa Pentium II: kupumzika kwa laurels na kupokea faida ya rekodi, itakuwa nzuri kufanya uendelezaji wa usanifu wa mafanikio, bila kubadilisha jina lake sana, na kuongeza mpya, matumizi ambayo yataboresha utendaji kwa kiasi kikubwa, bila kusahau kuhusu ubunifu mwingine unaoharakisha programu za matoleo ya leo. Ukweli, tofauti na hali hiyo miaka 10 iliyopita, lazima tuzingatie mada ya sasa ya ufanisi wa nishati, iliyochezwa na kivumishi kisichoeleweka - "baridi" na "baridi" - na hamu isiyo ya kawaida ya kujumuika kwenye processor kila kitu ambacho bado kipo kama tofauti. Huu ndio mchuzi ambao bidhaa mpya hutolewa.

"Siku moja kabla ya jana", "jana" na "leo" ya wasindikaji wa Intel.

Conveyor mbele. Rangi zinaonyesha aina tofauti habari na usindikaji au kuhifadhi vitalu.

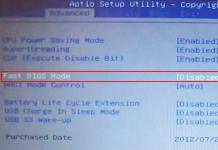

Utabiri

Wacha tuanze na tangazo la Intel la kitengo kilichoundwa upya kabisa (BPU). Kama ilivyo kwa Nehalem, kila mzunguko wa saa (na kabla ya utekelezaji halisi) inatabiri anwani ya sehemu inayofuata ya baiti 32 kulingana na tabia inayotarajiwa ya maagizo ya kuruka katika sehemu iliyotabiriwa - na, dhahiri, bila kujali nambari na aina ya mabadiliko. Kwa usahihi zaidi, ikiwa sehemu ya sasa ina mpito unaodaiwa kuanzishwa, anwani zake mwenyewe na lengwa hutolewa, vinginevyo mpito kwa sehemu inayofuata mfululizo hutolewa. Utabiri wenyewe umekuwa sahihi zaidi kwa sababu ya kuongezeka maradufu (BTB), kurefusha (GBHR) na kuboresha utendaji wa heshi ya ufikiaji (BHT). Kweli, vipimo halisi vimeonyesha kuwa katika baadhi ya matukio ufanisi wa utabiri bado ni mbaya zaidi kuliko katika Nehalem. Labda kuongeza tija kwa kupunguza matumizi hakupatani na utabiri wa mpito wa hali ya juu? Hebu jaribu kufikiri.

Katika Nehalem (pamoja na usanifu mwingine wa kisasa), BTB iko katika mfumo wa uongozi wa ngazi mbili - ndogo-"haraka" L1 na kubwa-"polepole" L2. Hii hutokea kwa sababu sawa kwa nini kuna viwango kadhaa: ufumbuzi wa ngazi moja utakuwa maelewano sana katika mambo yote (ukubwa, kasi ya majibu, matumizi, nk). Lakini katika SB, wasanifu waliamua kuweka kiwango kimoja, na ukubwa ulikuwa mkubwa mara mbili ya L2 BTB ya Nehalem, yaani, labda angalau seli 4096 - hiyo ndiyo idadi kamili ya Atom. (Inapaswa kuzingatiwa kuwa saizi ya nambari inayotekelezwa mara nyingi inakua polepole na inazidi kutoshea kwenye kashe, saizi yake ambayo ni sawa kwa Intel CPUs zote tangu Pentium M ya kwanza.) Kwa nadharia, hii itakuwa kuongeza eneo lililochukuliwa na BTB, na kwa kuwa eneo la jumla litabadilika haipendekezi (hii ni mojawapo ya postulates ya awali ya usanifu) - kitu kitatakiwa kuondolewa kutoka kwa muundo mwingine. Lakini pia kuna kasi. Kwa kuzingatia kwamba SB inapaswa kuundwa kwa kasi ya juu kidogo na mchakato huo wa kiufundi, mtu anaweza kutarajia kwamba muundo huu mkubwa utakuwa kizuizi cha conveyor nzima - isipokuwa kupitishwa pia (mbili tayari zinatosha). Kweli, jumla ya idadi ya transistors zinazofanya kazi kwa mzunguko wa saa katika BTB itakuwa mara mbili, ambayo haichangia kuokoa nishati wakati wote. Mwisho wa mauti tena? Kwa hili, Intel anajibu kwamba BTB mpya huhifadhi anwani katika aina ya hali iliyoshinikizwa, ambayo inakuwezesha kuwa na seli mara mbili na eneo sawa na matumizi. Lakini bado haiwezekani kuthibitisha hili.

Hebu tuangalie kutoka upande mwingine. SB haikupokea algoriti mpya za utabiri, lakini iliboresha za zamani: jumla, kwa mabadiliko yasiyo ya moja kwa moja, vitanzi na kurudi. Nehalem ina GBHR ya 18-bit na BHT ya ukubwa usiojulikana. Hata hivyo, tunaweza kuhakikisha kwamba idadi ya seli katika jedwali ni chini ya 2 18, vinginevyo itachukua sehemu kubwa ya msingi. Kwa hiyo, kuna kazi maalum ya hashi ambayo huanguka bits 18 za historia ya mabadiliko yote na bits za anwani ya maelekezo kwenye index ya urefu mfupi. Zaidi ya hayo, uwezekano mkubwa, kuna angalau heshi mbili - kwa bits zote za GBHR na kwa zile zinazoonyesha kuchochea kwa mabadiliko magumu zaidi. Na kwa hivyo ufanisi wa usambazaji wa machafuko wa mifumo mbali mbali ya tabia na faharisi na nambari za seli za BHT huamua mafanikio ya mtabiri. mtazamo wa jumla. Ingawa haijasemwa wazi, Intel imeboresha heshi, ikiruhusu urefu wa GBHR kutumika kwa ufanisi sawa wa kuweka pedi. Lakini bado unaweza kukisia kuhusu saizi ya BHT - na vile vile jinsi matumizi ya nishati ya kitabiri kwa ujumla yamebadilika... Kuhusu (RSB), bado ni anwani 16, lakini kizuizi kipya kimetolewa. kuletwa kwenye simu zenyewe - hakuna zaidi nne kwa byte 16 za nambari.

Kabla hatujaenda mbali zaidi, wacha tuzungumze juu ya tofauti kidogo kati ya nadharia iliyotangazwa na mazoezi yaliyozingatiwa - na ilionyesha kuwa kitabiri cha mzunguko katika SB kiliondolewa, kama matokeo ambayo utabiri wa mpito wa mwisho hadi mwanzo wa mzunguko unafanywa. kwa algorithm ya jumla, i.e. mbaya zaidi. Mwakilishi wa Intel alituhakikishia kuwa hakuna "mbaya zaidi" inapaswa kutokea, hata hivyo ...

Kusimbua na IDQ

Anwani za amri zilizotekelezwa zilizotabiriwa mapema (mbadala kwa kila uzi - na teknolojia imewezeshwa) hutolewa ili kuangalia uwepo wao katika kashe za amri (L1I) na (L0m), lakini tutakaa kimya juu ya mwisho - tutaelezea wengine mbele kwa sasa. Kwa kawaida, Intel ilihifadhi saizi ya sehemu ya amri iliyosomwa kutoka L1I hadi 16 byte (hapa neno "sehemu" linaeleweka kulingana na yetu). Hadi sasa, hiki kimekuwa kikwazo kwa msimbo ambao ukubwa wa wastani wa maagizo umeongezeka zaidi ya baiti 4, na kwa hivyo maagizo 4 yanayotarajiwa kutekelezwa kwa kila mzunguko wa saa hayatatoshea tena katika baiti 16. AMD ilitatua tatizo hili katika usanifu wa K10 kwa kupanua sehemu ya mafundisho hadi ka 32 - ingawa CPU zake kwa sasa hazina zaidi ya bomba-3. Katika SB, usawa wa saizi husababisha athari ya upande: mtabiri hutoa anwani inayofuata ya kizuizi cha 32-byte, na ikiwa itagundua mpito (labda) wa kurusha katika nusu yake ya kwanza, basi hakuna haja ya kusoma na kusimbua ya pili. - hata hivyo, itafanyika.

Kutoka kwa L1I, sehemu hiyo huenda kwa kiandikishaji awali, na kutoka hapo hadi mita yenyewe ya urefu (), ambayo huchakata hadi maagizo/mzunguko 7 au 6 (pamoja na bila; Nehalem inaweza kushughulikia kiwango cha juu cha 6) kulingana na urefu wao wote na utata. Mara tu baada ya mpito, usindikaji huanza na amri kwenye anwani inayolengwa, vinginevyo - na byte ambayo predecoder ilisimamisha mzunguko mmoja mapema. Vile vile na hatua ya mwisho: ama ni (labda) mpito ulioanzishwa, anwani ya byte ya mwisho ambayo ilitoka kwa BTB, au byte ya mwisho ya sehemu yenyewe - isipokuwa kikomo cha amri 7 / mzunguko umefikiwa, au amri "isiyofaa" haipatikani. Uwezekano mkubwa zaidi, bafa ya mita ya urefu ina sehemu 2-4 tu, lakini mita ya urefu inaweza kupata 16 yoyote kutoka kwayo. mfululizo kwaheri. Kwa mfano, ikiwa mwanzoni mwa sehemu 7 amri mbili-byte zinatambuliwa, basi katika mzunguko wa saa unaofuata mwingine byte 16 zinaweza kusindika, kuanzia 15.

Mita ya urefu, kati ya mambo mengine, hutambua jozi za amri zilizounganishwa kwa jumla. Tutazungumza juu ya jozi zenyewe baadaye kidogo, lakini kwa sasa wacha tukumbuke kuwa, kama katika Nehalem, hakuna zaidi ya jozi moja kama hiyo inaweza kugunduliwa kwa kila mzunguko wa saa, ingawa kiwango cha juu cha 3 kati yao kinaweza kuwekwa alama (na moja zaidi. amri moja). Hata hivyo, kupima urefu wa maagizo ni mchakato unaofuatana kwa kiasi, kwa hivyo haingewezekana kubainisha jozi kadhaa za kuunganisha kwa wingi wakati wa mzunguko wa saa.

Amri zilizo na lebo huishia katika moja ya amri mbili (IQ: foleni ya maagizo) - moja kwa kila uzi, amri 20 kila moja (ambayo ni 2 zaidi ya Nehalem). kwa kutafautisha husoma amri kutoka kwa foleni na kuzihamisha hadi kwenye mops. Ina 3 rahisi (inatafsiri amri 1 kuwa mop 1, na kwa kuunganisha kwa jumla - amri 2 kwa mop 1), mtafsiri tata (amri 1 kwa uops 1-4 au amri 2 kwa mop 1) na sequencer ndogo kwa ngumu zaidi. amri zinazohitaji mops 5 na zaidi kutoka . Zaidi ya hayo, huhifadhi tu "mikia" ya kila mlolongo, kuanzia uup ya 5, kwa sababu 4 ya kwanza hutolewa na mtafsiri tata. Zaidi ya hayo, ikiwa idadi ya uops katika microprogram haiwezi kugawanywa na 4, basi nne zao za mwisho hazitakuwa kamili, lakini haitawezekana kuingiza uops mwingine 1-3 kutoka kwa watafsiri katika mzunguko huo. Matokeo ya kusimbua huenda kwa na mbili (moja kwa kila mkondo). Ya mwisho (inayoitwa rasmi IDQ - foleni ya kusimbua maagizo, foleni ya amri zilizowekwa) bado ina uops 28 na uwezo wa kuzuia kitanzi ikiwa sehemu yake inayoweza kutekelezwa inafaa hapo.

Haya yote (isipokuwa cache ya mop) yalikuwa tayari huko Nehalem. Je, ni tofauti gani? Kwanza kabisa, ambayo ni dhahiri, avkodare ilifundishwa kusindika amri mpya za sehemu ndogo. Msaada Seti za SSE na nambari zote hazishangazi tena mtu yeyote, na kuongeza kasi ya usimbaji fiche kwa amri (pamoja na PCLMULQDQ) iliongezwa kwa Westmere (toleo la nm 32 la Nehalem). Kuna mtego: kazi hii haifanyi kazi kwa amri ambazo zina anwani ya mara kwa mara na ya RIP-jamaa (RIP-jamaa, anwani inayohusiana na kiashirio cha amri - njia ya kawaida kupata data katika msimbo wa 64-bit). Amri hizo zinahitaji moduli 2 (upakiaji tofauti na uendeshaji), ambayo ina maana kwamba avkodare haitashughulikia zaidi ya moja yao kwa kila mzunguko wa saa, kwa kutumia mtafsiri tata tu. Intel inadai kwamba dhabihu hizi zinafanywa ili kuokoa nishati, lakini haijulikani ni nini: uwekaji mara mbili, utekelezaji na uops utachukua wazi rasilimali zaidi, na kwa hiyo hutumia nishati zaidi, kuliko moja.

Kuunganisha kwa Macro kumeboreshwa - hapo awali, tu hesabu au kulinganisha kimantiki(CMP au TEST), sasa amri rahisi za hesabu za kuongeza na kutoa (ADD, SUB, INC, DEC) na mantiki "AND" (AND), pia kubadilisha kwa kuruka (amri ya pili ya jozi), inaruhusiwa. Hii hukuruhusu kupunguza amri 2 za mwisho hadi mop 1 katika karibu mzunguko wowote. Kwa kweli, vizuizi kwa amri zilizounganishwa vinabaki, lakini sio muhimu, kwani hali zilizoorodheshwa za jozi ya amri karibu kila wakati hutekelezwa:

- ya kwanza ya amri ya kwanza lazima iwe rejista;

- ikiwa operesheni ya pili ya maagizo ya kwanza iko kwenye kumbukumbu, anwani ya jamaa ya RIP hairuhusiwi;

- amri ya pili haiwezi kuwa mwanzoni au kuvuka mpaka wa mstari.

Sheria za mpito yenyewe ni:

- TEST pekee na NA zinaendana na hali yoyote;

- kulinganisha na (si) sawa na na yoyote iliyotiwa saini inaendana na amri yoyote ya kwanza inayoruhusiwa;

- kulinganisha na (si) kubeba na yoyote ambayo haijatiwa saini haioani na INC na DEC;

- ulinganisho mwingine (ishara, kufurika, usawa na kanusho zao) ni halali kwa TEST na NA.

Mabadiliko kuu katika foleni za uop ni kwamba uops zilizounganishwa za type , ambapo ufikiaji wa kumbukumbu unahitaji kusoma rejista ya faharisi, (na aina zingine kadhaa adimu) zimegawanywa katika jozi zinapoandikwa kwa IDQ. Hata kama kuna matukio 4 kama haya, yote 8 yatarekodiwa kwenye IDQ. Hii inafanywa kwa sababu uop (IDQ), dispatcher (ROB) na foleni za uwekaji nafasi sasa zinatumia umbizo la uop lililofupishwa bila uga wa faharasa wa biti 6 (bila shaka, ili kuokoa wakati wa kusonga mbele). Inachukuliwa kuwa kesi hizo zitakuwa chache, na kwa hiyo kasi haitaathirika sana.

Tutakuambia historia ya hali ya kuzuia kitanzi ya bafa hii hapa chini, lakini hapa tutaonyesha maelezo kidogo tu: mpito hadi mwanzo wa kitanzi hapo awali ulichukua mzunguko wa saa 1 ya ziada, na kutengeneza "Bubble" kati ya kusoma mwisho na mwanzo wa kitanzi, lakini sasa imepita. Walakini, mihuisho minne inayosomwa kwa kila mzunguko wa saa haiwezi kujumuisha za mwisho kutoka kwa marudio ya sasa na ya kwanza kutoka kwa inayofuata, kwa hivyo idadi ya milio katika kitanzi inapaswa kugawanywa kwa 4. Vizuri, vigezo vya kuizuia. ni vigumu kubadilika:

- uops za kitanzi zinapaswa kuzalishwa na si zaidi ya sehemu 8 32 za msimbo wa chanzo;

- sehemu hizi lazima zihifadhiwe katika L0m (huko Nehalem, bila shaka, katika L1I);

- hadi mabadiliko 8 yasiyo na masharti yanayotabiriwa kuwa yameanzishwa yanaruhusiwa (pamoja na ya mwisho);

- simu na kurudi haziruhusiwi;

- Ufikiaji ambao haujaoanishwa kwa rafu hauruhusiwi (mara nyingi wakati kuna idadi isiyo sawa ya amri za PUSH na POP) - zaidi juu ya hii hapa chini.

Injini ya stack

Kuna utaratibu mmoja zaidi, utendakazi ambao hatukuzingatia katika makala zilizopita - tracker ya stack pointer, iko mbele ya IDQ. Ilionekana kwenye Pentium M na bado haijabadilika. Kiini chake ni kwamba urekebishaji wa kiashiria cha stack (rejista ya ESP/RSP kwa hali ya 32/64-bit) na maagizo ya kufanya kazi nayo (PUSH, POP, CALL na RET) hufanywa na kiongeza tofauti, matokeo yake huhifadhiwa katika sajili maalum na kurudishwa kwa uup kama kawaida - badala ya kurekebisha pointer baada ya kila amri, kama inavyotakiwa na kama ilivyokuwa katika Intel CPUs kabla ya Pentium M.

Hii hufanyika hadi amri fulani ifikie pointer moja kwa moja (na katika hali zingine adimu) - injini ya stack inalinganisha pointer ya kivuli na sifuri na, ikiwa thamani sio sifuri, inaingiza uup ya kusawazisha kwenye mkondo wa uops kabla ya simu ya amri. pointer, kuandika kwa pointer thamani ya sasa kutoka kwa rejista maalum (na rejista yenyewe imewekwa upya). Kwa kuwa hii haihitajiki sana, simu nyingi kwa rafu ambayo hurekebisha kielekezi tu itumie. nakala ya kivuli, iliyobadilishwa wakati huo huo na shughuli zingine. Hiyo ni, kutoka kwa mtazamo wa vitalu vya bomba, maagizo hayo yanasimbwa na uop moja iliyounganishwa na sio tofauti na upatikanaji wa kumbukumbu ya kawaida, bila kuhitaji usindikaji katika ALU.

Kisomaji makini (habari za mchana!) kitatambua muunganisho: wakati wa kurudisha foleni, simu ambazo hazijaoanishwa kwenye rundo hazikubaliki kwa sababu injini ya rafu iko kwenye bomba. kabla IDQ - ikiwa baada ya iteration inayofuata thamani ya pointer ya kivuli sio sifuri, utahitaji kuingiza syncromop kwenye mpya, lakini hii haiwezekani katika hali ya mzunguko (mops zinasomwa tu kutoka kwa IDQ). Zaidi ya hayo, injini ya rafu kwa ujumla huzimwa ili kuokoa nishati, kama sehemu nyingine zote za mbele.

Maisha ya siri ya nops

Mabadiliko mengine yalifanywa kwa kupima urefu, lakini kesi hii inasimama kwa kiasi fulani. Kwanza, acheni tukumbuke wao ni nini na kwa nini wanahitajika. Wakati mmoja katika usanifu wa x86 kulikuwa na kumbukumbu ya 1-byte tu. Wakati ilikuwa muhimu kuhamisha msimbo kwa zaidi ya 1 byte au kuchukua nafasi ya amri kwa muda mrefu kuliko byte 1, nop iliingizwa mara kadhaa. Lakini licha ya ukweli kwamba amri hii haifanyi chochote, wakati bado unatumiwa kuiandika, na kwa uwiano wa idadi ya hatua. Ili kuhakikisha kwamba utendaji wa programu "iliyopigwa" hauteseka, nop inaweza kupanuliwa. Walakini, katika CPU za miaka ya 90, kiwango cha maagizo ya kusimbua na idadi ya viambishi awali juu ya thamani fulani (ambayo ni ndogo sana kuliko urefu unaoruhusiwa wa maagizo ya x86 ya baiti 15) ilishuka sana. Kwa kuongezea, haswa kwa nopa, kiambishi awali hutumiwa, kama sheria, ya aina moja, lakini inarudiwa mara nyingi, ambayo inaruhusiwa tu kama ubaguzi usiofaa, ugumu wa kupima urefu.

Ili kutatua matatizo haya, kuanzia Pentium Pro na wasindikaji wa Athlon wanaelewa "nop ndefu" na modR/M byte ili "rasmi" kupanua maagizo kwa kutumia rejista na kukabiliana na anwani. Kwa kawaida, hakuna shughuli zilizo na kumbukumbu na rejista zinazotokea, lakini wakati wa kuamua urefu, vitalu vya mita za urefu sawa hutumiwa kama maagizo ya kawaida ya multibyte. Matumizi ya nodi ndefu sasa yanapendekezwa rasmi na mafunzo ya uboreshaji wa programu ya kiwango cha chini kutoka kwa Intel na AMD. Kwa njia, predecoder ya SB imepunguza nusu (kutoka kwa mzunguko wa saa 6 hadi 3) adhabu ya viambishi awali 66 na 67, ambayo hubadilisha urefu wa kukabiliana na mara kwa mara na anwani - lakini, kama katika Nehalem, adhabu haitolewi kwa maagizo ambapo viambishi awali hivi havibadilishi urefu (kwa mfano, ikiwa kiambishi awali 66 kinatumika kwa maagizo bila operesheni ya haraka) au ni sehemu ya orodha ya swichi (ambayo hutumiwa mara nyingi katika msimbo wa vekta).

Urefu wa juu wa nodi ndefu iliyoumbizwa kwa usahihi hauzidi baiti 9 kwa Intel na 11 kwa AMD. Kwa hiyo, ili kuunganisha kwa 16 au 32 byte, bado kunaweza kuwa na nodes kadhaa. Walakini, kwa kuwa amri hii ni rahisi, kusimbua na "utekelezaji" wake hautachukua rasilimali zaidi kuliko kusindika amri rahisi zaidi za kufanya kazi. Kwa hiyo, kwa miaka mingi, kupima kwa miguu ndefu imekuwa njia ya kawaida ya kuamua vigezo vya mbele ya conveyor, hasa, kupima urefu na decoder. Na hapa Sandy Bridge iliwasilisha mshangao wa ajabu sana: kupima utendaji wa programu za kawaida haukuonyesha ucheleweshaji wowote au kupungua, lakini hundi ya kawaida ya synthetic ya vigezo vya decoder bila kutarajia ilionyesha kuwa utendaji wake ni sawa na amri moja kwa mzunguko wa saa! Wakati huo huo, Intel haikutoa arifa zozote rasmi kuhusu mabadiliko hayo makubwa katika avkodare.

Utaratibu wa kipimo ulifanya kazi kikamilifu hata kwenye Nehalem na ilionyesha 4 sahihi. Unaweza kulaumu Turbo Boost 2.0 mpya na "iliyozidi" inayotumika, ambayo inaharibu usomaji wa saa iliyopimwa, lakini kwa majaribio ilizimwa. Kuzidisha kwa joto na kupunguzwa kwa kasi kwa mzunguko pia hakujumuishwa. Na sababu ilipogunduliwa mwishowe, ikawa ngeni zaidi: zinageuka kuwa nodi ndefu kwenye SB zinashughulikiwa tu na mtafsiri rahisi wa kwanza, ingawa nodi 1-byte zilizo na idadi yoyote ya viambishi awali na amri sawa za "kutokufanya" (kwa mfano, kunakili rejista yenyewe) zinakubaliwa kwa urahisi zote nne. Kwa nini hii ilifanyika haijulikani, lakini angalau drawback moja ya ufumbuzi huo wa kiufundi tayari umejionyesha wazi: ilichukua timu yetu ya utafiti siku kumi ili kujua sababu za polepole ya ajabu ya decoder ... Kwa kulipiza kisasi, sisi waombe mashabiki wenye bidii wa Kambi ya Upinzani waje na aina fulani ya nadharia ya njama kuhusu mipango ya hila ya kampuni fulani I. ili kuwavuruga watafiti hodari wa usindikaji. :)

Kwa njia, kama ilivyotokea, mtangazaji No. 1 alikuwa tayari "sawa zaidi" kati ya wengine. Huko Nehalem, amri za kusongesha za mzunguko (ROL na ROR) zilizo na operesheni ya wazi ya mara kwa mara pia ziliamuliwa tu katika mtafsiri wa kwanza, na katika mzunguko huo huo wa nne ilizimwa, kwa hivyo thamani ya IPC ilishuka hadi 3. Inaweza kuonekana - kwa nini kuleta mfano adimu hapa? Lakini haswa kwa sababu ya mtego huu, ili kufikia kasi ya kilele na algorithms ya kuharakisha kama SHA-1, mpangilio sahihi wa maagizo ulihitajika, ambao wakusanyaji hawakuweza kukabiliana nao. Katika SB, maagizo kama haya yakawa hali ya 2, ili, kuchukua mtafsiri mgumu (ambaye tayari ni mmoja), wanafanya karibu kutofautishwa kwa CPU, lakini kutabirika zaidi kwa wanadamu na mkusanyaji. Kwa nops, kinyume kilifanyika. Weka akiba

Malengo na watangulizi

Sio bure kwamba tulitenganisha sura hii kutoka kwa maelezo mengine ya mbele - nyongeza ya cache ya uop inaonyesha wazi njia ambayo Intel imechagua kwa wasindikaji wake wote, kuanzia na Core 2. Mwisho, kwa mara ya kwanza ( kwa Intel), iliongeza kizuizi ambacho wakati huo huo kilifikia mbili, ingeonekana, Malengo yanayokinzana: kuongeza kasi na kuokoa nishati. Tunazungumza juu ya foleni ya amri (IQ) kati ya predecoder na decoder, ambayo kisha ikahifadhi hadi amri 18 na urefu wa hadi 64 byte kwa jumla. Ikiwa tu ingerekebisha tofauti katika kasi ya utayarishaji na uundaji wa amri (kama buffer ya kawaida) - faida itakuwa ndogo. Lakini Intel alifikiria kuambatisha kitengo kidogo cha LSD kwenye IQ (hakuna uwezekano kwamba wavulana "walikubali" chochote, wana aina hiyo ya ucheshi) - Kigunduzi cha Mtiririko wa Kitanzi, "kigundua mtiririko wa mzunguko". Wakati mzunguko unaolingana na maagizo 18 umegunduliwa, LSD huzima hatua zote za awali (predictor, L1I cache na predecoder) na kupanga foleni maagizo ya mzunguko kwa kisimbuzi hadi ikamilike au hadi mpito ufanyike zaidi ya mipaka yake (kupiga simu na kurejesha. hazikubaliki). Hii huokoa nishati kwa kuzima vizuizi ambavyo havifanyi kitu kwa muda na huongeza utendakazi kwa sababu ya utiririshaji wa uhakika wa amri 4/mzunguko wa kisimbuzi, hata kama "zimewekewa" viambishi awali visivyofaa zaidi.

Intel ni wazi alipenda wazo hili, kwa hivyo mzunguko uliboreshwa kwa Nehalem: IQ ilirudiwa (kwa nyuzi mbili), na kati ya avkodare na kisambazaji (yaani, kwenye mpaka wa mbele na nyuma) foleni mbili za IDQ za uops 28 kila moja. ziliwekwa, na kitengo cha LSD kilihamishiwa kwao. Sasa, wakati mzunguko umezuiwa, decoder pia imezimwa, na utendaji umeongezeka, ikiwa ni pamoja na kutokana na utitiri wa uhakika wa si amri 4, lakini uops 4 kwa kila mzunguko wa saa, hata kama kizazi chao kilifanywa kwa kiwango cha chini (kwa Core 2/i) kwa kasi ya mops 2/mdundo. Mashabiki wenye hasira wa Kambi ya Upinzani, wakitafuta sekunde kutoka kwa mchezo wao wa kupenda, mara moja wataingiza kipini cha nywele: ikiwa LSD ni kitu kizuri sana, kwa nini haikujengwa ndani ya Atomu? Na hila ni sawa - kuwa na foleni ya hali 32 baada ya dekoda, Atom hajui jinsi ya kuzuia mzunguko ndani yake, ambayo itakuwa muhimu sana kwa kuokoa milliwatts za thamani. Walakini, Intel haikuacha wazo hilo na ikatayarisha sasisho kwa CPU mpya, na ilikuwa nzuri sana!

Jina rasmi la ndani la akiba ya uop ni DSB (kusimbua bafa ya mtiririko), ingawa halielezei kama neno linalopendekezwa la DIC (kache ya maagizo iliyotengwa). Cha ajabu, haibadilishi, lakini inakamilisha foleni za IDQ, ambazo sasa zimeunganishwa kwenye avkodare. au na kache ya ups. Wakati wa utabiri unaofuata wa tawi, anwani inayolengwa inaangaliwa kwa wakati mmoja katika maagizo na kache za uop. Ikiwa ya mwisho inafanya kazi, basi kusoma zaidi kunatoka kwake, na sehemu nyingine ya mbele imezimwa. Hii ndiyo sababu akiba ya uop ni kashe ya kiwango cha 0 kwa uops, yaani, L0m.

Cha kufurahisha, wazo hili linaweza kuendelezwa kwa kuita akiba za IDQ "ondoa kiwango cha kwanza". :) Lakini si uongozi tata kama huo ndani ya mfumo wa hata msingi mzima, lakini mbele tu, usio na maana? Hata kama Intel, isipokuwa, haikuhifadhi nafasi hiyo, lakini jozi ya IDQ italeta akiba kubwa ya ziada, ikizingatiwa kwamba wakati zinafanya kazi, ni kashe ya UOP pekee ndio imezimwa, kwani sehemu nyingine ya mbele (isipokuwa kwa mtabiri). ) tayari amelala? Na hautapata ongezeko kubwa la kasi pia, kwani kache ya uop pia imesanidiwa kutoa uops 4 kwa mzunguko. Inavyoonekana, wahandisi wa Intel waliamua kuwa mchezo wa kiwango cha 3 ulikuwa na thamani ya mshumaa wa milliwatt.

Mbali na kuokoa, cache ya uop huongeza kasi ya utendaji, ikiwa ni pamoja na kupunguza adhabu kwa utabiri wa uwongo wa tawi: huko Nehalem, wakati msimbo sahihi ulipatikana katika L1I, adhabu ilikuwa mizunguko 17, katika SB - 19, lakini ikiwa kanuni ilikuwa. kupatikana katika L0m, kisha 14 tu. Zaidi ya hayo Hizi ndizo nambari za juu zaidi: katika kesi ya mpito uliotabiriwa kwa uwongo, mpangaji bado anahitaji kuzindua na kukamilisha uops uliopita kwa utaratibu wa programu, na wakati huu L0m inaweza kusimamia kusukuma sahihi. uops ili kipanga ratiba apate muda wa kuzizindua mara tu baada ya kuacha amri kabla ya mpito. Katika Nehalem, mbinu hii ilifanya kazi na IDQ na makali, lakini katika kesi ya kwanza uwezekano kwamba anwani sahihi ya lengo pia itakuwa ndani ya mzunguko wa 28-mop ni ndogo sana, na kwa pili polepole ya makali katika hali nyingi ilifanya. hairuhusu kupunguza ucheleweshaji hadi sifuri. SB ina nafasi nzuri zaidi.

Kifaa

Kitopolojia, L0m ina mistari 32 8 (8- ). Kila mstari huhifadhi uops 6 (katika cache nzima - 1536, yaani "kilomita moja na nusu"), na cache inaweza kuandika na kusoma mstari mmoja kwa mzunguko wa saa. Mtabiri hutoa anwani za vizuizi vya 32-byte, na ni saizi hii ambayo inafanya kazi kwa L0m, kwa hivyo chini ya neno "sehemu" itamaanisha kizuizi cha 32-byte cha msimbo kilichopangwa na kutabiriwa kama inayoweza kutekelezwa (na sio 16-byte moja. , kama kwa avkodare). Wakati wa kusimbua, mtawala wa L0m anangojea sehemu hiyo kusindika hadi mwisho au hadi mpito wa kwanza uchochewe ndani yake (bila shaka, labda - hapa na chini tunadhani utabiri ni sahihi kila wakati), kukusanya uops wakati huo huo kama kutuma. wao kwa nyuma. Kisha hurekebisha pointi za kuingia na kutoka kwa sehemu, kulingana na tabia ya mabadiliko. Kwa kawaida, mahali pa kuingilia ni anwani inayolengwa ya mpito ulioanzishwa katika sehemu ya awali (kwa usahihi zaidi, biti 5 za chini za anwani), na sehemu ya kutoka ni. anwani yako mwenyewe ilianzisha mpito katika sehemu hii. KATIKA kama njia ya mwisho, ikiwa hakuna mpito mmoja unaoanzishwa katika sehemu ya awali au ya sasa (yaani, sehemu hazitekelezwi tu, bali pia zimehifadhiwa kwa safu), basi zote mbili zitatekelezwa kwa ukamilifu - ingizo kwao litawashwa. hali ya sifuri na baiti ya kwanza ya ile ya kwanza ambayo inafaa kabisa katika sehemu hii ya amri, na matokeo yapo kwenye uup ya mwisho ya amri inayofaa kabisa na byte yake ya awali.

Ikiwa sehemu ina zaidi ya marudio 18, haijahifadhiwa. Hii huweka kiwango cha chini cha wastani (ndani ya kipande) cha maagizo hadi baiti 1.8, ambayo haitakuwa kizuizi kikubwa katika programu nyingi. Unaweza kukumbuka nukta ya pili ya vizuizi vya IDQ - ikiwa mzunguko unalingana katika sehemu, lakini inachukua kutoka 19 hadi 28 uops, si kache ya L0m au foleni ya IDQ itarekebisha, ingawa kwa ukubwa ingetoshea popote. Walakini, katika kesi hii, urefu wa wastani wa amri unapaswa kuwa baiti 1.1-1.7, ambayo haiwezekani sana kwa amri dazeni mbili mfululizo.

Uwezekano mkubwa zaidi, uops wa sehemu huandikwa wakati huo huo kwenye cache, huchukua mistari 1-3 ya seti moja, hivyo kwa L0m moja ya kanuni kuu za uendeshaji wa cache ya kuweka-associative inakiukwa: kwa kawaida mstari mmoja wa seti husababishwa. Vitambulisho hadi mistari mitatu vinaweza kupokea mara moja anwani ya sehemu sawa, tofauti tu katika nambari za serial. Wakati anwani iliyotabiriwa inapiga L0m, kusoma hutokea kwa njia sawa - njia 1, 2 au 3 za seti inayotakiwa zinasababishwa. Kweli, mpango huo umejaa vikwazo.

Ikiwa programu inayoweza kutekelezwa katika sehemu zote imegawanywa katika uops 13-18, ambayo itachukua mistari 3 ya L0m kwa sehemu zote, yafuatayo yatafunuliwa: ikiwa seti ya sasa tayari imechukuliwa na sehemu mbili za mistari 3, na ya tatu. inajaribu kuiandikia (ambayo haitoshi kwa mstari mmoja) , itabidi uondoe moja ya zamani, na kwa kuzingatia uunganisho wake - zote 3 za zamani. Kwa hivyo, zaidi ya sehemu mbili za msimbo wa "fine-grained" haipaswi kuingia kwenye seti. Wakati wa kujaribu dhana hii katika mazoezi, hii ndio ilifanyika: sehemu zilizo na timu kubwa, zinazohitaji uops chini ya 7, zilijaa ndani ya L0m nambari 255 (kwa sababu fulani haikuwezekana kuchukua nyingine), inafaa karibu 8 KB ya msimbo. Sehemu za kati (7-12 uops) zilichukua nafasi zote 128 zinazowezekana (mistari 2 kila moja), ikihifadhi 4 KB haswa. Naam, amri ndogo zinafaa katika sehemu 66, ambazo ni mbili zaidi ya thamani inayotarajiwa (baiti 2112 dhidi ya 2048), ambayo inaonekana inaelezewa na athari za mpaka za nambari yetu ya jaribio. Uhaba ni dhahiri - ikiwa laini 256 za 6-op zingeweza kujazwa kabisa, zingetosha kwa mapacha 85 kamili na saizi ya nambari ya baiti 2720.

Labda Intel hatarajii kuwa katika msimbo fulani kutakuwa na amri nyingi fupi na rahisi ambazo zaidi ya 2/3 yake itakuwa katika sehemu za mstari 3, ambazo zitalazimishana kutoka kwa L0m mapema kuliko lazima. Na hata ikiwa nambari kama hiyo itapatikana, kwa kuzingatia unyenyekevu wa uainishaji wake, vizuizi vilivyobaki vya mbele vinaweza kukabiliana kwa urahisi na kazi ya kusambaza mizunguko 4 / mzunguko muhimu kwa nyuma (ingawa bila akiba iliyoahidiwa katika wati na mizunguko ya adhabu. kwa utabiri wa uwongo). Inashangaza kwamba ikiwa L0m ingekuwa na njia 6, shida isingetokea. Intel aliamua kuwa na saizi ya kache theluthi moja kubwa kwa sababu ya ushirika ni muhimu zaidi ...

Vipimo

Wacha tukumbuke kuwa wazo la kuhifadhi idadi kubwa ya uops badala ya amri za x86 sio mpya. Ilionekana kwanza kwenye Pentium 4 kwa namna ya kache ya athari za uop - mlolongo wa uops baada ya kufunguliwa kwa kitanzi. Zaidi ya hayo, kashe ya ufuatiliaji haikuongeza, lakini ilibadilisha amri za L1I zilizokosekana za avkodare zilisomwa mara moja kutoka . Licha ya kusahaulika kwa usanifu wa NetBurst, ni busara kudhani kuwa wahandisi wa Intel walitumia uzoefu wa zamani, ingawa bila kufunua kitanzi na kitabiri kilichowekwa kwa kache. Wacha tulinganishe suluhisho za zamani na mpya (CPU mpya zinaitwa Core i 2 hapa, kwa sababu nambari za karibu mifano yote iliyo na usanifu wa SB huanza na mbili):

* - labda

Ufafanuzi fulani unahitajika hapa. Kwanza, upitishaji wa L0m umebainishwa kwa kuzingatia kikomo cha upana wa conveyor wa jumla wa uopas 4. Hapo juu tulidhani kuwa L0m inaweza kusoma na kuandika uops 18 kwa kila mzunguko wa saa. Hata hivyo, wakati wa kusoma, wote 18 (ikiwa kulikuwa na hasa kwamba wengi wao wakati wa kutengeneza sehemu ya awali) hawawezi kutumwa kwa mzunguko wa saa, na kutuma hutokea katika mzunguko wa saa kadhaa.

Zaidi ya hayo, saizi ya mop katika bits kwa ujumla inarejelea habari nyeti sana ambayo watengenezaji hawatoi kabisa, au tu wakati wa kusukuma ukuta (wanasema, tayari umehesabu kila kitu, na iwe hivyo - tutathibitisha) . Kwa Intel CPUs, takwimu ya mwisho inayojulikana ni bits 118 kwa Pentium Pro. Ni wazi kwamba ukubwa umeongezeka tangu wakati huo, lakini hapa ndipo nadhani huanza. Biti 118 za 32-bit x86 CPU zinaweza kupatikana ikiwa mop ina sehemu za anwani ya maagizo ambayo iliizalisha (biti 32), operesheni ya haraka (biti 32), kukabiliana na anwani (biti 32), operesheni za kusajili (3 x Biti 3 + 2 kwa kila kiwango kwa rejista ya index) na opcode (biti 11 ambazo toleo maalum la amri ya x86 limesimbwa, kwa kuzingatia viambishi awali). Baada ya kuongeza , na SSE2, uwanja wa opcode labda uliongezeka kwa biti 1, kwa hivyo nambari 119.

Baada ya mpito kwenda (Prescott na zaidi), kwa nadharia, sehemu zote za 32-bit zinapaswa kuongezeka hadi biti 64. Lakini kuna hila hapa: 64-bit constants katika x86-64 inaruhusiwa moja tu kwa wakati (yaani, zote mbili thabiti kwenye amri hakika hazitachukua zaidi ya ka 8), halafu na sasa bado zinafanya. na bits 48. Kwa hivyo kuongeza saizi ya uop inahitajika na bits 16 tu za anwani na bits 3 za ziada za nambari za rejista (ambazo kuna 16) - tunapata (takriban) bits 138. Kweli, katika SB uop inaonekana imeongezeka kwa biti 1 kwa sababu ya kuongezwa kwa amri zingine mia chache tangu P4 iliyopita, na kwa zingine 8 kwa sababu ya kuongezeka. idadi ya juu Kuna hadi rejista 5 zilizoainishwa wazi katika amri (unapotumia AVX). Mwisho, hata hivyo, ni wa shaka: tangu wakati huo, fikiria tu, hakuna i386 moja iliyoongezwa kwenye usanifu wa x86. mpya amri inayohitaji angalau baiti 4 za mara kwa mara (pamoja na ubaguzi wa hivi majuzi na wa hila sana katika SSE4.a ya AMD, ambayo hata watayarishaji programu wengi hawajui). Na kwa kuwa Intel AVX na AMD wamesasisha usimbuaji wa maagizo ya vekta pekee, bits za nambari za rejista za ziada zitatoshea katika nusu ya juu ya sehemu ambayo haijatumiwa (kwa maagizo haya) uwanja wa uendeshaji wa 32-bit wa haraka. Zaidi ya hayo, katika maagizo ya x86 yenyewe, rejista ya 4 au ya 5 imefungwa na bits nne tu za mara kwa mara.

Ni dhahiri kwamba kuhifadhi na kutuma "monsters" kama hizo kwa yoyote kiasi kikubwa- ghali sana. Kwa hivyo, hata kwa P4, Intel ilikuja na toleo fupi la uop, ambalo kuna uwanja mmoja tu wa viboreshaji vyote viwili, na ikiwa haifai hapo, basi bits zilizokosekana zimewekwa kwenye uwanja sawa wa uup iliyo karibu. . Walakini, ikiwa tayari huhifadhi vidhibiti vyake hapo, basi italazimika kuingiza nop kama jirani kama mtoaji-wafadhili wa biti za ziada. Mwendelezo wa mpango huu pia unazingatiwa katika SB: nodi za ziada hazijaingizwa, lakini amri zilizo na viboreshaji vya 8-byte (au kwa jumla ya saizi za kawaida na kushughulikia anwani ya ka 5-8) zina saizi mbili ndani. L0m. Walakini, kwa kuzingatia urefu wa amri kama hizo, zaidi ya 4 kati yao hazitatoshea katika sehemu, kwa hivyo kizuizi cha uops zilizochukuliwa ni wazi sio muhimu. Walakini, tunasema: SB, tofauti na CPU zilizopita, ina fomati 3 za uop - inayoweza kutatuliwa (kamili zaidi), iliyohifadhiwa kwenye kashe ya uop (pamoja na kupunguzwa mara kwa mara) na ile kuu (bila uwanja wa rejista), inayotumika zaidi. katika bomba. Walakini, mops nyingi hupita kutoka kwa kusimbua hadi kustaafu.

Vikwazo