Ini adalah bahagian pertama siri khusus untuk logik boleh atur cara dan persekitaran pembangunan Quartus daripada Altera. Ia menerangkan proses mendapatkan kit pengedaran untuk edisi percuma Quartus IDE. Dan juga proses mencipta projek baru dalam persekitaran ini.

Bahagian seterusnya siri: Altera FPGA. Bahagian 2: Reka Bentuk Litar Digital.

Bahagian kedua mengkaji proses menambah fail baru pada projek. Reka bentuk visual litar digital.

Siri artikel ini tertumpu pada kerja dengan papan CTRL-CPLD-EPM570 pada cip Altera Max II. Papan ini tidak diperlukan untuk penguasaan bahan yang berjaya, kerana projek yang diterangkan di dalamnya tidak menggunakan sebarang ciri khas Max II.

Untuk memuatkan projek ke dalam cip, pengaturcara murah yang serasi dengan Altera USB Blaster digunakan.

Langkah 1. Mendapatkan pengedaran Altera Quartus

Perhatian! Pada 2015, Altera telah diambil alih oleh Intel. Jenama Altera tidak lagi wujud pada Julai 2018, dan alamat tapak web altera.com tidak lagi menuju ke mana-mana. Nama baharu Altera ialah Intel Programmable Solutions Group (PSG). Semua dokumentasi dan perisian yang diperlukan untuk berfungsi dengan FPGA Altera kini tersedia di intel.com

Untuk mencipta projek untuk Altera FPGA, IDE proprietari digunakan - Quartus. Terdapat banyak versi Quartus, dan anda perlu memilih yang sesuai untuk cip sedia ada. Altera kerap mengalih keluar sokongan untuk cip lama daripada versi baharu perisiannya. Sebaliknya, versi baharu Quartus mengubah keperluan untuk perisian dan perkakasan komputer. Sebagai contoh, Quartus 13.1 ialah versi terkini yang berfungsi pada kedua-dua sistem 64-bit dan 32-bit.

Siri artikel ini tertumpu pada Quartus versi 13.1. Oleh kerana, dalam satu tangan, ia tidak mempunyai keperluan khas untuk bitness sistem pengendalian. Sebaliknya, ia menyokong cip siri MAX II.

Untuk mendapatkan pengedaran Quartus, anda mesti mempunyai akaun di intel.com atau intel.ru Malangnya, pada masa ini (sehingga Disember 2018) prosedur pendaftaran di tapak web Intel agak sukar. Borang pendaftaran bukan senang nak cari. Ia hanya boleh diakses pada peringkat akhir memuatkan pengedaran. Selain itu, semasa proses pendaftaran anda perlu memberikan alamat e-mel yang sah, nombor telefon bimbit dan pastikan anda memberikan kata laluan yang kompleks.

Semasa proses penggabungan aktif antara Intel dan Altera sedang dijalankan, adalah lebih baik untuk menggunakan sumber pihak ketiga untuk memuat turun Quartus. Pengedaran tersedia secara umum pada cakera Yandex, pautan muat turun: https://yadi.sk/d/bcrz7IAAKY6dQg

Untuk bekerja dengan cip MAX II, anda memerlukan Quartus sendiri, dan pakej untuk menyokong MAX II dan MAX V. Ini ialah fail “ QuartusSetupWeb-13.1.0.162.exe"Dan" max_web-13.1.0.162.qdz"masing-masing.

Pada penghujung artikel, versi lama arahan untuk memuat turun pengedaran tersedia: . Anda boleh menggunakannya untuk mendapatkan gambaran kasar tentang cara memuat turun pengedaran dari laman web Intel, kerana laman web Intel menggunakan Pemilih Perisian daripada Altera. Dan sama seperti Altera, Pemilih Perisian mengubah hala pengguna ke halaman log masuk apabila cuba memuat turun mana-mana fail, jika pengguna tidak pernah log masuk ke tapak dengan akaunnya sebelum ini.

Halaman log masuk ini adalah satu-satunya tempat yang mengandungi pautan ke borang pendaftaran di tapak web Intel. Pautan pendaftaran terletak di sebelah kanan halaman. Untuk pengguna biasa, anda boleh menggunakan pautan "Daftar sekarang untuk akaun individu". Pautan ditunjukkan dalam gambar di bawah.

Langkah 2: Pasang Edisi Web Quartus II 13.1

Pemasangan perisian CAD Quartus II tidak mengandungi sebarang kejutan dan mengikut algoritma "Seterusnya → Seterusnya → Selesai" yang terbukti.

Tidak perlu menukar tetapan pemasangan. Yang berikut menganggap bahawa Quartus II telah dipasang dengan tetapan lalai.

Setelah pemasangan selesai, persekitaran Quartus akan bermula secara automatik. Autorun ini didayakan secara lalai.

Apabila anda mula-mula melancarkan Quartus CAD, anda akan diminta untuk mengkonfigurasi penghantaran telemetri kepada Altera (dipanggil TalkBack di sini) dan memilih jenis lesen.

Melumpuhkan atau mendayakan "TalkBack" ditetapkan dengan menandai kotak pilihan "Dayakan menghantar data TalkBack ke Altera", yang juga tersedia selepas memasang Quartus melalui menu Alat → Pilihan → Kesambungan Internet → butang "Pilihan TalkBack...".

Apabila digesa untuk jenis lesen, anda hanya memilih pilihan kedua: "Jalankan perisian Quartus II." Dengan cara ini anda akan memilih lesen percuma.

Pada ketika ini, pemasangan dan konfigurasi awal perisian telah selesai dan anda boleh meneruskan untuk mencipta projek pertama anda.

Langkah 3. Quartus II - mencipta projek pertama

Pertama, buat folder untuk projek baharu. Panggilnya "projek pertama".

Perhatian! Laluan ke direktori projek mestilah tidak termasuk aksara Cyrillic! Versi Quartus II 15 dan 13 mempunyai masalah dengan sokongan Cyrillic. Versi lain belum diuji.

Kini melancarkan Quartus II. Apabila anda melancarkan Quartus II yang baru dipasang, anda akan disambut oleh tetingkap, yang paparannya dipaparkan di bawah.

Untuk mencipta projek baharu, gunakan wizard yang tersedia dengan mengklik butang “New Project Wizard” atau melalui menu Fail → New Project Wizard.

Apabila anda melancarkan wizard, tetingkap akan dipaparkan yang menyediakan senarai ringkas parameter projek yang boleh dikonfigurasikan semasa wizard.

Klik "Seterusnya" dan anda akan dibawa ke tetingkap yang ditunjukkan dalam tangkapan skrin di bawah. Dalam tetingkap ini, anda mesti menentukan direktori kerja (“Apakah direktori kerja untuk projek ini?”) dan nama keseluruhan projek (“Apakah nama projek ini?”). Dan juga nama modul utamanya ("Apakah nama entiti reka bentuk peringkat atas untuk projek ini? ...").

Wizard secara automatik menggantikan nama projek sebagai nama modul utama, dan ini adalah cadangan umum untuk projek dalam Quartus II, yang mana anda tidak seharusnya menyimpang melainkan benar-benar perlu.

Beberapa perkataan mengenai "modul utama" itu sendiri. Projek Quartus II mungkin termasuk banyak fail (modul) yang menerangkan pelbagai blok berfungsi litar bersepadu yang direka bentuk. Dan di antara set ini, satu fail semestinya menonjol, yang menerangkan hubungan antara semua blok rajah - entiti reka bentuk peringkat atas. Untuk projek kecil yang mengandungi hanya satu fail, fail tunggal ini juga akan menjadi modul utama projek.

Pada langkah seterusnya, wizard akan menawarkan untuk menambah fail daripada mana-mana projek yang dibuat sebelum ini kepada projek baharu. Memandangkan ini adalah projek pertama anda, langkau ke langkah tiga.

Langkah ketiga adalah salah satu yang paling penting. Di sini anda perlu menunjukkan model khusus cip FPGA yang anda gunakan. Tetingkap wizard pada langkah ini ditunjukkan dalam tangkapan skrin di bawah. Dalam tetingkap ini, banyak parameter tersedia untuk pemilihan langkah demi langkah bagi litar mikro yang diperlukan daripada senarai luas yang tersedia. Tempat terbaik untuk bermula ialah dengan blok "Keluarga Peranti". Di sini anda perlu memilih keluarga yang menjadi milik cip anda. Papan CTRL-CPLD-EPM570 mengandungi cip EPM570T100C5N, yang dimiliki oleh keluarga Max II.

Dalam blok di sebelah kanan - "Tunjukkan dalam senarai 'Peranti yang tersedia'", anda boleh menyediakan penapis untuk mengurangkan senarai litar mikro, yang terletak di bahagian bawah tetingkap. Anda boleh menentukan jenis pembungkusan cip. Bilangan pin sarungnya. Dan juga kelajuan teras dalam unit konvensional. Penapis kedua hingga terakhir ditapis mengikut nama litar mikro. Ia akan menjadi paling mudah untuk menggunakannya, kerana nama litar mikro sudah diketahui dengan tepat. Tetapi menurut tanda EPM570T100C5N, tiada litar mikro ditawarkan untuk pemilihan. Pendekkan nama kepada EPM570T100C5, dan pilih cip dengan nama ini dalam senarai yang muncul sebagai yang paling serasi.

Jika anda beralih kepada lembaran data, ternyata huruf N terakhir dalam penandaan cip hanya bermakna ketiadaan plumbum dalam pembungkusan cip. Fakta ini tidak penting untuk projek anda dalam Quartus II kerana teras EPM570T100C5N dan EPM570T100C5 adalah sama.

Teruskan ke langkah keempat seterusnya - "Tetapan Alat EDA". Di sini anda boleh menyediakan penyepaduan dengan pelbagai alat CAD pihak ketiga yang digunakan oleh pereka cip profesional. Memandangkan tujuan artikel ini adalah untuk membantu anda menguasai Quartus II CAD, dan bukan keseluruhan pakej aplikasi yang menelan belanja beribu-ribu dolar, cuma langkau ke langkah terakhir.

Langkah terakhir memaparkan senarai umum parameter untuk projek baharu anda. Semak bahawa parameter berikut ditetapkan dengan betul: nama dan direktori kerja projek, entiti reka bentuk peringkat atas, penandaan cip yang digunakan. Kemudian klik butang "Selesai". Itu sahaja! Projek telah dibuat.

Anda mungkin perasan bahawa butang "Selesai" tersedia untuk mengklik dari langkah pertama wizard. Dan anda sebenarnya boleh mengkliknya dalam langkah pertama, hanya menentukan direktori kerja, nama projek dan modul utama. Hanya maklumat ini sangat diperlukan untuk membuat projek baharu. Semua parameter lain tersedia untuk konfigurasi pada bila-bila masa dari menu utama program. Jadi, untuk menambah lebih banyak fail pada projek anda (langkah kedua wizard), gunakan menu Projek → Tambah/Buang Fail dalam projek. Untuk memilih atau menukar model cip yang mana projek itu dicipta (langkah ketiga wizard), gunakan menu Tugasan → Peranti. Penyepaduan dengan alat pembangunan tambahan (langkah terakhir wizard) ialah Tugasan → Tetapan → Tetapan Alat EDA.

Secara umum, semua tetapan projek dikumpulkan dalam tetingkap, paparan yang dibentangkan dalam tangkapan skrin di bawah. Tetingkap dipanggil melalui menu Tugasan → Tetapan.

Item Fail – ini ialah tetingkap yang dipanggil daripada menu utama program (Projek → Tambah/Buang Fail dalam projek). Tetapan Alat EDA – serupa. Pilihan litar mikro tersedia menggunakan butang “Peranti...” di penjuru kanan sebelah atas tetingkap tetapan projek.

Ini menyimpulkan bahagian pertama artikel tentang latihan untuk bekerja dengan FPGA daripada Intel (Altera).

(Arkib) Mendapatkan pengedaran Altera Quartus

Untuk mendapatkan pengedaran Quartus, log masuk ke akaun anda myAltera di altera.com: butang “LOG MASUK” di penjuru kanan sebelah atas tapak, di sebelah bar carian.

Jika anda belum mempunyai akaun myAltera, maka anda boleh menciptanya hanya dengan mengikuti pautan di bahagian paling bawah borang pendaftaran, baris “Tidak mempunyai akaun? Buat satu."

Setelah log masuk ke myAltera, pergi ke pusat muat turun tapak. Pautan semasa penulisan: https://www.altera.com/downloads/download-center.html

Jika pautan tidak berfungsi, sila pergi ke pusat muat turun melalui halaman utama akaun anda.

Untuk melakukan ini, pilih bahagian "SOKONGAN" dan di dalamnya ikuti pautan "Muat Turun", yang akan membawa anda ke pusat muat turun.

Untuk melakukan ini, pilih bahagian "SOKONGAN" dan di dalamnya ikuti pautan "Muat Turun", yang akan membawa anda ke pusat muat turun.

Pusat muat turun mempunyai pautan terus untuk memuat turun versi terkini Quartus dalam pelbagai edisi. Di bawah ialah blok "Pemilih Perisian", tatal halaman kepadanya. Dalam Pemilih Perisian Terdapat beberapa cara untuk memilih apa yang anda perlukan Taburan Q uartus, tab: “Pilih mengikut Versi” (pemilihan terus mengikut versi perisian yang diperlukan), “Pilih mengikut Peranti” ( memilih versi perisian berdasarkan sokongan untuk cip tertentu ), Pilih mengikut Perisian ( pemilihan produk perisian

Pusat muat turun mempunyai pautan terus untuk memuat turun versi terkini Quartus dalam pelbagai edisi. Di bawah ialah blok "Pemilih Perisian", tatal halaman kepadanya. Dalam Pemilih Perisian Terdapat beberapa cara untuk memilih apa yang anda perlukan Taburan Q uartus, tab: “Pilih mengikut Versi” (pemilihan terus mengikut versi perisian yang diperlukan), “Pilih mengikut Peranti” ( memilih versi perisian berdasarkan sokongan untuk cip tertentu ), Pilih mengikut Perisian ( pemilihan produk perisian

Pilihan yang paling mudah nampaknya adalah pilihan berdasarkan ketersediaan sokongan untuk litar mikro sedia ada.

Contohnya, jika litar mikro digunakan Altera Max II maka anda perlu memilih tab " Pilih mengikut Peranti", dan dalam blok "Peranti". » kembangkan item « siri MAX". DALAM pilih daripada senarai yang muncul Maks II.

Di sebelah kanan blok Peranti akan dipaparkan senarai edisi dan versi Quartus yang termasuk sokongan Maks II. Edisi percuma hanyalah Edisi Web.

Di sebelah kanan blok Peranti akan dipaparkan senarai edisi dan versi Quartus yang termasuk sokongan Maks II. Edisi percuma hanyalah Edisi Web.

Apabila memilih versi, perhatikan fakta bahawa Quartus II, bermula dengan versi 14.0, hanya berfungsi pada sistem 64-bit. Atas sebab ini, saya mengesyorkan memilih Quartus II 13.1. Seterusnya, proses kerja dan pemasangan akan diterangkan khusus untuk ketiga belasversi.

Selepas memilih versi, anda akan dibawa ke halaman pilihan muat turun untuk pengedaran Edisi Web Quartus II.

"Sistem Pengendalian" - Windows.

"Kaedah Muat Turun" pilih mengikut budi bicara anda. Perbezaan"Pengurus Muat Turun Akamai DLM3" daripada "Muat Turun Terus" ialah dalam kes pertama, sebelum memuat turun fail Quartus itu sendiri, anda perlu memuat turun dan menjalankan aplikasi tambahan di bawah OS Windows terlebih dahulu.Aplikasi ini membolehkan anda memilih beberapa fail untuk dimuat turun pada masa yang sama, dan juga menyokong meneruskannya. Apabila anda memilih mod muat turun "Muat Turun Terus", fail boleh dimuat turun secara berasingan, setiap satu menggunakan pautannya sendiri, menggunakan pelayar Web.

Dalam tangkapan skrin di atas, pilihan muat turun "Muat Turun Langsung" dipilih.

Muat turun fail "Perisian Quartus II" dan "MAX II, sokongan peranti MAX V". Ini adalah minimum yang diperlukan untuk bekerja dengan cip MAX II.

PENGENALAN

Biasanya, apabila seseorang melihat papan yang berfungsi, mereka sentiasa bertanya soalan yang sama: - Adakah ini Arduino? - Bagaimanakah ia berfungsi tanpa Arduino?

Ia bukan mikropengawal, ia bukan juga pemproses, ia adalah FPGA. FPGA ialah litar bersepadu logik boleh atur cara, litar mikro sedemikian terdiri daripada banyak blok atau makrosel yang sama, setiap pengeluar memanggilnya secara berbeza, jadi untuk Xilinx ia adalah Slices (hirisan) untuk Altera - LogicElements (elemen logik). Blok ini agak mudah, ia boleh bertindak sebagai beberapa elemen logik, menjadi jadual carian kecil (LUT), mengandungi penambah siap sedia, pengganda, blok pemprosesan isyarat digital (DSP), secara umum, semua yang ada dalam fikiran pengeluar. . Pengguna boleh mengatur dan mengkonfigurasi blok ini mengikut kehendaknya, dengan itu melaksanakan litar digital yang agak kompleks. Anda boleh melaksanakan walaupun mikropengawal pada FPGA, contohnya melaksanakan Arduino yang sama atau pemproses seni bina anda sendiri, contohnya, bukan pemproses daftar tetapi pemproses tindanan, anda juga boleh melaksanakan FPGA anda sendiri pada FPGA!

Antara FPGA bajet yang ada, dua pengeluar utama boleh dikenal pasti: Altera dan Xilinx dengan produk mereka anda boleh memulakan perjalanan anda untuk menguasai teknologi ini. Pada pendapat saya, adalah lebih baik untuk memilih cip Altera, kerana persekitaran reka bentuk mereka sentiasa dikemas kini, dan jika anda memilih satu cip Xilinx XC3S500E yang popular, anda perlu berpuas hati dengan persekitaran ISE 14.7 yang ketinggalan zaman (walaupun ia juga mempunyai kelebihannya) .

Dalam kesusasteraan asing anda boleh mencari singkatan untuk FPGA: FPGA dan CPLD. CPLD (Complex Programmable Logic Device) - cip dengan sebilangan kecil sel makro, blok khusus dan penggunaan kuasa yang rendah. Projek besar tidak boleh disintesis untuk jenis cip ini, tetapi ia juga digunakan dalam amalan, sebagai contoh, mikropengawal yang jarang ditemui mempunyai, katakan, 300 kaki. Cip sedemikian sering digunakan sebagai sistem antara muka, prapemproses dan pengembang I/O. FPGA (Field-Programmable Gate Array) ialah tatasusunan get field-programmable (FPGA), cip yang jauh lebih berkuasa berbanding CPLD, tetapi menggunakan lebih banyak kuasa dan kos yang lebih ketara. Untuk mengurangkan kos kawasan mati, cip FPGA boleh mengandungi fungsi sedia, seperti unit pemprosesan isyarat digital (unit DSP), pemproses terbenam dan memori terbenam. FPGA digunakan secara meluas untuk menguji dan mengesahkan reka bentuk, dalam apa yang dipanggil pengesahan pra-silikon, dengan itu mengurangkan kos dan masa sebelum keluaran produk. Cip FPGA boleh dikonfigurasikan semula pada hampir bila-bila masa pembangunan sedang dijalankan, contohnya di Intel, untuk menggabungkan seni bina pemproses konvensional dan cip FPGA. Xilinx sudah mempunyai penyelesaian sedemikian - Zynq, tetapi kami tidak akan membincangkannya buat masa ini.

Kami akan bercakap tentang perkara yang lebih mudah, terutamanya kerana saya mendapat kit pembangunan: Papan Teras FPGA Cyclone IV 4 dan Kit Pembangunan PLD Altera USB Blaster Downloader pada harga $35, dibeli di AliExpress.

1 Papan demo Cyclone IV 4 Papan Teras FPGA, penerangan ringkas

nasi. 1 - Pembayaran demo Papan Teras FPGA Cyclone IV 4

Papan (Gamb. 1) mempunyai cip EP4CE6E22C8N dipasang, ciri-cirinya:

| Jenis sumber | Penerangan ringkas | Kuantiti |

|---|---|---|

| Unsur logik (Les) | Bilangan blok logik - sel, ciri utama yang membolehkan kita membandingkan "kuasa" cip mana-mana logik yang disintesis akan menggunakan blok ini | 6,272 |

| Memori terbenam (Kbits) | Memori terbina dalam belum lagi menjadi ciri penting bagi kami | 270 |

| Pengganda 18x18 terbenam | Pengganda perkakasan terbina dalam, parameter yang sangat penting dalam pemprosesan isyarat digital, kuasa penuh FPGA didedahkan apabila beberapa pengganda beroperasi secara selari | 15 |

| PLL tujuan am | Nod gelung terkunci fasa, belum lagi menjadi ciri penting, memudahkan penyegerakan peranti yang beroperasi pada frekuensi yang berbeza | 2 |

| Rangkaian Jam Global | Bilangan domain kekerapan belum lagi menjadi ciri penting | 10 |

| Bank I/O Pengguna | Bilangan bank I/O pengguna yang berasingan belum lagi menjadi ciri penting | 8 |

| I/O pengguna maksimum | Bilangan pin I/O tersuai, kami boleh menyambungkan mana-mana peranti, seperti Arduino | 91 |

Lembaga mempunyai:

- Memori Denyar – Apabila kuasa digunakan, FPGA akan dikonfigurasikan untuk dilaksanakan dalam memori denyar. Anda boleh mensintesis projek anda dan menulis ke dalam denyar ini

- Kuarza 25 MHz ialah penjana frekuensi jam rujukan, pada frekuensi inilah semua projek kami akan beroperasi, FPGA kami boleh menyokong sehingga 10 saluran sedemikian.

- LED – 10, butang – 2.

- Pin I/O 61 + 2 tanah, 1 tidak disambungkan. Anda boleh menyambungkan pelbagai peranti. DAC-ADC, pecutan dan giroskop, watak dan paparan grafik, seperti Arduino.

- Bekalan kuasa melalui USB, atau 5V luaran.

Kit ini juga termasuk pengaturcara JTAG, Altera USB Blaster.

2. Persekitaran Quartus II dan projek pertama kami

Untuk bekerja dengan FPGA ini, kami perlu memuat turun persekitaran pembangunan rasmi - Edisi Web Quartus II, ianya percuma. Kami pergi ke laman web rasmi http://dl.altera.com/15.0/?edition=web, semasa menulis versi 15.0 adalah yang terbaru, jika lebih baharu, muat turunnya.

Pilih:

nasi. 2 - pilih produk Altera yang diperlukan

Dan klik butang muat turun (Muat Turun Fail Terpilih). Selepas itu kami akan diminta untuk mendaftar, mendaftar, memuat turun dan memasang.

Mari buat projek pertama kami.

Lancarkan Quartus, pilih menu utama Fail -> Wizard Projek Baru, tetingkap pengenalan muncul, klik seterusnya. Seterusnya anda perlu menentukan direktori untuk projek dan namanya, medan ketiga adalah nama modul teratas, anda akan melihat kemudian apa itu. Kami memilih folder di mana kami ingin menyimpan projek dan menghasilkan nama, saya mempunyai ujian1.

nasi. 3 - tetingkap wizard projek baharu

Klik seterusnya, kami ditanya sama ada ia projek kosong atau templat Projek. Biarkan kosong, seterusnya. Kemudian kami diminta untuk menambah fail sedia ada, kami tidak mempunyai apa-apa, kerana kami baru memulakan perjalanan kami, klik seterusnya.

Seterusnya, kita perlu memilih cip kita ini boleh dilakukan pada bila-bila masa. Kami memilih seperti dalam rajah, Keluarga - Siklon IV E, peranti khusus yang dipilih dalam "Peranti yang tersedia" dan pilih cip EP4CE6E22C8N kami, ia adalah pada mulanya. Jika anda mempunyai yang lain, cari milik anda, ini penting. Klik seterusnya.

nasi. 4 -

Tetingkap akan muncul - memilih alat reka bentuk, nyahpepijat, langkau ini buat masa ini, klik seterusnya dan kemudian selesai.

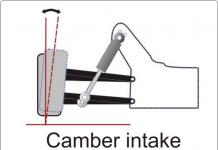

nasi. 5 - Tetingkap "Assinments-Deice"

Dalam tetingkap, pilih item "Pin tidak digunakan". Tetapan ini menentukan perkara yang berlaku kepada pin yang tidak disambungkan. Ini mungkin penting; dalam projek anda, anda tidak mungkin menggunakan semua pin, dan pin yang tidak disambungkan sebenarnya boleh disambungkan ke tanah atau kuasa (baik, anda tidak pernah tahu siapa yang memasangkan papan itu). Jika anda menggunakan satu pada pin yang dibumikan, ia akan hangus, jadi anda perlu memantau ini dengan teliti.

Secara lalai, pin yang tidak digunakan "Sebagai input tri-stated with weak pull-up" (pin input berada dalam keadaan ketiga dengan impedans tinggi, dengan power pull-up yang lemah), anda boleh meninggalkan atau memilih "Sebagai input tri-stated ”. Anda boleh membaca tentang perintang tarik-naik di Wikipedia https://ru.wikipedia.org/wiki/Pull-up_resistor. Dalam teknologi digital boleh terdapat tiga keadaan, yang logik ialah voltan bekalan atau tahap tinggi, sifar logik ialah apabila pin disambungkan ke tanah atau tahap rendah dan keadaan impedans tinggi. Keadaan impedans tinggi- ini adalah apabila pin mempunyai rintangan yang sangat tinggi dan praktikalnya tidak menjejaskan wayar yang ia disambungkan, keadaan ini diperlukan, sebagai contoh, apabila mengatur bas, apabila banyak peranti disambungkan ke satu wayar dan peranti tidak aktif tidak mengganggu; dengan operasi.

nasi. 6 - tetingkap "Peranti dan Pin Pilihan", Pin Tidak Digunakan

Kami menyambungkan semuanya dalam "Editor Tugasan"

nasi. 7 - Panggil "Editor Tugasan" daripada menu atau panel

Dalam tetingkap yang muncul, lakukan seperti yang saya lakukan, atau, jika betul-betul betul, kemudian mengikut rajah papan anda.

nasi. 8 - Editor Assinement

Dalam lajur "Kepada", masukkan nama input atau output. Dalam lajur "Nama Tugasan", pilih "Lokasi". Dalam lajur "Nilai" terdapat nombor pin litar mikro, mengikut rajah papan (saya mempunyai nombor pin yang ditulis terus di papan).

Anda juga perlu menentukan apa yang perlu dilakukan dengan butang, yang disambungkan dengan satu kaki ke tanah dan satu lagi ke input cip. Apabila anda menekan pada kaki akan ada tahap yang rendah, tetapi tanpa menekan, ia tidak jelas, kaki cip hanya akan tergantung di udara, yang sangat buruk. Anda perlu menyambungkan input cip kepada kuasa sama ada dengan perintang pada papan atau dengan cara yang lebih elegan dalam "Editor Tugasan". Dalam lajur "Nama Tugasan", pilih "Perintang Tarik Lemah" untuk kumpulan kunci* (kumpulan ditunjukkan dengan asterisk).

nasi. 9 - Editor Tugasan

Seterusnya, anda perlu membuat penerangan tentang modul peringkat atas, yang akan berfungsi secara langsung dengan kaki cip; semua modul lain hanya akan berfungsi dengannya. Dalam menu utama, klik Baharu, dan pilih "Fail Reka Bentuk-> Gambarajah Blok/Fail Skema".

nasi. 10 - Dialog fail baharu

Dalam tetingkap yang terbuka, pilih "Alat Pin" dan letakkan input dan output (pin input dan output) pada rajah. Kami menamakan semula input sebagai kunci, output sebagai led dan menyambungkannya dengan konduktor. Simpan dan klik "Mulakan Penyusunan".

nasi. 11 - Tetingkap penerangan grafik, Alat Pin dan Mulakan Kompilasi diserlahkan

Selepas penyusunan, kami mendapat amaran, kami mengabaikannya buat masa ini, ia berkaitan dengan pin yang tidak disambungkan, isyarat jam yang hilang dan penerangan untuk "Penganalisis Masa".

Kami menyambungkan papan demo dan pengaturcara, pilih alat "Programmer". Tetingkap harus mengatakan "USB-Blaster", jika tidak, kemudian klik "Persediaan Perkakasan" dan cuba fikirkan mengapa tidak, kemungkinan besar pemacu tidak dipasang, lihat peranti Windows, cari peranti yang tidak dikenali, mungkin ada masalah dengan kabel. Jika semuanya baik-baik saja, klik "Auto Detect" dan pilih cip kami.

nasi. 12 - Tetingkap Pengaturcara

Klik dua kali dalam medan "Fail" dan pilih fail untuk ditulis ke FPGA (terletak dalam folder output_files projek kami), semak medan "Program / Konfigurasi", dan klik butang "Mula".

nasi. 13 - Tetingkap pengaturcara, cip kami sudah dikonfigurasikan

Tahniah atas konfigurasi FPGA pertama anda! Diod D1 sepatutnya menyala, apabila anda menekan kekunci1 ia akan padam (memandangkan butang menutup kaki ke tanah), maka kami akan melakukan sesuatu mengenainya)

(C) Penyelidikan/VolgaSoft Teknologi moden.ALTERA.(bahan pengenalan) PENGENALAN Artikel ini akan membincangkan tentang keajaiban kecil moden, satu kejayaan yang dikira dalam dunia elektronik digital - cip logik boleh atur cara. Ini adalah batu bata yang terdapat dalam model paling moden ZX-SPECTRUM - GMX dan SPRINTER, ini adalah litar mikro yang sama di mana anda boleh melakukan hampir segala-galanya - dari Z80X (katakan, 30 MHz, kitaran mesin 1 jam), kepada segala-galanya bersama-sama dengan pemecut 2D, GS, tetikus dan pengawal IDE. Mungkin setiap radio amatur, apabila membangunkan peranti digital, bermimpi di dalam hatinya - di mana untuk mencari pil untuk semua penyakit - litar mikro yang akan menggantikan segala-galanya. Jurutera amat memerlukan peranti sedemikian, kerana apabila membangunkan produk yang serius mereka perlu mereka bentuk litar bersepadu tersuai "untuk tugas itu." Dari saat logik disusun sehingga produk berfungsi muncul, beberapa bulan biasanya berlalu dan sejumlah besar sumber telah dibelanjakan. Tetapi permintaan mencipta bekalan - litar bersepadu skala besar separa tersuai (LSI) dan tatasusunan logik boleh atur cara (PLA) telah muncul. Sains tidak berhenti, teknologi menjadi lebih dan lebih maju, dan suatu hari pelepasan pakej "perisian" + "perkakasan" + "batu" diumumkan. Idea ini sangat mudah: pembangun melukis gambar rajah dalam perisian (mungkin memindahkannya dari kertas), atau menerangkan logik produk masa depan dengan persamaan binari dan pengendali mudah, kemudian pengkompil menterjemah gambar rajah ke dalam beberapa kod, dan kod dijahit oleh pengaturcara (“perkakasan” ") ke dalam cip logik boleh atur cara ("batu"), yang boleh dipateri dengan serta-merta ke dalam papan. Dan tiada kos untuk pembangunan atau ujian cip. Pembangun peranti digital menerima produk baharu dengan hebat. Hari ini terdapat banyak pengeluar logik boleh atur cara (PL) LSI di pasaran. Produk mereka berbeza dalam kapasiti dan seni bina, serta dalam kualiti sokongan perisian dan perkakasan, perkhidmatan dan, akhirnya, kos. dikelaskan mengikut kriteria berikut: 1) darjah integrasi (bilangan get tersedia (elemen 2I-NOT) dan flip-flop); 2) seni bina penukar berfungsi paling mudah (sel); 3) organisasi struktur dalaman VLSI dan struktur matriks sambungan penukar berfungsi (kaedah menyambungkan sel);4) kehadiran memori RAM dalaman;5) teknologi untuk pembuatan elemen boleh atur cara (Fius, EPROM, EEPROM, FLASH, SRAM) - bagaimana litar berwayar. Untuk bekerja dengan kebanyakan syarikat BIS PLnya Altera menawarkan bahasa penerangan perkakasan MAX+plus II. atau daftar pemproses tambahan....). Anda boleh membuat perpustakaan fungsi perkakasan supaya tidak mencipta yang besar, seperti yang masih dilakukan oleh "pengekod" yang degil, dan membacanya mengikut tugas. "Perisian tegar" litar FLEX8282A yang sama ("paling mati", lihat di atas) berat, jika ingatan saya berfungsi dengan betul, 6kB. Semasa konfigurasi, semua kaki pengguna berada dalam keadaan Z dan tidak menjejaskan operasi sistem. Jika anda perlu membuat peranti "untuk kekal selama-lamanya" dan tidak mengkonfigurasinya setiap kali selepas menghidupkannya, anda boleh menggunakan keluarga MAX. Selain itu, sesetengah LSI keluarga MAX mempunyai perlindungan terhadap "kebocoran litar" - sedikit kerahsiaan pembangunan, bagaimanapun, pada pendapat saya, penggunaan keluarga ini agak terhad (sekurang-kurangnya dalam keadaan "rumah") kerana keperluan untuk pengaturcara dan bilangan kitaran pengaturcaraan yang terhad.SEKARANG BEBERAPA PERKATAAN TENTANG PERSEKITARAN PEMBANGUNAN: PERKAKASAN PENERANGAN BAHASA MAX + PLUS II.Sistem MAX + tambah II ditulis untuk platform berikut: PC, MAC, SUN. Speccy pun tidak , atas sebab tertentu, teman wanita yang terkenal itu tidak ada dalam senarai ini. Sistem ini sangat baik, mudah dan dengan kemungkinan yang luas. Komponen utama ialah penyunting grafik dan teks, pengkompil, penyunting gambar rajah (juga dikenali sebagai "debugger"), pemasa dan penyunting susun atur dan susun atur. Gambar rajah peranti dilukis dalam editor grafik (jika tugas grafik digunakan). Sebagai elemen skema, anda boleh menggunakan logik "mengikut tetamu borjuasi", keseluruhan siri ke-74 ada di sana, dan jika anda tidak menyukai sebutan musuh, anda boleh menarik segala-galanya dengan cara kami dan menjadikannya berfungsi. Penyunting teks digunakan untuk menyediakan penerangan teks perkakasan. Bahasanya berada di antara dBase, C, Pascal . Terdapat hampir perintah siap sedia untuk menerangkan mesin keadaan terhingga segerak, ada juga jika dan kes . Kad cip telefon diterangkan dan diuji (lihat di bawah) dalam satu jam tanpa meneran. Pengkompil menyemak skema (atau teks) dan menjana perisian tegar untuk "bata" yang diberikan. Had pengoptimuman boleh laras secara meluas untuk kelajuan dan kelantangan membolehkan anda memerah prestasi maksimum daripada peranti atau kawasan minimum yang diduduki pada cip. Terdapat satu perkara berguna yang direka oleh doktor. Menunjukkan di mana terdapat perlumbaan dan tempat berbahaya, dan dalam keadaan apa ia akan muncul, jangan lupa untuk meminta untuk menekan tetapan semula untuk memulakan peranti selepas menghidupkannya, dsb. Dalam editor gambar rajah, anda boleh mensimulasikan operasi peranti masa hadapan: katakan anda menetapkan isyarat input dan melihat keluaran yang sepadan jangan lupa untuk dipaparkan sama ada. Oleh itu, sebelum memasang litar, lebih baik untuk menjalankannya dalam "maks" dan menyemaknya. Benar, terdapat juga pepijat - T-trigger diperbuat daripada R.S. , disegerakkan oleh perbezaan, walaupun dalam praktiknya ia membajak. Melihat rajah dibuat dengan sangat mudah: anda boleh melihat rajah dengan menggabungkannya ke dalam kumpulan dan mempersembahkan sistem nombor yang mudah dilihat (perduaan, perpuluhan, perenambelasan). Data input juga boleh ditentukan oleh kod 2) seni bina penukar berfungsi paling mudah (sel); kelabu. Anda juga boleh melihat keadaan dalaman mesin. Keluarga Klasik termasuk 3 siri VLSI. LSI keluarga ini memungkinkan untuk menggantikan peranti yang mengandungi daripada 10 hingga 20 litar mikro tahap penyepaduan sederhana, dan menyediakan: * kelewatan perambatan isyarat daripada sebarang input dan output LSI tidak lebih daripada 10 ns; Nota: semua VLSI dalam siri ini mematuhi piawaian bas PCI. Pemasa - ia juga pemasa di Afrika - menunjukkan kelewatan dan kekerapan operasi maksimum yang mungkin bagi peranti. Penyunting susun atur dan susun atur digunakan untuk "perkakasan" mengalih keluar kaum (penyusunan semula sel logik) dan penempatan pin tersuai.Harga pengedar Malangnya, saya kehilangannya, jadi saya hanya boleh mengatakan dari ingatan bahawa FLEX10K10 berharga daripada $20, FLEX8282A daripada $8, elemen kos keluarga MAX daripada $3.3. Jika anda berminat di mana anda boleh mendapatkan maklumat, anda boleh tatal ke penghujung artikel, kerana maklumat lanjut akan menyusul. MAKLUMAT LANJUT TENTANG KELUARGAPENAMPILAN WWW.ALTERA.COM- di sana anda boleh mendapatkan maklumat yang lebih terperinci dan kunci elektronik untuk program MAX + Plus II (berpura-pura menjadi pelajar atau penyelidik).

ALTERA litar bersepadu logik boleh atur cara dan sistem reka bentuk bantuan komputer MAX+PLUS II

Litar bersepadu logik boleh atur (FPGA), atau dalam literatur asing yang disebut sebagai PLD (peranti logik boleh atur cara), ialah LSI digital separa tersuai, yang, berkat ciri seni bina dan teknologinya, boleh dibangunkan dan dihasilkan tanpa peralatan teknikal khusus. FPGA muncul di pasaran dunia pada pertengahan 80-an. Dan mereka serta-merta menjadi meluas, memindahkan proses mencipta LSI khusus dari kilang ke tempat kerja pereka. Kitaran pembangunan LSI telah dikurangkan kepada beberapa jam, dan kos yang berkaitan telah dikurangkan dengan ketara.

Sejak awal tahun 90an. Permintaan terbesar adalah untuk FPGA yang mempunyai:

penyepaduan logik tinggi berdasarkan teknologi CMOS;

kelajuan sehingga 80 -100 MHz dan lebih tinggi;

Kemungkinan pengaturcaraan (memuatkan konfigurasi dalaman) tanpa pengaturcara.

Semua keperluan ini dipenuhi oleh FPGA dari ALTERA (USA), peneraju dunia dalam bidang FPGA. Pada masa ini, ALTERA menghasilkan tujuh keluarga FPGA pelbagai seni bina [14].

Di Rusia, FPGA yang paling terkenal ialah keluarga Klasik, yang dihasilkan untuk beberapa lama oleh INTEL. Kelebihan utama litar mikro ini ialah kesederhanaan, kos rendah, pakej DIP yang mudah dipasang, penggunaan tenaga mikro dalam mod statik dan keupayaan untuk disokong oleh cara domestik (CAD FORS+, Blitz, Sterkh, pengaturcara Forsys). FPGA EP220 menggantikan mana-mana litar mikro siri 1556 (HP4, HP6, HP8, XL8).

Semua FPGA dihasilkan menggunakan teknologi CMOS (EPROM) boleh dipadam ultraviolet, yang menyediakan parameter penggunaan kuasa berikut:

dalam mod statik - 10-30 µA;

pada frekuensi 1 MHz - 2-8 mA;

dengan peningkatan kekerapan jam - 1 mA/MHz.

Untuk mengurangkan harga sebanyak 30-40% semasa pengeluaran besar-besaran produk, semua FPGA juga dihasilkan dalam bungkusan plastik (DIP dan PLCC) dengan pengaturcaraan sekali sahaja.

Kelemahan FPGA bagi keluarga klasik ialah tahap penyepaduan yang agak rendah dan beberapa ciri seni bina: kekurangan input untuk pencetus ditetapkan kepada "1" (SET), menyekat kenalan apabila melaksanakan elemen memori dalaman.

FPGA bagi keluarga MAX7000 dan FLASHlogic, yang mempunyai seni bina matriks, i.e. mengandungi matriks boleh atur cara get logik “AND”, “OR” dan flip-flop.

Keluarga MAX7000 terdiri daripada tujuh cip dengan tahap penyepaduan antara 1,200 hingga 10,000 get logik setara, yang mengandungi daripada 32 (EPM7032) hingga 256 (EPM 7256) selipar.

Selain itu, FPGA EPM7032V dihasilkan - analog berfungsi cip EPM7032 dengan voltan bekalan 3.3 V.

Keluarga FPGA MAX7000 dihasilkan menggunakan teknologi CMOS (EEPROM) boleh dipadam elektrik. Mereka menyediakan:

kelewatan perambatan isyarat minimum dari input ke output 5 ns;

kekerapan jam maksimum 190 MHz;

sehingga 100 kitaran pengaturcaraan/padam.

Keluarga MAX7000 FPGA mempunyai seni bina yang fleksibel. Makrosel mereka mengandungi dua baris maklum balas bebas; daripada pencetus dan daripada kenalan. Ini membolehkan flip-flop digunakan sebagai daftar dalaman dan pin digunakan sebagai port input pada masa yang sama. Sumber tambahan FPGA ialah istilah pengembangan - konjungtor, output songsang yang membentuk sambungan maklum balas dengan matriks elemen "DAN". Syarat membenarkan anda menjana isyarat kawalan (contohnya, CLK, SET, RESET) tanpa perbelanjaan makrosel. Hasil daripada pengagihan semula istilah antara makrosel, bilangan input unsur "ATAU" boleh ditingkatkan kepada 32.

Setiap makrosel mempunyai bit turbo individu, pengaturcaraan yang membolehkan anda mengurangkan penggunaan kuasa dengan sedikit penurunan dalam prestasi. Mulai tahun 1996, semua FPGA keluarga MAX7000 akan tersedia dalam varian ISP (dalam sistem boleh atur cara). Ini akan membolehkan anda memprogram dan memadam litar terus pada papan kerja melalui antara muka isyarat ke-4 yang disambungkan ke port komputer. Kehadiran pengaturcara menjadi pilihan, yang sangat memudahkan dan mengurangkan kos penggunaan FPGA.

Keluarga MAX7000 FPGA adalah kos rendah. Sebagai contoh, harga cip EPM7032 kurang daripada 7, dan cip EPM7128 kurang daripada 25.

Dengan kemunculan keluarga MAX7000, nilai praktikal FPGA yang dihasilkan sebelum ini bagi keluarga MAX5000 telah menurun dengan ketara, kerana analog semua litar mikro telah muncul (contohnya, EPM5128 - EPM7128) dengan prestasi yang lebih baik dan ciri penggunaan kuasa pada harga yang lebih rendah.

MAX+PLUS II ialah sistem reka bentuk litar bersepadu logik boleh atur cara automatik (FPGA) yang dibangunkan oleh Altera Corporation, peneraju global dalam pembuatan FPGA.

MAX+PLUS II ialah produk perisian pelbagai fungsi yang memberikan pereka keupayaan untuk mereka bentuk FPGA sepenuhnya, daripada memasuki litar yang pereka bentuk berhasrat untuk melaksanakan pada FPGA dan berakhir dengan pengaturcaraan FPGA itu sendiri pada pengaturcara.

MAX+PLUS II menawarkan pilihan pengguna berikut:

input struktur dalaman FPGA dengan input grafik rajah berfungsi;

input struktur dalaman FPGA menggunakan bahasa pengaturcaraan peringkat tinggi Altera Hardware Description Language (AHDL), yang dibina sepenuhnya ke dalam shell MAX+PLUS II;

pemodelan operasi FPGA dalam bentuk rajah masa;

Jika anda mempunyai pengaturcara, tulis struktur yang direka bentuk ke FPGA, dsb.

Apabila menerangkan struktur dalaman FPGA menggunakan AHDL, beberapa pilihan adalah mungkin.

Dalam pilihan pertama, huraikan struktur dalam primitif, i.e. menggunakan fungsi mudah seperti RS-trigger, D-trigger, T-trigger, JK-trigger, dsb.

Dalam pilihan kedua, jalankan penerangan menggunakan primitif dan fungsi mega.

Fungsi mega adalah fungsi logik yang kompleks seperti pembilang, pemultipleks, penyahkod, daftar, dll.

Kelebihan pilihan pertama ialah penterjemah menghabiskan lebih sedikit masa untuk menukar fungsi AHDL yang paling mudah kepada kod mesin.

Kelemahan pilihan ini ialah jumlah teks program yang besar dan keperluan untuk penerangan terperinci tentang keseluruhan sistem.

Dalam pilihan kedua, apabila menggunakan fungsi mega, tidak ada keperluan untuk penerangan terperinci tentang elemen dalam erti kata bahawa pengaturcara menetapkan hanya parameter fungsi logik yang kompleks. Contohnya, menggunakan fungsi mega lpm_counter, pembilang boleh diterangkan dengan menyatakan hanya input jam dan lebar pembilang itu sendiri. Ini dengan ketara mengurangkan kelantangan yang diduduki oleh teks program, dan juga membolehkan anda mengurangkan sedikit masa yang diperlukan untuk menulis program.

Kelemahannya ialah ia mengambil lebih banyak masa untuk menterjemah program ke dalam kod mesin berbanding dengan pilihan pertama.

Tetapi pada akhirnya hasilnya adalah sama, jadi gaya penulisan produk perisian bergantung sepenuhnya kepada pereka.

Apabila menyahpepijat produk perisian bertulis, SIMULATOR MAX+PLUS II membolehkan anda meneliti secara terperinci hasil operasi FPGA dalam bentuk rajah pemasaan. Pereka bentuk boleh memilih pelbagai output dan keadaan perantaraan yang diterangkan dalam program, serta menentukan pelbagai tindakan input.

Syarikat pertama memasuki pasaran dengan litar bersepadu boleh atur cara (FPGA). Altera menawarkan dua sistem CAD: MAX+PLUS II dan Quartus II. Setiap sistem CAD menyokong semua fasa reka bentuk: Input Reka Bentuk, Penyusunan, Pengesahan dan Pengaturcaraan. Setiap sistem CAD mempunyai Tutorial, yang dipasang semasa memasang pakej. Tutorial terdiri daripada kelas yang membimbing anda melalui keseluruhan kitaran reka bentuk daripada input reka bentuk kepada pengaturcaraan cip. Semasa pemasangan, fail juga dipasang yang menerangkan projek supaya semasa belajar Tutorial anda boleh melangkau pelajaran individu dan menggunakan fail siap sedia. Sebagai contoh, anda boleh melangkau "Input Projek" dan pergi ke "Kompilasi" projek menggunakan fail siap sedia.

Sistem MAX+PLUSII mempunyai algoritma sintesis yang cekap yang membenarkan penggunaan maksimum sumber cip dan set alat yang besar untuk pengesahan peranti pada tahap reka bentuk berfungsi dan pemasaan.

Syarikat itu juga mengedarkan Kit Reka Bentuk khusus yang memudahkan penggunaan FPGA dalam tugas tertentu. Kit sedemikian mengandungi fungsi logik serasi CAD dan metodologi untuk menggunakannya. Yang menarik ialah Kit Reka Bentuk, khusus untuk pembangunan produk dalam standard bas PCI dan litar pemprosesan isyarat digital. Yang pertama termasuk fungsi templat untuk melaksanakan pengawal (Master/Slave) dan litar semakan pariti.

Yang kedua tertumpu pada pelaksanaan litar yang cekap seperti pengganda, penapis FIR, operasi titik terapung, transformasi Fourier, transformasi Reed-Solomon, dll.

MAX direka bentuk untuk antara muka dengan piawaian VHDL, EDIF, Verilog. Sebarang konfigurasi CAD mengimport data input dalam format EDIF dan menghasilkan hasil reka bentuk dalam semua format yang disenaraikan. Menggunakan program penterjemah, adalah mungkin untuk mengimport maklumat ke dalam format penerangan teks CAD MAX daripada fail dalam format PDS (CAD PLDShell, PALASM) dan XNF (CAD XACT dari Xilinx). Ia adalah mungkin untuk menukar gambar rajah yang dibuat dalam sistem OrCAD ke dalam fail dalam format editor grafik anda sendiri.