Penukar digital-ke-analog(DAC) – peranti yang menukar isyarat digital input (kod) kepada analog.

DAC digunakan secara meluas di mana perlu, menggunakan maklumat digital yang dikeluarkan oleh komputer, untuk mengawal peranti analog, sebagai contoh, untuk menggerakkan injap yang berkadar dengan nilai yang dikira bagi isyarat digital. DAC digunakan untuk menyelaraskan komputer (DC) dengan peranti analog, sebagai komponen dalaman ADC dan alat pengukur digital. Sebagai sebahagian daripada penukar analog-ke-digital, DAC digunakan untuk menjana isyarat analog (semasa atau voltan), yang dengannya isyarat ditukar dibandingkan.

Ciri utama DAC ialah resolusi, ditentukan oleh bilangan bit n. Secara teorinya, DAC yang menukar n-bit kod binari, mesti menyediakan 2 n nilai isyarat keluaran yang berbeza dengan resolusi (2 n– 1)-1. Nilai mutlak kuantum voltan keluaran minimum ditentukan sebagai nombor maksimum yang diterima 2 n– 1, dan voltan keluaran maksimum DAC, dipanggil voltan skala U sekolah Oleh itu, dengan 12 bit, bilangan kuanta bebas (langkah) voltan keluaran DAC ialah 212 – 1 = 0.0245%. Voltan skala pilihan rujukan U shk = 10B, dibahagikan dengan bilangan kuanta ini, memberikan resolusi mutlak DAC

D x = U shk/(2 n– 1) = 103 mV/ (212 – 1) = 2.45 mV.

Ciri penukaran(HP) DAC– set nilai kuantiti analog keluaran xi bergantung kepada kod input b i.

Ciri penukaran (atau ciri pemindahan) DAC ditunjukkan dalam Rajah. 3.15.

nasi. 3.15. Ciri pemindahan DAC; A– kelinearan; B– tidak linear; C– tidak monotoni; D– isyarat keluaran; E– garis lurus yang menghubungkan nilai ideal tahap isyarat keluaran; dпш – ralat skala penuh

Perbezaan antara nilai resolusi sebenar dan nilai teori adalah disebabkan oleh ralat nod dan bunyi DAC. Ketepatan DAC ditentukan oleh nilai ralat mutlak peranti, ketaklinieran dan ketaklinear pembezaan.

Ralat mutlak dshk mewakili sisihan nilai voltan keluaran (semasa) daripada nilai pengiraan nominal sepadan dengan titik akhir ciri penukaran (lihat Rajah 3.15). Ralat mutlak biasanya diukur dalam unit digit terkecil (LSB).

Ketaklinearan dl mencirikan identiti kenaikan minimum isyarat keluaran ke atas keseluruhan julat penukaran dan ditakrifkan sebagai sisihan terbesar isyarat keluaran daripada garis lurus ketepatan mutlak yang dilukis melalui sifar dan titik nilai maksimum isyarat keluaran . Nilai tak lineariti tidak boleh melebihi ±0.5 unit MZ.

Ketaklinearan pembezaan dl.dif mencirikan identiti kenaikan isyarat bersebelahan. Ia ditakrifkan sebagai perbezaan minimum dalam ralat tak linear dua kuanta bersebelahan dalam isyarat keluaran. Nilai ketaklinearan pembezaan tidak boleh melebihi dua kali ganda nilai ralat ketaklinieran. Jika nilai dl.diff lebih besar daripada satu MZR, maka penukar dianggap tidak monotonik, i.e. pada outputnya, isyarat keluaran tidak boleh meningkat secara seragam dengan peningkatan seragam dalam kod input.

Ketidakmonotonan dalam sesetengah kuanta mengakibatkan penurunan dalam isyarat keluaran apabila kod input meningkat.

Ralat perkakasan, yang ditentukan oleh ketidakstabilan sumber voltan rujukan, ralat suis, matriks rintangan dan penguat operasi keluaran, dipanggil ralat instrumental. Faktor utama yang menyebabkan ralat elemen ialah: variasi teknologi dalam parameter; kesan perubahan alam sekitar (terutamanya suhu); perubahan dalam parameter dari masa ke masa (penuaan); pendedahan kepada bunyi dan gangguan luaran dan dalaman.

Semua kesilapan instrumental menunjukkan diri mereka terutamanya dalam bentuk berikut:

a) offset sifar, yang mencirikan anjakan selari ciri pemindahan DAC daripada garis lurus purata (disebabkan oleh voltan mengimbangi sifar dan arus input bukan sifar op-amp, serta parameter baki suis) ;

b) perubahan dalam pekali penghantaran, yang mencirikan sisihan cerun ciri penghantaran sebenar dari garis lurus purata;

c) sisihan ciri pemindahan penukar daripada garis lurus yang ideal (ketaklinieran penukaran tersebut menunjukkan dirinya sebagai kenaikan isyarat keluaran yang tidak sama sebagai fungsi kod input).

Ciri dinamik DAC termasuk parameter pemasaan dan kekerapan penukaran maksimum.

Parameter masa menentukan kelajuan penukar. Terdapat tiga parameter masa: langkah pengkuantitian (tempoh) D t, masa penukaran (masa penyelesaian isyarat output) t pr, tempoh kitaran penukaran t c.

Langkah pengkuantitian (tempoh) D t– selang masa antara dua transformasi berturut-turut. Nilai songsang bagi tempoh pengkuantitian 1/D t = f kV dipanggil kekerapan kuantisasi.

Masa persediaan output DAC t pr – masa dari saat kod berubah pada input DAC sehingga saat apabila nilai nilai analog keluaran berbeza daripada nilai yang ditetapkan oleh nilai yang diberikan (Rajah 3.16).

nasi. 3.16. Definisi masa t pr penukaran DAC

Masa kitaran penukaran t ts – masa antara saat penyerahan kod input dan pengeluaran isyarat analog output ( t ts = t dan lain-lain). Ia ditentukan terutamanya oleh siklogram dan rajah pemasaan yang menerangkan pengendalian maklumat dan peranti dan sistem pengkomputeran dengan penukar sedia ada.

Kekerapan penukaran maksimum – kekerapan pensampelan tertinggi di mana parameter DAC sepadan dengan nilai yang ditentukan.

Operasi DAC selalunya disertai dengan denyutan sementara tertentu, yang merupakan puncak tajam amplitud besar dalam isyarat keluaran, yang timbul disebabkan oleh perbezaan dalam masa buka dan tutup suis analog dalam DAC. Outlier amat ketara apabila, bukannya sifar dalam digit paling ketara dan satu dalam digit tertib rendah kod, satu unit memasukkan digit paling ketara (MSB) dan kod itu ialah "semua sifar" dalam LSB. Sebagai contoh, jika kod input 011...111 digantikan dengan kod 10...000, dan kekunci DAC yang lebih tinggi dibuka kemudian daripada kekunci yang lebih rendah ditutup, maka isyarat keluaran hanya akan bertambah satu. kuantum boleh disertai dengan nadi dengan amplitud 0.5 U sekolah Tempoh puncak ini akan sepadan dengan kelewatan dalam menukar keadaan kunci.

Pada masa ini, bergantung pada nilai parameter, DAC ketepatan dan berkelajuan tinggi dibezakan. DAC ketepatan mempunyai dl = 0.1%, dan berkelajuan tinggi t mulut = 100ns.

Penukar digital-ke-analog (DAC) direka bentuk untuk menukar kuantiti input (nyahkod) secara automatik yang diwakili oleh kod berangka ke dalam nilai sepadan kuantiti yang berubah-ubah secara berterusan (iaitu, analog). Dalam erti kata lain, DAC melakukan penukaran yang bertentangan berbanding dengan ADC. Kuantiti fizikal keluaran ADC paling kerap mewakili voltan dan arus elektrik, tetapi juga boleh menjadi selang masa, pergerakan sudut, dll. Dalam sistem automasi dengan komputer, lebih mudah untuk memproses (menukar dan menghantar) isyarat digital, tetapi ia lebih biasa dan mudah untuk seseorang (pengendali). melihat isyarat analog yang sepadan dengan nilai kod angka. Dengan bantuan ADC, maklumat dimasukkan ke dalam komputer, dan dengan bantuan DAC, ia adalah output daripada komputer untuk mempengaruhi objek terkawal dan dirasakan oleh seseorang.

Litar DAC biasanya menggunakan perwakilan nombor binari yang terdiri daripada beberapa digit sebagai jumlah kuasa 2. Setiap digit (jika mengandungi 1) ditukar menjadi isyarat analog yang berkadar dengan nombor 2 kepada kuasa yang sama dengan nombor digit dikurangkan dengan satu.

Dalam Rajah. Rajah 4.38 menunjukkan litar DAC ringkas, asasnya ialah matriks perintang - satu set perintang yang disambungkan kepada input penguat kendalian oleh suis yang dikawal oleh bit yang sepadan bagi nombor binari. Triod (contohnya, transistor MOS) boleh digunakan sebagai suis. Jika 1 ditulis dalam bit ini, maka kunci ditutup, jika 0, kunci dibuka.

Keperluan untuk menggunakan penguat operasi adalah disebabkan oleh fakta bahawa isyarat keluaran dalam DAC adalah analog. Kedua-dua isyarat input dan output bagi op-amp ialah voltan DC (dalam erti kata kekutuban malar).

Keuntungan penguat operasi adalah sama dengan nisbah rintangan perintang R os dalam litar maklum balas kepada rintangan perintang pada input penguat, yang, seperti yang boleh dilihat dari Rajah. 4.38, setiap digit mempunyai makna tersendiri. Pekali pemindahan K =- U keluar / U op untuk setiap bit nombor binari yang ditukar (jika 1 ditulis dalam bit ini) masing-masing sama dengan: K 0 =R o.s/ R 0 ;K 1 = 2R o.s/ R 0 ;K 2 = 4R o.s/ R 0 ;

K 3 = 8R o.s/ R 0 . Voltan keluaran DAC

U keluar = - U op ( K 3 +K 2 +K 1 + K 0) =

= - U op ( R o.s/ R 0)(8x 3 + 4x 2 + 2x 1 + x 0),

di mana X mengambil nilai 1 atau 0 bergantung pada apa yang ditulis dalam bit tertentu nombor binari.

nasi. 4.38. Litar digital-analog

penukar berdasarkan matriks rintangan

Oleh itu, nombor perduaan empat digit ditukar kepada voltan U keluar, yang boleh mengambil 16 nilai yang mungkin dari 0 hingga 15D u kv, di mana D u kv - langkah pengkuantitian.

Untuk mengurangkan ralat pengkuantitian, adalah perlu untuk meningkatkan bilangan bit binari DAC. Apabila membuat litar bersepadu DAC menggunakan skema ini, sangat sukar untuk membuat perintang berketepatan tinggi dengan rintangan yang berbeza antara satu sama lain dengan berpuluh atau ratusan kali. Di samping itu, beban voltan rujukan U op berubah bergantung pada keadaan kunci, jadi perlu menggunakan sumber dengan rintangan dalaman yang rendah.

Litar DAC ditunjukkan dalam Rajah. 4.39, adalah bebas daripada kelemahan yang dinyatakan. Di dalamnya, pekali pemberat setiap digit ditetapkan dengan pembahagian jujukan voltan rujukan menggunakan matriks rintangan jenis R- 2R, yang merupakan pembahagi voltan berbilang pautan.

Litar DAC ini menggunakan suis dua kedudukan yang menyambungkan perintang 2 R sama ada kepada input penguat kendalian (dengan 1 dalam bit ini), atau kepada wayar neutral sepunya. Rintangan input matriks perintang tidak bergantung pada kedudukan kekunci. Pekali penghantaran antara nod matriks bersebelahan ialah 0.5. Voltan keluaran

U keluar = - U op ( R/16R)(x 1 + 2x 2 + 4x 3 + 8x 4).

nasi. 4.39. Litar penukar digital ke analog

berdasarkan matriks rintangan R-2R

Pengaruh terbesar pada ralat DAC adalah disebabkan oleh sisihan rintangan perintang dari nilai nominalnya, dan juga oleh fakta bahawa dalam suis sebenar rintangan dalam keadaan tertutup tidak sama dengan infiniti, dan dalam keadaan terbuka ia tidak sama dengan sifar. Matriks rintangan yang dihasilkan mempunyai ralat relatif kira-kira seperseratus peratus, i.e. adalah sangat tepat.

4.5.2. Pengekodan selari penukar analog-ke-digital

Penukar analog-ke-digital (ADC) direka untuk menukar (mengukur dan mengekod) secara automatik mengubah kuantiti (iaitu analog) ke dalam nilai kod berangka yang sepadan. Dalam kes ini, perkataan "digit" bermaksud kod binari. Apabila kita bercakap tentang rakaman bunyi digital dan peralatan mengeluarkan semula atau telefon digital, kami bermaksud bahawa isyarat bunyi yang sentiasa berubah dirakam atau dihantar secara digital, i.e. dalam bentuk kod binari (binari).

Bergantung pada kaedah penukaran, ADC dibahagikan kepada siri, selari dan selari siri.

ADC bertindak terpantas ialah jenis selari. Mereka menukar isyarat analog kepada kod dalam satu langkah, tetapi ADC tersebut memerlukan beberapa pembanding. Voltan input secara serentak dibandingkan dalam semua pembanding dengan voltan rujukan berbilang. ADC selari mempunyai bilangan elemen yang lebih besar daripada yang bersiri.

Mari kita pertimbangkan operasi tiga-bit selari

ADC (Rajah 4.40).

nasi. 4.40. Litar ADC tiga bit selari

Tiga digit binari boleh mewakili lapan nombor - dari 0 hingga 7. Oleh itu, tujuh pembanding digunakan untuk membandingkan voltan masukan dengan voltan rujukan yang diperoleh menggunakan pembahagi perintang. Setiap pembanding menghantar isyarat 0 jika voltan input kurang daripada voltan rujukan, dan isyarat 1 sebaliknya.

Keadaan pembanding dan kod binari yang sepadan dibentangkan dalam Jadual. 4.12. Penukar kod menghasilkan nombor tiga digit binari. Masa penukaran ADC selari boleh menjadi beberapa puluh nanosaat, iaitu ratusan kali lebih cepat daripada ADC bersiri.

Jadual 4.12

Kebergantungan kod digital pada voltan input

| Nilai voltan masukan relatif U=U input /U op | Status pembanding | Nombor kod binari | ||||||||

| U< 0,5 | ||||||||||

| £0.5 U< 1,5 | ||||||||||

| £1.5 U< 2 ,5 | ||||||||||

| £2.5 U < 3,5 | ||||||||||

| £3.5 U< 4,5 | ||||||||||

| £4.5 U< 5 ,5 | ||||||||||

| £5.5 U<6 ,5 | ||||||||||

| £6.5 U |

4.5.3. Penukar A/D Bersiri

Dalam Rajah. Rajah 4.41 menunjukkan litar ADC jenis bersiri.

nasi. 4.41. Litar analog-ke-digital

penukar bersiri

Pada arahan "Mula", mesin digital penonton sasaran menjana urutan nombor perduaan yang disalurkan kepada input penukar digital-ke-analog DAC yang menjana voltan U DAC sepadan dengan setiap isyarat binari input. Voltan ini (terus berkembang semasa bekerja) penonton sasaran) dibekalkan kepada salah satu input pembanding K, input lain yang menerima voltan masukan U input.Pembanding membandingkan kedua-dua voltan ini dan menghasilkan isyarat apabila ia sama. Dengan isyarat ini penonton sasaran berhenti, dan kod binari yang sepadan dengan U input Oleh itu, penukaran dalam ADC bersiri berlaku dalam mod langkah. Nilai output adalah dalam langkah berasingan (kitaran), i.e. konsisten mendekati nilai yang diukur. Oleh itu, ADC bersiri menghabiskan banyak masa pada setiap penukaran isyarat analog. Untuk meningkatkan prestasi mereka, kaedah pengimbangan bitwise digunakan. Gambar rajah yang menggambarkan kaedah ini ditunjukkan dalam Rajah. 4.42.

nasi. 4.42. Litar penukar analog-ke-digital

dengan pengimbangan sedikit demi sedikit

Peranan mesin digital dilakukan oleh daftar Rg dengan sensor nadi jam DTI. Kod output dibaca berdasarkan isyarat daripada litar kesediaan data SRS, yang dibekalkan apabila isyarat tiba dari pembanding K kira-kira voltan masukan yang sama U input dan voltan U DAC Operasi pembanding disegerakkan oleh denyutan DTI.Denyutan yang sama memindahkan bit daftar secara berurutan Rg untuk menyatakan 1. Pemindahan bermula dari bit yang paling ketara, dan yang paling kurang ketara kekal dalam keadaan 0. Dalam kes ini, DAC menghasilkan voltan yang sepadan, yang dibandingkan dalam pembanding K dengan input. Jika U DAC > U input, kemudian pada arahan pembanding, bit yang paling ketara ditetapkan semula kepada keadaan 0; Jika U DAC< Um, maka bit paling ketara kekal 1. Kemudian bit tertinggi seterusnya dipindahkan ke keadaan 1 Rg dan voltan dibandingkan semula U DAC dan U input. Kitaran diulang sehingga kesamaan voltan yang ditunjukkan direkodkan apabila salah satu digit tertib rendah dipindahkan ke keadaan 1. Selepas itu SRS memberi isyarat untuk mengeluarkan kod output. Bilangan kitaran perbandingan dalam ADC sedemikian akan sama dengan bilangan bit kod keluaran.

4.6. Tatasusunan logik boleh atur dan litar bersepadu

Organisasi ROM dan tatasusunan logik boleh atur cara (PLM) mempunyai banyak persamaan. Marilah kita mengenal pasti pendekatan umum untuk membina skema ini menggunakan contoh.

Mari kita anggap bahawa adalah perlu untuk membina peranti yang menyediakan isyarat keluaran Y1 apabila kod 000, 001 diterima pada input; di pintu keluar Y2 dengan kod 010, 100, 110; di pintu keluar Y3 dengan kod 011, 101, 110, 111. Kod yang dibekalkan kepada input peranti boleh dianggap sebagai kod alamat sel ROM bit tunggal, dari mana unit dibaca melalui elemen OR dibekalkan kepada salah satu output Y i. Mari kita pertimbangkan hubungan antara alamat dan data - fungsi

(Jadual 4.13).

Dalam Rajah. 4.43, A litar ROM dibentangkan, yang terdiri daripada penyahkod alamat pada elemen logik dan elemen storan dalam bentuk litar diod-resistif, litar yang termasuk pelompat. Pembolehubah X3, X2, X1 dianggap sebagai kod alamat pelbagai sel memori. Dari meja Rajah 4.13 menunjukkan bahawa dalam penyahkod, pada alamat tertentu, bas keluaran yang sepadan teruja, yang mesti digabungkan pada salah satu keluaran litar: Y1, Y2, Y3. ATAU elemen yang digunakan untuk menghasilkan isyarat Y i, mewakili pengekod yang tidak lengkap.

Jadual 4.13

Jadual kebenaran penyahkod

| Alamat | Input | Keluar | ||||

| X3 | X2 | XI | Y1 | Y2 | Y3 | |

| A0 A1 A2 A3 A4 A5 A6 A7 |

Dalam Rajah. 4.43, b Litar ROM yang sama dibentangkan dalam bentuk dua matriks. Matriks A1 ialah penyahkod linear lengkap dengan lapan output. Setiap garis menegak masuk A1 sepadan dengan elemen AND dengan tiga input, setiap satunya melaksanakan salah satu gabungan pembolehubah input X3, X2, X1. Matriks A2 ialah pengekod yang tidak lengkap.

nasi. 4.43. Matriks ROM sebagai asas PLM

Setiap garis mendatar masuk A2 sepadan dengan get OR lapan input. Pembentukan isyarat yang diperlukan pada setiap inputnya ditunjukkan oleh titik di persimpangan garis menegak matriks A1 dan garisan matriks mendatar A2.

Gambar rajah yang ditunjukkan dalam Rajah. 4.43 boleh dilaksanakan dalam bentuk litar gabungan pada PLM (Rajah 4.44).

nasi. 4.44. Litar gabungan pada PLM

Membandingkan dua litar yang menjalankan fungsi yang sama (lihat Rajah 4.43, b dan 4.44), kita melihat bahawa litar yang dilaksanakan dalam bentuk PLM adalah lebih mudah. Matriks A1 dalam ROM ia adalah penyahkod yang lengkap dan diprogram keras; dalam matriks PLM ia adalah minterms boleh diprogramkan untuk fungsi. Kos peralatan biasanya ditentukan oleh kawasan cip semikonduktor yang diduduki oleh litar. Oleh itu, litar yang dibuat pada PLM memberikan tahap penyepaduan yang lebih tinggi dan dengan itu mengembangkan kefungsian litar mikro.

BAB 5.

ALAT PENGKOMPUTERAN UNTUK PEMPROSESAN MAKLUMAT DALAM SISTEM PENGAUTOMASIAN

5.1. Mikropemproses dalam sistem automasi tekstil

Litar mikro digital kini telah mencapai prestasi tinggi dengan penggunaan semasa yang boleh diterima. Litar mikro digital terpantas mempunyai kelajuan pensuisan dari urutan 3 - 5 ns. Dalam litar mikro ini, penggunaan semasa adalah berkadar terus dengan kelajuan pensuisan get logik dalam litar mikro.

Satu lagi sebab untuk penggunaan meluas mikropemproses ialah mikropemproses ialah cip universal yang boleh melaksanakan hampir semua fungsi. Kesejagatan memastikan permintaan yang luas untuk litar mikro ini, yang bermaksud pengeluaran besar-besaran. Kos litar mikro adalah berkadar songsang dengan pengeluaran besar-besaran mereka, iaitu, mikropemproses menjadi litar mikro murah dan dengan itu meningkatkan permintaan lebih banyak lagi.

Setakat yang paling besar, semua sifat di atas ditunjukkan dalam mikrokomputer cip tunggal atau, kerana ia lebih kerap dipanggil oleh bidang aplikasinya: mikropengawal. Pengawal mikro menggabungkan semua komponen komputer pada satu cip: mikropemproses (sering dipanggil teras mikropengawal), RAM, ROM, pemasa dan port I/O.

Dengan peralihan kepada automasi kompleks teknologi pengeluaran tekstil dan kemunculan cara untuk pelaksanaannya dalam bentuk subsistem kawalan mikropemproses khusus (MPCS), persoalan timbul mengenai peraturan berbilang berkaitan beberapa parameter. Ini memerlukan penyelesaian isu mengenal pasti proses teknologi, perkaitan dan kebolehkawalannya mengikut parameter yang dicadangkan oleh ahli teknologi seperti yang dikawal. Dengan bantuan MPSU, tugas utama berikut boleh diselesaikan dalam automasi pengeluaran tekstil yang kompleks.

1. Maklumat dan pengukuran, memastikan pengumpulan maklumat yang luas; imuniti bunyi; pemprosesan data statistik yang diperlukan, pembetulan perisian bagi ralat pengukuran, diagnostik automatik dan penentukuran kendiri sistem pengukuran. Pada masa yang sama, logik operasi boleh atur cara MPSU memberikan fleksibiliti dalam konfigurasi semula dan membolehkan anda mengembangkan fungsi sistem semasa pemodenan tanpa perubahan litar yang ketara.

2. Pengawalseliaan parameter teknologi dan mod pengendalian peralatan, membolehkan untuk mengekalkan parameter yang dikawal oleh ahli teknologi pada nilai tertentu atau mengubahnya untuk memenuhi syarat pengoptimuman dalam sistem kawalan berbilang sambungan, kelajuan masa, tenaga dan penunjuk kualiti. Walau apa pun, kualiti peraturan ditentukan oleh kebolehpercayaan pengukuran dan maklumat yang diterima.

3. Kawalan mod pengendalian peralatan teknologi dan robotik, dilaksanakan terutamanya dalam bentuk pengendali auto atau manipulator auto yang menjalankan operasi, contohnya, pemunggahan dan pemunggahan bal gentian, penggelek meledingkan dan rasuk tenunan, menanggalkan dan memasang gelendong pada gulungan dan mesin berputar , mengisi stesen berputar dengan kartrij , pita pita dan simpulan, dsb.

Penyelarasan operasi semua kawalan peralatan proses, termasuk peraturan aliran isyarat dalam masa dan ruang dan pemprosesannya, dijalankan oleh peranti kawalan pusat. Peranti kawalan pusat moden adalah elektronik dan dibahagikan kepada yang universal menggunakan mikrokomputer dan yang khusus menggunakan mikropengawal, mikropemproses dan litar logik.

Penggunaan prinsip kawalan program dalam sistem kawalan automatik dan pengumpulan data pada keadaan sistem dalam kombinasi dengan mikropemproses telah meningkatkan fungsinya dengan ketara, memberikan fleksibiliti yang lebih besar, mengurangkan kos dan saiz, meningkatkan kebolehpercayaan, ketahanan terhadap keadaan persekitaran yang buruk dan operasi lain. ciri-ciri.

Mikropemproses dan mikropengawal berdasarkannya digunakan secara meluas dalam instrumen dan sistem pengukur digital, yang memudahkan input dan output data, isyarat amaran atau arahan kepada paparan, serta penskalaan automatik parameter ini. Mikropemproses boleh menyediakan ujian kendiri dan penentukuran kendiri, semakan ketekalan data, komunikasi dengan mikrokomputer atau instrumen dikawal komputer, dan purata bacaan automatik. Walau bagaimanapun, mikropemproses dan mikropengawal berdasarkannya mempunyai volum perisian standard yang lebih kecil, rangkaian peranti persisian dan keupayaan antara muka berbanding mikrokomputer.

Mikropemproses juga telah menemui aplikasi dalam terminal, rangkaian mikrokomputer, modul penukaran mesej, pengulang, sistem storan penghantaran data, peranti pengekodan dan penyahkodan, sistem komunikasi mudah alih, sistem keselamatan dan modem.

Mikropemproses digunakan dalam unit sistem komputer mikro, pengawal input/output dan peranti persisian lain. Pengawal mikro dalam peranti persisian membenarkan banyak tugasan dilakukan pada persisian, membebaskan CPU untuk melaksanakan tugas lain.

Mikropemproses, mikropengawal dan mikrokomputer digunakan dalam peralatan tekstil: dalam sistem kawalan data, pemasangan kawalan kualiti, sistem penimbangan dan dos automatik, kawalan unit/mesin, penentuan tahap keriting, pengawal yang mengawal operasi individu, contohnya, ketegangan benang, pita, fabrik, dsb., menyusun peranti, memuatkan dan memunggah peranti, terminal dan peranti diagnostik automatik.

Perlu diingatkan bahawa apabila mengawal pemproses teknologi dalam industri tekstil, sejumlah besar parameter boleh laras dan kerumitan algoritma kawalan memerlukan penggunaan mikrokomputer yang berkuasa. Mikropemproses digunakan dalam sistem teragih di mana algoritma untuk mengurus objek di tapak dilaksanakan dan data disediakan untuk mikrokomputer, yang meningkatkan kebolehpercayaan sistem dalam keadaan gangguan industri.

Dalam model mikropemproses terkini, sistem pengendalian sepenuhnya atau sebahagiannya dilaksanakan dalam perkakasan berdasarkan memori kilat, yang mengoptimumkan proses mengurus kemudahan industri.

Permohonan

DAC digunakan apabila perlu untuk menukar isyarat daripada perwakilan digital kepada analog, contohnya, dalam pemain CD (CD Audio).

Jenis DAC

Jenis DAC elektronik yang paling biasa ialah:

- Modulator lebar nadi- jenis DAC yang paling mudah. Sumber arus atau voltan yang stabil dihidupkan secara berkala untuk masa yang berkadar dengan kod digital yang ditukar, kemudian jujukan nadi yang terhasil ditapis oleh penapis laluan rendah analog. Kaedah ini sering digunakan untuk mengawal kelajuan motor elektrik, dan juga menjadi popular dalam peralatan audio Hi-Fi;

- DAC berlebihan, seperti DAC delta-sigma, adalah berdasarkan kepadatan nadi berubah-ubah. Persampelan berlebihan membolehkan anda menggunakan DAC dengan kedalaman bit yang lebih rendah untuk mencapai kedalaman bit yang lebih tinggi bagi penukaran akhir; Selalunya DAC delta-sigma dibina berdasarkan DAC satu bit yang mudah, yang boleh dikatakan linear. DAC bit rendah menerima isyarat nadi dengan ketumpatan nadi dimodulasi(dengan tempoh nadi tetap, tetapi dengan kitaran tugas berubah-ubah), dicipta menggunakan maklum balas negatif. Maklum balas negatif bertindak sebagai penapis laluan tinggi untuk hingar kuantisasi.

- DAC jenis penimbang, di mana setiap bit kod binari yang ditukar sepadan dengan perintang atau sumber semasa yang disambungkan ke titik penjumlahan biasa. Arus sumber (konduksi perintang) adalah berkadar dengan berat bit yang sepadan dengannya. Oleh itu, semua bit bukan sifar kod ditambah pada berat. Kaedah penimbangan adalah salah satu yang terpantas, tetapi ia dicirikan oleh ketepatan yang rendah kerana keperluan untuk satu set banyak sumber ketepatan yang berbeza atau perintang dan impedans berubah-ubah. Atas sebab ini, DAC penimbang mempunyai lebar maksimum lapan bit;

- Tangga DAC(litar R-2R rantai). Dalam R-2R-DAC, nilai dicipta dalam litar khas yang terdiri daripada perintang dengan rintangan R Dan 2R, dipanggil matriks impedans malar, yang mempunyai dua jenis kemasukan: matriks arus terus dan matriks voltan songsang. Penggunaan perintang yang sama boleh meningkatkan ketepatan dengan ketara berbanding DAC penimbang konvensional, kerana ia agak mudah untuk menghasilkan satu set elemen ketepatan dengan parameter yang sama. DAC jenis R-2R membolehkan anda menolak had kedalaman bit. Dengan pemangkasan laser perintang pada satu substrat, ketepatan 20-22 bit dicapai. Kebanyakan masa penukaran dibelanjakan dalam penguat operasi, jadi ia mestilah secepat mungkin. Kelajuan DAC ialah beberapa mikrosaat atau kurang (iaitu nanosaat);

Ciri-ciri

DAC terletak pada permulaan laluan analog mana-mana sistem, jadi parameter DAC sebahagian besarnya menentukan parameter keseluruhan sistem secara keseluruhan. Berikut adalah ciri yang paling penting bagi DAC.

- Kadar pensampelan maksimum- kekerapan maksimum di mana DAC boleh beroperasi, menghasilkan hasil yang betul pada output. Menurut teorem Nyquist-Shannon (juga dikenali sebagai teorem Kotelnikov), untuk menghasilkan semula isyarat analog dengan betul daripada bentuk digital, kekerapan pensampelan mestilah tidak kurang daripada dua kali frekuensi maksimum dalam spektrum isyarat. Sebagai contoh, untuk menghasilkan semula keseluruhan julat frekuensi audio boleh didengar manusia, yang spektrumnya memanjang sehingga 20 kHz, isyarat audio perlu diambil sampel pada frekuensi sekurang-kurangnya 40 kHz. Piawaian CD Audio menetapkan kadar pensampelan audio kepada 44.1 kHz; Untuk menghasilkan semula isyarat ini, anda memerlukan DAC yang mampu beroperasi pada frekuensi ini. Kad bunyi komputer murah mempunyai kadar pensampelan 48 kHz. Isyarat yang disampel pada frekuensi lain disampel semula kepada 48 kHz, yang sebahagiannya merendahkan kualiti isyarat.

- Monoton- keupayaan DAC untuk meningkatkan isyarat keluaran analog apabila kod input meningkat.

- THD+N(total herotan harmonik + hingar) - ukuran herotan dan hingar yang dimasukkan ke dalam isyarat oleh DAC. Dinyatakan sebagai peratusan kuasa harmonik dan bunyi dalam isyarat keluaran. Parameter penting untuk aplikasi DAC isyarat kecil.

- Julat dinamik- nisbah isyarat terbesar dan terkecil yang DAC boleh menghasilkan semula, dinyatakan dalam desibel. Parameter ini berkaitan dengan kedalaman bit dan ambang hingar.

- Ciri-ciri statik:

- DNL (ketaklinearan pembezaan) - mencirikan berapa banyak kenaikan isyarat analog yang diperoleh dengan meningkatkan kod sebanyak 1 bit paling ketara (LSB) berbeza daripada nilai yang betul;

- INL (tak linear integral) - mencirikan berapa banyak ciri pemindahan DAC berbeza daripada yang ideal. Ciri yang ideal adalah linear; INL menunjukkan sejauh mana voltan pada output DAC untuk kod yang diberikan adalah daripada ciri linear; dinyatakan dalam gaji minimum;

- keuntungan;

- berat sebelah.

- Ciri-ciri kekerapan:

- SNDR (nisbah isyarat kepada hingar + herotan) - mencirikan dalam desibel nisbah kuasa isyarat keluaran kepada jumlah kuasa hingar dan herotan harmonik;

- HDi (pekali harmonik ke-i) - mencirikan nisbah harmonik ke-i kepada harmonik asas;

- THD (faktor herotan harmonik) ialah nisbah jumlah kuasa semua harmonik (kecuali yang pertama) kepada kuasa harmonik pertama.

lihat juga

kesusasteraan

- Jean M. Rabai, Anantha Chandrakasan, Borivozh Nikolic. Litar bersepadu digital. Metodologi Reka Bentuk = Litar Bersepadu Digital. - ed ke-2. - M.: Williams, 2007. - 912 p. - ISBN 0-13-090996-3

- Mingliang Liu. Menyahmistifikasi Litar Kapasitor Bersuis. ISBN 0-75-067907-7.

- Phillip E. Allen, Douglas R. Holberg. Reka Bentuk Litar Analog CMOS. ISBN 0-19-511644-5.

Pautan

- Penukar digital-ke-analog (DAC), teori dan prinsip operasi di laman web Pasaran Mikroelektronik

- Penukar digital-ke-analog untuk aplikasi pemprosesan isyarat digital

- Pengukuran INL/DNL untuk ADC Berkelajuan Tinggi menerangkan cara INL dan DNL dikira

- Alexey Stakhov. Komputer Fibonacci Bahagian 1, Bahagian 2, Bahagian 3 // PCweek.ru, 2002

- R-2R Ladder DAC dijelaskan mengandungi skema

| Pengawal mikro | |||||

|---|---|---|---|---|---|

| Seni bina |

| ||||

DAC– penukar digital-ke-analog – peranti yang direka untuk menukar isyarat diskret (digital) kepada isyarat berterusan (analog). Penukaran dijalankan mengikut perkadaran dengan kod binari isyarat.

Klasifikasi DAC

Mengikut jenis isyarat keluaran: dengan keluaran arus dan keluaran voltan;

Mengikut jenis antara muka digital: dengan input bersiri dan dengan input selari kod input;

Dengan bilangan DAC pada cip: saluran tunggal dan berbilang saluran;

Dengan laju: kelajuan sederhana dan kelajuan tinggi.

Parameter DAC asas:

1. N – kedalaman bit.

2. Arus keluaran maksimum.

4. Magnitud voltan rujukan.

5. Resolusi.

6. Kawal tahap voltan (TTL atau CMOS).

7. Ralat penukaran (output ralat offset sifar, ralat penukaran mutlak, bukan linear penukaran, bukan linear pembezaan). 8. Masa penukaran – selang masa dari saat kod dibentangkan (diserahkan) kepada saat isyarat output muncul.

9. Masa penetapan isyarat analog

Elemen utama DAC ialah:

Matriks rintangan (satu set pembahagi dengan TCR tertentu, dengan sisihan tertentu 2%, 5% atau kurang) boleh dibina ke dalam IC;

Suis (pada transistor bipolar atau MOS);

Sumber voltan rujukan.

Litar asas untuk membina DAC.

21. ADC. Peruntukan am. Kekerapan pensampelan. Klasifikasi ADC. Prinsip operasi ADC selari.

Mengikut kelajuan operasi, ADC dibahagikan kepada:

1. ADC penukaran selari (ADC selari) - ADC berkelajuan tinggi, mempunyai penggunaan perkakasan kompleks unit GHz.resolusi N = 8-12 bit, Fg = puluhan MHz

2. ADC penghampiran berturut-turut (pengiraan berturut-turut) sehingga 10 MHz. resolusi N = 10-16 bit, Fg = puluhan kHz

3. Mengintegrasikan ADC beratus-ratus Hz.peleraian N = 16-24 bit, Fg = puluhan

4. Sigma-delta ADC unit MHz.peleraian N = 16-24 bit, Fg = ratusan Hz

22. ADC pengiraan bersiri. Prinsip operasi.

23. ADC anggaran berturut-turut. Prinsip operasi.

Kod ini daripada output RPP disalurkan kepada DAC, yang menghasilkan voltan sepadan 3/4Uinmax, yang dibandingkan dengan Uin (pada CC) dan hasilnya ditulis pada bit yang sama dengan nadi jam keempat. Proses kemudian diteruskan sehingga semua digit telah dianalisis.

Kod ini daripada output RPP disalurkan kepada DAC, yang menghasilkan voltan sepadan 3/4Uinmax, yang dibandingkan dengan Uin (pada CC) dan hasilnya ditulis pada bit yang sama dengan nadi jam keempat. Proses kemudian diteruskan sehingga semua digit telah dianalisis.

Masa penukaran SAR ADC:

tpr = 2nTG, di mana TG ialah tempoh pengulangan nadi penjana; n – kapasiti bit ADC.

ADC sedemikian adalah lebih rendah dari segi kelajuan berbanding ADC jenis selari, tetapi ia lebih murah dan menggunakan kuasa yang lebih sedikit. Contoh: 1113PV1.

24. Prinsip operasi bagi ADC jenis penyepaduan.

Prinsip pengendalian ADC penyepaduan adalah berdasarkan dua prinsip asas:

1. Menukar voltan input kepada frekuensi atau tempoh nadi (masa)

Uin → f (VLF – penukar frekuensi voltan)

2. Tukar kekerapan atau tempoh (masa) kepada kod digital

f → N; T→N.

Ralat utama adalah disebabkan oleh VLF.

ADC jenis ini melakukan penukaran dalam dua peringkat.

Pada peringkat pertama, isyarat analog input disepadukan dan nilai bersepadu ini ditukar kepada urutan nadi. Kadar pengulangan denyutan dalam urutan ini atau tempohnya dimodulasi oleh nilai bersepadu isyarat input.

Pada peringkat kedua, urutan denyutan ini ditukar kepada kod digital - kekerapan atau tempoh nadinya diukur.

Penukar digital-ke-analog (DAC) ialah peranti untuk menukar kod digital kepada isyarat analog dalam magnitud yang berkadar dengan nilai kod.

DAC digunakan untuk menyambungkan sistem kawalan digital dengan peranti yang dikawal oleh tahap isyarat analog. Selain itu, DAC adalah bahagian penting dalam kebanyakan peranti analog-ke-digital dan struktur penukar.

DAC dicirikan oleh fungsi penukaran. Ia mengaitkan perubahan dalam kod digital dengan perubahan voltan atau arus. Fungsi penukaran DAC dinyatakan seperti berikut

U keluar- nilai voltan keluaran sepadan dengan kod digital Nin, dibekalkan kepada input DAC.

U maks- voltan keluaran maksimum sepadan dengan kod maksimum yang digunakan pada input N maks

Saiz K DAC, ditentukan oleh nisbah, dipanggil pekali penukaran digital-ke-analog. Walaupun sifat berperingkat bagi ciri yang dikaitkan dengan perubahan diskret dalam nilai input (kod digital), adalah dipercayai bahawa DAC adalah penukar linear.

Jika nilai Nin diwakili melalui nilai pemberat digitnya, fungsi transformasi boleh dinyatakan seperti berikut

, Di mana

, Di mana

i- nombor digit kod input Nin; A i- maksudnya i digit ke-1 (sifar atau satu); Ui – berat i-kategori ke-; n – bilangan bit kod input (bilangan bit DAC).

Berat bit ditentukan untuk kapasiti bit tertentu, dan dikira menggunakan formula berikut

U OP - voltan rujukan DAC

Prinsip operasi kebanyakan DAC ialah penjumlahan bahagian isyarat analog (berat nyahcas), bergantung pada kod input.

DAC boleh dilaksanakan menggunakan penjumlahan semasa, penjumlahan voltan, dan pembahagian voltan. Dalam kes pertama dan kedua, mengikut nilai bit kod input, isyarat penjana semasa dan sumber E.M.F. disimpulkan. Kaedah terakhir ialah pembahagi voltan terkawal kod. Dua kaedah terakhir tidak digunakan secara meluas kerana kesukaran praktikal pelaksanaannya.

Kaedah untuk melaksanakan DAC dengan penjumlahan wajaran arus

Mari kita pertimbangkan pembinaan DAC mudah dengan penjumlahan wajaran arus.

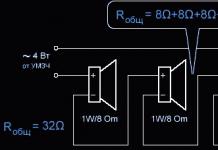

DAC ini terdiri daripada satu set perintang dan satu set suis. Bilangan kekunci dan bilangan perintang adalah sama dengan bilangan bit n kod input. Nilai perintang dipilih mengikut undang-undang binari. Jika R=3 Ohms, maka 2R=6 Ohms, 4R=12 Ohms, dan seterusnya, i.e. Setiap perintang berikutnya adalah 2 kali lebih besar daripada yang sebelumnya. Apabila sumber voltan disambungkan dan suis ditutup, arus akan mengalir melalui setiap perintang. Nilai semasa perintang, terima kasih kepada pilihan penilaian mereka yang sesuai, juga akan diedarkan mengikut undang-undang binari. Semasa menghantar kod kemasukan Nin Kekunci dihidupkan mengikut nilai bit yang sepadan bagi kod input. Kekunci ditutup jika bit yang sepadan adalah sama dengan satu. Dalam kes ini, arus disimpulkan dalam nod, berkadar dengan berat bit ini, dan magnitud arus yang mengalir dari nod secara keseluruhan akan berkadar dengan nilai kod input. Nin.

Rintangan perintang matriks dipilih agak besar (berpuluh-puluh kOhms). Oleh itu, untuk kebanyakan kes praktikal, DAC memainkan peranan sebagai sumber semasa untuk beban. Sekiranya perlu untuk mendapatkan voltan pada output penukar, maka penukar voltan arus dipasang pada output DAC sedemikian, sebagai contoh, pada penguat operasi

Walau bagaimanapun, apabila kod berubah pada input DAC, jumlah arus yang diambil daripada sumber voltan rujukan berubah. Ini adalah kelemahan utama kaedah membina DAC ini. . Kaedah pembinaan ini hanya boleh digunakan jika sumber voltan rujukan mempunyai rintangan dalaman yang rendah. Dalam kes lain, pada masa ini kod input diubah, arus yang diambil dari sumber berubah, yang membawa kepada perubahan penurunan voltan merentasi rintangan dalamannya dan, seterusnya, kepada perubahan tambahan dalam arus keluaran yang tidak berkaitan secara langsung kepada perubahan kod. Struktur DAC dengan suis pensuisan membolehkan kami menghapuskan kelemahan ini.

Dalam struktur sedemikian terdapat dua nod keluaran. Bergantung pada nilai bit kod input, kekunci yang sepadan disambungkan ke nod yang disambungkan ke output peranti, atau ke nod lain, yang paling kerap dibumikan. Dalam kes ini, arus sentiasa mengalir melalui setiap perintang matriks, tanpa mengira kedudukan suis, dan jumlah arus yang digunakan daripada sumber voltan rujukan adalah malar.

Kelemahan biasa kedua-dua struktur yang dipertimbangkan ialah nisbah besar antara nilai terkecil dan terbesar bagi perintang matriks. Pada masa yang sama, walaupun terdapat perbezaan besar dalam penarafan perintang, adalah perlu untuk memastikan ketepatan mutlak yang sama untuk kesesuaian untuk kedua-dua penarafan perintang terbesar dan terkecil. Dalam reka bentuk DAC bersepadu dengan lebih daripada 10 bit, ini agak sukar untuk dicapai.

Struktur berdasarkan bahan rintangan adalah bebas daripada semua kelemahan di atas. R-2R matriks

Dengan pembinaan matriks rintangan ini, arus dalam setiap cawangan selari berikutnya adalah dua kali kurang daripada yang sebelumnya. Kehadiran hanya dua nilai perintang dalam matriks menjadikannya agak mudah untuk menyesuaikan nilai mereka.

Arus keluaran untuk setiap struktur yang dibentangkan adalah berkadar serentak bukan sahaja dengan nilai kod input, tetapi juga dengan nilai voltan rujukan. Selalunya dikatakan bahawa ia adalah berkadar dengan hasil dua kuantiti ini. Oleh itu, DAC sedemikian dipanggil pengganda. Setiap orang akan mempunyai sifat-sifat ini DAC, di mana pembentukan nilai arus berwajaran yang sepadan dengan pemberat nyahcas dijalankan menggunakan matriks rintangan.

Di samping digunakan untuk tujuan yang dimaksudkan, pendaraban DAC digunakan sebagai pengganda analog-ke-digital, sebagai rintangan dan kekonduksian terkawal kod. Ia digunakan secara meluas sebagai komponen dalam pembinaan penguat kawalan kod (boleh melaras), penapis, sumber voltan rujukan, perapi isyarat, dsb.

Parameter asas dan ralat DAC

Parameter utama yang boleh dilihat dalam direktori:

1. Bilangan bit – bilangan bit kod input.

2. Pekali penukaran – nisbah kenaikan isyarat output kepada kenaikan isyarat input untuk fungsi penukaran linear.

3. Masa penetapan voltan atau arus keluaran - selang masa dari saat perubahan kod yang diberikan pada input DAC sehingga saat voltan keluaran atau arus akhirnya memasuki zon dengan lebar digit paling tidak ketara. ( MZR).

4. Kekerapan penukaran maksimum – kekerapan tertinggi perubahan kod di mana parameter yang ditentukan mematuhi piawaian yang ditetapkan.

Terdapat parameter lain yang mencirikan prestasi DAC dan ciri fungsinya. Ini termasuk: voltan input tahap rendah dan tinggi, penggunaan semasa, voltan keluaran atau julat arus.

Parameter yang paling penting untuk DAC adalah yang menentukan ciri ketepatannya.

Ciri-ciri ketepatan setiap DAC , Pertama sekali, mereka ditentukan oleh ralat yang dinormalkan dalam magnitud.

Ralat dibahagikan kepada dinamik dan statik. Ralat statik ialah ralat yang kekal selepas selesai semua proses sementara yang berkaitan dengan menukar kod input. Ralat dinamik ditentukan oleh proses sementara pada output DAC yang timbul akibat perubahan dalam kod input.

Jenis utama ralat DAC statik:

Ralat penukaran mutlak pada titik akhir skala ialah sisihan nilai voltan keluaran (semasa) daripada nilai nominal yang sepadan dengan titik akhir skala fungsi penukaran. Diukur dalam unit digit terkecil penukaran.

Voltan offset sifar keluaran – Voltan DC pada output DAC dengan kod input sepadan dengan nilai voltan keluaran sifar. Diukur dalam unit tertib rendah. Ralat pekali penukaran (skala) – dikaitkan dengan sisihan cerun fungsi penukaran daripada yang diperlukan.

Ketaklinearan DAC ialah sisihan fungsi penukaran sebenar daripada garis lurus yang ditentukan. Ia adalah kesilapan yang paling teruk yang sukar untuk dilawan.

Ralat tak linear biasanya dibahagikan kepada dua jenis - kamiran dan pembezaan.

Ralat tak linear kamiran ialah sisihan maksimum ciri sebenar daripada yang ideal. Malah, ini mengambil kira fungsi transformasi purata. Ralat ini ditentukan sebagai peratusan julat akhir nilai output.

Ketaklinearan pembezaan dikaitkan dengan ketidaktepatan menetapkan berat nyahcas, i.e. dengan ralat elemen pembahagi, taburan parameter baki elemen utama, penjana semasa, dsb.

Kaedah untuk mengenal pasti dan membetulkan ralat DAC

Adalah wajar pembetulan ralat dijalankan semasa pembuatan penukar (pelarasan teknologi). Walau bagaimanapun, ia sering diingini apabila menggunakan sampel tertentu BIS dalam satu peranti atau yang lain. Dalam kes ini, pembetulan dijalankan dengan memasukkan ke dalam struktur peranti, kecuali LSI DAC elemen tambahan. Kaedah sedemikian dipanggil struktur.

Proses yang paling sukar adalah untuk memastikan kelinearan, kerana ia ditentukan oleh parameter berkaitan banyak elemen dan nod. Selalunya, hanya offset sifar dan pekali dilaraskan

Parameter ketepatan yang disediakan oleh kaedah teknologi merosot apabila penukar terdedah kepada pelbagai faktor ketidakstabilan, terutamanya suhu. Ia juga perlu diingat tentang faktor penuaan unsur.

Ralat offset sifar dan ralat skala mudah diperbetulkan pada output DAC. Untuk melakukan ini, offset malar dimasukkan ke dalam isyarat output, mengimbangi offset ciri penukar. Skala penukaran yang diperlukan diwujudkan sama ada dengan melaraskan set keuntungan pada output penukar penguat, atau dengan melaraskan nilai voltan rujukan jika DAC ialah satu darab.

Kaedah pembetulan dengan kawalan ujian terdiri daripada mengenal pasti ralat DAC merentas keseluruhan set pengaruh input yang dibenarkan dan menambah pembetulan yang dikira berdasarkan ini kepada nilai input atau output untuk mengimbangi ralat ini.

Untuk sebarang kaedah pembetulan dengan kawalan menggunakan isyarat ujian, tindakan berikut disediakan:

1. Mengukur ciri-ciri DAC pada set pengaruh ujian yang mencukupi untuk mengenal pasti ralat.

2. Mengenalpasti ralat dengan mengira sisihan mereka daripada hasil pengukuran.

3. Pengiraan pindaan pembetulan untuk nilai yang ditukar atau kesan pembetulan yang diperlukan pada blok yang diperbetulkan.

4. Menjalankan pembetulan.

Kawalan boleh dijalankan sekali sebelum memasang penukar ke dalam peranti menggunakan peralatan pengukur makmal khas. Ia juga boleh dijalankan menggunakan peralatan khusus yang dibina ke dalam peranti. Dalam kes ini, pemantauan, sebagai peraturan, dijalankan secara berkala, sepanjang masa sementara penukar tidak terlibat secara langsung dalam pengendalian peranti. Organisasi kawalan dan pembetulan penukar sedemikian boleh dijalankan apabila ia beroperasi sebagai sebahagian daripada sistem pengukur mikropemproses.

Kelemahan utama mana-mana kaedah ujian hujung ke hujung adalah masa ujian yang panjang bersama-sama dengan kepelbagaian dan jumlah besar peralatan yang digunakan.

Nilai pembetulan yang ditentukan dalam satu cara atau yang lain disimpan, sebagai peraturan, dalam bentuk digital. Pembetulan ralat, dengan mengambil kira pembetulan ini, boleh dilakukan dalam bentuk analog dan digital.

Dengan pembetulan digital, pembetulan ditambah dengan mengambil kira tandanya pada kod input DAC. Akibatnya, kod diterima pada input DAC, yang menjana voltan atau nilai arus yang diperlukan pada outputnya. Pelaksanaan paling mudah kaedah pembetulan ini terdiri daripada laras DAC, pada input yang mana peranti storan digital dipasang ( ingatan). Kod input memainkan peranan kod alamat. DALAM ingatan Alamat yang sepadan mengandungi pra-kiraan, dengan mengambil kira pembetulan, nilai kod yang dibekalkan kepada DAC yang diperbetulkan.

Untuk pembetulan analog, sebagai tambahan kepada DAC utama, DAC tambahan lain digunakan. Julat isyarat keluarannya sepadan dengan nilai ralat maksimum DAC yang diperbetulkan. Kod input dibekalkan serentak kepada input DAC yang diperbetulkan dan kepada input alamat ingatan pindaan daripada ingatan pembetulan, pembetulan yang sepadan dengan nilai yang diberikan bagi kod input dipilih. Kod pembetulan ditukar kepada isyarat yang berkadar dengannya, yang dijumlahkan dengan isyarat keluaran DAC yang diperbetulkan. Oleh kerana kecilnya julat isyarat keluaran DAC tambahan yang diperlukan berbanding julat isyarat keluaran DAC yang diperbetulkan, ralat pertama sendiri diabaikan.

Dalam sesetengah kes, ia menjadi perlu untuk membetulkan dinamik DAC.

Tindak balas sementara DAC akan berbeza apabila menukar kombinasi kod yang berbeza, dengan kata lain, masa penyelesaian isyarat keluaran akan berbeza. Oleh itu, masa penyelesaian maksimum mesti diambil kira apabila menggunakan DAC. Walau bagaimanapun, dalam beberapa kes adalah mungkin untuk membetulkan tingkah laku ciri pemindahan.

Ciri-ciri menggunakan LSI DAC

Untuk kejayaan penggunaan moden BIS Ia tidak mencukupi untuk DAC mengetahui senarai ciri utamanya dan litar asas untuk kemasukannya.

Kesan yang ketara terhadap keputusan permohonan BIS DAC memenuhi keperluan operasi yang ditentukan oleh ciri-ciri cip tertentu. Keperluan sedemikian termasuk bukan sahaja penggunaan isyarat input yang dibenarkan, voltan bekalan kuasa, kapasiti dan rintangan beban, tetapi juga susunan menghidupkan sumber kuasa yang berbeza, pemisahan litar yang menyambungkan sumber kuasa yang berbeza dan bas biasa, penggunaan penapis, dan lain-lain.

Untuk DAC ketepatan, voltan keluaran hingar adalah amat penting. Satu ciri masalah hingar dalam DAC ialah kehadiran lonjakan voltan pada outputnya yang disebabkan oleh menukar suis di dalam penukar. Amplitud letusan ini boleh mencapai beberapa puluh berat MZR dan mewujudkan kesukaran dalam pengendalian peranti pemprosesan isyarat analog berikutan DAC. Penyelesaian kepada masalah menyekat letupan tersebut adalah dengan menggunakan peranti sampel dan tahan pada output DAC ( UVH). UVH dikawal daripada bahagian digital sistem, yang menjana kombinasi kod baharu pada input DAC. Sebelum menyerahkan gabungan kod baharu UVH beralih ke mod storan, membuka litar penghantaran isyarat analog kepada output. Terima kasih kepada ini, lonjakan voltan keluaran DAC tidak mencapai output UVH, yang kemudiannya dimasukkan ke dalam mod penjejakan, mengulangi output DAC.

Perhatian khusus apabila membina DAC berdasarkan BIS Adalah perlu untuk memberi perhatian kepada pilihan penguat operasi yang berfungsi untuk menukar arus keluaran DAC kepada voltan. Apabila menggunakan kod input DAC pada output OU akan berlaku kesilapan DU, disebabkan oleh voltan pincangnya dan sama dengan

![]() ,

,

di mana U cm– voltan pincang OU; R os– nilai rintangan dalam litar suap balik OU; R m– rintangan matriks perintang DAC (rintangan keluaran DAC), bergantung pada nilai kod yang digunakan pada inputnya.

Oleh kerana nisbah berbeza dari 1 hingga 0, ralat disebabkan oleh U cm, perubahan di lorong (1...2)U cm. Pengaruh U cm diabaikan semasa menggunakan OU, yang mana satu .

Oleh kerana kawasan suis transistor yang besar CMOS BIS kapasiti keluaran yang ketara bagi LSI DAC (40...120 pF bergantung kepada nilai kod input). Kapasiti ini mempunyai kesan yang ketara ke atas masa penyelesaian voltan keluaran. OU kepada ketepatan yang diperlukan. Untuk mengurangkan pengaruh ini R os dipintas dengan kapasitor Dengan OS.

Dalam sesetengah kes, adalah perlu untuk mendapatkan voltan keluaran bipolar pada keluaran DAC. Ini boleh dicapai dengan memperkenalkan pincang julat voltan keluaran pada output, dan untuk mendarab DAC dengan menukar kekutuban sumber voltan rujukan.

Sila ambil perhatian bahawa jika anda menggunakan DAC bersepadu , mempunyai bilangan bit yang lebih besar daripada yang anda perlukan, maka input bit yang tidak digunakan disambungkan ke bas tanah, dengan jelas menentukan tahap sifar logik padanya. Lebih-lebih lagi, untuk bekerja dengan julat seluas mungkin bagi isyarat keluaran LSI DAC, digit diambil sebagai digit sedemikian, bermula dengan angka yang paling tidak signifikan.

Salah satu contoh praktikal menggunakan DAC ialah pembentuk isyarat pelbagai bentuk. Saya membuat model kecil di Proteus. Menggunakan DAC yang dikawal oleh MK (Atmega8, walaupun ia juga boleh dilakukan pada Tiny), isyarat pelbagai bentuk dijana. Program ini ditulis dalam C dalam CVAVR. Dengan menekan butang, isyarat yang dihasilkan berubah.

LSI DAC DAC0808 Semikonduktor Kebangsaan, 8-bit, berkelajuan tinggi, disertakan mengikut litar standard. Oleh kerana outputnya adalah semasa, ia ditukar kepada voltan menggunakan penguat penyongsangan menggunakan op-amp.

Pada dasarnya, anda juga boleh mempunyai angka yang menarik, ia mengingatkan saya kepada sesuatu, bukan? Jika anda memilih kedalaman bit yang lebih tinggi, anda akan menjadi lebih lancar

Bibliografi:

1. Bakhtiyarov G.D., Malinin V.V., Shkolin V.P. Penukar analog-ke-digital/Ed. G.D. Bakhtiyarov - M.: Sov. radio. – 1980. – 278 hlm.: sakit.

2. Reka bentuk sistem mikropemproses kawalan analog-digital.

3. O.V. Shishov. - Saransk: Rumah Penerbitan Mordov. Universiti 1995. - hlm.

Di bawah anda boleh memuat turun projek di