Maklumat am

Fakta bahawa Intel berhasrat untuk memindahkan fungsi secara sistematik yang sebelum ini dilaksanakan dalam set logik kepada pemproses menjadi jelas lebih daripada dua tahun lalu. Pemproses pertama dengan microarchitecture Nehalem - Bloomfield - memperoleh pengawal memori terbina dalam. Dalam generasi seterusnya, Lynnfield, pengawal bas telah ditambahkan pada pengawal memori PCI Express. Kemudian, di Clarkdale, teras grafik terbina dalam muncul dalam pemproses, walaupun dilaksanakan oleh kristal semikonduktor yang berasingan. Sandy Bridge meletakkan sentuhan akhir pada penyepaduan yang konsisten ini - pemproses dengan seni bina mikro baharu akan mengandungi semuanya sekali gus dalam satu cip: teras pemproses, teras grafik, pengawal memori dan pengawal bas PCI Express.

Keluasan kristal semikonduktor Sandy Bridge akan menjadi kira-kira 225 meter persegi. mm, iaitu, terima kasih kepada 32 nm moden proses teknologi kristal ini akan menjadi lebih kecil daripada kristal pemproses Bloomfield dan Lynnfield empat teras atau Gulftown enam teras.

Tiada kompromi dari segi prestasi di Sandy Bridge. Struktur umum pemproses mengandaikan kehadiran dua atau empat teras pemproses dengan sokongan untuk teknologi Hyper-Threading, cache peringkat ketiga sehingga 8 MB, pengawal memori DDR3 dwi-saluran, sokongan untuk 16 lorong PCI Express 2.0 dan kehadiran teras grafik DirectX 10.1 moden. Iaitu, pemproses generasi baharu mempunyai semua yang mereka perlukan untuk melaksanakan dalam segmen pasaran yang berbeza, termasuk yang teratas.

Berlatarbelakangkan penyepaduan ke Sandy Bridge, penambahbaikan ketara telah dibuat pada tahap yang lebih rendah. Seni bina mikro teras pengkomputeran telah mengalami reka bentuk semula yang ketara; mereka telah menerima beberapa penambahbaikan, yang mana pemproses baharu akan menjadi lebih pantas daripada pendahulunya, walaupun ketika beroperasi pada kelajuan jam yang sama. Pada masa yang sama, penambahbaikan telah dibuat untuk mengurangkan penjanaan haba, supaya Sandy Bridge hanya boleh beroperasi pada frekuensi yang lebih tinggi. Di samping itu, pada peringkat seni bina mikro, pemproses telah menambah sokongan untuk set arahan vektor baharu AVX (Advanced Vector Extensions), yang akan berguna untuk melaksanakan beberapa algoritma multimedia, kewangan atau saintifik. Perbezaan asas antara AVX dan set arahan vektor sebelumnya dalam keluarga SSE ialah peningkatan dalam lebar operan daripada 128 kepada 256 bit, supaya untuk banyak tugasan, ia akan memungkinkan untuk memproses sejumlah besar data pada kos yang lebih rendah. Oleh itu, Sandy Bridge boleh dicirikan sebagai satu langkah ke hadapan yang ketara dalam beberapa arah sekaligus, yang memberikan alasan untuk kenyataan yang paling menyanjung tentang produk yang menjanjikan ini.

Dengan melancarkan Sandy Bridge awal tahun depan, Intel menjangkakan untuk cepat menakluki majoriti segmen harga. Oleh itu, pada awal tahun ini, pelbagai jenis Core i3, Core i5 dan Core i7 dengan seni bina mikro baharu, kos pelbagai pilihan yang akan berkisar antara $100 hingga $300. Dan kemudian pada tahun 2011, pengubahsuaian yang lebih murah akan dibentangkan.

Menurut data yang ada, pengumuman kumpulan pertama wakil keluarga Sandy Bridge dijadualkan pada 5 Januari, dan permulaan jualan mereka adalah pada 9 Januari. Pada hari ini, senarai harga syarikat akan diisi semula dengan model empat teras berikut yang direka untuk desktop:

Perlu diingatkan bahawa sebagai tambahan kepada perkara di atas model Intel juga akan menawarkan seluruh kelas pemproses Sandy Bridge yang cekap tenaga mudah alih dan desktop. Dengan memfokuskan pada versi tertumpu pada desktop, kami juga boleh melaporkan beberapa Sandy Bridges yang dilancarkan pada 5 Januari dengan TDP biasa sebanyak 65, 45 dan 35 W.

Oleh itu, satu-satunya kategori harga yang akan kekal dikuasai oleh pemproses Nehalem untuk masa yang lama ialah CPU mahal, di mana pemproses LGA1366 Bloomfiled dan Gulftown akan terus disebut harga sepanjang tahun hadapan. Penggantian mereka mungkin berlaku tidak lebih awal daripada penghujung tahun 2011, apabila Intel menyediakan dan menyesuaikan platform pelayan LGA2011 yang menjanjikan untuk desktop. Variasi pemproses "dicas" khas Jambatan Sandy-E, yang akan ditawarkan sebagai sebahagian daripada platform ini, akan dapat menawarkan peminat sehingga 8 teras pengkomputeran, cache L3 16-MB, pengawal memori empat saluran, 32 lorong PCI Express 2.0 dan "barangan" lain yang seseorang boleh hanya impian hari ini. Walau bagaimanapun, ini adalah prospek yang jauh; versi pertama Sandy Bridge akan menjadi asas kepada platform yang lebih biasa, tetapi masih baharu.

Walaupun Sandy Bridge tidak memperkenalkan sebarang nod asas baru berbanding Clarkdale, pemproses generasi baharu akan datang ke pasaran bersama-sama dengan platform LGA1155. Malangnya, ia tidak serasi dengan LGA1156, bermakna pemproses baharu akan memerlukan penggunaan papan induk khas dengan soket pemproses khas.

Bersama-sama dengan Sandy Bridge, sekeluarga set cip segar juga akan mula digunakan, tulang belakangnya ialah set cip Intel P67 yang biasa digunakan dan set cip sistem dengan sokongan untuk grafik Intel H67. Sama seperti chipset untuk pemproses LGA1156, P67 dan H67 sangat mudah: selepas memindahkan fungsi jambatan utara ke pemproses, ia terdiri daripada satu cip - jambatan selatan dengan set ciri yang agak tipikal. Selain keserasian Sandy Bridge ciri utama Produk baharu ini akan menyokong dua port SATA dengan lebar jalur 6 Gbit/s.

Malangnya, tiada sokongan USB3 dalam set cip baharu, tetapi tanpa ragu-ragu, sebahagian besar papan induk LGA1155 akan mempunyai port yang sepadan dilaksanakan melalui pengawal tambahan. Perkara yang sama berlaku untuk bas PCI - ketiadaan pengawal standard yang sepadan sebagai sebahagian daripada set logik sistem baharu tidak bermakna sama sekali tradisional Penyambung PCI akan hilang pada motherboard.

Walaupun hakikatnya masih ada masa lagi sebelum pengumuman pemproses sebenar dengan seni bina mikro Sandy Bridge dan platform LGA1155, maklumat yang ada membolehkan kami membuat ramalan yang sangat spesifik tentang prestasi sistem masa hadapan. Oleh itu, apabila membandingkan pemproses Sandy Bridge dan Lynnfield, yang mempunyai bilangan teras yang sama dan beroperasi pada kelajuan jam yang sama, mikroarchitecture baharu memberikan prestasi sebenar 5-10% lebih tinggi.

Prestasi mengikut inpai.com.cn. Berbanding

pemproses empat teras pada 3.4 GHz

Pada masa yang sama, penggunaan kuasa pemproses Sandy Bridge adalah lebih kurang 20% lebih rendah, iaitu, dari segi prestasi per watt, CPU baharu telah melangkah jauh ke hadapan. Dan, dengan cara ini, jika kita mengambil kira bahawa frekuensi jam model Sandy Bridge melebihi frekuensi pemproses Lynnfield yang setara sebanyak kira-kira 10%, maka secara amnya kita boleh mengatakan bahawa keseluruhan platform LGA1155 akan lebih pantas daripada platform LGA1156 sebelumnya dengan sekurang-kurangnya 25%. Nombor ini boleh digunakan sebagai garis panduan untuk penilaian cetek nilai praktikal seni bina mikro baharu, jika anda menutup mata anda kepada peningkatan yang lebih mendalam seperti teras grafik yang dipertingkatkan dan sokongan untuk set arahan AES-NI dan AVX baharu.

Asal-usul Prestasi Tinggi

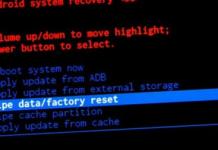

Banyak perubahan seni bina mikro melalui mana jurutera Intel Ia adalah mungkin untuk mencapai peningkatan dalam prestasi pemproses sambil mengurangkan penggunaan kuasa dan pelesapan haba mereka, yang, paling tidak, tidak dijangka. Hakikatnya ialah Sandy Bridge bukan sekadar pembangunan evolusi Nehalem yang lebih lanjut - ia menggunakan beberapa idea yang dipinjam daripada projek Pentium 4 yang kelihatan gagal. Ya, ya, walaupun mikroarkitektur NetBurst telah lama ditolak oleh Intel kerana sifatnya yang tidak ekonomik, beberapa elemen berfungsi Pemproses Pentium 4 kini boleh didapati dalam Core i3, Core i5 dan Core i7 yang akan datang. Dan amat ironis bahawa peminjaman Sandy Bridge daripada mikroarchitecture berusia sedekad bukan sahaja untuk meningkatkan prestasi, tetapi juga untuk mengurangkan pelesapan haba.Perubahan ketara dalam seni bina mikro Sandy Bridge bermula pada peringkat awal saluran paip - pada peringkat penyahkodan arahan x86 ke dalam operasi mikro pemproses yang lebih mudah. Unit penyahkodan aliran arahan input itu sendiri kekal sama seperti di Nehalem - ia menyediakan pemprosesan sehingga 4 arahan setiap kitaran jam dan menyokong teknologi Micro-Fusion dan Macro-Fusion, yang menjadikan aliran arahan output lebih seragam dari segi kerumitan pelaksanaannya. Walau bagaimanapun, dalam microarchitecture baharu, arahan yang dinyahkodkan ke dalam microinstructions pemproses tidak hanya dialihkan ke peringkat pemprosesan seterusnya, ia juga dicache. Dalam erti kata lain, sebagai tambahan kepada cache arahan peringkat pertama 32 KB yang biasa, yang merupakan atribut hampir mana-mana pemproses x86, Sandy Bridge telah menambah satu lagi cache "peringkat sifar" tambahan - cache hasil penyahkodan. Cache ini adalah rujukan pertama kepada microarchitecture NetBurst, kerana dari sudut pandangan prinsip umum operasi, ia adalah analog langsung dari Execution Trace Cache yang sentiasa diingati.

Cache hasil penyahkodan mempunyai volum kira-kira 6 KB dan boleh menampung sehingga satu setengah ribu arahan mikro, yang menjadikannya bantuan penting untuk penyahkod. Hakikatnya ialah sekarang, jika penyahkod mengesan arahan yang telah diterjemahkan semula sebelum ini dalam aliran arahan input dalam cache, ia segera menggantikannya dengan arahan mikro dalaman tanpa penyahkodan baharu. Kehadiran cache hasil penyahkodan membolehkan anda meringankan beban pada penyahkod dengan ketara, yang merupakan bahagian pemproses yang agak intensif tenaga. Menurut Intel, cache tambahan ini berguna kira-kira 80% daripada masa, yang memadamkan sebarang syak wasangka tentang ketidakberkesanannya. Di samping itu, semasa momen terbiar, penyahkod di Sandy Bridge dimatikan, yang memberikan sumbangan besar untuk mengurangkan penggunaan kuasa pemproses ini.

Penambahbaikan penting kedua kepada peringkat awal saluran paip adalah untuk menambah baik unit ramalan cawangan. Kepentingan operasi yang betul bagi nod ini sukar untuk dinilai terlalu tinggi, kerana setiap ramalan cawangan yang salah membawa kepada keperluan untuk menghentikan dan menetapkan semula saluran paip sepenuhnya. Akibatnya, ralat peramal memerlukan bukan sahaja penurunan prestasi, tetapi juga keperluan tenaga tambahan untuk mengisi semula penghantar. Ia mesti dikatakan bahawa dalam pemproses terkini Intel berjaya mencapai kecekapan yang sangat tinggi bagi unit ini. Walau bagaimanapun, dalam Sandy Bridge, semua penimbal yang menyimpan alamat peralihan dan sejarahnya telah direka bentuk semula untuk memampatkan maklumat yang terkandung di dalamnya. Akibatnya, tanpa meningkatkan saiz struktur data yang unit ramalan cawangan beroperasi, Intel dapat mencapai pemeliharaan sejarah cawangan yang lebih mendalam. Dan ini memberi kesan positif pada prestasi peramal, yang prestasinya berkaitan secara langsung dengan jumlah maklumat statistik yang digunakannya tentang peralihan bersyarat yang dilakukan. Dianggarkan bilangan cawangan yang diramalkan dengan betul telah meningkat di Sandy Bridge berbanding pendahulunya sebanyak lebih daripada 5%.

Tetapi perubahan yang paling menarik mempengaruhi unit penyusunan semula arahan, yang merupakan nod utama semua pemproses Luar Pesanan. Di sinilah hubungan kekerabatan mikroarchitecture Sandy Bridge dengan NetBurst dapat dilihat dengan jelas - jurutera Intel mengembalikan fail daftar fizikal kepada pemproses baharu mereka, yang telah dimansuhkan dalam Core dan Nehalem yang memihak kepada fail daftar terpusat yang berasingan. Intipati perubahan ialah jika sebelum ini, semasa menyusun semula arahan mikro, salinan lengkap daftar yang mereka gunakan untuk setiap arahan yang diproses disimpan dalam penimbal, kini hanya rujukan untuk mendaftar nilai yang disimpan dalam fail daftar fizikal digunakan. Pendekatan ini bukan sahaja menghapuskan pemindahan data yang tidak perlu, tetapi juga menghapuskan pelbagai duplikasi kandungan daftar, yang menjimatkan ruang dalam fail daftar.

Akibatnya, unit pelaksanaan perintah yang tidak mengikut pesanan bagi pemproses Sandy Bridge boleh menyimpan sehingga 168 arahan mikro "dalam pandangan", manakala dalam pemproses Nehalem hanya 128 arahan mikro diletakkan dalam penimbal susunan semula. Di samping itu, beberapa penjimatan tenaga dicapai. Walau bagaimanapun, menggantikan nilai daftar dengan rujukan kepada nilai ini juga mempunyai sisi negatif - saluran paip pelaksanaan memperoleh peringkat tambahan yang diperlukan untuk penunjuk dereferencing.

Tetapi dalam kes Sandy Bridge, pada umumnya, pemaju tidak mempunyai pilihan lain. Pemproses ini memperkenalkan arahan AVX baharu yang beroperasi pada daftar 256-bit, pemindahan berbilang yang nilainya akan mewujudkan overhed yang serius. Dan jurutera mengambil perhatian khusus untuk memastikan arahan baharu dilaksanakan dalam seni bina mikro Sandy Bridge pada kelajuan yang baik. Prestasi tinggi apabila bekerja dengan mereka adalah kunci kepada penerimaan mereka oleh pembangun perisian, kerana hanya dalam kes ini mereka benar-benar boleh meningkatkan tahap selari dan daya pemprosesan dalam pengiraan vektor.

Arahan AVX itu sendiri adalah pembangunan lanjut SSE, mengembangkan kapasiti bit operasi SIMD vektor biasa kepada operan 256-bit. selain itu, set baru membenarkan operasi dijalankan dalam bentuk yang tidak merosakkan, iaitu, tanpa kehilangan data asal dalam daftar. Terima kasih kepada sifat-sifat ini, set arahan AVX, bersama-sama dengan penambahbaikan mikroarkitektur, juga boleh dianggap sebagai inovasi yang bertujuan untuk meningkatkan prestasi dan menjimatkan tenaga, kerana pelaksanaannya akan memudahkan banyak algoritma dan melaksanakan lebih banyak kerja menggunakan bilangan yang lebih kecil arahan Arahan AVX sangat sesuai untuk aplikasi multimedia, saintifik dan kewangan intensif titik terapung.

Untuk melaksanakan arahan 256-bit dengan cekap, penggerak pemproses telah direka semula khas. Intipati perubahan adalah bahawa untuk bekerja dengan data 256-bit, penggerak 128-bit digabungkan secara berpasangan. Dan memandangkan setiap satu daripada tiga port pelaksanaan Sandy Bridge (seperti Nehalem) mempunyai peranti untuk berfungsi serentak dengan tiga jenis data - integer 64-bit, 128-bit atau 128-bit nyata - gabungan berpasangan peranti SIMD dalam satu port kelihatan seperti penyelesaian yang semula jadi dan munasabah. Dan, yang penting, pengagihan semula sumber sedemikian tidak membahayakan daya pemprosesan keseluruhan unit pelaksanaan pemproses.

Fokus Sandy Bridge untuk bekerja dengan arahan vektor 256-bit memaksa pembangun pemproses untuk memikirkan tentang meningkatkan prestasi peranti berfungsi memuat dan memunggah data. Tiga port untuk bekerja dengan data yang dilaksanakan di Nehalem berhijrah ke Sandy Bridge. Tetapi untuk meningkatkan kecekapan mereka, jurutera menyatukan dua port yang sebelum ini bertujuan untuk menyimpan alamat dan memuatkan data. Kini mereka telah menjadi setara dan kedua-duanya boleh sama ada memuatkan alamat dan data, atau memuat naik alamat. Port ketiga kekal tidak berubah dan bertujuan untuk menyimpan data. Memandangkan setiap port mampu melepasi sehingga 16 bait setiap kitaran, jumlah pemprosesan cache data peringkat pertama dalam seni bina mikro baharu telah meningkat sebanyak 50%. Akibatnya, pemproses dengan seni bina mikro Sandy Bridge boleh memuatkan sehingga 32 bait data dan menyimpan 16 bait data bagi setiap kitaran jam.

Membandingkan semua inovasi yang diterangkan, kami mendapati bahawa seni bina mikro teras pengkomputeran dalam pemproses Sandy Bridge telah berubah dengan lebih ketara. Inovasi yang diperkenalkan, tanpa ragu-ragu, agak hampir dengan fakta bahawa pemproses ini benar-benar boleh dikaitkan bukan kepada penghalusan mudah kesesakan Nehalem, tetapi kepada pemprosesan yang agak serius.

Pendekatan baru untuk integrasi

Dengan pembangunan seni bina Nehalem, Intel mula mengambil langkah sebenar ke arah meningkatkan tahap integrasi pemprosesnya. Mereka mula memindahkan unit berfungsi secara berturut-turut yang sebelum ini merupakan hak prerogatif satu set logik: pengawal memori, pengawal PCI Ekspres, teras grafik. Juga, cache tahap ketiga telah ditambahkan pada pemproses. Dalam erti kata lain, pemproses telah menjadi bukan sahaja "pusat pengkomputeran" tempatan, tetapi kepekatan sekumpulan besar blok kompleks heterogen.

Sudah tentu, kesatuan sedemikian mempunyai banyak aspek positif dan membolehkan anda meningkatkan produktiviti dengan mengurangkan kelewatan dalam pertukaran data. Walau bagaimanapun, semakin banyak blok yang berbeza terdapat dalam pemproses, semakin sukar untuk melaksanakan perhubungan antara mereka di peringkat elektrik. Dan masalah yang paling serius dalam hal ini ialah sambungan cache L3 yang dikongsi dengan teras pemproses, terutamanya memandangkan prospek peningkatan selanjutnya dalam bilangan mereka. Dalam erti kata lain, semasa mengusahakan seni bina mikro pemproses Sandy Bridge, pemaju terpaksa memikirkan secara serius tentang mengatur skema interaksi yang mudah antara unit berfungsi yang terletak dalam pemproses. Sambungan silang konvensional yang digunakan sebelum ini boleh berfungsi dalam Nehalem dua, empat dan enam teras, tetapi untuk reka bentuk pemproses modular dengan jumlah yang besar Ia tidak lagi sesuai untuk biji yang berbeza.

Sebenarnya, ini telah diambil kira dalam pemproses pelayan lapan teras Nehalem-EX, di mana prinsip sambungan antara teras pengkomputeran dan cache L3 digunakan Teknologi baru. Teknologi ini, yang telah berjaya berhijrah ke Sandy Bridge, adalah bas cincin. Dalam pemproses lanjutan, teras pengkomputeran, cache, teras grafik dan elemen northbridge digabungkan dengan bas gelang khas dengan protokol seperti QPI, yang telah memungkinkan untuk mengurangkan dengan ketara bilangan sambungan intra-pemproses yang diperlukan untuk isyarat penghalaan.

Untuk melaksanakan interaksi blok berfungsi pemproses dengan berkesan dengan cache peringkat ketiga melalui bas gelang, dalam pemproses Sandy Bridge ia dibahagikan kepada bank yang sama sebanyak 2 MB setiap satu. Reka bentuk asal menganggap bahawa bilangan bank ini sepadan dengan bilangan teras pemproses. Tetapi untuk tujuan pemasaran, tanpa menjejaskan integriti cache, bank boleh diputuskan sambungan dari bas, sekali gus mengurangkan saiz cache keseluruhan. Setiap bank memori cache dikawal oleh pengadilnya sendiri, tetapi pada masa yang sama mereka semua bekerja dalam kerjasama rapat - maklumat tidak diduplikasi di dalamnya. Membahagikan kepada bank tidak bermakna memisahkan cache L3, ia hanya membolehkan anda meningkatkan daya pengeluarannya, yang hasilnya berskala dengan peningkatan bilangan teras dan, dengan itu, bank. Sebagai contoh, memandangkan lebar "cincin" yang digunakan untuk pemindahan data ialah 32 bait, lebar jalur cache L3 puncak pemproses empat teras yang beroperasi pada 3.4 GHz ialah 435.2 GB/s.

Bas cincin adalah baik bukan sahaja untuk skalabiliti kerana bilangan teras pemproses meningkat. Memandangkan apabila bertukar maklumat di sepanjang "cincin" laluan terpendek digunakan, kependaman cache L3 juga telah berkurangan. Kini ia adalah 26-31 kitaran, manakala cache Nehalem L3 menawarkan kependaman 35-40 kitaran. Walau bagaimanapun, perlu diambil kira bahawa semua memori cache di Sandy Bridge beroperasi pada frekuensi pemproses, iaitu, ia menjadi lebih pantas disebabkan ini juga.

Satu lagi kelebihan yang dibawa oleh bas cincin ialah ia memungkinkan untuk menyambungkan teras grafik yang disepadukan ke dalam pemproses ke laluan pemindahan data biasa. Iaitu, grafik dalam Sandy Bridge berfungsi dengan memori tidak secara langsung, tetapi sama dengan teras pemproses - melalui cache tahap ketiga. Ini meningkatkan prestasinya dan juga mengurangkan kerosakan yang boleh disebabkan oleh grafik bersepadu kepada prestasi sistem keseluruhan dengan bersaing untuk bas memori dengan teras pemprosesan.

Teras grafik mendapat ciri baharu

Penampilan teras grafik bersepadu dalam pemproses bukanlah perkara baharu; pemproses keluarga Clarkdale dengan GPU Intel HD Graphics terbina dalam telah berada di pasaran selama hampir setahun. Tetapi di Sandy Bridge, grafik dan teras pengkomputeran akhirnya menjadi kawan; mereka terletak pada cip semikonduktor yang sama dan disambungkan oleh bas gelang biasa di mana semua sumber pemproses lain digunakan secara sama rata. Penstrukturan semula seni bina ini, yang membawa teras grafik lebih dekat dengan pengawal memori dan meletakkan semua keupayaan cache peringkat ketiga, mempunyai kesan positif ke atas prestasi. Walau bagaimanapun, seperti teras pengkomputeran, teras grafik telah menerima penambahbaikan penting lain, yang mana ia secara rasmi dimiliki oleh generasi akan datang.

Secara umum, seni bina teras grafik tidak menjadi berbeza secara asas: ia masih berdasarkan 12 pemproses eksekutif (shader). Walau bagaimanapun, pembangun dapat hampir menggandakan prestasi mereka pada beberapa operasi, dan sebagai tambahan, mencapai keselarian yang lebih baik dalam kerja mereka. Terima kasih kepada perubahan yang dibuat, sokongan untuk Shader Model 4.1 dan DirectX 10.1 telah ditambah kepada ciri-ciri teras grafik baharu.

Memandangkan teras grafik berpindah ke kristal semikonduktor 32-nm, ia menjadi mungkin untuk meningkatkan kekerapan jamnya tanpa rasa sakit, yang boleh mencapai sehingga 1.35 GHz. Hasil daripada semua tindakan ini, grafik Sandy Bridge dalam aplikasi sebenar akan menjadi setanding dalam kelajuan kepada kad video diskret tahap kemasukan. Intel juga berfikir tentang melaksanakan anti-aliasing skrin penuh menggunakan teras grafiknya yang menjanjikan! Dalam erti kata lain, Sandy Bridge mempunyai setiap peluang untuk menjadi bersepadu yang paling produktif penyelesaian grafik, yang akan dapat memijak kedudukan kad video diskret dalam julat harga yang lebih rendah. Walaupun, sudah tentu, AMD dan NVIDIA, sebagai hujah balas, pastinya akan menekankan kekurangan sokongan untuk DirectX 11, yang boleh berguna bukan sahaja permainan terkini, tetapi juga, sebagai contoh, aplikasi yang menggunakan DirectCompute, seperti pelayar Internet masa depan.

Walau bagaimanapun, perkara itu tidak terhad kepada hanya menambah baik seni bina teras grafik sedia ada. Blok khusus baharu telah ditambahkan pada bahagian grafik Sandy Bridge, direka untuk penyahkodan dan pengekodan strim video dalam format MPEG2, VC1 dan AVC yang popular.

Sudah tentu, hari ini anda tidak akan mengejutkan sesiapa sahaja dengan penyahkodan video perkakasan; teras grafik Clarkdale juga boleh melakukannya. Walau bagaimanapun, sebelum ini operasi ini diberikan kepada pemproses shader, tetapi kini ia dikendalikan oleh unit berfungsi yang berasingan. Inti pengagihan semula peranan ini ialah keserasian baharu dengan video 3D; untuk teras grafik baharu, penyahkodan perkakasan bagi strim Blu-ray atau MVC 3D stereo tidak menimbulkan sebarang masalah.

Tambahan yang lebih menarik ialah codec perkakasan yang mampu mengekod aliran video ke dalam format AVC. Dari segi praktikal, ini bermakna teras grafik Sandy Bridge mempunyai semua sumber yang diperlukan untuk melaksanakan transkod video pada prestasi tinggi tanpa menggunakan kuasa pemprosesan tradisional. Yang sebenarnya, memandangkan penggunaan pemproses Intel yang meluas, pastinya akan berjaya digunakan oleh pembangun perisian. Lebih-lebih lagi, blok pengekodan perkakasan dan penyahkodan juga boleh digunakan dalam sistem berdasarkan cipset Intel P67, iaitu, menggunakan kad grafik diskret luaran.

Anda tidak perlu mencari jauh untuk contoh khusus: diketahui bahawa sokongan untuk keupayaan media baharu Sandy Bridge akan hadir dalam produk popular seperti ArcSoft MediaConverter, Corel DVD Factory, CyberLink MediaEspresso, Movavi Video Converter, Roxio Creator, dll. . Dan, dengan cara ini, apabila menggunakan unit multimedia teras grafik Sandy Bridge untuk transkod video, pemproses shader kekal bebas daripada beban, yang tiada siapa yang mengganggu untuk menyambung ke proses pemprosesan tambahan video atau kesan khas.

DALAM pelbagai model pemproses dengan microarchitecture Sandy Bridge, teras grafik akan hadir dalam dua versi: Intel HD Graphics 2000 dan Intel HD Graphics 3000. Perbezaannya adalah dalam bilangan pemproses pelaksanaan aktif (shader). Model teras grafik yang lebih lama, yang bertujuan untuk penyelesaian mudah alih dan pemproses lama untuk segmen "desktop" akan mempunyai kesemua 12 unit pelaksanaan, manakala variasi mudah teras ini, Intel HD Graphics 2000, berpuas hati dengan hanya enam unit sedemikian. Selain itu, kekerapan Intel HD Graphics 2000 akan lebih rendah sedikit. Tetapi elemen GPU yang paling menarik - pengekod dan penyahkod perkakasan - akan hadir sepenuhnya dalam kedua-dua versi.

Northbridge dengan cara baharu - ejen sistem

Hanya satu unit berfungsi pemproses Sandy Bridge kekal tidak diperiksa - yang dipanggil ejen sistem, yang menggabungkan pengawal untuk antara muka pemproses luaran: PCI Express, DMI, memori dan antara muka paparan. Sebenarnya, dalam diri ejen sistem kita mempunyai lebih kurang perkara yang sama yang dipanggil Uncore dalam pemproses Nehalem. Walau bagaimanapun, ejen sistem di Sandy Bridge masih bukan analog lengkap Uncore. Ia tidak termasuk cache L3, yang dalam seni bina mikro baharu bertindak sebagai unit berfungsi berasingan yang beroperasi pada frekuensi pemproses. Satu lagi perbezaan antara ejen sistem ialah pertukaran data antaranya dengan pemproses dan teras grafik, serta dengan cache peringkat ketiga, berlaku melalui bas gelang yang sama yang menyatukan semua entiti dalam Sandy Bridge.

Bercakap tentang inovasi yang terdapat dalam ejen sistem, pertama sekali saya ingin mengatakan tentang peningkatan yang lama diinginkan pada pengawal memori. Dalam pemproses Westmere (Clarkdale), pengawal memori yang digabungkan dengan teras grafik tidak berfungsi dengan baik sisi terbaik. Di Sandy Bridge, regresi ini akhirnya telah dihapuskan; pengawal memori baharu sekurang-kurangnya tidak lebih perlahan daripada pengawal memori pemproses Lynnfield. Pada masa yang sama, pengawal menyokong DDR3 SDRAM dwi-saluran: secara rasmi - DDR3-1067 atau DDR3-1333, tetapi sebenarnya pemproses Sandy Bridge mempunyai satu set pengganda yang membolehkan memori dicatatkan pada frekuensi 1600, 1866 dan 2133 MHz.

Anda boleh bayangkan anggaran tahap prestasi pengawal memori Sandy Bridge, sebagai contoh, berdasarkan keputusan ujian Aida64 yang tersedia.

Menurut xfastest.com. Ujian telah dijalankan pada Teras i7-2400 dengan

memori DDR3-1600 dwi saluran dengan pemasaan 7-7-7-21-1T

Kependaman subsistem memori dalam sistem dengan pemproses Sandy Bridge ternyata setanding dengan kependaman platform serupa dengan pemproses LGA1156 Core i7. Pada masa yang sama, CPU baharu jelas mendapat manfaat dari segi daya pemprosesan subsistem memori.

Pengawal bas PCIE di Sandy Bridge adalah serupa dengan pengawal serupa untuk pemproses LGA1156. Ia menyokong 16 lorong PCI Express 2.0, yang boleh dikumpulkan ke dalam sama ada satu bas PCIE 16x atau dua bas PCIE 8x. Itulah sebabnya platform LGA1366 lama tidak akan kehilangan kaitannya dengan keluaran sistem LGA1155: ia akan terus menjadi satu-satunya pilihan yang membolehkan anda memasang subsistem video berkelajuan penuh yang menggabungkan beberapa GPU yang disambungkan oleh bas PCIE dengan lebar jalur maksimum.

Perubahan penting juga telah berlaku dari segi antara muka paparan yang disokong. Teras grafik pemproses baharu akan dapat menggunakan HDMI versi 1.4, ciri utamanya ialah sokongan untuk penghantaran imej 3D.

Pengurusan kuasa dan overclocking

Satu lagi bahagian penting dalam ejen sistem Sandy Bridge, sebagai tambahan kepada pengawal antara muka luaran, ialah PCU (Unit Kawalan Kuasa). Sama seperti dalam pemproses Nehalem, unit ini ialah mikropengawal boleh atur cara yang mengumpul maklumat tentang suhu dan penggunaan semasa pelbagai nod pemproses dan mempunyai keupayaan untuk mengawal frekuensi dan voltan bekalan secara interaktif. PCU melaksanakan kedua-dua fungsi penjimatan tenaga dan mod turbo, yang telah dibangunkan lagi di Sandy Bridge.Semua modul berfungsi yang membentuk pemproses Sandy Bridge dibahagikan kepada tiga domain yang menggunakan jam frekuensi bebas dan litar sambungan kuasa. Domain pertama dan utama menggabungkan teras pemproses dan cache L3, yang berjalan pada frekuensi tunggal dan ketegangan. Domain kedua ialah teras grafik, yang menggunakan frekuensinya sendiri. Domain ketiga ialah ejen sistem itu sendiri.

Pemisahan ini membenarkan jurutera melaksanakan Intel SpeedStep yang Dipertingkatkan dan Turbo Boost serentak dan bebas untuk teras grafik dan pemproses. Pendekatan yang sama telah digunakan dalam pemproses mudah alih Arrandale, tetapi di sana ia berfungsi dengan cara yang mudah, melalui pemandu. Di Sandy Bridge ia dilaksanakan sepenuhnya penyelesaian perkakasan, yang mengawal kekerapan pengkomputeran dan teras grafik dalam cara yang saling berkaitan, dengan mengambil kira penggunaan semasanya. Ini membolehkan anda mendapatkan overclocking teras pemproses yang lebih serius, dilaksanakan melalui mod turbo, manakala teras grafik melahu, dan sebaliknya - overclocking ketara teras grafik apabila teras pengkomputeran tidak dimuatkan sepenuhnya. Keagresifan mod turbo dalam Sandy Bridge mudah dinilai dengan fakta bahawa kekerapan pemproses boleh meningkat empat langkah berbanding dengan kekerapan dinilai, dan variasi dalam kekerapan teras grafik boleh mencapai enam hingga tujuh langkah.

Walau bagaimanapun, ini bukan semua inovasi dalam Teknologi turbo Galakan. Kelebihannya pelaksanaan baharu Ia juga terletak pada hakikat bahawa PCU mempunyai keupayaan untuk mengawal frekuensi dengan lebih bijak, memfokuskan pada suhu sebenar komponen pemproses, dan bukan hanya penggunaan kuasanya. Ini bermakna apabila pemproses beroperasi dalam keadaan terma yang menggalakkan, penggunaan kuasanya dibenarkan melebihi had TDP.

Semasa kerja harian biasa, beban pemproses berubah-ubah. Pemproses menghabiskan sebahagian besar masanya dalam keadaan penjimatan tenaga, dan prestasi tinggi diperlukan hanya untuk jangka masa yang singkat. Semasa selang waktu sedemikian, pemanasan pemproses tidak mempunyai masa untuk mencapai sebarang nilai yang serius - inersia yang disediakan oleh kekonduksian terma penyejuk mempengaruhinya. PCU yang mengawal frekuensi di Sandy Bridge betul-betul percaya bahawa tiada perkara buruk akan berlaku jika pada saat-saat seperti itu pemproses overclocked lebih daripada nilai pelesapan haba teori yang boleh dibenarkan secara teori. Apabila suhu pemproses mula menghampiri nilai kritikal, kekerapan akan dikurangkan kepada nilai selamat.

Ini secara automatik menghasilkan faedah dari sudut pandangan mencapai prestasi maksimum menggunakan penyejukan berkualiti tinggi dalam sistem berdasarkan Sandy Bridge. Tetapi jangan menipu diri sendiri - tempoh maksimum operasi dalam keadaan "melampaui TDP" dihadkan oleh perkakasan kepada 25 saat.

Bagi overclocking konvensional, dilakukan kaedah tradisional, maka perubahan kardinal menanti kami di sini, yang tidak mungkin diterima dengan penuh semangat oleh overclockers. Punca semua kejahatan terletak pada keinginan yang sama untuk integrasi - dalam platform LGA1155, Intel memindahkan penjana frekuensi asas ke set logik sistem. Walau bagaimanapun, bukan ini yang menyebabkan akibat maut untuk overclocking tradisional, tetapi hakikat bahawa penjana frekuensi menjadi satu-satunya dan ia digunakan untuk menjana semua frekuensi dalam sistem. Seperti yang anda ketahui, tidak semua bas dan pengawal mengendalikan overclocking dengan baik. Contohnya, apabila meningkatkan kekerapan atau kelajuan bas PCI Express Operasi USB atau pengawal SATA, ketidakstabilan boleh berlaku dengan cepat. Dan faktor inilah yang akan menjadi halangan yang serius apabila cuba meningkatkan kekerapan pemproses pusat dengan mempercepatkan penjana frekuensi asas.

Faktanya adalah seperti berikut. Kekerapan jam asas yang digunakan dalam pemproses Sandy Bridge ditetapkan kepada 100 MHz. Penjana itu sendiri membolehkan anda mengubah nilai frekuensi ini dalam julat yang sangat luas dan juga dalam kenaikan 0.1 MHz. Walau bagaimanapun, percubaan untuk meningkatkannya dengan cepat mengalami ketidakstabilan atau ketidakupayaan sistem. Oleh itu, kami tidak mengetahui sebarang pengalaman yang berjaya dalam meningkatkan frekuensi asas melebihi 105 MHz. Dalam erti kata lain, kaedah overclocking tradisional dan teruji masa dengan meningkatkan kekerapan penjana jam dalam sistem berdasarkan Sandy Bridge gagal dan tidak membenarkan overclocking melebihi 5%.

Jadi satu-satunya pilihan yang benar-benar bermakna untuk overclocking pemproses LGA1155 yang menjanjikan ialah meningkatkan faktor pendaraban mereka. Antara model Sandy Bridge yang Intel akan tawarkan kepada pelanggan, akan ada produk istimewa yang tidak mempunyai pengganda terkunci dan boleh, secara teori, dioverclock kepada 5.7 GHz (57 ialah nilai pengganda maksimum yang terbina dalam mikroarkitektur). Walau bagaimanapun, pemproses sedemikian, yang akan ditetapkan oleh akhiran "K" dalam nombor pemproses, akan diklasifikasikan sebagai atas kategori harga dan pada masa yang sama mereka akan kos lebih sedikit daripada rakan sejawatan biasa mereka.

Bagi pengguna model CPU biasa, overclocking terhad secara buatan akan ditawarkan - pemproses sedemikian juga akan membenarkan peningkatan dalam faktor pendaraban, tetapi tidak lebih daripada 4 langkah berbanding nilai standard. Lebih-lebih lagi, kita bercakap secara khusus mengenai overclocking; menukar pengganda tidak akan menjejaskan teknologi Turbo Boost, yang, sebagai tambahan kepada peningkatan frekuensi manual ini, juga akan menambah satu automatiknya sendiri. Di samping itu, dalam semua pemprosesnya, Intel tidak akan mengehadkan pengganda yang menentukan kekerapan teras grafik dan memori. Iaitu, overclocking teras grafik dan memori akan tersedia dalam sistem dengan sebarang pengubahsuaian Sandy Bridge - kedua-dua overclocking dan biasa.

Walau bagaimanapun, overclocker tidak mungkin mempertimbangkan pampasan yang mencukupi ini, jadi kemungkinan besar mereka akan berminat secara eksklusif dalam pemproses tidak berkunci - Core i5-2500K dan Core i7-2600K. Selain itu, maklumat yang tersedia tentang potensi frekuensi mereka kelihatan sangat menggalakkan. Sebagai contoh, terdapat bukti prestasi stabil Core i7-2600K apabila overclock dan sehingga 5.0 GHz dengan penyejukan udara.

data windwithme, http://itbbs.pconline.com.cn/diy/12120702.html

Keputusan yang diterangkan telah dicapai dengan menggunakan penyejuk Prolimatech Mega Shadow Deluxe Edition dan meningkatkan voltan teras pemproses kepada 1.45 V. Sudah tentu, peningkatan serius dalam voltan tidak mungkin sesuai untuk kegunaan harian, tetapi kami percaya bahawa pada frekuensi kira-kira Pemproses Sandy Bridge 4.8 GHz akan berfungsi 24/7 mod yang mereka pasti boleh.

Mari kita ringkaskan

Kembali ke permulaan artikel ini, saya ingin mengingatkan anda bahawa Intel meletakkan Sandy Bridge sebagai "tok" sebagai sebahagian daripada strategi "tik-tok"nya. Ini bermakna, menurut pengilang, pemproses ini adalah pembawa mikroarchitecture baru. Pada masa yang sama, meneliti strukturnya, kami tidak menjumpai sebarang idea asas baru yang akan menyerang imaginasi. Malah, terdapat hanya banyak penambahbaikan kecil, kebangkitan teknologi lama yang berjaya dan penyepaduan selanjutnya. Adakah munasabah untuk bercakap tentang pemproses generasi baharu dalam kes ini, atau patutkah Sandy Bridge benar-benar dianggap hanya sebagai Nehalem yang telah berkembang?

Dan di sini kami tidak mempunyai keraguan - kami bersetuju sepenuhnya dengan pendapat Intel. Pemproses Sandy Bridge adalah ilustrasi yang sangat baik tentang kemunculan kualiti baharu akibat pengumpulan perubahan kuantitatif. Banyak inovasi dalam seni bina mikro teras pengkomputeran, penambahan sokongan untuk arahan AVX 256-bit, teras grafik yang lebih baik, penampilan unit perkakasan untuk pengekodan dan penyahkodan video, cache L3 baharu, bas cincin, sistem pintar ejen, teknologi Turbo Boost yang lebih agresif dan peningkatan frekuensi jam - itu sahaja Secara individu, ini mungkin kelihatan seperti perkara kecil, tetapi secara keseluruhannya ia menghasilkan produk yang telah bertambah baik secara asasnya. Lebih-lebih lagi, keunggulannya agak ketara - ia dapat dilihat dengan jelas dalam fakta bahawa Sandy Bridge telah menjadi jauh lebih pantas daripada pendahulunya, sambil kekal dalam pakej terma yang sama.

Sudah tentu, apabila kami menyebut "ketara," kami tidak bermaksud peningkatan kelajuan yang ketara. Walau bagaimanapun, dengan menggantikan sistem LGA1156 berasaskan Lynnfield atau Clarkdale dengan set papan induk LGA1155 harga yang sama dan pemproses Sandy Bridge, anda boleh menjangkakan sekurang-kurangnya 25% peningkatan dalam prestasi dalam semua aplikasi yang bergantung kepada pemproses.

Walau bagaimanapun, terdapat juga kelas masalah tertentu di mana Sandy Bridge akan menjadi susunan magnitud yang lebih baik daripada pendahulunya disebabkan oleh blok struktur baharu. Pertama sekali, peningkatan yang ketara dalam prestasi dijangka dalam banyak utiliti untuk transkoding video, untuk keperluan codec dan penyahkod perkakasan khas telah ditambahkan pada CPU baharu. Selain itu, algoritma multimedia, kriptografi, saintifik atau kewangan menggunakan set arahan AES-NI dan AVX baharu akan dapat berjalan dengan lebih pantas pada CPU baharu. Sudah tentu, semua kelebihan ini boleh diperolehi hanya dengan pengoptimuman perisian khas, tetapi nampaknya anda tidak perlu menunggu terlalu lama untuk itu, kerana jurutera Intel telah berusaha sedaya upaya untuk memastikan bahawa inovasi itu mudah untuk pembangun.

Pengguna yang berhasrat untuk menggunakan teras grafik terbina dalam juga akan mendapat manfaat yang besar daripada platform baharu. Berbanding dengan versi Intel HD Graphics sebelumnya, ia telah menjadi jauh lebih pantas, yang mana pemilik komputer riba masa depan berdasarkan Sandy Bridge dan platform baharu Sungai Huron. Dan jika pemproses baharu dirancang untuk digunakan sebagai sebahagian daripada komputer rumah atau HTPC, teras grafik terbina dalam akan berpuas hati dengan sokongan antara muka HDMI 1.4, yang membolehkan anda menghantar imej 3D ke peranti luaran.

Secara umum, nampaknya hanya terdapat satu kelemahan serius dalam Sandy Bridge - masalah dengan overclocking. Dan jika pembeli pemproses dalam kategori harga atas boleh, dengan membayar sedikit tambahan, mendapatkan pemproses tidak berkunci mesra overclocking, maka antara pemproses yang lebih murah daripada $200 tidak akan ada pilihan sedemikian. Jadi platform LGA1155 akan menandakan satu lagi trend - Intel mahu mengehadkan keupayaan overclocking pemproses kos rendah. Walau bagaimanapun, ini tidak mungkin memberi kesan besar terhadap populariti overclocking sebagai fenomena - penganut peralatan operasi sehingga had keupayaannya akan diterima dengan senang hati di kalangan penganutnya oleh AMD, yang tahun ini akan mengeluarkan produknya sendiri, tidak kurang membuat zaman daripada Sandy Bridge - Jentolak.

Akhirnya, Intel secara rasmi telah mengumumkan pemproses baharu yang berjalan pada mikroarkitektur baharu. Bagi kebanyakan orang, "Pengumuman Sandy Bridge" hanyalah perkataan, tetapi pada umumnya, generasi Intel Core ll, jika bukan era baharu, maka sekurang-kurangnya kemas kini hampir keseluruhan pasaran pemproses.

Pada mulanya dilaporkan bahawa hanya tujuh pemproses akan dilancarkan, tetapi pada halaman yang paling berguna ark.intel.com maklumat tentang semua produk baharu telah pun muncul. Terdapat beberapa lagi pemproses, atau sebaliknya pengubahsuaian mereka (dalam kurungan saya menunjukkan harga anggaran - berapa kos setiap pemproses dalam kumpulan 1000 keping):

mudah alih:

Intel Core i5-2510E (~$266)Intel Core i5-2520M

Intel Core i5-2537M

Intel Core i5-2540M

Perbandingan terperinci visual pemproses mudah alih Intel Core i5 generasi kedua.

Intel Core i7-2617M

Intel Core i7-2620M

Intel Core i7-2629M

Intel Core i7-2649M

Intel Core i7-2657M

Intel Core i7-2710QE (~$378)

Intel Core i7-2720QM

Intel Core i7-2820QM

Intel Core i7-2920XM Edisi Extreme

Perbandingan terperinci visual pemproses mudah alih Intel Core i7 generasi kedua.

Atas meja:

Intel Core i3-2100 (~$117)Intel Core i3-2100T

Intel Core i3-2120 ($138)

Perbandingan visual dan terperinci pemproses desktop Intel Core i3 generasi kedua.

Intel Core i5-2300 (~$177)

Intel Core i5-2390T

Intel Core i5-2400S

Intel Core i5-2400 (~$184)

Intel Core i5-2500K (~$216)

Intel Core i5-2500T

Intel Core i5-2500S

Intel Core i5-2500 (~205$)

Perbandingan visual dan terperinci pemproses desktop Intel Core i5 generasi kedua.

Intel Core i7-2600K (~$317)

Intel Core i7-2600S

Intel Core i7-2600 (~$294)

Perbandingan visual dan terperinci pemproses desktop Intel Core i7 generasi kedua.

Seperti yang anda lihat, nama model kini mempunyai empat digit dalam nama - ini dilakukan untuk mengelakkan kekeliruan dengan pemproses generasi sebelumnya. Barisan pemain ternyata agak lengkap dan logik - siri i7 yang paling menarik jelas dipisahkan daripada i5 dengan kehadiran teknologi Hiper Threading dan peningkatan saiz cache. Dan pemproses keluarga i3 berbeza daripada i5 bukan sahaja dalam bilangan teras yang lebih kecil, tetapi juga dalam kekurangan teknologi Turbo Boost.

Anda mungkin juga melihat huruf dalam nama pemproses, yang tanpanya barisan telah dikurangkan dengan banyak. Jadi inilah surat-suratnya S Dan T bercakap tentang penggunaan kuasa yang dikurangkan, dan KEPADA – pengganda percuma.

Struktur visual pemproses baharu:

Seperti yang anda lihat, sebagai tambahan kepada grafik dan teras pengkomputeran, memori cache dan pengawal memori, terdapat apa yang dipanggil Agen Sistem– banyak perkara dibuang ke sana, contohnya, pengawal memori DDR3 dan PCI-Express 2.0, model pengurusan kuasa dan blok yang bertanggungjawab pada peringkat perkakasan untuk pengendalian GPU terbina dalam dan untuk output imej apabila ia digunakan.

Semua komponen "teras" (termasuk pemproses grafik) disambungkan oleh bas gelang berkelajuan tinggi dengan akses penuh ke cache L3, yang menyebabkan kelajuan pertukaran data keseluruhan dalam pemproses itu sendiri telah meningkat; Apa yang menarik ialah pendekatan ini membolehkan anda meningkatkan prestasi pada masa hadapan, hanya dengan menambah bilangan teras yang ditambahkan pada bas. Walaupun kini semuanya menjanjikan yang terbaik - berbanding dengan pemproses generasi sebelumnya, prestasi yang baharu lebih mudah disesuaikan dan, menurut pengilang, dalam banyak tugas ia boleh menunjukkan peningkatan 30-50% dalam kelajuan pelaksanaan tugas !

Jika anda ingin mengetahui lebih lanjut tentang seni bina baharu, maka dalam bahasa Rusia saya boleh mengesyorkan tiga artikel ini - , , .

Pemproses baharu ini dihasilkan sepenuhnya mengikut teknologi proses 32nm dan buat pertama kalinya mempunyai seni bina mikro "visual pintar" yang menggabungkan terbaik dalam kelasnya. kuasa pengkomputeran dan teknologi pemprosesan grafik 3D pada satu cip. Terdapat banyak inovasi dalam grafik Sandy Bridge, terutamanya bertujuan untuk meningkatkan prestasi apabila bekerja dengan 3D. Seseorang boleh berhujah untuk masa yang lama tentang "mengenakan" sistem video bersepadu, tetapi tidak ada penyelesaian lain seperti itu. Tetapi terdapat slaid ini daripada pembentangan rasmi, yang mendakwa sebagai munasabah, termasuk dalam produk mudah alih (komputer riba):

Saya sebahagiannya bercakap tentang teknologi baharu generasi kedua pemproses Intel Core, jadi saya tidak akan mengulangi diri saya sendiri. Saya hanya akan fokus pada pembangunan Intel Insider, yang penampilannya ramai yang terkejut. Seperti yang saya faham, ini akan menjadi sejenis kedai yang akan memberi pemilik komputer akses kepada filem definisi tinggi, terus daripada pencipta filem ini - sesuatu yang sebelum ini muncul hanya beberapa lama selepas pengumuman dan penampilan cakera DVD atau Blu-ray. Untuk menunjukkan ciri ini, Naib Presiden Intel Muli Eden(Mooly Eden) dijemput ke pentas Kevin Tsujiharu(Kevin Tsujihara), Presiden Kumpulan Hiburan Warner Home. saya petik:

« Warner Bros. jumpa sistem peribadi platform yang paling serba boleh dan meluas untuk menyampaikan kandungan hiburan berkualiti tinggi, dan kini Intel menjadikan platform itu lebih dipercayai dan selamat. Mulai sekarang, dengan bantuan kedai WBShop, serta rakan kongsi kami seperti CinemaNow, kami akan dapat menyediakan pengguna PC dengan keluaran baharu dan filem daripada katalog kami dalam kualiti HD sebenar"- Muli Eden menunjukkan kerja teknologi ini menggunakan contoh filem "Inception". Dengan kerjasama studio industri terkemuka dan gergasi media (seperti Best Buy CinemaNow, Hungama Digital Media Entertainment, Image Entertainment, Sonic Solutions, Warner Bros. Digital Distribution dan lain-lain), Intel mencipta ekosistem (perkakasan) yang selamat dan kalis cetak rompak untuk pengedaran, penyimpanan dan main balik video berkualiti tinggi.

« Warner Bros. jumpa sistem peribadi platform yang paling serba boleh dan meluas untuk menyampaikan kandungan hiburan berkualiti tinggi, dan kini Intel menjadikan platform itu lebih dipercayai dan selamat. Mulai sekarang, dengan bantuan kedai WBShop, serta rakan kongsi kami seperti CinemaNow, kami akan dapat menyediakan pengguna PC dengan keluaran baharu dan filem daripada katalog kami dalam kualiti HD sebenar"- Muli Eden menunjukkan kerja teknologi ini menggunakan contoh filem "Inception". Dengan kerjasama studio industri terkemuka dan gergasi media (seperti Best Buy CinemaNow, Hungama Digital Media Entertainment, Image Entertainment, Sonic Solutions, Warner Bros. Digital Distribution dan lain-lain), Intel mencipta ekosistem (perkakasan) yang selamat dan kalis cetak rompak untuk pengedaran, penyimpanan dan main balik video berkualiti tinggi.

Operasi teknologi yang disebutkan di atas akan serasi dengan dua perkembangan yang tidak kurang menarik, yang turut hadir dalam semua model pemproses generasi baharu. Saya bercakap tentang (Intel WiDi 2.0) dan Intel InTru 3-D. Yang pertama direka untuk penghantaran wayarles video HD (menyokong resolusi sehingga 1080p), yang kedua direka untuk memaparkan kandungan stereo pada monitor atau TV definisi tinggi melalui sambungan HDMI 1.4.

Dua lagi fungsi yang saya tidak temui tempat yang lebih sesuai dalam artikel itu - Sambungan Vektor Lanjutan Intel(AVX). Sokongan pemproses untuk arahan ini meningkatkan kelajuan aplikasi intensif data seperti editor audio dan perisian untuk penyuntingan foto profesional.

… Dan Video Penyegerakan Pantas Intel- terima kasih kepada bekerjasama Dengan syarikat perisian seperti CyberLink, Corel dan ArcSoft, gergasi pemproses itu telah berjaya meningkatkan prestasi tugas ini (transkod antara format H.264 dan MPEG-2) sebanyak 17 kali ganda berbanding prestasi grafik bersepadu generasi sebelumnya.

Katakan terdapat pemproses - bagaimana untuk menggunakannya? Betul - bersama-sama mereka, chipset baharu (set logik) juga diumumkan, yang merupakan wakil siri "keenam puluh". Nampaknya, hanya dua set dikhaskan untuk pengguna yang dahagakan produk baru, ini Intel H67 Dan Intel P67, di mana kebanyakan papan induk baharu akan dibina. H67 mampu berfungsi dengan teras video yang disepadukan ke dalam pemproses, manakala P67 dilengkapi dengan fungsi Performance Tuning untuk overclocking pemproses. Semua pemproses akan berfungsi dalam soket baharu, 1155 .

Saya gembira kerana pemproses baharu nampaknya serasi dengan soket pemproses Intel dengan seni bina generasi akan datang. Tambahan ini akan berguna sebagai pengguna biasa, dan pengeluar yang tidak perlu mereka bentuk semula dan mencipta peranti baharu.

Secara keseluruhan, Intel memperkenalkan lebih daripada 20 cip, set cip dan penyesuai wayarles, termasuk pemproses Intel Core i7, i5 dan i3 baharu, set cip Intel 6 Series dan penyesuai Intel Centrino Wi-Fi dan WiMAX. Sebagai tambahan kepada yang dinyatakan di atas, "lencana" berikut mungkin muncul di pasaran:

Tahun ini, lebih 500 model komputer meja dan komputer riba daripada jenama terkemuka dunia dijangka dikeluarkan pada pemproses baharu.

Dan akhirnya, sekali lagi video yang hebat, sekiranya sesiapa tidak melihatnya:

![]()

Adakah keunggulan Core i pertama (Nehalem dan, pada 2009, Westmere) berbanding CPU pesaing muktamad? Keadaan ini sedikit mengingatkan pada tahun pertama selepas pelepasan Pentium II: berehat dengan kejayaan dan menerima keuntungan rekod, adalah baik untuk meneruskan seni bina yang berjaya, tanpa banyak menukar namanya, menambah yang baru, penggunaan yang akan meningkatkan prestasi dengan ketara, tidak lupa tentang inovasi lain yang mempercepatkan program versi hari ini. Benar, berbeza dengan situasi 10 tahun yang lalu, kita mesti memberi perhatian kepada topik kecekapan tenaga yang sedang bergaya, dimainkan oleh kata sifat samar-samar Cool - "sejuk" dan "sejuk" - dan keinginan yang tidak kurang bergaya untuk disepadukan ke dalam pemproses semua yang masih wujud sebagai berasingan. Ini adalah sos produk baru yang dihidangkan.

"Sehari sebelum semalam", "semalam" dan "hari ini" pemproses Intel.

Hadapan penghantar. Warna menunjukkan jenis yang berbeza maklumat dan memproses atau menyimpan blok.

Ramalan

Mari kita mulakan dengan pengumuman Intel mengenai unit yang direka bentuk semula sepenuhnya (BPU). Seperti dalam Nehalem, setiap kitaran jam (dan sebelum pelaksanaan sebenar) ia meramalkan alamat bahagian 32-bait kod seterusnya bergantung pada kelakuan yang dijangkakan arahan lompatan dalam bahagian yang diramalkan - dan, nampaknya, tanpa mengira nombor dan jenis peralihan. Lebih tepat lagi, jika bahagian semasa mengandungi peralihan yang dicetuskan, alamatnya sendiri dan alamat sasaran akan dikeluarkan, jika tidak peralihan ke bahagian seterusnya berturut-turut diberikan. Ramalan itu sendiri telah menjadi lebih tepat kerana penggandaan (BTB), pemanjangan (GBHR) dan mengoptimumkan fungsi cincang capaian (BHT). Benar, ujian sebenar telah menunjukkan bahawa dalam beberapa kes kecekapan ramalan masih lebih buruk sedikit daripada di Nehalem. Mungkin meningkatkan produktiviti dengan pengurangan penggunaan tidak serasi dengan ramalan peralihan berkualiti tinggi? Mari kita cuba memikirkannya.

Di Nehalem (serta seni bina moden yang lain), BTB hadir dalam bentuk hierarki dua peringkat - kecil-"cepat" L1 dan besar-"perlahan" L2. Ini berlaku atas sebab yang sama mengapa terdapat beberapa peringkat: penyelesaian satu peringkat akan terlalu berkompromi dalam semua aspek (saiz, kelajuan tindak balas, penggunaan, dll.). Tetapi di SB, arkitek memutuskan untuk meletakkan satu tahap, dan saiznya adalah dua kali lebih besar daripada L2 BTB Nehalem, iaitu, mungkin sekurang-kurangnya 4096 sel - itulah jumlah yang terdapat dalam Atom. (Perlu diambil kira bahawa saiz kod yang paling kerap dilaksanakan perlahan-lahan berkembang dan semakin jarang dimuatkan ke dalam cache, saiznya adalah sama untuk semua CPU Intel sejak Pentium M pertama.) Secara teori, ini akan meningkatkan kawasan yang diduduki oleh BTB, dan kerana jumlah kawasan akan berubah tidak disyorkan (ini adalah salah satu postulat awal seni bina) - sesuatu perlu diambil dari beberapa struktur lain. Tetapi ada juga kelajuan. Memandangkan SB harus direka untuk kelajuan yang lebih tinggi sedikit dengan proses teknikal yang sama, seseorang boleh menjangkakan bahawa struktur besar ini akan menjadi hambatan bagi keseluruhan penghantar - melainkan ia juga disampaikan (dua sudah mencukupi). Benar, jumlah bilangan transistor yang beroperasi setiap kitaran jam dalam BTB akan berganda, yang tidak menyumbang kepada penjimatan tenaga sama sekali. Jalan buntu lagi? Untuk ini, Intel menjawab bahawa BTB baharu menyimpan alamat dalam jenis keadaan termampat, yang membolehkan anda mempunyai dua kali lebih banyak sel dengan kawasan dan penggunaan yang serupa. Tetapi masih belum mungkin untuk mengesahkan ini.

Mari kita lihat dari sisi lain. SB tidak menerima algoritma ramalan baharu, tetapi algoritma lama yang dioptimumkan: umum, untuk peralihan tidak langsung, gelung dan pulangan. Nehalem mempunyai GBHR 18-bit dan BHT yang tidak diketahui saiznya. Walau bagaimanapun, kami boleh menjamin bahawa bilangan sel dalam jadual adalah kurang daripada 2 18 , jika tidak, ia akan menduduki sebahagian besar teras. Oleh itu, terdapat fungsi cincang khas yang meruntuhkan 18 bit sejarah semua peralihan dan bit alamat arahan ke dalam indeks yang lebih pendek. Selain itu, kemungkinan besar, terdapat sekurang-kurangnya dua cincang - untuk semua bit GBHR dan bagi mereka yang mencerminkan pencetus peralihan yang paling sukar. Oleh itu, keberkesanan pengagihan huru-hara pelbagai corak tingkah laku mengikut indeks oleh nombor sel BHT menentukan kejayaan peramal Pandangan umum. Walaupun tidak dinyatakan secara eksplisit, Intel pastinya telah menambah baik cincang, membolehkan panjang GBHR yang lebih panjang digunakan dengan kecekapan padding yang sama. Tetapi anda masih boleh meneka tentang saiz BHT - serta bagaimana penggunaan tenaga peramal secara keseluruhan sebenarnya telah berubah... Bagi (RSB), ia masih 16-alamat, tetapi sekatan baharu telah diperkenalkan pada panggilan itu sendiri - tidak lebih empat setiap 16 bait kod.

Sebelum kita pergi lebih jauh, mari kita bercakap tentang sedikit percanggahan antara teori yang diisytiharkan dan amalan yang diperhatikan - dan ia menunjukkan bahawa peramal kitaran dalam SB telah dialih keluar, akibatnya ramalan peralihan terakhir ke permulaan kitaran dibuat oleh algoritma umum, iaitu lebih teruk. Seorang wakil Intel memberi jaminan kepada kami bahawa tiada apa yang "lebih teruk" akan berlaku, bagaimanapun...

Penyahkodan dan IDQ

Alamat perintah yang dilaksanakan yang diramalkan lebih awal (bergantian untuk setiap utas - dengan teknologi didayakan) dikeluarkan untuk menyemak kehadirannya dalam cache arahan (L1I) dan (L0m), tetapi kami akan berdiam diri tentang yang terakhir - kami akan menerangkan selebihnya depan buat masa ini. Anehnya, Intel mengekalkan saiz bahagian arahan yang dibaca dari L1I hingga 16 bait (di sini perkataan "bahagian" difahami mengikut kami). Sehingga kini, ini telah menjadi penghalang untuk kod yang saiz arahan puratanya telah berkembang melebihi 4 bait, dan oleh itu 4 arahan yang diingini untuk dilaksanakan setiap kitaran jam tidak akan masuk ke dalam 16 bait lagi. AMD menyelesaikan masalah ini dalam seni bina K10 dengan mengembangkan bahagian arahan kepada 32 bait - walaupun pada masa ini CPUnya tidak mempunyai lebih daripada 3 saluran paip. Dalam SB, ketidaksamaan saiz membawa kepada kesan sampingan: peramal menghasilkan alamat seterusnya bagi blok 32-bait, dan jika ia mengesan peralihan penembakan (mungkin) pada separuh pertamanya, maka tidak perlu membaca dan menyahkod yang kedua - walau bagaimanapun, ia akan dilakukan.

Dari L1I, bahagian pergi ke pradekoder, dan dari sana ke meter panjang itu sendiri (), yang memproses sehingga 7 atau 6 arahan/kitaran (dengan dan tanpa; Nehalem boleh mengendalikan maksimum 6) bergantung pada jumlah panjang dan kerumitan. Sejurus selepas peralihan, pemprosesan bermula dengan arahan pada alamat sasaran, jika tidak - dengan bait di mana predecoder menghentikan satu kitaran lebih awal. Begitu juga dengan titik akhir: sama ada ia (mungkin) peralihan yang dicetuskan, alamat bait terakhir yang datang daripada BTB, atau bait terakhir bahagian itu sendiri - melainkan had 7 perintah/kitaran dicapai, atau arahan "menyusahkan" tidak ditemui. Kemungkinan besar, penimbal meter panjang hanya mempunyai 2-4 bahagian, tetapi meter panjang boleh mendapat mana-mana 16 daripadanya berturut-turut bait. Sebagai contoh, jika pada permulaan bahagian 7 perintah dua bait diiktiraf, maka dalam kitaran jam seterusnya 16 bait lagi boleh diproses, bermula dari 15hb.

Meter panjang, antara lain, mengesan pasangan perintah gabungan makro. Kita akan bercakap tentang pasangan itu sendiri sedikit kemudian, tetapi buat masa ini mari kita ambil perhatian bahawa, seperti dalam Nehalem, tidak lebih daripada satu pasangan itu boleh dikesan setiap kitaran jam, walaupun maksimum 3 daripadanya boleh ditanda (dan satu lagi perintah tunggal). Walau bagaimanapun, mengukur panjang arahan ialah proses separa berurutan, jadi tidak mungkin untuk menentukan beberapa pasangan penggabungan makro semasa kitaran jam.

Perintah berlabel berakhir dalam satu daripada dua arahan (IQ: baris gilir arahan) - satu setiap utas, 20 perintah setiap satu (iaitu 2 lebih daripada Nehalem). membaca arahan dari baris gilir secara bergilir-gilir dan memindahkannya ke mop. Ia mempunyai 3 yang mudah (terjemahkan 1 arahan kepada 1 mop, dan dengan penggabungan makro - 2 arahan menjadi 1 mop), penterjemah yang kompleks (1 arahan kepada 1–4 uops atau 2 arahan kepada 1 mop) dan mikrosequencer untuk yang paling kompleks arahan yang memerlukan 5 dan lebih mop daripada . Selain itu, ia hanya menyimpan "ekor" setiap urutan, bermula dari uop ke-5, kerana 4 yang pertama dihasilkan oleh penterjemah yang kompleks. Lebih-lebih lagi, jika bilangan uop dalam program mikro tidak boleh dibahagikan dengan 4, maka empat terakhir mereka akan menjadi tidak lengkap, tetapi tidak mungkin untuk memasukkan 1-3 uops lagi daripada penterjemah dalam kitaran yang sama. Hasil penyahkodan pergi ke dan dua (satu setiap aliran). Yang terakhir (secara rasmi dipanggil IDQ - baris gilir penyahkod arahan, baris gilir perintah yang dinyahkod) masih mempunyai 28 uops dan keupayaan untuk menyekat gelung jika bahagian boleh lakunya sesuai di sana.

Semua ini (kecuali cache mop) sudah ada di Nehalem. Apakah perbezaannya? Pertama sekali, yang jelas, penyahkod telah diajar untuk memproses perintah subset baharu. Sokongan Set SSE dengan semua nombor tidak lagi mengejutkan sesiapa, dan pecutan penyulitan melalui arahan (termasuk PCLMULQDQ) telah ditambahkan pada Westmere (versi 32 nm Nehalem). Terdapat perangkap: fungsi ini tidak berfungsi untuk arahan yang mempunyai kedua-dua pemalar dan pengalamatan relatif RIP (relatif RIP, alamat relatif kepada penunjuk arahan - cara biasa mengakses data dalam kod 64-bit). Perintah sedemikian memerlukan 2 modul (pemuatan dan operasi berasingan), yang bermaksud bahawa penyahkod akan memproses tidak lebih daripada satu daripadanya setiap kitaran jam, menggunakan hanya penterjemah yang kompleks. Intel mendakwa bahawa pengorbanan ini dibuat untuk menjimatkan tenaga, tetapi tidak jelas tentang apa: penempatan berganda, pelaksanaan dan uops jelas akan mengambil lebih banyak sumber, dan oleh itu menggunakan lebih banyak tenaga, daripada satu.

Penggabungan makro telah dioptimumkan - sebelum ini, hanya aritmetik atau perbandingan logik(CMP atau TEST), kini perintah aritmetik mudah tambah dan tolak (TAMBAH, SUB, INC, DEC) dan logik “DAN” (DAN), juga berubah untuk lompat (perintah kedua pasangan), dibenarkan. Ini membolehkan anda mengurangkan 2 arahan terakhir kepada 1 mop dalam hampir mana-mana kitaran. Sudah tentu, sekatan pada arahan gabungan kekal, tetapi ia tidak kritikal, kerana situasi yang disenaraikan untuk sepasang arahan hampir selalu dilaksanakan:

- yang pertama daripada arahan pertama mestilah daftar;

- jika operan kedua bagi arahan pertama berada dalam ingatan, pengalamatan relatif RIP tidak dibenarkan;

- arahan kedua tidak boleh berada di permulaan atau melintasi sempadan garisan.

Peraturan untuk peralihan itu sendiri ialah:

- hanya UJIAN dan DAN yang serasi dengan sebarang syarat;

- perbandingan kepada (tidak) sama dengan dan mana-mana yang ditandatangani adalah serasi dengan mana-mana arahan pertama yang dibenarkan;

- perbandingan kepada (tidak) membawa dan mana-mana yang tidak ditandatangani tidak serasi dengan INC dan DEC;

- perbandingan lain (tanda, limpahan, pariti dan penolakannya) hanya sah untuk UJIAN dan DAN.

Perubahan utama dalam baris gilir uop ialah gabungan jenis uop , di mana akses memori memerlukan pembacaan daftar indeks, (dan beberapa jenis jarang lain) dibahagikan kepada pasangan apabila ditulis ke IDQ. Walaupun ada 4 uops sebegitu, kesemua 8 jumlah itu akan direkodkan dalam IDQ. Ini dilakukan kerana uop (IDQ), penghantar (ROB) dan baris gilir tempahan kini menggunakan format uop yang dipendekkan tanpa medan indeks 6-bit (sudah tentu, untuk menjimatkan pergerakan uops). Diandaikan bahawa kes sedemikian jarang berlaku, dan oleh itu kelajuan tidak akan terjejas dengan ketara.

Kami akan memberitahu anda sejarah kemunculan mod penyekat gelung dalam penimbal ini di bawah, tetapi di sini kami hanya akan menunjukkan satu perincian kecil: peralihan ke permulaan gelung sebelum ini mengambil 1 kitaran jam tambahan, membentuk "gelembung" antara membaca penghujung dan permulaan gelung, tetapi kini ia hilang. Walau bagaimanapun, empat uops yang dibaca setiap kitaran jam tidak boleh termasuk yang terakhir dari lelaran semasa dan yang pertama dari yang seterusnya, jadi idealnya bilangan uops dalam gelung harus betul-betul dibahagikan dengan 4. Nah, kriteria untuk menyekatnya hampir tidak berubah:

- loop uops hendaklah dijana oleh tidak lebih daripada 8 bahagian 32-bait kod sumber;

- bahagian ini mesti dicache dalam L0m (dalam Nehalem, sudah tentu, dalam L1I);

- sehingga 8 peralihan tanpa syarat yang diramalkan sebagai dicetuskan dibenarkan (termasuk yang terakhir);

- panggilan dan pemulangan tidak dibenarkan;

- Akses tidak berpasangan kepada timbunan tidak dibenarkan (paling kerap apabila terdapat bilangan perintah PUSH dan POP yang tidak sama) - lebih lanjut mengenai perkara ini di bawah.

Enjin timbunan

Terdapat satu lagi mekanisme, operasi yang tidak kami pertimbangkan dalam artikel sebelumnya - penjejak penuding tindanan, terletak di hadapan IDQ. Ia muncul dalam Pentium M dan masih belum berubah. Intipatinya ialah pengubahsuaian penuding tindanan (daftar ESP/RSP untuk mod 32/64-bit) dengan arahan untuk bekerja dengannya (PUSH, POP, CALL dan RET) dilakukan oleh penambah berasingan, hasilnya disimpan dalam daftar khas dan dikembalikan kepada uop sebagai pemalar - bukannya mengubah suai penunjuk selepas setiap arahan, seperti yang diperlukan dan seperti yang berlaku dalam CPU Intel sebelum Pentium M.

Ini berlaku sehingga beberapa arahan mengakses penuding secara terus (dan dalam beberapa kes lain yang jarang berlaku) - enjin tindanan membandingkan penuding bayang kepada sifar dan, jika nilainya bukan sifar, memasukkan uop penyegerakan ke dalam aliran uops sebelum perintah memanggil penunjuk, menulis kepada penuding nilai semasa daripada daftar khas (dan daftar itu sendiri ditetapkan semula). Oleh kerana ini jarang diperlukan, kebanyakan panggilan ke timbunan yang hanya mengubah suai penunjuk secara tersirat menggunakannya. salinan bayangan, berubah serentak dengan operasi lain. Iaitu, dari sudut pandangan blok saluran paip, arahan sedemikian dikodkan oleh satu uop gabungan dan tidak berbeza daripada akses memori biasa, tanpa memerlukan pemprosesan dalam ALU.

Pembaca yang penuh perhatian (selamat tengah hari!) akan melihat sambungan: apabila menggelungkan baris gilir uop, panggilan tidak berpasangan ke timbunan tidak boleh diterima dengan tepat kerana enjin tindanan terletak dalam saluran paip sebelum ini IDQ - jika selepas lelaran seterusnya nilai penuding bayangan adalah bukan sifar, anda perlu memasukkan sinkromop ke dalam yang baharu, tetapi ini adalah mustahil dalam mod kitaran (mop hanya dibaca dari IDQ). Selain itu, enjin tindanan biasanya dimatikan untuk menjimatkan tenaga, seperti semua bahagian hadapan yang lain.

Kehidupan rahsia nops

Satu lagi perubahan telah dibuat pada tolok panjang, tetapi kes ini agak menonjol. Pertama, mari kita ingat apa itu dan mengapa ia diperlukan. Suatu ketika dahulu dalam seni bina x86 hanya terdapat memori 1-bait. Apabila perlu untuk mengalihkan kod lebih daripada 1 bait atau menggantikan arahan yang lebih panjang daripada 1 bait, nop hanya dimasukkan beberapa kali. Tetapi walaupun pada hakikatnya arahan ini tidak melakukan apa-apa, masa masih dibelanjakan untuk menyahkodnya, dan berkadaran dengan bilangan langkah. Untuk memastikan bahawa prestasi program "tampalan" tidak terjejas, nop boleh dipanjangkan. Walau bagaimanapun, dalam CPU tahun 90-an, kadar arahan penyahkodan dengan bilangan awalan di atas nilai tertentu (yang jauh lebih rendah daripada panjang arahan x86 maksimum yang dibenarkan iaitu 15 bait) menurun dengan mendadak. Di samping itu, khusus untuk nopa, awalan digunakan, sebagai peraturan, jenis yang sama, tetapi diulang berkali-kali, yang dibenarkan hanya sebagai pengecualian yang tidak diingini, merumitkan tolok panjang.

Untuk menyelesaikan masalah ini, bermula daripada pemproses Pentium Pro dan Athlon memahami "long nop" dengan bait modR/M untuk "secara rasmi" melanjutkan arahan menggunakan daftar dan alamat offset. Sememangnya, tiada operasi dengan memori dan daftar berlaku, tetapi apabila menentukan panjang, blok meter panjang yang sama digunakan seperti untuk arahan multibait biasa. Penggunaan nod panjang kini disyorkan secara rasmi oleh tutorial pengoptimuman perisian peringkat rendah daripada kedua-dua Intel dan AMD. By the way, SB predecoder telah mengurangkan separuh (dari 6 hingga 3 kitaran jam) penalti untuk awalan 66 dan 67, yang mengubah panjang pemalar dan alamat offset - tetapi, seperti dalam Nehalem, penalti tidak dikenakan pada arahan di mana awalan ini sebenarnya tidak mengubah panjang (contohnya, jika awalan 66 digunakan pada arahan tanpa operan segera) atau merupakan sebahagian daripada senarai suis (yang sering digunakan dalam kod vektor).

Panjang maksimum nod panjang yang diformat dengan betul tidak melebihi 9 bait untuk Intel dan 11 untuk AMD. Oleh itu, untuk menjajarkan sebanyak 16 atau 32 bait, mungkin masih terdapat beberapa nod. Walau bagaimanapun, oleh kerana arahan ini mudah, penyahkodan dan "pelaksanaan"nya tidak akan mengambil lebih banyak sumber daripada memproses arahan pengendalian yang paling mudah. Oleh itu, selama bertahun-tahun, ujian dengan kaki panjang telah menjadi kaedah standard untuk menentukan parameter bahagian hadapan penghantar, khususnya, tolok panjang dan penyahkod. Dan di sini Sandy Bridge memberikan kejutan yang sangat pelik: menguji prestasi program biasa tidak mendedahkan sebarang kelewatan atau kelembapan, tetapi pemeriksaan sintetik rutin parameter penyahkod secara tidak dijangka menunjukkan bahawa prestasinya adalah sama dengan satu arahan setiap kitaran jam! Pada masa yang sama, Intel tidak memberikan sebarang pemberitahuan rasmi mengenai perubahan radikal sedemikian dalam penyahkod.

Prosedur pengukuran berfungsi dengan sempurna walaupun pada Nehalem dan menunjukkan 4 yang betul. Anda boleh menyalahkan Turbo Boost 2.0 yang baru dan "terlalu" aktif, yang merosakkan bacaan jam yang diukur, tetapi untuk ujian ia dilumpuhkan. Terlalu panas dengan pendikitan memperlahankan kekerapan juga dikecualikan. Dan apabila sebabnya akhirnya ditemui, ia menjadi lebih pelik: ternyata nod panjang pada SB hanya diproses oleh penterjemah mudah pertama, walaupun nod 1-bait dengan sebarang bilangan awalan dan arahan "tidak bertindak" yang serupa (contohnya, menyalin daftar kepada dirinya sendiri) mudah diterima keempat-empatnya. Mengapa ini dilakukan tidak jelas, tetapi sekurang-kurangnya satu kelemahan penyelesaian teknikal sedemikian telah jelas menunjukkan dirinya: pasukan penyelidik kami mengambil masa sepuluh hari untuk mengetahui sebab kelambatan misteri penyahkod... Sebagai membalas dendam, kami minta peminat setia Kem Bertentangan untuk menghasilkan beberapa jenis teori konspirasi tentang rancangan licik syarikat I. tertentu untuk mengelirukan penyelidik pemproses yang naif. :)

Ngomong-ngomong, ternyata, penyiar No. 1 sudah "lebih sama" antara yang lain. Di Nehalem, perintah tatal kitaran (ROL dan ROR) dengan operan pemalar eksplisit juga dinyahkod hanya dalam penterjemah pertama, dan dalam kitaran yang sama perintah keempat dimatikan, jadi nilai IPC turun kepada 3. Nampaknya - mengapa membawa contoh yang jarang berlaku di sini? Tetapi tepat kerana tangkapan ini, untuk mencapai kelajuan puncak dengan algoritma pencincangan seperti SHA-1, susun atur arahan yang sangat tepat diperlukan, yang tidak dapat diatasi oleh penyusun. Dalam SB, arahan sedemikian hanya menjadi 2-mod, supaya, menggunakan penterjemah yang kompleks (yang sudah menjadi satu), mereka berkelakuan hampir tidak dapat dibezakan untuk CPU, tetapi lebih mudah diramal untuk manusia dan pengkompil. Dengan nops, sebaliknya berlaku. Atas cache

Matlamat dan pendahulunya

Bukan sia-sia kami memisahkan bab ini daripada perihalan bahagian hadapan yang lain - penambahan cache uop jelas menunjukkan laluan yang telah dipilih oleh Intel untuk semua pemprosesnya, bermula dengan Teras 2. Yang terakhir, buat kali pertama ( untuk Intel), menambah blok yang pada masa yang sama mencapai dua, nampaknya, Matlamat bercanggah: meningkatkan kelajuan dan menjimatkan tenaga. Kita bercakap tentang baris gilir arahan (IQ) antara predecoder dan decoder, yang kemudiannya menyimpan sehingga 18 arahan dengan panjang sehingga 64 bait secara keseluruhan. Sekiranya ia melicinkan perbezaan dalam kadar penyediaan dan penyahkodan arahan (seperti penampan biasa) - faedahnya akan menjadi kecil. Tetapi Intel berfikir untuk melampirkan unit LSD kecil pada IQ (tidak mungkin lelaki itu "menerima" apa-apa, mereka hanya mempunyai jenaka seperti itu) - Pengesan Strim Gelung, "pengesan aliran kitaran". Apabila kitaran yang sesuai dengan 18 arahan dikesan, LSD melumpuhkan semua peringkat sebelumnya (peramal, cache L1I dan pradekoder) dan mengarahkan arahan untuk kitaran ke penyahkod sehingga ia selesai atau sehingga peralihan dibuat melebihi hadnya (memanggil dan mengembalikan tidak boleh diterima). Ini menjimatkan tenaga dengan melumpuhkan blok terbiar buat sementara waktu dan meningkatkan prestasi disebabkan aliran terjamin 4 arahan/kitaran untuk penyahkod, walaupun ia "dilengkapi" dengan awalan yang paling menyusahkan.

Intel jelas menyukai idea ini, jadi litar dioptimumkan untuk Nehalem: IQ telah diduplikasi (untuk dua utas), dan antara penyahkod dan penghantar (iaitu, betul-betul di sempadan hadapan dan belakang) dua baris gilir IDQ sebanyak 28 uops setiap satu. telah diletakkan, dan Unit LSD telah dialihkan kepada mereka. Kini, apabila kitaran disekat, penyahkod juga dimatikan, dan prestasi telah meningkat, termasuk disebabkan oleh kemasukan yang dijamin bukan 4 arahan, tetapi 4 uops setiap kitaran jam, walaupun penjanaan mereka dijalankan dengan minimum (untuk Teras 2/i) pada tempo 2 mop/pukul. Peminat Kem Bertentangan yang marah, melihat sejenak dari hobi kegemaran mereka, akan segera memasukkan jepit rambut: jika LSD adalah perkara yang baik, mengapa ia tidak dibina ke dalam Atom? Dan muslihatnya adalah adil - mempunyai baris gilir 32 mod selepas penyahkod, Atom tidak tahu cara menyekat kitaran di dalamnya, yang akan sangat berguna untuk menjimatkan miliwatt berharga. Walau bagaimanapun, Intel tidak akan melepaskan idea itu dan menyediakan kemas kini untuk CPU baharu, dan sungguh hebat!

Nama dalaman rasmi untuk cache uop ialah DSB (penimbal strim nyahkod), walaupun ia tidak deskriptif seperti istilah DIC yang disyorkan (cache arahan dinyahkod). Anehnya, ia tidak menggantikan, tetapi melengkapkan baris gilir IDQ, yang kini disambungkan kepada penyahkod atau dengan cache up. Semasa ramalan cawangan seterusnya, alamat sasaran disemak secara serentak dalam arahan dan cache uop. Jika yang terakhir berfungsi, maka bacaan lanjut datang daripadanya, dan bahagian hadapan yang lain dimatikan. Inilah sebabnya mengapa cache uop adalah cache tahap 0 untuk uops, iaitu L0m.

Menariknya, idea ini boleh diteruskan dengan memanggil cache IDQ "tolak tahap pertama". :) Tetapi bukankah hierarki yang begitu kompleks dalam rangka bukan keseluruhan teras, tetapi hanya bahagian depan, berlebihan? Walaupun Intel, sebagai pengecualian, tidak memberi ruang, tetapi adakah sepasang IDQ akan membawa penjimatan tambahan yang ketara, memandangkan apabila ia berfungsi, hanya cache UOP kini dilumpuhkan, kerana bahagian hadapan yang lain (kecuali peramal ) sudah tidur? Dan anda juga tidak akan mendapat banyak peningkatan dalam kelajuan, kerana cache uop juga dikonfigurasikan untuk menjana 4 uops/kitaran. Nampaknya, jurutera Intel memutuskan bahawa permainan 3 peringkat bernilai lilin milliwatt.

Selain daripada menyimpan, cache uop mempercepatkan prestasi, termasuk dengan mengurangkan penalti untuk ramalan cawangan palsu: di Nehalem, apabila kod yang betul ditemui dalam L1I, penalti ialah 17 kitaran, dalam SB - 19, tetapi jika kod itu adalah ditemui dalam L0m, kemudian hanya 14. Selain itu, Ini adalah nombor maksimum: dalam kes peralihan yang diramalkan secara salah, penjadual masih perlu melancarkan dan melengkapkan uops sebelumnya dalam susunan program, dan pada masa ini L0m boleh menguruskan untuk mengepam yang betul uops supaya penjadual mempunyai masa untuk melancarkannya dengan segera selepas meninggalkan arahan sebelum peralihan. Di Nehalem, teknik ini berfungsi dengan IDQ dan tepi, tetapi dalam kes pertama kebarangkalian bahawa alamat sasaran yang betul juga akan berada di dalam kitaran 28-mop adalah sangat kecil, dan dalam kes kedua, kelambatan tepi dalam kebanyakan kes berlaku. tidak membenarkan mengurangkan kelewatan kepada sifar. SB mempunyai peluang yang lebih baik.

Peranti

Secara topologi, L0m terdiri daripada 32 8 baris (8- ). Setiap baris menyimpan 6 uops (dalam keseluruhan cache - 1536, iaitu “satu setengah kilomop”), dan cache boleh menulis dan membaca satu baris setiap kitaran jam. Peramal menghasilkan alamat blok 32-bait, dan saiz inilah yang berfungsi untuk L0m, jadi di bawah istilah "bahagian" akan bermakna blok kod 32-bait yang diselaraskan dan diramalkan sebagai boleh laku (dan bukan kod 16-bait , bagi penyahkod). Apabila penyahkodan, pengawal L0m menunggu bahagian diproses sehingga tamat atau sehingga peralihan pertama dicetuskan di dalamnya (sudah tentu, mungkin - di sini dan di bawah kami menganggap ramalan sentiasa betul), mengumpul uops pada masa yang sama seperti menghantar mereka ke belakang. Kemudian ia membetulkan titik masuk dan keluar bahagian, mengikut gelagat peralihan. Biasanya, titik masuk ialah alamat sasaran peralihan yang dicetuskan dalam bahagian sebelumnya (lebih tepat, 5 bit alamat yang lebih rendah), dan titik keluar ialah alamat sendiri mencetuskan peralihan dalam bahagian ini. DALAM sebagai jalan terakhir, jika tidak satu peralihan dicetuskan sama ada dalam bahagian sebelumnya atau semasa (iaitu, bahagian bukan sahaja dilaksanakan, tetapi juga disimpan dalam satu baris), maka kedua-duanya akan dilaksanakan secara keseluruhan - input kepada mereka akan dihidupkan mod sifar dan bait pertama bagi yang pertama yang sesuai sepenuhnya dalam bahagian perintah ini, dan outputnya adalah pada uop terakhir bagi perintah yang sesuai sepenuhnya dan bait awalnya.

Jika bahagian mengandungi lebih daripada 18 uops, ia tidak dicache. Ini menetapkan saiz arahan purata minimum (dalam ketulan) kepada 1.8 bait, yang tidak akan menjadi had yang serius dalam kebanyakan program. Anda boleh mengingati titik kedua sekatan IDQ - jika kitaran sesuai dengan bahagian, tetapi mengambil masa dari 19 hingga 28 uops, cache L0m mahupun baris gilir IDQ tidak akan membetulkannya, walaupun saiznya sesuai di mana-mana sahaja. Walau bagaimanapun, dalam kes ini, purata panjang arahan hendaklah 1.1–1.7 bait, yang sangat tidak mungkin untuk dua dozen perintah berturut-turut.

Kemungkinan besar, bahagian uops ditulis pada cache secara serentak, menduduki 1–3 baris bagi satu set, jadi untuk L0m salah satu prinsip utama operasi cache bersekutu set dilanggar: biasanya satu baris set dicetuskan. Teg sehingga tiga baris boleh menerima alamat bahagian yang sama dengan serta-merta, berbeza hanya dalam nombor siri. Apabila alamat yang diramalkan mencecah L0m, bacaan berlaku dengan cara yang sama - 1, 2 atau 3 laluan set yang dikehendaki dicetuskan. Benar, skim sedemikian penuh dengan kelemahan.

Jika program boleh laku dalam semua bahagian dinyahkodkan kepada 13–18 uops, yang akan mengambil 3 baris L0m untuk semua bahagian, perkara berikut akan didedahkan: jika set semasa sudah diduduki oleh dua bahagian 3 baris, dan yang ketiga sedang cuba menulis kepadanya (yang tidak akan mencukupi untuk satu baris), anda perlu menggantikan salah satu baris lama, dan mengambil kira ketersambungannya - kesemua 3 baris lama. Oleh itu, lebih daripada dua bahagian kod "berbutir halus" tidak boleh dimuatkan dalam set. Apabila menguji andaian ini dalam amalan, inilah yang berlaku: bahagian dengan pasukan yang besar, memerlukan kurang daripada 7 uops, telah dimasukkan ke dalam L0m bernombor 255 (atas sebab tertentu tidak mungkin untuk mengambil satu lagi), muat hampir 8 KB kod. Bahagian tengah (7–12 uops) menduduki kesemua 128 kemungkinan kedudukan (2 baris setiap satu), menyimpan cache tepat 4 KB. Nah, arahan kecil dimuatkan ke dalam 66 bahagian, iaitu dua lebih daripada nilai yang dijangkakan (2112 bait berbanding 2048), yang nampaknya dijelaskan oleh kesan sempadan kod ujian kami. Kekurangannya jelas - jika 256 baris 6-op boleh diisi sepenuhnya, ia akan mencukupi untuk 85 kembar tiga penuh dengan jumlah saiz kod 2720 bait.

Mungkin Intel tidak menjangkakan bahawa dalam sesetengah kod akan terdapat begitu banyak arahan pendek dan mudah sehingga lebih daripada 2/3 daripadanya akan berada dalam bahagian 3 baris, yang akan memaksa satu sama lain keluar dari L0m lebih awal daripada yang diperlukan. Dan walaupun kod sedemikian ditemui, memandangkan kesederhanaan penyahkodannya, blok yang tinggal di hadapan dengan mudah dapat mengatasi tugas membekalkan 4 uops/kitaran yang diperlukan untuk bahagian belakang (walaupun tanpa penjimatan yang dijanjikan dalam watt dan kitaran penalti untuk ramalan palsu). Adalah aneh bahawa jika L0m mempunyai 6 laluan, masalah itu tidak akan timbul. Intel memutuskan bahawa mempunyai saiz cache satu pertiga lebih besar dengan tepat disebabkan persekutuan adalah lebih penting...

Dimensi

Mari kita ingat bahawa idea untuk menyimpan sebilangan besar uops dan bukannya arahan x86 bukanlah perkara baru. Ia mula-mula muncul dalam Pentium 4 dalam bentuk cache jejak uop - urutan uops selepas pembukaan gelung. Selain itu, cache surih tidak menambah, tetapi menggantikan L1I yang hilang - arahan untuk penyahkod dibaca serta-merta daripada . Walaupun mengabaikan seni bina NetBurst, adalah munasabah untuk mengandaikan bahawa jurutera Intel menggunakan pengalaman lalu, walaupun tanpa membuka gelung dan peramal khusus untuk cache. Mari kita bandingkan penyelesaian lama dan baharu (CPU baharu dipanggil Core i 2 di sini, kerana bilangan hampir semua model dengan seni bina SB bermula dengan dua):

* - agaknya