Первые интегральные схемы

50-летию официальной даты посвящается

Б. Малашевич

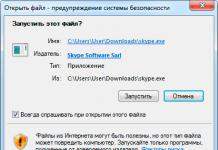

12 сентября 1958 года сотрудник фирмы Texas Instruments (TI) Джек Килби продемонстрировал руководству три странных прибора - склеенные пчелиным воском на стеклянной подложке устройства из двух кусочков кремния размером 11,1?1,6 мм (рис.1). Это были объёмные макеты – прототипы интегральной схемы (ИС) генератора, доказывающие возможность изготовления всех элементов схемы на основе одного полупроводникового материала. Эта дата отмечается в истории электроники как день рождения интегральных схем. Но так ли это?

Рис. 1. Макет первой ИС Дж. Килби. Фото с сайта http://www.computerhistory.org/semiconductor/timeline/1958-Miniaturized.html

К концу 1950-х годов технология сборки радиоэлектронной аппаратуры (РЭА) из дискретных элементов исчерпала свои возможности. Мир пришёл к острейшему кризису РЭА, требовались радикальные меры. К этому моменту в США и СССР уже были промышленно освоены интегральные технологии производства, как полупроводниковых приборов, так и толстоплёночных и тонкопленочных керамических плат, т. е. созрели предпосылки для выхода из этого кризиса путем создания многоэлементных стандартных изделий – интегральных схем.

К интегральным схемам (микросхемам, ИС) относятся электронные устройства различной сложности, в которых все однотипные элементы изготавливаются одновременно в едином технологическом цикле, т.е. по интегральной технологии. В отличие от печатных плат (в которых в едином цикле по интегральной технологии одновременно изготавливаются все соединительные проводники) в ИС аналогично формируются и резисторы, и конденсаторы, и (в полупроводниковых ИС) диоды и транзисторы. Кроме того, одновременно изготавливается много ИС, от десятков, до тысяч.

ИС разрабатываются и выпускаются промышленностью в виде серий, объединяющий ряд микросхем различного функционального назначения, предназначенных для совместного применения в электронной аппаратуре. ИС серии имеют стандартное конструктивное исполнение и единую систему электрических и иных характеристик. ИС поставляются производителем разным потребителям как самостоятельная товарная продукция, удовлетворяющая определенной системе стандартизованных требований. ИС относятся к неремонтируемым изделиям, при ремонте РЭА вышедшие из строя ИС заменяются.

Различают две основные группы ИС: гибридные и полупроводниковые.

В гибридных ИС (ГИС) на поверхности подложки микросхемы (как правило, из керамики) по интегральной технологии формируются все проводники и пассивные элементы. Активные элементы в виде бескорпусных диодов, транзисторов и кристаллов полупроводниковых ИС, устанавливаются на подложку индивидуально, вручную или автоматами.

В полупроводниковых ИС соединительные, пассивные и активные элементы формируются в едином технологическом цикле на поверхности полупроводникового материала (обычно кремния) с частичным вторжением в его объём методами диффузии. Одновременно на одной пластине полупроводника, в зависимости от сложности устройства и размеров его кристалла и пластины, изготавливается от нескольких десятков до нескольких тысяч ИС. Промышленность полупроводниковые ИС выпускает в стандартных корпусах, в виде отдельных кристаллов или в виде неразделенных пластин.

Явление миру гибридных (ГИС) и полупроводниковых ИС происходило по-разному. ГИС является продуктом эволюционного развития микромодулей и технологии монтажа на керамических платах. Поэтому появились они незаметно, общепринятой даты рождения ГИС и общепризнанного автора не существует. Полупроводниковые ИС были естественным и неизбежным результатом развития полупроводниковой техники, но потребовавшим генерации новых идей и создания новой технологии, у которых есть и свои даты рождения, и свои авторы. Первые гибридные и полупроводниковые ИС появились в СССР и США почти одновременно и независимо друг от друга.

Первые гибридные ИС

К гибридным относятся ИС, в производстве которых сочетается интегральная технология изготовления пассивных элементов с индивидуальной (ручной или автоматизированной) технологией установки и монтажа активных элементов.

Еще в конце 1940-х годов в фирме Centralab в США были разработаны основные принципы изготовления толстоплёночных печатных плат на керамической основе, развитые затем другими фирмами. В основу были положены технологии изготовления печатных плат и керамических конденсаторов. От печатных плат взяли интегральную технологию формирования топологии соединительных проводников – шелкографию. От конденсаторов – материал подложки (керамика, чаще ситал), а также материалы паст и термическую технологию их закрепления на подложке.

А в начале 1950-х годов в фирме RCA изобрели тонкоплёночную технологию: распыляя в вакууме различные материалы и осаждая их через маску на специальные подложки, научились на единой керамической подложке одновременно изготавливать множество миниатюрных плёночных соединительных проводников, резисторов и конденсаторов.

По сравнению с толстоплёночной, тонкоплёночная технология обеспечивала возможность более точного изготовления элементов топологии меньших размеров, но требовала более сложного и дорогостоящего оборудования. Устройства, изготавливаемые на керамических платах по толстоплёночной или тонкоплёночной технологии, получили название “гибридные схемы”. Гибридные схемы выпускались как комплектующие изделия собственного производства, их конструкция, размеры, функциональное назначение у каждого изготовителя были свои, на свободный рынок они не попадали, а потому мало известны.

Вторглись гибридные схемы и в микромодули. Сначала в них применялись дискретные пассивные и активные миниатюрные элементы, объединённые традиционным печатным монтажом. Технология сборки была сложной, с огромной долей ручного труда. Поэтому микромодули были весьма дорогими, их применение было ограничено бортовой аппаратурой. Затем применили толстопленочные миниатюрные керамические платки. Далее по толстопленочной технологии начали изготавливать резисторы. Но диоды и транзисторы использовались ещё дискретные, индивидуально корпусированные.

Гибридной интегральной схемой микромодуль стал в тот момент, когда в нём применили бескорпусные транзисторы и диоды и герметизировали конструкцию в общем корпусе. Это позволило значительно автоматизировать процесс их сборки, резко снизить цены и расширить сферу применения. По методу формирования пассивных элементов различают толстоплёночные и тонкоплёночные ГИС.

Первые ГИС в СССР

Первые ГИС (модули типа “Квант” позже получившие обозначение ИС серии 116) в СССР были разработаны в 1963 г. в НИИРЭ (позже НПО “Ленинец”, Ленинград) и в том же году его опытный завод начал их серийное производство. В этих ГИС в качестве активных элементов использовались полупроводниковые ИС “Р12- 2” , разработанные в 1962 г. Рижским заводом полупроводниковых приборов. В связи с неразрывностью историй создания этих ИС и их характеристик, мы рассмотрим их вместе в разделе, посвященном Р12-2.

Бесспорно, модули “Квант” были первыми в мире ГИС с двухуровневой интеграцией – в качестве активных элементов в них использовались не дискретные бескорпусные транзисторы, а полупроводниковые ИС. Вполне вероятно, что они вообще были и первыми в мире ГИС – конструктивно и функционально законченными многоэлементными изделиями, поставляемыми потребителю как самостоятельная товарная продукция. Самым ранним из выявленных автором зарубежных подобных изделий являются ниже описанные SLT -модули корпорации IBM , но они были анонсированы в следующем, 1964 г.

Первые ГИС в США

Появление толстоплёночных ГИС, как основной элементной базы новой ЭВМ IBM System /360, впервые было анонсировано корпорации IBM в 1964 г. Похоже, что это было первое применение ГИС за пределами СССР, более ранних примеров автору обнаружить не удалось.

Уже известные в то время в кругах специалистов полупроводниковые ИС серий “Micrologic” фирмы Fairchild и " SN -51" фирмы TI (о них мы скажем ниже) были ещё недоступно редки и непозволительно дороги для коммерческого применения, каким было построение большой ЭВМ. Поэтому корпорация IBM , взяв за основу конструкцию плоского микромодуля, разработала свою серию толстоплёночных ГИС, анонсированную под общим названием (в отличие от “микромодулей”) – “ SLT -модули” (Solid Logic Technology – технология цельной логики. Обычно слово “s olid ” переводят на русский язык как “твёрдый”, что абсолютно нелогично. Действительно, термин “ SLT -модули” был введен IBM как противопоставление термину “микромодуль” и должен отражать их отличие. Но оба модуля “твёрдые”, т. е. этот перевод не годится. У слова “ solid ” есть и другие значения – “сплошной”, “целый”, которые удачно подчеркивают различие “ SLT -модулей” и “микромодулей” – SLT -модули неделимы, неремонтопригодны, т. е. “целые”. Поэтому мы и использовали не общепринятый перевод на русский язык: Solid Logic Technology – технология цельной логики).

SLT -модуль представлял собой квадратную керамическую толстоплёночную микроплатку полудюймового размера с впрессованными вертикальными штыревыми выводами. На её поверхность методом шелкографии наносились (согласно схеме реализуемого устройства) соединительные проводники и резисторы, и устанавливались бескорпусные транзисторы. Конденсаторы, при необходимости, устанавливались рядом с SLT -модулем на плате устройства. При внешней почти идентичности (микромодули несколько повыше, рис. 2.) SLT -модули от плоских микромодулей отличались более высокой плотностью компоновки элементов, низким энергопотреблением, высоким быстродействием и высокой надёжностью. Кроме того, SLT -технология достаточно легко автоматизировалась, следовательно их можно было выпускать в огромных количествах при достаточно низкой для применения в коммерческой аппаратуре стоимости. Именно это IBM и было нужно. Фирма построила для производства SLT -модулей автоматизированный завод в East Fishkill близ Нью-Йорка, который выпускал их миллионными тиражами.

Рис. 2. Микромодуль СССР и SLT-модуль ф. IBM. Фото STL с сайта http://infolab.stanford.edu/pub/voy/museum/pictures/display/3-1.htm

Вслед за IBM ГИС начали выпускать и другие фирмы, для которых ГИС стала товарной продукцией. Типовая конструкция плоских микромодулей и SLT -модулей корпорации IBM стала одним из стандартов для гибридных ИС.

Первые полупроводниковые ИС

К концу 1950-х годов промышленность имела все возможности для производства дешёвых элементов электронной аппаратуры. Но если транзисторы или диоды изготовлялись из германия и кремния, то резисторы и конденсаторы делали из других материалов. Многие тогда полагали, что при создании гибридных схем не будет проблем в сборке этих элементов, изготовленных по отдельности. А если удастся изготовить все элементы типового размера и формы и тем самым автоматизировать процесс сборки, то стоимость аппаратуры будет значительно снижена. На основании таких рассуждений сторонники гибридной технологии рассматривали её как генеральное направление развития микроэлектроники.

Но не все разделяли это мнение. Дело в том, что уже созданные к тому периоду меза-транзисторы и, особенно, планарные транзисторы, были приспособлены для групповой обработки, при которой ряд операций по изготовлению многих транзисторов на одной пластине-подложке осуществлялись одновременно. Т. е. на одной полупроводниковой пластине изготавливалось сразу множество транзисторов. Затем пластина разрезалась на отдельные транзисторы, которые размещались в индивидуальные корпуса. А затем изготовитель аппаратуры объединял транзисторы на одной печатной плате. Нашлись люди, которым такой подход показался нелепым – зачем разъединять транзисторы, а потом снова объединять их. Нельзя ли их объединить сразу на полупроводниковой пластине? При этом избавиться от нескольких сложных и дорогостоящих операций! Эти люди и придумали полупроводниковые ИС.

Идея предельно проста и совершенно очевидна. Но, как часто бывает, только после того, как кто-то первым её огласил и доказал. Именно доказал, просто огласить часто, как и в данном случае, бывает недостаточно. Идея ИС была оглашена еще в 1952 г., до появления групповых методов изготовления полупроводниковых приборов. На ежегодной конференции по электронным компонентам, проходившей в Вашингтоне, сотрудник Британского королевского радиолокационного управления в Малверне Джеффри Даммер представил доклад о надёжности элементов радиолокационной аппаратуры. В докладе он сделал пророческое утверждение: “ С появлением транзистора и работ в области полупроводниковой техники вообще можно себе представить электронное оборудование в виде твердого блока, не содержащего соединительных проводов. Блок может состоять из слоев изолирующих, проводящих, выпрямляющих и усиливающих материалов, в которых определенные участки вырезаны таким образом, чтобы они могли непосредственно выполнять электрические функции” . Но этот прогноз остался специалистами незамеченным. Вспомнили о нём только после появления первых полупроводниковых ИС, т. е. после практического доказательства давно оглашенной идеи. Кто-то должен был первым вновь сформулировать и реализовать идею полупроводниковой ИС.

Как и в случае с транзистором, у общепризнанных создателей полупроводниковых ИС были более или менее удачливые предшественники. Попытку реализовать свою идею в 1956 г. предпринял сам Даммер, но потерпел неудачу. В 1953 г. Харвик Джонсон из фирмы RCA получил патент на однокристальный генератор, а в 1958 г. совместно с Торкелом Валлмарком анонсировал концепцию “полупроводникового интегрального устройства”. В 1956 году сотрудник фирмы Bell Labs Росс изготовил схему двоичного счётчика на основе n-p-n-p структур в едином монокристалле. В 1957 г. Ясуро Тару из японской фирмы MITI получил патент на соединение различных транзисторов в одном кристалле. Но все эти и другие им подобные разработки имели частный характер, не были доведены до производства и не стали основой для развития интегральной электроники. Развитию ИС в промышленном производстве способствовали только три проекта.

Удачливыми оказались уже упомянутый Джек Килби из Texas Instruments (TI), Роберт Нойс из Fairchild (оба из США) и Юрий Валентинович Осокин из КБ Рижского завода полупроводниковых приборов (СССР). Американцы создали экспериментальные образцы интегральных схем: Дж. Килби – макет ИС генератора (1958 г.), а затем триггер на меза-транзисторах (1961 г.), Р. Нойс – триггер по планарной технологии (1961 г.), а Ю. Осокин – сразу пошедшую в серийное производство логическую ИС “2НЕ-ИЛИ” на германии (1962 г.). Серийное производство ИС эти фирмы начали почти одновременно, в 1962 г.

Первые полупроводниковые ИС в США

ИС Джека Килби. Серия ИС “ SN - 51”

В 1958 году Дж. Килби (пионер применения транзисторов в слуховых аппаратах) перешёл в фирму Texas Instruments. Новичка Килби, как схемотехника, “бросили” на усовершенствование микромодульной начинки ракет путём создания альтернативы микромодулям. Рассматривался вариант сборки блоков из деталей стандартной формы, подобный сборке игрушечных моделей из фигурок LEGO. О днако Килби увлекло иное. Решающую роль сыграл эффект “свежего взгляда”: во-первых, он сразу констатировал, что микромодули – тупик, а во-вторых, налюбовавшись меза-структурами, пришёл к мысли, что схему нужно (и можно) реализовать из одного материала – полупроводника. Килби знал об идее Даммера и его неудачной попытке её реализации в 1956 г. Проанализировав, он понял причину неудачи и нашел способ её преодоления. “ Моя заслуга в том, что взяв эту идею, я превратил её в реальность ” , сказал Дж. Килби позже в своей нобелевской речи.

Не заработав ещё права на отпуск, он без помех трудился в лаборатории, пока все отдыхали. 24 июля 1958 года Килби сформулировал в лабораторном журнале концепцию, получившую название “Идея монолита” (Monolithic Idea). Её суть заключалась в том, что “. ..элементы схемы, такие как резисторы, конденсаторы, распределенные конденсаторы и транзисторы, могут быть интегрированы в одну микросхему - при условии, что они будут выполнены из одного материала... В конструкции триггерной схемы все элементы должны изготавливаться из кремния, причём резисторы будут использовать объёмное сопротивление кремния, а конденсаторы - ёмкости p-n-переходов ” . “ Идея монолита” встретила снисходительно-ироничное отношение со стороны руководства Texas Instruments, потребовавшего доказательств возможности изготовления транзисторов, резисторов и конденсаторов из полупроводника и работоспособности собранной из таких элементов схемы.

В сентябре 1958 г. Килби реализовал свою идею – сделал генератор из склеенных пчелиным воском на стеклянной подложке двух кусочков германия размером 11,1 х 1,6 мм, содержащих диффузионные области двух типов (рис. 1). Эти области и имевшиеся контакты он использовал для создания схемы генератора, соединяя элементы тонкими золотыми проволочками диаметром 100 мкм путём термокомпрессионной сварки. Из одной области создавался мезатранзистор, из другой – RC-цепочка. Собранные три генератора были продемонстрированы руководству компании. При подключении питания они заработали на частоте 1,3 МГц. Это случилось 12 сентября 1958 года. Через неделю аналогичным образом Килби изготовил усилитель. Но это ещё не были интегральные структуры, это были объёмные макеты полупроводниковых ИС, доказывающие идею изготовления всех элементов схемы из одного материала – полупроводника.

Рис. 3. Триггер Type 502 Дж. Килби. Фото с сайта http://www.computerhistory.org/semiconductor/timeline/1958-Miniaturized.html

Первой действительно интегральной схемой Килби, выполненной в одном кусочке монолитного германия, оказалась экспериментальная ИС триггера “ Type 502” (рис. 3). В ней были использованы и объёмное сопротивление германия, и ёмкость p-n-перехода. Её презентация состоялась в марте 1959 года. Небольшое количество таких ИС было изготовлено в лабораторных условиях и продавалось в узком кругу по цене 450$. ИС содержала шесть элементов: четыре меза-транзистора и два резистора, размещённых на кремниевой пластине диаметром 1 см. Но ИС Килби имела серьёзный недостаток – меза-транзисторы, которые в виде микроскопических “активных” столбиков возвышались над остальной, “пассивной” частью кристалла. Соединение меза-столбиков друг с другом в ИС Килби осуществлялось развариванием тонких золотых проволочек – ненавистная всем “волосатая технология”. Стало ясно, что при таких межсоединениях микросхему с большим количеством элементов не сделать – проволочная паутина разорвется или перезамкнется. Да и германий в то время уже рассматривался как материал не перспективный. Прорыв не состоялся.

К этому времени в фирме Fairchild была разработана планарная кремниевая технология. Учитывая все это, Texas Instruments пришлось отложить всё сделанное Килби в сторонку и приступить, уже без Килби, к разработке серии ИС на основе планарной кремниевой технологии. В октябре 1961 г. фирма анонсировала создание серии ИС типа SN -51, а с 1962 г. начала их серийное производство и поставки в интересах Минобороны США и НАСА.

ИС Роберта Нойса. Серия ИС “ Micrologic ”

В 1957 г. по ряду причин от У. Шокли, изобретателя плоскостного транзистора, ушла группа в восемь молодых инженеров, которые хотели попробовать реализовать собственные идеи. “Восьмерка предателей”, как их называл Шокли, лидерами которых были Р. Нойс и Г. Мур, основала фирму Fairchild Semiconductor (“прекрасное дитя”) . Возглавил фирму Роберт Нойс, было ему тогда 23 года.

В конце 1958 года физик Д. Хорни, работавший в компании Fairchild Semiconductor, разработал планарную технологию изготовления транзисторов. А физик чешского происхождения Курт Леховек, работавший в Sprague Electric, разработал технику использования обратно включенного n - p перехода для электрической изоляции компонентов. В 1959 году Роберт Нойс, прослышав про макет ИС Килби, решил попробовать создать интегральную схему, комбинируя процессы, предложенные Хорни и Леховеком. А вместо “волосатой технологии” межсоединений Нойс предложил избирательное напыление тонкого слоя металла поверх изолированных двуокисью кремния полупроводниковых структур с подключением к контактам элементов через отверстия, оставленные в изолирующем слое. Это позволило “погрузить” активные элементы в тело полупроводника, изолировав их окислом кремния, а затем соединить эти элементы напылёнными дорожками алюминия или золота, которые создаются при помощи процессов фотолитографии, металлизации и травления на последней стадии изготовления изделия. Таким образом, был получен действительно “монолитный” вариант объединения компонентов в единую схему, а новая технология получила название “планарной”. Но сначала нужно было идею проверить.

Рис. 4. Экспериментальный триггер Р. Нойса. Фото с сайта http://www.computerhistory.org/semiconductor/timeline/1960-FirstIC.html

Рис. 5. Фотография ИС Micrologic в журнале Life. Фото с сайта http://www.computerhistory.org/semiconductor/timeline/1960-FirstIC.html

В августе 1959 г. Р. Нойс поручил Джою Ласту проработать вариант ИС на планарной технологии. Сначала, как и Килби, изготовили макет триггера на нескольких кристаллах кремния, на которых было сделано 4 транзистора и 5 резисторов. Затем 26 мая 1960 г. изготовили первый однокристальный триггер. Для изоляции элементов в нём с обратной стороны кремниевой пластины протравливали глубокие канавки, заполняемые эпоксидной смолой. 27 сентября 1960 г. изготовили третий вариант триггера (рис. 4), в котором элементы изолировались обратно включенным p - n переходом.

Фирма Fairchild Semiconductor до этого времени занималась только транзисторами, схемотехников для создания полупроводниковых ИС у неё не было. Поэтому в качестве разработчика схем был приглашен Роберт Норман из фирмы Sperry Gyroscope . Норман был знаком с резисторно-транзисторной логикой, которую фирма с его подачи и выбрала в качестве основы своей будущей серии ИС “Micrologic”, нашедшей своё первое применение в аппаратуре ракеты “Минитмен”. В марте 1961 г. Fairchild анонсировала первую опытную ИС этой серии (F -триггер, содержащий шесть элементов: четыре биполярных транзистора и два резистора, размещённых на пластине диаметром 1 см.) с опубликованием её фотографии (рис. 5) в журнале Life (от 10 марта 1961 г.). Ещё 5 ИС были анонсированы в октябре. А с начала 1962 г. Fairchild развернула серийное производство ИС и поставки их также в интересах Минобороны США и НАСА.

Килби и Нойсу пришлось выслуш ать немало критических замечаний по поводу своих новаций. Считалось, что практический выход годных интегральных схем будет очень низким. Понятно, что он должен быть ниже, чем у транзисторов (поскольку содержит несколько транзисторов), у которых он тогда был не выше 15%. Во-вторых, многие полагали, что в интегральных схемах используются неподходящие материалы, поскольку резисторы и конденсаторы делались тогда отнюдь не из полупроводников. В третьих, многие не могли воспринять мысль неремонтопригодности ИС. Им казалось кощунственным выбрасывать изделие, в котором вышел из строя только один из многих элементов. Все сомнения постепенно были отброшены, когда интегральные схемы были успешно использованы в военных и космических программах США.

Один из основателей фирмы Fairchild Semiconductor Г. Мур сформулировал основной закон развития кремниевой микроэлектроники, согласно которому число транзисторов в кристалле интегральной схемы удваивалось каждый год. Этот закон, названный “закон Мура”, довольно чётко действовал в течение первых 15 лет (начиная с 1959 г.), а затем такое удвоение происходило приблизительно за полтора года.

Далее индустрия ИС в США начала развиваться стремительными темпами. В США начался лавинообразный процесс возникновения предприятий, ориентированных исключительно “под планар”, иногда доходило до того, что регистрировались по десятку фирм в неделю. Стремясь к ветеранам (фирмам У. Шокли и Р. Нойса), а также благодаря налоговым льготам и сервису, представляемому Стенфордским университетом, “новички” кучковались главным образом в долине Санта-Клара (Калифорния). Поэтому неудивительно, что в 1971 г. в обиход с легкой руки журналиста-популяризатора технических новинок Дона Хофлера в обращение вошел романтически-техногенный образ “Кремниевой долины” (Silicon Valley), навсегда ставший синонимом Мекки полупроводниковой технологической революции. Кстати, в той местности действительно имеется славившаяся ранее многочисленными абрикосовыми, вишневыми и сливовыми садами долина, имевшая до появления в ней фирмы Шокли другое, более приятное название – Долина сердечного удовольствия (the Valley of Heart"s Delight), ныне, к сожалению, почти забытое.

В 1962 год в США началось серийное производство интегральных схем, хотя их объём поставок заказчикам и составил всего лишь несколько тысяч. Сильнейшим стимулом для развития приборостроительной и электронной промышленности на новой основе явилась ракетно-космическая техника. США не имели тогда таких же мощных межконтинентальных баллистических ракет, как советские, и для увеличения заряда были вынуждены пойти на максимальное сокращение массы носителя, в том числе систем управления, за счёт внедрения последних достижений электронной технологии. Фирмы Texas Instrument и Fairchild Semiconductor заключили крупные контракты на разработку и изготовление интегральных схем с министерством обороны США и с НАСА.

Первые полупроводниковые ИС в СССР

К концу 1950-х годов советская промышленность нуждалась в полупроводниковых диодах и транзисторах настолько, что потребовались радикальные меры. В 1959 году были основаны заводы полупроводниковых приборов в Александрове, Брянске, Воронеже, Риге и др. В январе 1961 года ЦК КПСС и СМ СССР приняли очередное Постановление “О развитии полупроводниковой промышленности”, в котором предусматривалось строительство заводов и НИИ в Киеве, Минске, Ереване, Нальчике и других городах.

Нас будет интересовать один их новых заводов – выше упомянутый Рижский завод полупроводниковых приборов (РЗПП, он несколько раз менял свои названия, для простоты мы используем наиболее известное, действующее и ныне). В качестве стартовой площадки новому заводу выделили строящееся здание кооперативного техникума площадью 5300 м 2 , одновременно началось строительство специального здания. К февралю 1960 года на заводе было уже создано 32 службы, 11 лабораторий и опытное производство, приступившее в апреле к подготовке производства первых приборов. На заводе уже работало 350 человек, 260 из которых в течение года направлялись на учёбу в московский НИИ-35 (позже НИИ “Пульсар”) и на ленинградский завод “Светлана”. А к концу 1960 года численность работающих достигла 1900 человек. Первоначально технологические линии размещались в перестроенном спортивном зале корпуса кооперативного техникума, а лаборатории ОКБ – в бывших учебных аудиториях. Первые приборы (сплавно-диффузионные и конверсионные германиевые транзисторы П-401, П-403, П-601 и П-602 разработки НИИ-35) завод выпустил через 9 месяцев после подписания приказа о его создания, в марте 1960 года. А к концу июля изготовил первую тысячу транзисторов П-401. Затем освоил в производстве многие другие транзисторы и диоды. В июне 1961 года завершилось строительство специального корпуса, в котором началось массовое производство полупроводниковых приборов.

С 1961 года завод приступил к самостоятельным технологическим и опытно-конструкторским работам, в том числе – по механизации и автоматизации производства транзисторов на основе фотолитографии. Для этого был разработан первый отечественный фотоповторитель (фотоштамп) – установка совмещения и контактной фотопечати (разработчик А.С. Готман). Большую помощь в финансировании и изготовлении уникального оборудования оказывали предприятия Минрадиопрома, в том числе КБ-1 (позже НПО “Алмаз”, Москва) и НИИРЭ. Тогда наиболее активные разработчики малогабаритной радиоаппаратуры, не имея своей технологической полупроводниковой базы, искали пути творческого взаимодействия с недавно созданными полупроводниковыми заводами.

На РЗПП проводились активные работы по автоматизации производства германиевых транзисторов типа П401 и П403 на основе создаваемой заводом технологической линии “Аусма”. Её главный конструктор (ГК) А.С. Готман предложил делать на поверхности германия токоведущие дорожки от электродов транзистора к периферии кристалла, чтобы проще разваривать выводы транзистора в корпусе. Но главное, эти дорожки можно было использовать в качестве внешних выводов транзистора при бескорпусной их сборке на платы (содержащие соединительные и пассивные элементы), припаивая их непосредственно к соответствующим контактным площадкам (фактически предлагалась технология создания гибридных ИС). Предлагаемый метод, при котором токоведущие дорожки кристалла как бы целуются с контактными площадками платы, получил оригинальное название – “поцелуйная технология”. Но из-за ряда оказавшихся тогда неразрешимыми технологических проблем, в основном связанных с проблемами точности получения контактов на печатной плате, практически реализовать “поцелуйную технологию” не удалось. Через несколько лет подобная идея была реализована в США и СССР и нашла широкое применение в так называемых “шариковых выводах” и в технологии “чип-на-плату”.

Тем не менее, аппаратурные предприятия, сотрудничающие с РЗПП, в том числе НИИРЭ, надеялись на “поцелуйную технологию” и планировали её применение. Весной 1962 года, когда стало понятно, что её реализация откладывается на неопределённый срок, главный инженер НИИРЭ В.И. Смирнов попросил директора РЗПП С.А. Бергмана найти другой путь реализации многоэлементной схемы типа 2НЕ-ИЛИ, универсальной для построения цифровых устройств.

Рис. 7. Эквивалентная схема ИС Р12-2 (1ЛБ021) . Рисунок из проспекта ИС от 1965 г.

Первая ИС и ГИС Юрия Осокина. Твердая схема Р12-2 (ИС серий 102 и 116 )

Директор РЗПП поручил эту задачу молодому инженеру Юрию Валентиновичу Осокину . Организовали отдел в составе технологической лаборатории, лаборатории разработки и изготовления фотошаблонов, измерительной лаборатории и опытно-производственной линейки. В то время в РЗПП была поставлена технология изготовления германиевых диодов и транзисторов, ее и взяли за основу новой разработки. И уже осенью 1962 года были получены первые опытные образцы германиевой твёрдой схемы 2НЕ-ИЛИ (поскольку термина ИС тогда не существовало, из уважения к делам тех дней сохраним название “твёрдая схема” – ТС), получившей заводское обозначение “Р12- 2” . Сохранился рекламный буклет 1965 г. на Р12-2 (рис. 6), информацией и иллюстрациями из которого мы воспользуемся. ТС Р12-2 содержала два германиевых p - n - p -транзистора (модифицированные транзисторы типа П401 и П403) с общей нагрузкой в виде распределённого германиевого резистора р-типа (рис.7).

Рис. 8. Структура ИС Р12-2. Рисунок из проспекта ИС от 1965 г.

Рис. 9. Габаритный чертеж ТС Р12-2. Рисунок из проспекта ИС от 1965 г.

Внешние выводы формируются термокомпрессионной сваркой между германиевыми областями ТС структуры и золотом выводных проводников. Это обеспечивает устойчивую работу схем при внешних воздействиях в условиях тропиков и морского тумана, что особенно важно для работы в военно-морских квазиэлектронных АТС, выпускаемых рижским заводом ВЭФ, так же заинтересовавшимся этой разработкой.

Конструктивно ТС Р12-2 (и последующая за ней Р12-5) были выполнены в виде “таблетки” (рис.9) из круглой металлической чашечки диаметром 3 мм и высотой 0,8 мм. В неё размещался кристалл ТС и заливался полимерным компаундом, из которого выходили короткие внешние концы выводов из мягкой золотой проволоки диаметром 50 мкм, приваренные к кристаллу. Масса Р12-2 не превышала 25 мг. В таком исполнении ТС были устойчивы к воздействию относительной влажности 80% при температуре окружающей среды 40 ° С и к циклическим изменениям температуры от -60 ° до 60 ° С.

К концу 1962 года опытное производство РЗПП выпустило около 5 тыс. ТС Р12-2, а в 1963 году их было сделано несколько десятков тысяч. Таким образом, 1962 год стал годом рождения микроэлектронной промышленности в США и СССР.

Рис. 10. Группы ТС Р12-2

Рис. 11. Основные электрические характеристики Р12-2

Полупроводниковая технология тогда находилась на стадии становления и ещё не гарантировала строгой повторяемости параметров. Поэтому работоспособные приборы рассортировывали по группам параметров (это часто делают и в наше время). Так же поступили и рижане, установив 8 типономиналов ТС Р12-2 (рис. 10). Все другие электрические и иные характеристики у всех типономиналов одинаковы (рис. 11).

Выпуск ТС Р12-2 начался одновременно с проведением ОКР “Твердость”, завершившимся в 1964 году (ГК Ю.В. Осокин). В рамках этой работы была разработана усовершенствованная групповая технология серийного производства германиевых ТС на основе фотолитографии и гальванического осаждения сплавов через фотомаску. Её основные технические решения зарегистрированы как изобретение Осокина Ю.В. и Михаловича Д.Л. (А.С. №36845). В издававшемся с грифом “секретно” журнале “Спецрадиоэлектроника” вышло несколько статей Ю.В. Осокина в соавторстве со специалистами КБ-1 И.В. Ничего, Г.Г. Смолко и Ю.Е. Наумовым с описанием конструкции и характеристик ТС Р12-2 (и последовавшей за ней ТС Р12-5).

Конструкция Р12-2 была всем хороша, кроме одного – потребители не умели применять такие маленькие изделия с тончайшими выводами. Ни технологии, ни оборудования для этого у аппаратурных фирм, как правило, не было. За всё время выпуска Р12-2 и Р12-5 их применение освоили НИИРЭ, Жигулевский радиозавод Минрадиопрома, ВЭФ, НИИП (с 1978 года НПО “Радиоприбор”) и немногие другие предприятия. Понимая проблему, разработчики ТС совместно с НИИРЭ сразу же продумали второй уровень конструкции, который одновременно увеличил плотность компоновки аппаратуры.

Рис. 12. Модуль из 4 ТС Р12-2

В1963 г. в НИИРЭ в рамках ОКР “Квант” (ГК А.Н. Пелипенко, при участии Е.М. Ляховича) была разработана конструкция модуля, в котором объединялось четыре ТС Р12-2 (рис.12). На микроплату из тонкого стеклотекстолита размещали от двух до четырёх ТС Р12-2 (в корпусе), реализующих в совокупности определённый функциональный узел. На плату впрессовывали до 17 выводов (число менялось для конкретного модуля) длиной 4 мм. Микроплату помещали в металлическую штампованную чашечку размером 21,6 ? 6,6 мм и глубиной 3,1 мм и заливали полимерным компаундом. В результате получилась гибридная интегральная схема (ГИС) с двойной герметизацией элементов. И, как мы уже говорили, это была первая в мире ГИС с двухуровневой интеграцией, а, возможно, вообще первая ГИС. Было разработано восемь типов модулей с общим названием “Квант”, выполнявших различные логические функции. В составе таких модулей ТС Р12-2 сохраняли работоспособность при воздействии постоянных ускорений до 150 g и вибрационных нагрузок в диапазоне частот 5–2000 Гц с ускорением до 15 g .

Модули “Квант” сначала выпускало опытное производство НИИРЭ, а затем их передали на Жигулевский радиозавод Минрадиопрома СССР, поставлявший их различным потребителям, в том числе заводу ВЭФ.

ТС Р12-2 и модули “Квант” на их основе хорошо зарекомендовали себя и широко применялись. В 1968 году вышел стандарт, устанавливающий единую в стране систему обозначений интегральных схем, а в 1969 году – Общие технические условия на полупроводниковые (НП0.073.004ТУ) и гибридные (НП0.073.003ТУ) ИС с единой системой требований. В соответствии с этими требованиями в Центральном бюро по применению интегральных схем (ЦБПИМС, позже ЦКБ “Дейтон”, Зеленоград) 6 февраля 1969 года на ТС были утверждены новые технические условия ЩТ3.369.001-1ТУ. При этом в обозначении изделия впервые появился термин “интегральная схема” серии 102. ТС Р12-2 стали называться ИС: 1ЛБ021В, 1ЛБ021Г, 1ЛБ021Ж, 1ЛБ021И. Фактически это была одна ИС, рассортированная на четыре группы по выходному напряжению и нагрузочной способности.

Рис. 13. ИС серии 116 и 117

А 19 сентября 1970 года в ЦБПИМС были утверждены технические условия АВ0.308.014ТУ на модули “Квант”, получившие обозначение ИС серии 116 (рис.13). В состав серии входило девять ИС: 1ХЛ161, 1ХЛ162 и 1ХЛ163 – многофункциональные цифровые схемы; 1ЛЕ161 и 1ЛЕ162 – два и четыре логических элемента 2НЕ-ИЛИ; 1ТР161 и 1ТР1162 – один и два триггера; 1УП161 – усилитель мощности, а также 1ЛП161 – логический элемент "запрет" на 4 входа и 4 выхода. Каждая их этих ИС имела от четырёх до семи вариантов исполнения, отличающихся напряжением выходных сигналов и нагрузочной способностью, всего было 58 типономиналов ИС. Исполнения маркировались буквой после цифровой части обозначения ИС, например, 1ХЛ161Ж. В дальнейшем номенклатура модулей расширялась. ИС серии 116 фактически были гибридными, но по просьбе РЗПП были маркированы как полупроводниковые (первая цифра в обозначении – “ 1” , у гибридных должно быть “ 2”).

В 1972 году совместным решением Минэлектронпрома и Минрадиопрома производство модулей было передано из Жигулевского радиозавода на РЗПП. Это исключило транспортировку ИС серии 102 на дальние расстояния, поэтому отказались от герметизации кристалла каждой ИС. В результате упростилась конструкция ИС и 102-й, и 116-й серий: отпала необходимость корпусировать ИС серии 102 в металлическую чашечку с заливкой компаундом. Бескорпусные ИС серии 102 в технологической таре поступали в соседний цех на сборку ИС серии 116, монтировались непосредственно на их микроплату и герметизировались в корпусе модуля.

В середине 1970-х годов вышел новый стандарт на систему обозначений ИС. После этого, например, ИС 1ЛБ021В получила обозначение 102ЛБ1В.

Вторая ИС и ГИС Юрия Осокина. Твердая схема Р12-5 (ИС серий 103 и 117 )

К началу 1963 года в результате серьёзных работ по разработке высокочастотных n - p - n транзисторов коллектив Ю.В. Осокина накопил большой опыт работы с p -слоями на исходной n -германиевой пластине. Это и наличие всех необходимых технологических компонентов позволило Осокину в 1963 году приступить к разработке новой технологии и конструкции более быстродействующего варианта ТС. В 1964 году по заказу НИИРЭ была завершена разработка ТС Р12-5 и модулей на её основе. По её результатам в 1965 году была открыта ОКР “Паланга” (ГК Ю.В. Осокин, его заместитель – Д.Л. Михалович, завершена в 1966 году). Разрабатывались модули на основе Р12-5 в рамках той же ОКР “Квант”, что и модули на Р12-2. Одновременно с техническими условиями на серии 102 и 116 были утверждены технические условия ЩТ3.369.002-2ТУ на ИС серии 103 (Р12-5) и АВ0.308.016ТУ на ИС серии 117 (модули на основе ИС серии 103). Номенклатура типов и типономиналов ТС Р12-2, модулей на них и серий ИС 102 и 116 была идентична номенклатуре ТС Р12-5 и ИС серий 103 и 117, соответственно. Отличались они только быстродействием и технологией изготовления кристалла ИС. Типовое время задержки распространения сигнала серии 117 составило 55 нс против 200 нс в серии 116.

Конструктивно ТС Р12-5 представляла собой четырёхслойную полупроводниковую структуру (рис.14), где подложка n -типа и эммитеры p + -типа подсоединялись к общей шине “земли”. Основные технические решения построения ТС Р12-5 зарегистрированы как изобретение Осокина Ю.В., Михаловича Д.Л. Кайдалова Ж.А и Акменса Я.П. (А.С. №248847). При изготовлении четырехслойной структуры ТС Р12-5 важным ноу-хау было формирование в исходной германиевой пластине n -типа p -слоя. Это достигалось диффузией цинка в кварцевой отпаянной ампуле, где пластины располагаются при температуре около 900 ° С, а цинк – в другом конце ампулы при температуре около 500 ° С. Дальнейшее формирование структуры ТС в созданном p -слое аналогично ТС Р12-2. Новая технология позволила уйти от сложной формы кристалла ТС. Пластины с Р12-5 также шлифовались с тыльной стороны до толщины около 150 мкм с сохранением части исходной пластины, далее они скрайбировались на отдельные прямоугольные кристаллы ИС.

Рис. 14. Структура кристалла ТС Р12-5 из АС №248847. 1 и 2 – земля, 3 и 4 – входы, 5 – выход, 6 - питание

После первых положительных результатов изготовления опытных ТС Р12-5, по заказу КБ-1 была открыта НИР “Мезон- 2” , направленная на создание ТС с четырьмя Р12-5. В 1965 году получены действующие образцы в плоском металлокерамическом корпусе. Но Р12-5 оказалась сложной в производстве, главным образом – из-за сложности формирования легированного цинком p -слоя на исходной n - Ge пластине. Кристалл оказался трудоёмким в изготовлении, процент выхода годных низкий, стоимость ТС высокая. По этим же причинам ТС Р12-5 выпускалась в небольших объёмах и вытеснить более медленную, но технологичную Р12-2 она не смогла. А НИР “Мезон- 2” вообще не получил продолжения, в том числе – из-за проблем межсоединений.

К этому времени в НИИ “Пульсар” и в НИИМЭ уже широким фронтом велись работы по развитию планарной кремниевой технологии, обладающей рядом преимуществ перед германиевой, главные из которых – более высокий диапазон рабочих температур (+150°С у кремния и +70°С у германия) и наличии у кремния естественной защитной пленки SiO 2 . А специализация РЗПП была переориентирована на создание аналоговых ИС. Поэтому специалисты РЗПП посчитали развитие германиевой технологии для производства ИС нецелесообразным. Однако при производстве транзисторов и диодов германий ещё какое-то время не сдавал своих позиций. В отделе Ю.В. Осокина уже после 1966 года были разработаны и производились РЗПП германиевые планарные малошумящие СВЧ транзисторы ГТ329, ГТ341, ГТ 383 и др. Их создание было отмечено Государственной премией Латвийской СССР.

Применение

Рис. 15. Арифметическое устройство на твердосхемных модулях. Фото из буклета ТС от 1965 г.

Рис. 16. Сравнительные габариты устройства управления АТС, выполненного на реле и ТС. Фото из буклета ТС от 1965 г.

Заказчиками и первыми потребителями ТС Р12-2 и модулей были создатели конкретных систем: ЭВМ “Гном” (рис. 15) для бортовой самолетной системы “Купол” (НИИРЭ, ГК Ляхович Е.М.) и военно-морских и гражданских АТС (завод ВЭФ, ГК Мисуловин Л.Я.). Активно участвовало на всех стадиях создания ТС Р12-2, Р12-5 и модулей на их и КБ-1, главным куратором этого сотрудничества от КБ-1 был Н.А. Барканов. Помогали финансированием, изготовлением оборудования, исследованиями ТС и модулей в различных режимах и условиях эксплуатации.

ТС Р12-2 и модули “Квант” на её основе были первыми микросхемами в стране. Да и в мире они были среди первых – только в США начинали выпускать свои первые полупроводниковые ИС фирмы Texas Instruments и Fairchild Semiconductor , а в 1964 г. корпорация IBM начала выпуск толстопленочных гибридных ИС для своих ЭВМ. В других странах об ИС ещё и не задумывались. Поэтому интегральные схемы для общественности были диковинкой, эффективность их применения производила поразительное впечатление и обыгрывалась в рекламе. В сохранившемся буклете на ТС Р12-2 от 1965 года (на основе уже реальных применений) сказано: “ Применение твёрдых схем Р12-2 в бортовых вычислительных устройствах позволяет в 10–20 раз сократить вес и габариты этих устройств, уменьшить потребляемую мощность и увеличить надёжность работы. … Применение твёрдых схем Р12-2 в системах управления и коммутации трактов передачи информации АТС позволяет сократить объём управляющих устройств примерно в 300 раз, а также значительно снизить потребление электроэнергии (в 30--50 раз )” . Эти утверждения иллюстрировались фотографиями арифметического устройства ЭВМ “Гном” (рис. 15) и сравнением выпускаемой тогда заводом ВЭФ стойки АТС на основе реле с маленьким блочком на ладони девушки (рис.16). Были и другие многочисленные применения первых рижских ИС.

Производство

Сейчас трудно восстановить полную картину объёмов производства ИС серий 102 и 103 по годам (сегодня РЗПП из крупного завода превратился в небольшое производство и многие архивы утеряны). Но по воспоминаниям Ю.В. Осокина, во второй половине 1960-х годов производство исчислялось многими сотнями тысяч в год, в 1970-х годах – миллионами. По сохранившимся его личным записям в 1985 году было выпущено ИС серии 102 – 4 100 000 шт., модулей серии 116 – 1 025 000 шт., ИС серии 103 – 700 000 шт., модулей серии 117 – 175 000 шт.

В конце 1989 года Ю.В. Осокин, тогда генеральный директор ПО “Альфа”, обратился к руководству Военно-промышленной комиссии при СМ СССР (ВПК) с просьбой о снятии серий 102, 103, 116 и 117 с производства ввиду их морального старения и высокой трудоёмкости (за 25 лет микроэлектроника далеко ушла вперед), но получил категорический отказ. Заместитель председателя ВПК В.Л. Коблов сказал ему, что самолеты летают надёжно, замена исключается. После распада СССР ИС серий 102, 103, 116 и 117 выпускались ещё до середины 1990-х годов, т. е. более 30 лет. ЭВМ “Гном” до сих пор стоят в штурманской кабине “Ил- 76” и некоторых других самолетов. “Это суперкомпьютер”, – не теряются наши лётчики, когда зарубежные коллеги удивленно интересуются невиданным ныне агрегатом.

О приоритетах

Несмотря на то, что у Дж. Килби и Р. Нойса были предшественники, именно они признаны мировой общественностью в качестве изобретателей интегральной схемы.

Р. Килби и Дж. Нойс через свои фирмы подали заявки на выдачу патента на изобретение интегральной схемы. Texas Instruments подала заявку на патент раньше, в феврале 1959 г., а Fairchild сделала это только в июле того же года. Но патент под номером 2981877 выдали в апреле 1961 г. Р. Нойсу. Дж. Килби подал в суд и только в июне 1964 г. получил свой патент под номером 3138743. Потом была десятилетняя война о приоритетах, в результате которой (редкий случай) “победила дружба”. В конечном счёте, Апелляционный Суд подтвердил претензии Р. Нойса на первенство в технологии, но постановил считать Дж. Килби создателем первой работающей микросхемы. А Texas Instruments и Fairchild Semiconductor подписали договор о кросс-лицензировании технологий.

В СССР патентование изобретений авторам ничего, кроме хлопот, ничтожной разовой выплаты и морального удовлетворения не давало, поэтому многие изобретения вообще не оформлялись. И Осокин тоже не спешил. Но для предприятий количество изобретений было одним из показателей, так что их всё же приходилось оформлять. Поэтому Авторское свидетельство СССР за №36845 на изобретение ТС Р12-2 Ю. Осокина и Д. Михалович получили только 28 июня 1966 года.

А Дж. Килби в 2000 г. за изобретение ИС стал одним из лауреатов Нобелевской премии. Р. Нойс не дождался мирового признания, он скончался в 1990 г., а п о положению Нобелевская премия не присваивается посмертно. Что, в данном случае, не совсем справедливо, поскольку вся микроэлектроника пошла по пути, начатом Р. Нойсом. Авторитет Нойса среди специалистов был настолько высок, что он даже получил прозвище “мэр Кремниевой долины”, поскольку был тогда самым популярным из ученых, работавших в той части Калифорнии, которая получила неофициальное название Silicon Valley (В. Шокли называли “Моисеем Кремниевой долины”). А путь Дж. Килби (“волосатый” германий) оказался тупиковым, и не был реализован даже в его фирме. Но жизнь не всегда справедлива.

Нобелевская премия была присвоена троим ученым. Половину её получил 77-летний Джек Килби, а вторую половину разделили между академиком Российской академии наук Жоресом Алферовым и профессором Калифорнийского университета в Санта-Барбаре, американцем немецкого происхождения Гербертом Кремером, за “развитие полупроводниковых гетероструктур, используемых в высокоскоростной оптоэлектронике”.

Оценивая эти работы, эксперты отметили, что “интегральные схемы есть, безусловно, открытие века, оказавшее сильнейшее влияние на общество и мировую экономику”. Для всеми забытого Дж. Килби присуждение Нобелевской премии оказалось сюрпризом. В интервью журналу Europhysics News он признался: “ В то время я лишь думал о том, что было бы важным для развития электроники с точки зрения экономики. Но я не понимал тогда, что снижение стоимости электронных изделий вызовет лавинный рост электронных технологий” .

А работы Ю. Осокина не оценены не только Нобелевским комитетом. Забыты они и в нашей стране, приоритет страны в создании микроэлектроники не защищен. А он бесспорно был.

В 1950-е годы была создана материальная основа для формирования в одном монолитном кристалле или на одной керамической подложке многоэлементных изделий – интегральных схем. Поэтому не удивительно, что почти одновременно идея ИС независимо возникла в головах многих специалистов. А оперативность внедрения новой идеи зависела от технологических возможностей автора и заинтересованности изготовителя, т. е. от наличия первого потребителя. В этом отношении Ю. Осокин оказался в лучшем положении, чем его американские коллеги. Килби был новичком в TI , ему даже пришлось доказывать руководству фирмы принципиальную возможность реализации монолитной схемы изготовлением её макета. Собственно роль Дж. Килби в создании ИС сводится к перевоспитанию руководства TI и в провокации своим макетом Р. Нойса к активным действиям. В серийное производство изобретение Килби не пошло. Р. Нойс в своей молодой и ещё не окрепшей компании пошёл на создание новой планарной технологии, которая действительно стала основой последующей микроэлектроники, но поддалась автору не сразу. В связи с вышесказанным им обоим и их фирмам пришлось потратить немало сил и времени для практической реализации своих идей по построению серийноспособных ИС. Их первые образцы остались экспериментальными, а в серийное производство пошли уже другие микросхемы, даже не ими разработанные. В отличие от Килби и Нойса, которые были далеки от производства, заводчанин Ю. Осокин опирался на промышленно освоенные полупроводниковые технологии РЗПП, и у него были гарантированные потребители первых ТС в виде инициатора разработки НИИРЭ и рядом расположенного завода ВЭФ, помогавших в данной работе. По этим причинам уже первый вариант его ТС сразу пошел в опытное, плавно перешедшее в серийное производство, которое непрерывно продолжалось более 30 лет. Таким образом, начав разработку ТС позже Килби и Нойса, Ю. Осокин (не зная об этом соревновании) быстро догнал их. Причём работы Ю. Осокина никак не связаны с работами американцев, свидетельство тому абсолютная непохожесть его ТС и реализованных в ней решений на микросхемы Килби и Нойса. Производство своих ИС Texas Instruments (не изобретение Килби), Fairchild и РЗПП начали почти одновременно, в 1962 году. Это дает полное право рассматривать Ю. Осокина одним из изобретателей интегральной схемы наравне с Р. Нойсом и более, чем Дж. Килби, а часть нобелевской премии Дж. Килби было бы справедливо поделить с Ю. Осокиным. Что же касается изобретения первой ГИС с двухуровневой интеграцией (а возможно и ГИС вообще) то здесь приоритет А. Пелипенко из НИИРЭ абсолютно бесспорен.

К сожалению, не удалось найти образцов ТС и приборов на их основе, необходимых для музеев. Автор будет весьма признателен за такие образцы или их фотографии.

Развитие микроэлектроники привело в начале 70-х годов к появлению узкоспециализированных БИС, содержащих сотни и тысячи логических элементов и выполняющих одну или ограниченное число функций. Разнообразие типов цифровой аппаратуры требовало расширения номенклатуры БИС, что сопряжено с неприемлемыми с точки зрения экономики затратами. Выходом из этого положения явилась разработка и крупносерийное производство ограниченной номенклатуры БИС, выполняющих разнообразные функции, зависящие от внешних управляющих сигналов. Совокупности таких БИС образуют микропроцессорные комплекты и позволяют строить разнообразную цифровую аппаратуру любой сложности. Важнейшим суперкомпонентом комплекта БИС является микропроцессор (МП): универсальная стандартная БИС, функции которой определяются заданной программой.

Качественной особенностью МП является возможность их функциональной перестройки с помощью изменения внешней программы. По сути, МП представляют собой центральные процессорные элементы ЭВМ, выполненные в виде одной или нескольких БИС.

Главное отличие МП от других типов интегральных схем- способность к программированию последовательности выполняемых функций, т. е. возможность работы по заданной программе.

Таблица 4.1

| Обозначение |

технология |

Число ИС |

Разрядность, |

Быстродействие, |

| р -МДП |

||||

| n -МДП |

||||

| n -МДП |

||||

| n -МДП |

||||

| n -МДП |

||||

| p -МДП |

||||

| n -МДП |

||||

| р -МДП |

||||

| р -МДП |

||||

| n -МДП |

Внедрение микропроцессоров позволяет изменять принцип проектирования цифровой аппаратуры. Раньше для реализации нового алгоритма требовалась новая разработка аппаратуры. Теперь при использовании МП для реализации нового алгоритма не требуется новой аппаратуры, достаточно изменить соответствующим образом программу его работы. Указанная особенность и объясняет огромный интерес, проявляемый у нас в стране и за рубежом к микропроцессорным устройствам.

Короткий интервал времени (1971-1975 гг.) характеризуется появлением МП самых разнообразных модификаций. В настоящее время число типов МП в мире превышает 1000.

Параметры основных типов отечественных микропроцессорных комплектов (МПК) приведены в табл. 4.1.

4.2. Структуры микропроцессоров

Упрощенная структурная схема МП приведена на рис. 4.1.

Рисунок 4.1

Рисунок 4.2

Микропроцессор содержит арифметически-логическое устройство АЛУ, запоминающие устройства ЗУ для оперативного (ОЗУ) и постоянного (ПЗУ) хранения информации, устройство управления, осуществляющее прием, расшифровку команд и задающее последовательность их выполнения, а также устройства ввода-вывода (УВВ) информации, с помощью которого вводятся исходные и выводятся полученные в результате работы МП данные.

Микропроцессоры обрабатывают 2-, 4-, 8-, 16-, 32-разрядные числа, выполняют 30...500 команд сложения, вычитания, сдвига, логических операций. Четырех- и восьмиразрядные МП представляют собой БИС с размерами кристалла 5 х 5 х 0,2 мм.

Обобщенная структурная схема МП приведена на рис. 4.2. Арифметическо-логическое устройство АЛУ совершает различные арифметические и логические операции над числами и адресами, представленными в двоичном коде. Состав операций, выполняемых АЛУ, определен списком инструкций (набором команд). В набор команд входят, как правило, арифметические и логические сложения и умножения, сдвиги, сравнения и т. п. Арифметические операции выполняются в соответствии с правилами двоичной арифметики. Логические операции выполняются по правилам булевой алгебры.

В состав АЛУ входят сумматор, сдвигатели, регистры и другие элементы.

Устройство управления управляет работой АЛУ и всех других блоков МП. В УУ поступают команды из блока памяти. Здесь они преобразуются в двоичные сигналы управления для выполнения данной команды. Работа УУ синхронизируется таймером, распределяющим процесс выполнения команды во времени. Команда представляет собой двоичное слово из 8, 16, 24 разрядов и более (до 64), часть которых представляет код операции, а остальные распределены между адресами данных (операндов) в памяти. Команда с 16-разрядной адресной частью позволяет обращаться к 2 16 -1=65635 ячейкам памяти. Этого количества, как правило, вполне достаточно для задач, решаемых МП. Такое обращение к памяти называется прямой адресацией.

Однако чаще применяется косвенная адресация, которая необходима, когда разрядность адресной части меньше, чем требуется. В этом случае, адресация проводится в два этапа. На первом этапе по адресу, содержащемуся в команде, выбирается ячейка, содержащая адрес другой ячейки, из которой на втором этапе выбирается операнд. Команда при косвенном методе адресации должна содержать один разряд признака операнда, состояние которого определяет, что выбирается на данном этапе: адрес операнда или сам операнд? Конечно, косвенный способ адресации медленнее прямого. Он позволяет за счет наращивания объема памяти адресов обращаться к числу операндов в 2 n раза (где n-разрядность адресной части команды) большему, чем при прямом способе.

Управляющее устройство любую операцию согласно коду, заданному командным словом, распределяет на последовательность фаз (фазы адресации и фазы выполнения), называемую циклом. Из-за ограниченной разрядности МП действия над операндами большой разрядности могут выполняться за два и более циклов. Очевидно, что это в 2 и более раз снижает быстродействие МП. Отсюда следует интересный и практически важный вывод: быстродействие МП находится в обратной зависимости от точности, однозначно определяемой разрядностью операндов.

Микропроцессор содержит блок регистров (Р). Рабочие регистры МП физически представляют собой одинаковые ячейки памяти, служащие для сверхоперативного хранения текущей информации (СОЗУ). По выполненным функциям Р содержит группы, связанные с определенными элементами структуры МП.

Два регистра операндов (О) в течение выполнения операции в АЛУ хранят два двоичных числа. По окончании операции в первом регистре число заменяется результатом, т. е. как бы накапливается (отсюда и название регистра «аккумулятор»). Содержимое второго регистра операндов заменяется в следующей операции другим операндом, в то время как содержимое аккумулятора может быть сохранено по ряду специальных команд.

Регистр команд (К) хранит в течение выполнения операции несколько разрядов командного слова, представляющих собой код этой операции. Адресная часть командного слова содержится в регистре адреса А.

После реализации какой-либо операции разрядность результата может оказаться больше разрядности каждого из операндов, что регистрируется состоянием специального флагового регистра, иногда называемого триггером переполнения. В процессе отладки составленной программы программист должен следить за состоянием флагового регистра и в случае необходимости устранять возникшее переполнение.

Очень важными в системе команд МП являются команды переходов к выполнению заданного участка программы по определенным признакам и условиям, так называемые команды условных переходов. Наличие таких команд определяет уровень «интеллектуальности» МП, так как характеризует его способность принимать альтернативные решения и выбирать различные пути в зависимости от возникающих в ходе решения условий. Для определения таких условий служит специальный регистр состояний (С), фиксирующий состояние МП в каждый момент выполнения программы и посылающий в УУ сигнал перехода к команде, адрес которой содержится в специальном регистре, называемом счетчиком команд (СК). Команды в памяти записываются в определенной программной последовательности по адресам, образующим натуральный ряд, т. е. адрес следующей команды отличается от адреса предыдущей на единицу. Поэтому при реализации непрерывной последовательности команд адрес следующей команды получается путем прибавления к содержимому СК единицы, т. е. образуется в результате счета. Назначение СК-нахождение необходимых адресов команд, причем при наличии в программе команд перехода очередная команда может не иметь следующего адреса. В таком случае в СК записывается адресная часть команды перехода.

Регистры общего назначения (РОН) используются для хранения промежуточных результатов, адресов и команд, возникающих в ходе выполнения программы, и могут связываться по общим шинам с другими рабочими регистрами, а также со счетчиками команд и блоком ввода-вывода информации. В МП обычно содержите» 10...16 РОН разрядностью 2...8 бит каждый. Количество РОН косвенно характеризует вычислительные возможности МП.

Особый интерес представляет наличие у многих моделей МП группы регистров, имеющих магазинную или стековую организацию - так называемые стеки. Стек позволяет без обмена с памятью организовать правильную последовательность выполнения различных последовательностей арифметических действий. Операнд или другая информация может посылаться в стек без указания адреса, поскольку каждое помещаемое в него слово занимает сначала первый регистр, затем «проталкивается» последующими словами каждый раз на регистр глубже. Вывод информации происходит в обратном порядке, начиная с первого регистра, в котором хранится слово, посланное в стек последним. При этом последние регистры очищаются.

Блоки АЛУ, УУ, Р образуют центральный процессор (ЦП), входящий в состав, любой ЭВМ: выделенный на рис. 4.2 штриховой линией. В состав МП может, входить таймер (Т), использующий навесной времязадающий конденсатор или кварцевый резонатор. Таймер - сердце МП, поскольку его работа определяет динамику всех информационных, адресных и управляющих сигналов и синхронизирует работу УУ, а через него и других элементов структуры. Частота синхронизации, называемая тактовой, выбирается максимальной и ограничивается только задержками прохождения сигналов, определяемыми в основном технологией изготовления БИС. Скорость выполнения микропроцессором программы прямо, пропорциональна тактовой частоте.

В составе МП может быть устройство ввода-вывода (УВВ) для обмена информацией между МП и другими устройствами.

Сигналы трех видов - информационные, адресные и управляющие - могут передаваться по одной, двум или трем шинам. Шина представляет собой группу линий связи, число которых определяет разрядность одновременно передаваемой по ней двоичной информации.

Число линий информационной шины (ИШ) определяет объем информации, получаемой или передаваемой МП за одно обращение к памяти, к устройству ввода или вывода. Большинство МП имеет 8-шиниую информационную магистраль. Это позволяет за один раз принять восемь двоичных единиц информации (1 байт). Один байт информация может содержать один из 256 возможных символов алфавита источника информации или один из 256 возможных кодов операций. Такое количество допустимых символов и типов операций для большинства применений является достаточным.

Существуют МП, содержащие 16 и 32 шины в информационной магистрали.

Число линий в шине управления (VIII) зависит от порядка взаимодействия между МП, ЗУ, внешними УВВ информации. Обычно шины управления содержат 8... 16 линий.

4.3. МикроЭВМ

Важным итогом развития программируемых БИС явилась разработка микроЭВМ. Если микроЭВМ создается на одной интегральной микросхеме, то она называется однокристальной. Упрощенная структурная схема микроЭВМ приведена на рис. 4.3.

Рисунок 4.3

Как видно, она содержит центральный процессор ЦП (имеющий устройство аналогично рассмотренному выше МП), ПЗУ, ОЗУ и устройства ввода и вывода информации. Устройство ввода содержит селектор адреса и так называемые порты ввода для считывания информации с гибкого диска, АЦП, телетайпа, перфоленты. Устройство вывода также содержит селектор адреса и порты вывода информации (дисплею, печатающему устройству, устройству выхода на перфоленту, ЦАП).

Данные, поступающие обустройства ввода, передаются на адресную магистраль обычно в виде 8-разрядных параллельных или последовательных кодовых сигналов через порт ввода. Селектор адреса определяет порт ввода, который передает данные на информационную магистраль в некоторый момент времени. Основная память состоит из ПЗУ и ОЗУ. Постоянное ЗУ используется как память программы, которую разработчик микроЭВМ заранее запрограммировал в соответствии с требованием пользователя. Для различных программ используют различные части ПЗУ.

Памятью данных в микроЭВМ является ОЗУ. Информация, хранящаяся в ОЗУ, стирается, когда отключается напряжение питания. Данные, поступающие в ОЗУ, обрабатываются в ЦП в соответствии с программой, хранящейся в ПЗУ. Результаты операций в ЦП хранятся в специальном накопителе информации, называемом аккумулятором или ОЗУ. Они могут быть выведены по команде через один из портов вывода на устройства вывода, подсоединенные к этому порту. Требуемый порт вывода выбирается с помощью схемы селекции адреса.

4.4. Запоминающие устройства

Важнейшими блоками цифровой аппаратуры являются запоминающие устройства (блоки памяти), которые подразделяются на внешние и внутренние. Внешние ЗУ до сих пор реализуются на магнитных лентах и магнитных дисках. Они обеспечивают неопределенно длительное сохранение информации при отсутствии! питания, а также практически любую необходимую емкость памяти. Внутренние ЗУ являются неотъемлемой частью цифровой аппаратуры. Раньше они выполнялись на основе ферритовых сердечников с прямоугольной петлей гистерезиса. Теперь в связи с разработкой ИС имеются широкие возможности создания полупроводниковыхЗУ.

К устройствам памяти относятся следующие виды запоминающих устройств:

Оперативные запоминающие устройства, выполняющие запись и хранение произвольной двоичной информации. В цифровых системах ОЗУ хранят массивы обрабатываемых данных и программы, определяющие процесс текущей обработки информации. В зависимости от назначения и структуры ОЗУ имеют емкость 10 2 …10 7 бит.

Постоянные запоминающие устройства, служащие для хранения информации, содержание которой не изменяется в ходе работы системы, например используемые в процессе работы стандартные подпрограммы и микропрограммы, табличные значения различных функций, константы и др. Запись информации в ПЗУ производится заводом-изготовителем БИС.

Программируемые постоянные запоминающие устройства являются разновидностьюПЗУ, отличающиеся возможностью однократной записи информации по заданию заказчика.

Репрограммируемые ПЗУ, отличающиеся от обычных возможностью многократной электрической сменой информации, осуществляемой заказчиком. Объем РПЗУ обычно составляет 10 2 …10 5 бит.

К устройствам постоянной памяти (ПЗУ, ППЗУ, РПЗУ) предъявляется требование сохранности информации при отключении питания.

Основными параметрамиЗУ являются: информационная емкость в битах; минимальный период обращения; минимально допустимый интервал между началом одного цикла и началом второго; максимальная частота обращения - величина, обратная минимальному периоду обращения; удельная мощность - общая мощность, потребляемая в режиме хранения, отнесенная к 1 биту; удельная стоимость одного бита информации - общая стоимость кристалла, поделенная на информационную емкость.

4.5. Оперативные запоминающиеся устройства

Типовая структура БИС ОЗУ приведена на рис. 4.4.

Рисунок 4.4

Рисунок 4.5

Основным узлом является матрица ячеек памяти (МЯП), состоящая из n строк с т запоминающими ячейками (образующими разрядное слово) в каждой строке. Информационная емкость БИС памяти определяется по формуле N = nm бит.

Входы и выходы ячеек памяти подключаются к адресным АШ и разрядным РШ шинам. При записи и считывании осуществляется обращение (выборка) к одной или одновременно к нескольким ячейкам памяти. В первом случае используются двухкоординатные матрицы (рис. 4.5, а), во втором случае матрицы с пословной выборкой (рис. 4.5,6).

Дешифратор адресных сигналов (ДАС) при подаче соответствующих адресных сигналов осуществляет выбор требуемых ячеек памяти. С помощью РШ осуществляется связь МЯП с буферными усилителями записи (БУЗ) и считывания (БМС) информации. Схема управления записью (СУЗ) определяет режим работы БИС (запись, считывание, хранение информации). Схема выбора кристалла (СВК) разрешает выполнение операций записи-считывания данной микросхемы. Сигнал выборки кристалла обеспечивает выбор требуемой БИС памяти в ЗУ, состоящем из нескольких БИС.

Подача управляющего сигнала на вход СУЗ при наличии сигнала выборки кристалла на входе СВК осуществляет операцию записи. Сигнал на информационном входе БУЗ (1 или 0) определяет записываемую в ячейку памяти информацию. Выходной информационный сигнал снимается с БУС и имеет уровни, согласующиеся с серийными ЦИС.

Большие интегральные схемы ОЗУ стремятся на основе простейших элементов ТТЛ, ТТЛШ, МДП, КМДП, И 2 Л, ЭСЛ, модифицированных с учетом специфики конкретных изделий. В динамических ячейках памяти чаще всего используются накопительные емкости, а в качестве ключевых элементов - МДП транзисторы.

Выбор элементной базы определяется требованиями к информационной емкости и быстродействию БИС памяти. Наибольшей емкости достигают при использовании логических элементов, занимающих малую площадь на кристалле: и 2 л, МДП, динамических ЗЯ. Высоким быстродействием обладают БИС с логическими элементами, имеющими малые перепады логических уровней (ЭСЛ, И 2 Л), а также логические элементы ТТЛШ.

Частотные области применения БИС, использующих различные базовые технические решения, иллюстрирует рис. 4.6.

Рисунок 4.6

Благодаря развитию технологии и схемотехники быстродействие элементов непрерывно возрастает, поэтому границы раздела указанных областей с течением времени сдвигаются в область больших рабочих частот.

4.6. Постоянные запоминающие устройства

Схема ПЗУ аналогична схеме ОЗУ (см. рис. 4.4). Отличия состоят лишь в следующем:

ПЗУ используются для считывания информации;

в ПЗУ осуществляется выборка нескольких разрядов одного адреса одновременно (4, 8, 16 разрядов);

информация, записанная в ПЗУ, не может меняться, и в режиме выборки происходит только ее считывание.

Большие интегральные схемы ПЗУ подразделяются на программируемые изготовителем (с помощью специальных фотошаблонов) и программируемые заказчиком (электрически).

Рисунок 4.7

В ПЗУ используется матричная структура: строки образуются адресными шинами ДШ, а столбцы - разрядами РШ. Каждая АШ хранит определенный код: заданную совокупность логических 1 и 0. В МЯП, изображенной на рис. 4.7, а, однократная запись кода осуществляется с помощью диодов, которые присоединены между АЩ и теми РШ, на которых при считывании должна быть логическая 1. Обычно заказчику поставляют ПЗУ с матрицей, во всех узлах которой имеются диоды.

Суть однократного электрического программирования ППЗУ заключается в том, что пользователь (с помощью специального устройства-программатора) пережигает выводы - перемычки тех диодов, которые находятся в местах расположения логических 0. Пережигание выводов осуществляется путем пропускания через соответствующий диод тока, превышающего допустимое значение.

Диодные ПЗУ отличаются простотой, но имеют существенный недостаток, потребляют значительную мощность. Чтобы облегчить работу дешифратора, вместо диодов используют биполярные (рис. 4.7,6) и (рис. 4.7, в) транзисторы.

При использовании биполярных транзисторов АШ обеспечивает протекание базового тока, который в β б.т. +1 раз меньше эмиттерного, питающего РШ. Следовательно, существенно уменьшается необходимая мощность дешифратора.

Еще больший выигрыш обеспечивает применение МДП транзисторов, так как цепь затвора практически не потребляет мощности. Здесь используется не пережигание выводов, а отсутствие металлизации затвора у транзисторов, обеспечивающих считывание логических 0 в разрядной шине.

4.7. Репрограммируемые постоянные запоминающие устройства

Репрограммируемые ПЗУ являются наиболее универсальными устройствами памяти. Структурная схема РПЗУ аналогична схеме ОЗУ (см. рис. 4.4). Важной отличительной особенностью РПЗУ является использование в МЯП транзистора специальной конструкции со структурой «металл-нитрид-окисел-полупроводник» (МНОП). Принцип действия такой ячейки памяти основан на обратимом изменении порогового напряжения МНОП транзистора. Например, если сделать U ЗИпор >U АШ, то транзистор не будет отпираться адресными импульсами (т. е. не участвует в работе). В то же время другие МНОП транзисторы, у которых U ЗИпор

Структура МНОП транзистора с индуцированным каналом р -типа показана на рис. 4.8, а.

Рисунок 4.8

Здесь диэлектрик состоит из двух слоев: нитрида кремния (Si 3 N 4) и окисла кремния (SiO 2). Пороговое напряжение можно менять, подавая на затвор короткие (порядка 100 мкс) импульсы напряжения разной полярности, с большой амплитудой 30...50 В. При подаче импульса +30 В устанавливается пороговое напряжение U ЗИпор = -5 В. Это напряжение сохраняется, если использовать транзистор или напряжения на затворе U ЗИ =±10В. В таком режиме МНОП транзистор работает как обычный МДП транзистор с индуцированным каналом р -типа.

При подаче импульса -30 В пороговое напряжение принимает значение U ЗИпор ~20 В, как показано на рис. 4.8, 6 и в. При этом сигналы на входе транзистора U ЗИ ± 10 В не могут вывести транзистор из закрытого состояния. Это явление используется в РПЗУ.

В основе работы МНОП транзисторов лежит накопление, заряда на границе нитридного и оксидного слоев. Это накопление есть результат неодинаковых токов проводимости в слоях. Процесс накопления описывается выражением dq / dt = I sio 2 - I si 3 n 4 . При большом отрицательном напряжении U ЗИ на границе накапливается положительный заряд. Это равносильно введению доноров в диэлектрик и сопровождается увеличением отрицательного порогового напряжения. При большом положительном напряжении U ЗИ на границе накапливается отрицательный заряд. Это приводит к уменьшению отрицательного порогового напряжения. При малых напряжениях U ЗИ токи в диэлектрических слоях уменьшаются на 10...15 порядков, поэтому накопленный заряд сохраняется в течение тысяч часов, а, следовательно, сохраняется и пороговое напряжение.

Известна и другая возможность построения ячейки памяти для РПЗУ на основе МДП транзисторов с однослойным диэлектриком. Если прикладывать к затвору достаточно большое напряжение, то будет наблюдаться лавинный пробой диэлектрика, в результате чего в нем будут накапливаться электроны. При этом у транзистора изменится пороговое напряжение. Заряд электронов сохраняется в течение тысяч часов. Для того чтобы осуществить перезапись информации, нужно удалить электроны из диэлектрика. Это достигается путем освещения кристалла ультрафиолетовым светом, вызывающим фотоэффект: выбивание электронов из диэлектрика.

При использовании ультрафиолетового стирания удается существенно упростить схему РПЗУ. Обобщенная структурная схема РПЗУ с ультрафиолетовым стиранием (рис. 4.9) содержит кроме МЯП дешифратор адресных сигналов (ДАС), устройство выбора кристалла (УВК) и буферный усилитель (БУ) для считывания информации.

Рисунок 4.9

По приведенной структурной схеме выполнена, в частности, БИС РПЗУ с ультрафиолетовым стиранием типа К573РФ1 емкостью 8192 бита.

4.8. Цифроаналоговые преобразователи

Назначение ЦАП - преобразование двоичного цифрового сигнала в эквивалентное аналоговое напряжение. Такое преобразование можно произвести с помощью резистивных цепей, показанных на рис. 4.10.

Рисунок 4.10

В ЦАП с двоично-весовыми резисторами (рис. 4.10, а) требуется меньшее число резисторов, однако при этом необходим целый ряд номиналов прецизионных сопротивлений. Аналоговое выходное напряжение U ан ЦАП определяется как функция двухуровневых входных напряжений:

U ан =(U A +2U B +4U C +…)/(1+2+4+...).

На цифровых входах U A , U B , U C , ... напряжение может принимать лишь два фиксированных значения, например, либо 0, либо 1. Для ЦАП, в котором используются резисторы R и R /2, требуется больше резисторов (рис. 4.10,6), но только с двумя номиналами. Аналоговое напряжение на выходе такого ЦАП определяется по формуле

U ан =(U A +2U B +4U C +…+mU n)/2 n

где n - число разрядов ЦАП; т - коэффициент, зависящий от числа разрядов ЦАП.

Для обеспечения высокой точности работы резистивные цепи ЦАП должны работать на высокоомную нагрузку. Чтобы согласовать резистивные цепи с низкоомной нагрузкой, используют буферные усилители на основе операционных усилителей, показанные на рис. 4.10, а, б.

4.9. Аналого-цифровые преобразователи

Назначение АЦП - преобразование аналогового напряжения в его цифровой эквивалент. Как правило, АЦП имеют более сложную схему, чем ЦАП, причем ЦАП часто является узлом АЦП. Обобщенная структурная схема АЦП с ЦАП в цепи обратной связи показана на рис. 4.11.

Рисунок 4.11

Выполненные по такой схеме АЦП находят широкое применение благодаря хорошим показателям по точности, быстродействию при сравнительной простоте и низкой стоимости.

В состав АЦП входят n -разрядный триггерный регистр результатов преобразования DD 1 - DD n , управляющий разрядами ЦАП; компаратор, связанный с устройством управления УУ и содержащий генератор тактовой частоты. Реализуя вУУ различные алгоритмы работы АЦП, получают различные характеристики преобразователя.

Используя рис. 4.11, рассмотрим принцип действия АЦП, предполагая, что в качестве триггерного регистра используется реверсивный счетчик. Реверсивный счетчик имеет цифровой выход, напряжение на котором возрастает от каждого тактового импульса, когда на входе счетчика «Прямой счет» высокий уровень напряжения, а на входе «Обратный счет» - низкий. И наоборот, напряжение на цифровом выходе при каждом тактовом импульсе уменьшается, когда на входе «Прямой счет» низкий, а на входе «Обратный счет» - высокий уровень напряжения.

Важнейшим узлом АЦП является компаратор (К), имеющий два аналоговых входа U ЦАП и U ан и цифровой выход, подключенный через УУ к реверсивному счетчику. Если напряжение на выходе компаратора имеет высокий уровень, уровень на входе счетчика «Прямой счет» также будет высоким. И наоборот, когда выходное напряжение компаратора имеет низкий уровень, низким будет также и уровень на входе «Прямой счет».

Таким образом, в зависимости от того, высокий или низкий уровень на выходе компаратора, реверсивный счетчик считает соответственно в прямом или обратном направлении. В первом случае на входе U ЦАП компаратора наблюдается ступенчато-нарастающее напряжение, а во втором - ступенчато-спадающее.

Поскольку компаратор работает без обратной связи, уровень его выходного напряжения делается высоким, когда напряжение на его входе U ан станет немного отрицательнее, чем на входе U ЦАП. И наоборот, уровень его выходного напряжения становится низким, как только напряжение на входе U ан станет немного положительнее напряжения на входе U ЦАП.

На вход U ЦАП компаратора поступает выходное напряжение ЦАП, которое сравнивается с аналоговым входным напряжением,поступающим на вход U ан .

Если аналоговое напряжение U ан превышает напряжение, снимаемое с выхода ЦАП, реверсивный счетчик считает в прямом направлении, ступенями наращивая напряжение на входе U ЦАП до значения напряжения на входе U ан. Если же U ан <U ЦАП или становится таковым в процессе счета, напряжение на выходе компаратора имеет низкий уровень и счетчик считает в обратном направлении, вновь приводя U ЦАП к U ан . Таким образом, система имеет обратную связь, которая поддерживает выходное напряжение ЦАП приблизительно равным напряжению U ан . Следовательно, выход реверсивного счетчика всегда представляет собой цифровой эквивалент аналогового входного напряжения. С выхода реверсивного счетчика считывается цифровой эквивалент аналогового входного сигнала АЦП.

4.10. Цифровые и аналоговые мультиплексоры

В микропроцессорных системах, АЦП, ЦАП, а также в системах электронной коммутации широкое применение находят мультиплексоры: многоканальные коммутаторы (имеющие 4, 8, 16, 32, 64 входа и 1-2 выхода) с цифровым устройством управления. Простейшие мультиплексоры цифровых и аналоговых сигналов показаны на рис. 4.12, а и б соответственно.

Рисунок 4.12

Цифровой мультиплексор (рис. 4.12, а) позволяет осуществлять последовательный или произвольный опрос логических состояний источников сигналов Х 0 , Х 1 , Х 2 , Х 3 и передачу результата опроса на выход

По указанному принципу строятся мультиплексоры на любое требуемое число информационных входов. Некоторые типы цифровых мультиплексоров допускают коммутацию и аналоговых информационных сигналов.

Однако лучшими показателями обладают аналоговые мультиплексоры, содержащие матрицу высококачественных аналоговых ключей (AK 1 ...AK 4), работающих на выходной буферный усилитель, цифровое УУ. Соединение узлов между собой иллюстрирует рис. 4.12,6.