Missä käytetään palamattomia kankaita www.algo-textile.ru. Hyttysverkkotarvikkeet hyttysverkkoihin 2-sklad.ru.

PCI ja PCI-X

PCI- ja PCI-X-väylät

Johdanto

PCI- ja PCI-X-väylät ovat tärkeimmät I/O-laajennusväylät nykyaikaisissa tietokoneissa; videosovittimien liittämistä varten niitä täydentää AGP-portti. I/O-laajennusväylät (Expansion Bus) ovat järjestelmätason liitettävyyttä: niiden avulla sovittimet ja oheislaitteet voivat käyttää suoraan tietokonejärjestelmän resursseja - muistia ja I/O-osoitetilaa, keskeytyksiä, suoraa muistin käyttöä. Laajennusväyliin liitetyt laitteet voivat itse ohjata näitä väyliä ja saada pääsyn muihin tietokoneresursseihin. Laajennusväylät toteutetaan mekaanisesti paikoilla (paikkaliittimillä) tai nastaliittimillä; Niille on ominaista lyhyt johtimien pituus, toisin sanoen ne ovat puhtaasti paikallisia, mikä mahdollistaa korkean toimintanopeuden saavuttamisen. Näitä väyliä ei saa lähettää liittimiin, mutta niitä käytetään integroitujen emolevyjen laitteiden kytkemiseen.

Aluksi PCI-väylä esiteltiin laajennuksena (mezzanine-väylä) järjestelmiin, joissa oli ISA-väylä. Se kehitettiin Pentium-prosessoreille, mutta se toimi hyvin myös i486-prosessorien kanssa. Myöhemmin PCI:stä tuli keskusväylä joksikin aikaa: se yhdistettiin prosessoriväylään korkean suorituskyvyn sillalla ("pohjoinen" silta), joka oli osa emolevyn piirisarjaa. Loput I/O-laajennusväylät (ISA/EISA tai MCA) sekä paikallinen ISA-tyyppinen X-BUS-väylä ja LPC-liitäntä, johon emolevyn sirut on kytketty (ROM BIOS, keskeytysohjaimet, näppäimistöt, DMA , COM- ja LPT-portit, HDD ja muut "pienet asiat"), jotka on kytketty PCI-väylään "eteläisen" sillan kautta. Nykyaikaisissa emolevyissä, joissa on "hub"-arkkitehtuuri, PCI-väylä on siirretty reuna-alueelle vaarantamatta tietoliikennekanavan tehoa prosessorin ja muistin kanssa, mutta myös lataamatta laitteita muihin väyliin, joissa on liikennettä.

PCI-väylä on synkroninen - kaikki signaalit siepataan CLK-signaalin positiivisella reunalla (reunalla). Nimellistahdistustaajuuden katsotaan olevan 33,3 MHz, sitä voidaan tarvittaessa alentaa. Versiosta PCI 2.1 alkaen on mahdollista nostaa taajuutta 66,6 MHz:iin, jos kaikki väylällä olevat laitteet ovat samaa mieltä. PCI-X:ssä taajuus voi olla 133 MHz.

PCI käyttää rinnakkaismultipleksoitua osoite/data (AD) väylää, jonka tyypillinen leveys on 32 bittiä. Spesifikaatio määrittelee mahdollisuuden laajentaa bittisyvyyttä 64 bittiin; PCI-X-versio 2.0 määrittää myös 16-bittisen väylävaihtoehdon. Väylätaajuudella 33 MHz teoreettinen suorituskyky saavuttaa 132 MB/s 32-bittisellä väylällä ja 264 MB/s 64-bittisellä väylällä; synkronointitaajuudella 66 MHz - 264 MB/s ja 528 MB/s, vastaavasti. Nämä huippuarvot saavutetaan kuitenkin vain pakettisiirron aikana: protokollan ylikuormituksen vuoksi todellinen keskimääräinen väylän läpäisykyky on pienempi.

PCI- ja PCI-X-väylien ja muiden PC-yhteensopivien tietokoneiden laajennusväylien vertailuominaisuudet on esitetty taulukossa. 1.1. ISA-väylä poistuu pöytätietokoneista, mutta säilyttää asemansa teollisuus- ja sulautetuissa tietokoneissa sekä perinteisessä slot-versiossa että "sandwich" PC/104 -versiossa. PCMCIA-paikkoja, joissa on PC Card ja Card Bus -väylät, käytetään laajalti kannettavissa tietokoneissa. LPC-väylä on moderni, edullinen tapa liittää resurssiintensiivisiä laitteita emolevyyn.

| Rengas | Huippukapasiteetti MB/s | DMA-kanavat | Bussimestari | ACFG | Tietojen leveys | Osoitteen koko | Taajuus MHz |

| ISA-8 | 4 | 3 | - | - | 8 | 20 | 8 |

| ISA-16 | 8 |

7 |

+ |

- |

16 |

24 |

8 |

| LPC | 6,7 |

7 |

+ |

- |

8/16/32 |

32 |

33 |

| EISA |

33,3 | 7 | + |

+ |

32 |

32 |

8,33 |

| MCA-16 |

16 |

- |

+ |

+ |

16 |

24 |

10 |

| MCA-32 |

20 |

- |

+ |

+ |

32 |

32 |

10 |

| VLB |

132 |

- |

(+) |

- |

32/64 |

32 |

33-50(66) |

| PCI |

133-533 |

- |

+ |

+ |

32/64 |

32/64 |

33/66 |

| PCI-X |

533-4256 |

- |

+ |

+ |

16/32/64 |

32/64 |

66-133 |

| PCI Express |

496-15872 |

- |

+ |

+ |

1/2/4/8/12/16/32 |

32/64 |

2,5 GHz |

| AGP 1x/2x/4x/8x |

266/533/1066/2132 |

- |

+ |

+ |

32 |

32/64 |

66 |

| PCMCIA |

10/22 |

+ |

- |

+ |

8/16 |

26 |

10 |

| Korttibussi | 132 | - | + | + | 32 | 32 | 33 |

ACFG1- Tukee automaattista konfigurointia. ISA:lle PnP on sovittimien ja ohjelmistojen toteuttama myöhäinen lisäys.

PCI- ja PCI-X-väyläsignalointiprotokolla

Tiedonvaihto PCI- ja PCI-X-väylällä järjestetään transaktioiden muodossa - loogisesti suoritettuina vaihtooperaatioina. Tyypillinen tapahtuma sisältää kaksi laitetta: vaihdon aloittaja, joka tunnetaan myös nimellä master-laite, ja kohdelaite, joka tunnetaan myös nimellä orja. Näiden laitteiden välisen vuorovaikutuksen säännöt määräytyvät PCI-väyläprotokollan mukaan. Laite voi seurata tapahtumia väylällä olematta osallistuja (syöttämättä signaaleja); Termi Snooping vastaa seurantatilaa. On olemassa erityinen tapahtumatyyppi (Special Cycle) - lähetys, jossa aloittaja ei ole vuorovaikutuksessa minkään laitteen kanssa protokollan mukaisesti. Jokainen tapahtuma suorittaa yhden komennon, tyypillisesti lukee tai kirjoittaa tietoja tiettyyn osoitteeseen. Tapahtuma alkaa osoitevaiheella, jossa aloittaja määrittää komennon ja kohdeosoitteen. Voi seurata datavaiheita, joissa yksi laite (tietolähde) laittaa dataa väylään ja toinen (nielu) lukee sen. Tapahtumia, joissa on useita tietovaiheita, kutsutaan erätapahtumiksi. On myös yksittäisiä tapahtumia (yhdellä datavaiheella). Tapahtuma voidaan suorittaa ilman datavaiheita, jos kohdelaite (tai aloittaja) ei ole valmis vaihtoon. PCI-X-väylään on lisätty attribuuttivaihe, jossa siirretään lisätietoja tapahtumasta.

PCI- ja PCI-X-väyläsignalointiprotokolla

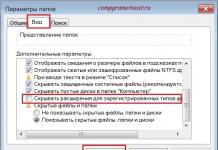

Väyläliityntäsignaalien koostumus ja tarkoitus on esitetty alla olevassa taulukossa. Kaikkien signaalilinjojen tilat havaitaan positiivisella reunalla CLK ja näitä hetkiä seuraavassa kuvauksessa tarkoitetaan väyläjaksoilla (merkitty kuvissa pystysuoralla katkoviivalla). Eri aikoina samoja signaalilinjoja ohjataan eri väylälaitteilla, ja oikean (konfliktittoman) "valtuutuksen siirtoon" edellytetään olevan ajanjakso, jonka aikana mikään laite ei ohjaa linjaa. Aikakaavioissa tämä tapahtuma - niin kutsuttu "piruetti" (käännös) - on osoitettu puoliympyrän muotoisilla nuolilla.

Taulukko. PCI-väylän signaalit

| Signaali |

Tarkoitus |

| ILMOITUS | Osoite/Data - multipleksoitu osoite/tietoväylä. Tapahtuman alussa osoite lähetetään, seuraavissa jaksoissa - tiedot |

| C/B # | Command/Byte Enable - komento/lupa käyttää tavuja. Seuraavan väyläjakson tyypin määrittävä komento määritellään nelibittisellä koodilla osoitevaiheessa |

| FRAME# |

Kehys. Signaalin tulo merkitsee tapahtuman alkua (osoitevaihe), signaalin poistaminen osoittaa, että seuraava tiedonsiirtojakso on tapahtuman viimeinen |

| DEVSEL# |

Laitevalinta - laite on valittu (ohjauskeskuksen vastaus sille osoitettuun tapahtumaan) |

| IRDY# |

Initiator Ready - päälaitteen valmius vaihtaa tietoja |

| TRDY# |

Target Ready - ohjauskeskuksen valmius tiedonvaihtoon |

| STOP# |

Pyyntö CPU:lta isännälle nykyisen tapahtuman pysäyttämiseksi |

| LUKKO# |

Väylän lukitussignaali keskeytymättömän toiminnan varmistamiseksi. Sitä käyttää silta, joka vaatii useita PCI-tapahtumia yhden toiminnon suorittamiseen |

| REQ# |

Pyyntö - pyyntö päälaitteelta väylän kaappaamiseksi |

| GNT# |

Grant - väylän ohjauksen myöntäminen isännälle |

| PAR |

Pariteetti - yhteinen pariteettibitti AD- ja C/BE#-linjoille |

| PERR# |

Parity Error — pariteettivirhesignaali (kaikille jaksoille paitsi erikoisjaksoille). Luoda mikä tahansa laite, joka havaitsee virheen |

| PME# |

Virranhallintatapahtuma - signaali tapahtumista, jotka aiheuttavat muutoksen kulutustilassa (PCI 2.2:ssa käyttöön otettu lisäsignaali) |

| CLKRUN# |

Kello käynnissä — väylä toimii nimelliskellotaajuudella. Signaalin poistaminen tarkoittaa synkronoinnin hidastamista tai pysäyttämistä kulutuksen vähentämiseksi (mobiilisovellukset) |

| PRSN# |

Nykyinen - virrankulutuspyynnön koodaavat piirilevyn läsnäoloilmaisimet. Laajennuskortissa yksi tai kaksi LED-linjaa on kytketty GND-väylään, jonka emolevy havaitsee. |

| RST# |

Nollaa - palauta kaikki rekisterit alkuperäiseen tilaan (napsauta "Palauta" -painiketta ja uudelleenkäynnistyksen yhteydessä) |

| IDSEL |

Initialization Device Select - laitteen valinta konfiguraation luku- ja kirjoitusjaksoissa; Näihin sykleihin reagoi laite, joka havaitsee korkean signaalitason tällä linjalla |

| SERR# |

System Error - järjestelmävirhe. Osoite- tai datapariteettivirhe erityisessä kehyksessä tai muu laitteen havaitsema katastrofaalinen virhe. Aktivoi mikä tahansa PCI-laite ja kutsuu NMI:tä |

| REQ64# |

Pyydä 64 bittiä - pyyntö 64-bittiselle vaihdolle. Signaali syötetään 64-bittisellä aloittimella, ja se osuu ajallisesti yhteen FRAME#-signaalin kanssa. Resetoinnin aikana (RST#-signaali) ilmoittaa 64-bittiselle laitteelle, että se on kytketty 64-bittiseen väylään. Jos 64-bittinen laite ei havaitse tätä signaalia, sen on määritettävä itsensä uudelleen 32-bittiseen tilaan poistamalla käytöstä korkeabittiset puskuripiirit |

| ACK64# |

64-bittisen vaihdon vahvistus. Signaalin syöttää 64-bittinen CPU, joka on tunnistanut osoitteensa, samanaikaisesti DEVSEL#:n kanssa. Jos tätä vahvistusta ei toimiteta, aloittaja pakottaa suorittamaan vaihdon 32-bittisenä |

| INTA#, INTB#, INTC#, INTD# |

Keskeytys A, B, C, D - keskeytä pyyntörivit, tason herkkyys, aktiivinen taso - matala, mikä mahdollistaa linjojen erottelun (jakamisen) |

| CLK |

Kello — väylän kellotaajuus. Sen pitäisi olla välillä 20-33 MHz, PCI 2.1:stä alkaen se voi olla jopa 66 MHz, PCI-X:ssä jopa 100 ja 133 MHz |

| M66FI |

66 MHz käytössä - kellotaajuuden tarkkuus jopa 66 MHz (korteilla 33 MHz on maadoitettu, 66 MHz on ilmainen) |

| PCIXCAP (38B) |

PCI-X-ominaisuudet: PCI-korteilla - maadoitettu, PCI-X133:ssa kytketty maahan 0,01 µF:n kondensaattorilla, PCI-X66:ssa - rinnakkaisella RC-piirillä 10 kOhm, 0,01 µF. |

| SDONE |

Snoop Done - signaali, että snoop-jakso on valmis nykyiselle tapahtumalle. Matala taso osoittaa, että muistin ja välimuistin koherenssin valvontasykli on epätäydellinen. Valinnainen signaali, jota käyttävät vain väylälaitteet, joissa on välimuisti. Vanhentunut PCI 2.2:sta lähtien |

| SBO# |

Snoop Backoff - nykyinen pääsy väylätilaajan muistiin päätyy muokattuun välimuistiriville. Valinnainen signaali, jota käyttävät vain väylätilaajat, joilla on välimuistia takaisinkirjoitusalgoritmin aikana. Vanhentunut PCI 2.2:sta lähtien |

| SMBCLK |

SMBus Clock - SMBus-väylän kellosignaali (I2C-liitäntä). Otettu käyttöön PCI 2.3:n jälkeen |

| SMBDAT |

SMBus Data - SMBus-väylän sarjatiedot (I2C-liitäntä). Otettu käyttöön PCI 2.3:n jälkeen |

| TCK |

Test Clock - JTAG testaa käyttöliittymän synkronointia |

| TDI |

Test Data Input - JTAG-testirajapinnan syöttötiedot |

| TDO |

Test Data Output - JTAG testiliitännän lähtötiedot |

| TMS |

Test Mode Select - valitse JTAG-testiliittymän tila |

| TRST |

Test Logic Reset - nollaa testilogiikka |

Väylää voi kulloinkin ohjata vain yksi isäntälaite, joka on saanut siihen oikeuden tuomarilta. Jokaisella isäntälaitteella on signaalipari - REQ# väyläohjauksen pyytämiseksi ja GNT# väyläohjauksen hyväksymisen vahvistamiseksi. Laite voi aloittaa tapahtuman (asettaa FRAME#-signaalin) vain, kun se vastaanottaa aktiivisen GNT#-signaalin ja odottaa, kunnes väylätoimintaa ei ole. Huomaa, että lepoa odottaessaan tuomari voi "muuttaa mieltään" ja antaa väylän ohjauksen toiselle laitteelle, jolla on korkeampi prioriteetti. GNT#-signaalin poistaminen estää laitetta aloittamasta seuraavaa tapahtumaa ja voi tietyissä olosuhteissa (katso alla) pakottaa sen lopettamaan nykyisen tapahtuman. Väylän käyttöä koskevien pyyntöjen sovittelusta huolehtii erityinen solmu - välimies, joka on osa siltaa, joka yhdistää tämän väylän keskustaan. Prioriteettikaavio (kiinteä, round-robin, yhdistetty) määräytyy välimiesohjelmoinnin mukaan.

Yhteisiä multipleksoituja AD-linjoja käytetään osoitteeseen ja dataan. Neljä multipleksoitua C/BE-linjaa tarjoavat käskykoodauksen osoitevaiheessa ja tavuresoluution datavaiheessa. Kirjoitustapahtumissa C/BE-rivit sallivat datatavujen käytön samanaikaisesti niiden läsnäolon kanssa lukutapahtumissa, nämä signaalit viittaavat seuraavan datavaiheen tavuihin. Osoitevaiheessa (transaction start) isäntä aktivoi FRAME#-signaalin, lähettää kohdeosoitteen AD-väylällä ja välittää tiedon tapahtumatyypistä (komennosta) C/BE#-linjoilla. Osoitettu kohdelaite vastaa DEVSEL#-signaalilla. Päälaite ilmaisee valmiutensa vaihtaa tietoja IRDY#-signaalin kanssa. Tämä valmius voidaan asettaa ennen DEVSEL#:n vastaanottamista. Kun kohdelaite on valmis vaihtamaan tietoja, se asettaa TRDY#-signaalin. Dataa siirretään AD-väylällä vain, kun signaalit IRDY# ja TRDY# ovat läsnä samanaikaisesti. Näiden signaalien avulla isäntä- ja kohdelaitteet koordinoivat nopeuksiaan ottamalla käyttöön odotustilat. Alla olevassa kuvassa on tiedonsiirron ajoituskaavio, jossa sekä isäntä- että kohdelaitteet syöttävät odotuskellot. Jos molemmat syöttäisivät valmiita signaaleja osoitevaiheen lopussa ja poistaisivat ne vasta vaihdon lopussa, niin jokaisessa kellojaksossa osoitevaiheen jälkeen lähetettäisiin 32 bittiä dataa, mikä antaisi maksimaalisen vaihdon suorituskyvyn. Lukutapahtumissa osoitevaiheen jälkeen tarvitaan piruettille lisäkello, jonka aikana aloittaja lopettaa AD-linjan ohjauksen; Kohdelaite pystyy ottamaan AD-väylän hallinnan vasta seuraavassa kellojaksossa. Kirjoitustapahtumassa piruettia ei tarvita, koska aloittaja lähettää tiedot.

PCI-väylällä kaikkia tapahtumia käsitellään purskeina: jokainen tapahtuma alkaa osoitevaiheella, jota voi seurata yksi tai useampi datavaihe. Datavaiheiden lukumäärää paketissa ei nimenomaisesti ilmoiteta, mutta viimeisen datavaiheen kellojaksossa isäntälaite, kun IRDY#-signaali syötetään, poistaa FRAME#-signaalin. Yksittäisissä tapahtumissa FRAME#-signaali on aktiivinen vain yhden kellojakson ajan. Jos laite ei tue erätapahtumia orjatilassa, sen on pyydettävä erätapahtuman lopettamista ensimmäisen datavaiheen aikana (vakuuttamalla STOP#-signaali samaan aikaan kuin TRDY#). Vastauksena tähän isäntä suorittaa tietyn tapahtuman ja jatkaa seuraavan tapahtuman vaihtamista seuraavalla osoitearvolla. Viimeisen datavaiheen jälkeen isäntälaite poistaa IRDY#-signaalin ja väylä siirtyy Idle-tilaan - molemmat signaalit: FRAME# ja IRDY# ovat passiivisessa tilassa.

Aloittaja voi aloittaa seuraavan tapahtuman ilman taukoaikaa asettamalla FRAME# samanaikaisesti IRDY#:n poistamisen kanssa. Tällaiset nopeat vierekkäiset tapahtumat (Fast Back-to-Back) voidaan osoittaa joko samalle tai eri kohdelaitteelle. Kaikki kohdelaitteena toimivat PCI-laitteet tukevat ensimmäistä tyyppiä nopeita peräkkäisiä tapahtumia. Toisen tyyppisten vierekkäisten tapahtumien tuki (tällainen tuki on valinnainen) osoitetaan tilarekisterin bitillä 7. Aloittaja saa (jos hän voi) käyttää nopeita peräkkäisiä tapahtumia eri laitteilla (luvan määrää komentorekisterin bitti 9) vain, jos kaikki väyläagentit sallivat nopeat kutsut. Kun tietoja vaihdetaan PCI-X-tilassa, nopeat peräkkäiset tapahtumat eivät ole sallittuja.

Väyläprotokolla varmistaa keskuksen luotettavuuden - isäntälaite saa aina tiedon tapahtuman käsittelystä kohdelaitteen toimesta. Eräs keino vaihdon luotettavuuden lisäämiseksi on pariteettiohjauksen käyttö: AD- ja C/BE#-linjat sekä osoite- että datavaiheessa on suojattu pariteettibitillä PAR (näiden linjojen asetettujen bittien määrä, PAR mukaan lukien, on oltava parillinen). Todellinen PAR-arvo ilmestyy väylään yhden kellojakson viiveellä suhteessa AD- ja C/BE#-linjoihin. Kun virhe havaitaan, laite generoi PERR#-signaalin (siirretty kellon verran sen jälkeen, kun kelvollinen pariteettibitti ilmestyy väylään). Kun pariteettia lasketaan tiedonsiirron aikana, kaikki tavut otetaan huomioon, mukaan lukien virheelliset tavut (merkitty korkealla C/BEx#-signaalilla). Bittitilan, jopa virheellisissä datatavuissa, on pysyttävä vakaana datavaiheen aikana.

Jokainen tapahtuma väylällä on suoritettava suunnitellusti tai keskeytettävä, ja väylän on mentävä lepotilaan (FRAME#- ja IRDY#-signaalit ovat passiivisia). Tapahtuman suorittamisen aloittaa joko päälaite tai kohdelaite.

Isäntä voi suorittaa tapahtuman jollakin seuraavista tavoista:

- valmistuminen - normaali lopettaminen tiedonvaihdon lopussa;

- aikakatkaisu — valmistuminen aikakatkaisulla. Tapahtuu, kun isäntälaitteen väyläohjaus poistetaan tapahtuman aikana (poistamalla GNT#-signaali) ja sen latenssiajastin vanhenee. Tämä voi tapahtua, jos osoitettu kohdelaite on odottamattoman hidas tai tapahtuma on ajoitettu liian pitkäksi. Lyhyet tapahtumat (yhdellä tai kahdella datavaiheella), vaikka GNT#-signaali poistetaan ja ajastin laukeaisi, suoritetaan normaalisti;

- master-Abort – Keskeytä tapahtuma, kun päälaite ei saa vastausta kohdelaitteelta (DEVSEL#-signaali) tietyn ajan kuluessa.

Tapahtuma voidaan lopettaa kohdelaitteen aloitteesta; Tätä varten se voi syöttää STOP#-signaalin. Tapahtuman lopettamista on kolme mahdollista:

- uudelleenyritys - toisto, STOP#-signaalin käyttöönotto passiivisella TRDY#-signaalilla ennen ensimmäistä datavaihetta. Tämä tilanne syntyy, kun kohdelaite ei sisäisen kiireen vuoksi ehdi tuottaa ensimmäistä dataa ajoissa (16 kellojaksoa). Uudelleenyrityksen keskeytys on osoitus isännälle käynnistää sama tapahtuma uudelleen;

- irrota - irtikytkentä, STOP#-signaalin syöttäminen ensimmäisen datavaiheen aikana tai sen jälkeen. Jos STOP#-signaali syötetään seuraavan datavaiheen TRDY#-signaalin ollessa aktiivinen, tämä data lähetetään ja tapahtuma on valmis. Jos STOP#-signaali asetetaan, kun TRDY#-signaali on passiivinen, tapahtuma suoritetaan ilman seuraavan vaiheen tietojen lähettämistä. Yhteys katkeaa, kun kohdelaite ei pysty antamaan tai vastaanottamaan seuraavaa pakettidatan osaa ajoissa. Yhteyden katkaisu on ilmoitus isännälle käynnistää tämä tapahtuma uudelleen, mutta muokatulla aloitusosoitteella;

- target-abort - epäonnistuminen, STOP#-signaalin syöttäminen samanaikaisesti DEVSEL#-signaalin poistamisen kanssa (aikaisemmissa tapauksissa STOP#-signaalin ilmestyessä DEVSEL#-signaali oli aktiivinen). Tämän jälkeen tietoja ei enää lähetetä. Kieltäytyminen tapahtuu, kun kohdelaite havaitsee vakavan virheen tai muut olosuhteet, joissa se ei enää pysty palvelemaan annettua pyyntöä (mukaan lukien komento, jota ei tueta).

Kolmen tyyppisen tapahtuman lopettamisen käyttäminen ei ole välttämätöntä kaikille kohdelaitteille, mutta minkä tahansa päälaitteen tulee olla valmis lopettamaan tapahtumat mistä tahansa näistä syistä.

Uudelleen irtisanomisen tyyppiä käytetään viivästyneiden tapahtumien järjestämiseen. Viivästettyjä tapahtumia käyttävät vain hitaat kohdelaitteet sekä PCI-sillat siirrettäessä tapahtumia toiseen väylään. Keskeyttämällä (aloittajalle) tapahtuman uudelleenyritysehdon kanssa kohdelaite suorittaa tapahtuman sisäisesti. Kun aloittaja toistaa tämän tapahtuman (antaa saman komennon samalla osoitteella ja samalla joukolla C/BE#-signaaleja datavaiheessa), kohdelaitteella (tai sillalla) on jo tulos valmiina (luku data tai kirjoitus edistyminen tila), että se palaa nopeasti aloittajalle. Laitteen tai sillan on tallennettava tietyn laitteen suorittaman odottavan tapahtuman tulos, kunnes aloittaja pyytää tuloksia. Hän voi kuitenkin "unohtaa" toistaa tapahtuman (joistakin epänormaaleista tilanteista). Tulosten tallennuspuskurin ylivuodon välttämiseksi laitteen on hylättävä nämä tulokset. Pudottaminen voidaan suorittaa ilman sivuvaikutuksia, jos tapahtuma siirrettiin muistiin, joka mahdollistaa esihaun (esihaku-attribuutilla, katso alla). Yleensä muun tyyppisiä tapahtumia ei voida hylätä rankaisematta (niiden osalta tietojen eheys voi loukata), hylkääminen on sallittua vain, kun on odotettu 215 väyläjakson toistoa (kun hylkäysajastin laukeaa). Laite voi ilmoittaa tästä poikkeuksesta ajurilleen (tai koko järjestelmälle).

Tapahtuman aloittaja voi pyytää PCI-väylän yksinomaista käyttöä usean väylätapahtuman vaativan vaihtotoiminnan ajaksi. Joten jos CPU esimerkiksi suorittaa datanmuokkauskäskyn PCI-laitteen muistisolussa, sen täytyy lukea tiedot laitteesta, muokata sitä ALU:ssaan ja palauttaa tulos laitteelle. Jotta muiden aloittajien tapahtumat eivät häiritse tätä toimintoa (mikä voi johtaa tietojen eheysrikkomuksiin), pääsilta suorittaa sen estettynä toimintona - LOCK#-väyläsignaali syötetään koko toiminnan ajan. Perinteiset PCI-laitteet (ei sillat) eivät käytä (tai tuota) tätä signaalia millään tavalla; sitä käyttävät vain sillat välimiesmenettelyn ohjaamiseen.

Laitteistokeskeytykset PC-yhteensopivissa tietokoneissa

PCI-laitteet pystyvät signaloimaan asynkronisia tapahtumia keskeytyksiä käyttämällä. PCI-väylällä on saatavilla neljän tyyppistä keskeytyssignalointia:

- perinteinen langallinen signalointi INTx-linjojen kautta;

- energianhallintatapahtumien langallinen signalointi PME#-linjan kautta;

- signalointi viesteillä - MSI;

- ilmoittaa vakavasta virheestä SERR#-linjalla.

Tämä luku kattaa kaikki näistä signalointityypeistä sekä yleiskuvan laitteiston keskeytystuesta PC-yhteensopivissa tietokoneissa.

Laitteistokeskeytykset PC-yhteensopivissa tietokoneissa

Laitteistokeskeytykset varmistavat, että prosessori vastaa tapahtumiin, jotka tapahtuvat asynkronisesti suoritettavan ohjelmakoodin suhteen. Muista, että laitteistokeskeytykset jaetaan peitettäviin ja ei-maskeoitaviin. Vastaanotettuaan keskeytyssignaalin x86-prosessori keskeyttää nykyisen käskyvirran suorittamisen, tallentaa tilan (liput ja paluuosoite) pinoon ja suorittaa keskeytyskäsittelyn. Tietty käsittelyprosessi valitaan keskeytystaulukosta keskeytysvektorilla - tämän taulukon elementin yksitavuisella numerolla. Keskeytysvektori tuodaan prosessorille eri tavoilla: ei-maskattavalle keskeytykselle se on kiinteä, maskoitaville keskeytyksille se raportoidaan erityisellä keskeytysohjaimella. Laitteistokeskeytusten lisäksi x86-prosessoreissa on myös sisäisiä keskeytyksiä - poikkeuksia, jotka liittyvät käskyjen suorittamisen erityistapauksiin ja ohjelmistokeskeytuksiin. Poikkeuksissa vektorin määrittää itse erikoisehto, ja Intel varaa ensimmäiset 32 vektoria (0-31 tai 00-1Fh) poikkeuksia varten. Ohjelmistokeskeytyksessä vektorin numero sisältyy itse käskyyn (ohjelmistokeskeytykset ovat vain erityinen tapa kutsua proseduureja numeron perusteella, jolloin pinoon tallennetaan ensin lippurekisteri). Kaikki nämä keskeytykset käyttävät samaa 256 mahdollisen vektorin joukkoa. Historiallisesti laitteistokeskeytyksiä varten käytetyt vektorit ovat päällekkäisiä BIOS- ja DOS-palvelukutsuissa käytettyjen poikkeusvektorien ja ohjelmistokeskeytysvektorien kanssa. Siten useille vektorinumeroille keskeytystaulukon viittaaman proseduurin täytyy ensin sisältää ohjelmakoodi, joka määrittää, miksi se kutsuttiin: poikkeuksen, laitteistokeskeytyksen tai jonkin järjestelmäpalvelun kutsumiseksi. Siten proseduuri, joka todella varmistaa prosessorin vastauksen samaan asynkroniseen tapahtumaan, kutsutaan vasta keskeytyslähteen tunnistamiseen liittyvien toimien sarjan jälkeen. Huomaa myös tässä, että samaa keskeytysvektoria voivat käyttää useat oheislaitteet - tämä on ns. jaettu keskeytyskäyttö, jota käsitellään yksityiskohtaisesti alla.

Keskeytyspalvelurutiinin kutsuminen prosessorin todellisissa ja suojatuissa tiloissa on merkittävästi erilaista:

- reaalitilassa keskeytystaulukko sisältää 4-tavuisia kaukoosoittimia (segmentti ja offset) vastaaviin proseduureihin, joita kutsutaan etäkutsulla (Call Far ennalta tallennetuilla lipuilla). Taulukon koko (256 × 4 tavua) ja sijainti (osoitteesta 0 alkaen) ovat kiinteät;

- Suojatussa tilassa (ja erityistapauksessaan V86-tilassa) taulukko sisältää 8-tavuisia keskeytyskuvauksia, jotka voivat olla keskeytysportteja, trap-portteja tai tehtäväportteja. Taulukon kokoa voidaan pienentää (enintään - 256 × 8 tavua), taulukon sijainti voi muuttua (määritetään prosessorin IDT-rekisterin sisällöstä). Keskeytyksen käsittelijän koodin on oltava vähintään yhtä etuoikeutettu kuin keskeytetyn tehtäväkoodin (muuten laukeaa suojauspoikkeus). Tästä syystä keskeytyskäsittelijöiden on suoritettava käyttöjärjestelmän ydintasolla (nolla käyttöoikeustasolla). Oikeustason muuttaminen käsittelijää kutsuttaessa lisää aikaa pinon uudelleenmäärittelyyn. Tehtävän vaihtamista aiheuttavat keskeytykset (Task Gaten kautta) käyttävät huomattavasti aikaa kontekstin vaihtamiseen - prosessorirekisterien purkamiseen vanhan tehtävän tilasegmenttiin ja niiden lataamiseen uuden tilasegmentistä.

Suojatun tilan käyttöjärjestelmissä laitteistokeskeytyksiä varten käytetyt vektorinumerot eroavat reaalitilan käyttöjärjestelmissä käytetyistä sen varmistamiseksi, että ne eivät ole ristiriidassa prosessoripoikkeuksissa käytettyjen vektoreiden kanssa.

Prosessori vastaa aina ei-maskoitavaan keskeytykseen (NMI) (jos edellisen NMI:n huolto on valmis); Tämä keskeytys vastaa kiinteää vektoria 2. Ei-maskoitavia keskeytyksiä PC-tietokoneissa käytetään signaloimaan kohtalokkaat laitteistovirheet. Signaali NMI-linjalle tulee muistin ohjauspiireistä (pariteetti tai ECC), ISA-väylän ohjauslinjoista (IOCHK) ja PCI-väylästä (SERR#). NMI-signaali estetään ennen prosessoriin tuloa asettamalla portin 070h bitti 7 arvoon 1, yksittäiset lähteet otetaan käyttöön ja tunnistetaan portin 061h biteillä:

- bitti 2 R/W - ERP - lupa ohjata PCI-väylän RAM-muistia ja SERR#-signaalia;

- bitti 3 R/W - EIC - ISA-väylän ohjausresoluutio;

- bitti 6 R - IOCHK - ohjausvirhe ISA-väylässä (IOCHK# signaali);

- bitti 7 R - PCK - RAM-pariteettivirhe tai SERR#-signaali PCI-väylällä.

Prosessorin vastausta maskoitaviin keskeytyksiin voidaan viivyttää nollaamalla sen sisäinen IF-lippu (CLI-käsky poistaa keskeytykset käytöstä, STI-käsky ottaa käyttöön). Maskoitavia keskeytyksiä käytetään signaloimaan tapahtumia laitteissa. Kun tapahtuu tapahtuma, joka vaatii vastausta, laitesovitin (ohjain) muodostaa keskeytyspyynnön, joka lähetetään keskeytysohjaimen tuloon. Keskeytysohjaimen tehtävänä on tuoda keskeytyspyyntö prosessorille ja viestiä vektori, jolla ohjelmistokeskeytyksen käsittelymenettely valitaan.

Laitteen keskeytysrutiinin on suoritettava toimintoja laitteen huoltamiseksi, mukaan lukien sen pyynnön nollaus, jotta se voi vastata seuraaviin tapahtumiin, ja lopetuskomentojen lähettäminen keskeytysohjaimelle. Prosessointirutiinia kutsuessaan prosessori tallentaa automaattisesti kaikkien pinon lippujen arvon ja nollaa IF-lipun, mikä poistaa maskettavat keskeytykset käytöstä. Palatessaan tästä proseduurista (IRET-käskyä käyttäen) prosessori palauttaa tallennetut liput, mukaan lukien set (ennen keskeytystä) IF:n, joka taas mahdollistaa keskeytykset. Jos keskeytyskäsittelijän toiminnan aikana vaaditaan reagointia muihin keskeytyksiin (korkeampi prioriteetti), STI-käskyn on oltava käsittelijässä. Tämä pätee erityisesti pitkiin käsittelijöihin; tässä STI-ohje tulee syöttää mahdollisimman aikaisin, heti kriittisen (ei keskeytyvän) osan jälkeen. Keskeytysohjain palvelee myöhempiä saman tai alemman prioriteettitason keskeytyksiä vasta saatuaan EOI (End Of Interrupt) -komennon.

IBM PC -yhteensopivat tietokoneet käyttävät kahta päätyyppiä keskeytysohjaimia:

- PIC (Peripheral Interrupt Controller) on oheislaitteiden keskeytysohjain, ohjelmisto on yhteensopiva "historiallisen" 8259A-ohjaimen kanssa, jota käytettiin ensimmäisissä IBM PC -malleissa. IBM PC/AT:n ajoista lähtien on käytetty peräkkäistä PIC-paria, mikä mahdollistaa jopa 15 keskeytyspyyntölinjan palvelun;

- APIC (Advanced Peripheral Interrupt Controller) on edistynyt oheislaitteiden keskeytysohjain, joka on otettu käyttöön moniprosessorijärjestelmien tukemiseksi tietokoneissa, jotka perustuvat 4-5 sukupolven prosessoreihin (486 ja Pentium), ja sitä käytetään edelleen myöhemmissä prosessorimalleissa. Sen lisäksi, että se tukee moniprosessorikokoonpanoja, nykyaikainen APIC mahdollistaa käytettävissä olevien keskeytyslinjojen määrän lisäämisen ja viestimoottorin (MSI) kautta lähetettävien PCI-laitteiden keskeytyspyyntöjen käsittelemisen. APIC-ohjaimella varustetun tietokoneen on kyettävä toimimaan standardin PIC-parin kanssa yhteensopivassa tilassa. Tämä tila aktivoidaan laitteiston nollauksella (ja virran kytkemisellä), jolloin voit käyttää vanhoja OS- ja MS DOS -sovelluksia, jotka eivät tunne APIC:tä ja moniprosessointia.

Perinteinen menetelmä keskeytyspyyntöjen generoimiseksi käyttämällä PIC-paria on esitetty alla olevassa kuvassa.

Keskeytysohjaimen tulot vastaanottavat pyyntöjä järjestelmälaitteilta (näppäimistö, järjestelmäajastin, CMOS-ajastin, apuprosessori), emolevyn oheisohjaimista ja laajennuskorteilta. Perinteisesti kaikki pyyntölinjat, joita luetellut laitteet eivät käytä, ovat kaikissa ISA/EISA-väyläpaikoissa. Nämä linjat on nimetty IRQx ja niillä on yhteinen tarkoitus (katso taulukko alla). Jotkut näistä linjoista on varattu PCI-väylälle. Taulukossa näkyy myös keskeytysprioriteetit - pyynnöt on järjestetty laskevaan järjestykseen. Ohjaimen pyyntörivejä, prioriteettijärjestelmää ja joitain muita parametreja vastaavat vektorien määrät asetetaan ohjelmoidusti ohjaimia alustettaessa. Nämä perusasetukset pysyvät perinteisinä ohjelmistojen yhteensopivuuden kannalta, mutta eroavat toisistaan reaalitilan ja suojatun tilan käyttöjärjestelmien välillä. Esimerkiksi Windows-käyttöjärjestelmässä isäntä- ja orjaohjaimien perusvektorit ovat 50h ja 58h, vastaavasti.

| Nimi (numero 1) | Vektori 2 | Vektori 3 | Ohjain/naamio | Kuvaus |

| NMI | 02h | |||

| IRQ0 | 08h | 50h |

#1/1h |

Kanavan ohjaus, muistin pariteetti (XT:ssä - apuprosessori) |

| IRQ1 | 09h | 51h |

#1/2h |

Näppäimistö |

| IRQ2 | 0 Ah | 52h |

#1/4h |

XT - vara, AT - ei saatavilla (IRQ8-IRQ15-kaskadi on kytketty) |

| IRQ8 | 70h |

58h |

#2/1h |

CMOS RTC - Reaaliaikainen kello |

| IRQ9 | 71h |

59h |

#2/2h |

Varata |

| IRQ10 | 72h |

5 Ah |

#2/4h |

Varata |

| IRQ11 | 73h |

5 Bh |

#2/8h |

Varata |

| IRQ12 | 74h |

5 Ch |

#2/10h |

PS/2-hiiri (varaus) |

| IRQ13 | 75h |

5Dh |

#2/20h |

Matemaattinen apuprosessori |

| IRQ14 | 76h |

5 Eh |

#2/40h |

HDC - HDD-ohjain |

| IRQ15 | 77h |

5Fh |

#2/80h |

Varata |

| IRQ3 | 0 Bh |

52h |

#1/4h |

COM2, COM4 |

| IRQ4 | 0 Ch |

53h |

#1/10h |

COM1, COM3 |

| IRQ5I | 0Dh |

54h |

#1/20h |

XT - HDC, AT - LPT2, Ääni (varaus) |

| IRQ6 | 0 Eh |

55h |

#1/40h |

FDC - float drive -ohjain |

| IRQ7 | 0Fh |

56h |

#1/80h |

LPT1 - tulostin |

*1 Keskeytyspyyntöjä 0, 1, 8 ja 13 ei lähetetä laajennusväylille.

*2 Vektorinumerot näytetään käytettäessä todellisessa prosessoritilassa.

*3 Vektorinumerot näytetään, kun työskentelet Windows-käyttöjärjestelmässä.

Jokaiselle laitteelle, joka tarvitsee keskeytyksiä toimiakseen, on annettava oma keskeytysnumeronsa. Keskeytysnumeroiden määritykset tehdään kahdelta puolelta: ensin keskeytyksiä vaativa sovitin on konfiguroitava käyttämään tiettyä väylälinjaa (joko hyppyjohdin tai ohjelmisto). Toiseksi sovitinta tukevalle ohjelmistolle on ilmoitettava käytettävä vektorinumero. PnP-järjestelmä ISA- ja PCI-väylille voi osallistua keskeytysten määrittämiseen. Erityisiä CMOS-asetusparametreja käytetään pyyntölinjojen jakamiseen väylien välillä. Nykyaikaisissa käyttöjärjestelmissä on mahdollisuus muuttaa CMOS-asennuksen kautta tehtyjen pyyntöjen kohdentamista.

Kun keskeytysjärjestelmä on konfiguroitu (keskeytysohjain on alustettu, pyyntörivit osoitetaan laitteille ja osoittimet prosessointiproseduuriin on asetettu), maskattavat laitteistokeskeytykset käsitellään seuraavasti:

- keskeytystapahtuman yhteydessä laite herättää sille osoitetun keskeytyspyyntörivin;

- ohjain vastaanottaa pyyntösignaalit keskeytyslähteistä (IRQx-signaalit) ja, jos on peittämätön pyyntö, lähettää yleisen keskeytyspyyntösignaalin (INTR-signaalin) x86-prosessorille;

- prosessori vastaa pyyntöön (kun keskeytykset IF-lipulla ovat käytössä) tallentaa pinoon lippurekisterin sisällön ja paluuosoitteen, minkä jälkeen se generoi INTA (Interrupt Acknowledge) -väyläsyklin, joka toimitetaan keskeytysohjain;

- sillä hetkellä, kun INTA-signaali vastaanotetaan, keskeytysohjain tallentaa pyyntötulojensa tilan - tähän hetkeen mennessä niiden tila on voinut muuttua: uusia pyyntöjä saattaa ilmestyä tai pyyntö "kärsimättömältä" laitteelta voi kadota. Ohjain analysoi saapuvat pyynnöt ohjelmoidun prioriteettimallin mukaisesti ja lähettää prosessorille keskeytysvektorin, joka vastaa korkeimman prioriteetin peittämätöntä pyyntöä, joka on läsnä ohjaimen tulossa INTA-väyläkomennon antamishetkellä. Samanaikaisesti ohjain suorittaa myös joitain toimintoja vahvistetun prioriteettipolitiikan mukaisesti ottaen huomioon, mikä vektori lähetettiin (mikä pyynnöistä meni palveluun);

- Vastaanotettuaan keskeytysvektorin prosessori kutsuu vastaavan keskeytyksenkäsittelyproseduurin numerollaan. Jos tiettyä keskeytysvektoria ei käytetä vain laitteistokeskeytyksiä, vaan myös poikkeuksia ja/tai ohjelmistokeskeytyksiä varten, rutiinin on ensin määritettävä, mikä näistä tyypeistä on tapahtuma. Tätä varten menettely voi ottaa yhteyttä PIC-ohjaimeen (lukea ISR-rekisteri) ja analysoida prosessorirekisterien tilaa. Lisävaiheita harkitaan siinä tapauksessa, että laitteistokeskeytys havaitaan;

- Keskeytyksen käsittelyprosessin tulee tunnistaa keskeytyksen lähde - määrittää keskeytyksen aiheuttanut laite. Jos useat laitteet käyttävät yhteisesti tiettyä pyyntönumeroa (ja siten vektoria), keskeytyksen lähde voidaan tunnistaa vain peräkkäisellä pääsyllä kunkin laitteen rekistereihin. Tässä tapauksessa tulee ottaa huomioon mahdollisuus vastaanottaa pyyntöjä usealta laitteelta samanaikaisesti tai käsiteltäessä keskeytystä yhdeltä niistä;

- menettelyn tulee huoltaa keskeytyslähdelaitetta - suorittaa "hyödyllisiä" toimintoja, jotka liittyvät laitteen ilmoittamaan tapahtumaan. Tämän palvelun tulisi myös varmistaa, että keskeytyspyyntösignaali tästä laitteesta poistetaan. Jaetuissa keskeytyksissä voi olla useita lähteitä, ja ne kaikki vaativat ylläpitoa;

- jos keskeytyskäsittely vie merkittävästi aikaa, jonka aikana järjestelmän on vastattava korkeamman prioriteetin pyyntöihin, niin kriittisen osan jälkeen käsittelijään tulee STI-käsky, joka asettaa prosessoriin keskeytyksen sallimislipun (IF) . Tästä hetkestä lähtien sisäkkäiset keskeytykset ovat mahdollisia, jotka keskeyttävät tietyn käsittelijän työn toisella, korkeamman prioriteetin proseduurilla;

- keskeytyksen käsittelyproseduurin tulee lähettää ohjaimelle komento keskeytyskäsittelyn loppuun saattamiseksi EOI (End Of Interrupt), jonka avulla ohjain sallii myöhemmän signaalin vastaanoton huolletusta tulosta ja alemman prioriteetin tuloista. Tämä on tehtävä keskeytyssignaalin poistamisen jälkeen huolletuista laitteista, muuten ohjain lähettää toisen pyynnön EOI:n jälkeen. Keskeytyskäsittelijän, jolle on tullut pyyntö orjaohjaimelta, on lähetettävä EOI sekä orja- että isäntäohjaimelle. Käsittelijän osion EOI-käskyn antamisesta lopetukseen (IRET-käsky) tulee olla keskeytymätön, eli se on kriittinen osa. Jos käsittelijä salli sisäkkäiset keskeytykset, CLI-käskyn, joka estää keskeytykset, on oltava läsnä ennen EOI-komennon antamista;

- keskeytyskäsittely viimeistellään IRET-käskyllä, jolla prosessori palaa suorittamaan keskeytettyä käskyvirtaa haettuaan aiemmin lippurekisterin sisällön pinosta. Tässä tapauksessa laitteistokeskeytykset otetaan uudelleen käyttöön.

Tämä sekvenssi on kuvattu tavallisen keskeytysohjaimen (PIC) yhteydessä, APIC-järjestelmät muuttavat tapaa, jolla keskeytysvektori välitetään ohjaimesta prosessoriin, ja MSI-keskeytykset muuttavat tapaa, jolla signaali välitetään laitteesta APIC-ohjaimeen. . Nämä vivahteet kuvataan seuraavissa osissa.

Yleistä tietoa

PCI-sillat (PCI Bridge) ovat erikoislaitteita PCI- (ja PCI-X)-väylien yhdistämiseen toisiinsa ja muihin väyliin. Host Bridgeä käytetään PCI:n liittämiseen tietokoneen keskelle (järjestelmämuisti ja prosessori). Pääsillan "kunniallinen velvollisuus" on tuottaa kutsuja konfigurointitilaan keskusprosessorin ohjauksessa, jolloin isäntä (keskusprosessori) voi määrittää koko PCI-väyläalijärjestelmän. Järjestelmässä voi olla useita pääsiltoja, mikä mahdollistaa tehokkaan tiedonsiirron keskuksen kanssa suuremmalle määrälle laitteita (yhdessä väylässä olevien laitteiden määrä on rajoitettu). Näistä linja-autoista yksi on ehdollisesti pääbussiksi (bussi 0).

PCI-vertaissiltoja (PeertoPeer Bridge) käytetään lisäämään PCI-väyliä. Nämä sillat tuovat aina ylimääräistä tiedonsiirtoa, joten laitteiden ja keskittimen välisen viestinnän tehokas suorituskyky heikkenee jokaisen tielle tulevan sillan myötä.

PCMCIA-, CardBus-, MCA-, ISA/EISA-, X-Bus- ja LPC-väylien yhdistämiseen käytetään erityisiä siltoja, jotka sisältyvät emolevyn piirisarjoihin tai ovat erillisiä PCI-laitteita (siruja). Nämä sillat muuntavat liittämiensä väylien rajapinnat, synkronoivat ja puskuroivat tiedonvaihtoa.

Jokainen silta on ohjelmoitava - sille on annettu osoitealueet muistissa ja I/O-tilat, jotka on varattu laitteille sen väylissä. Jos nykyisen tapahtuman CPU-osoite sillan yhdellä väylällä (puolella) viittaa vastakkaisen puolen väylään, silta kääntää tapahtuman sopivalle väylälle ja varmistaa väyläprotokollan neuvottelun. Siten joukko PCI-siltoja suorittaa pyyntöjen reitityksen liittyviä väyliä pitkin. Jos järjestelmässä on useita pääsiltoja, niin päästä päähän -reititys eri väylillä olevien laitteiden välillä ei välttämättä ole mahdollista: pääsillat voivat olla yhteydessä toisiinsa vain muistiohjaimen runkopolkujen kautta. Kaikentyyppisten PCI-tapahtumien kääntämisen tukeminen pääsiltojen kautta osoittautuu tässä tapauksessa liian monimutkaiseksi, eikä sitä siksi vaadi PCI-spesifikaatiossa. Siten kaikki aktiiviset laitteet kaikilla PCI-väylillä voivat käyttää järjestelmämuistia, mutta vertaisviestinnän mahdollisuus voi riippua siitä, kuuluvatko nämä laitteet johonkin PCI-väylään.

PCI-siltojen käyttö tarjoaa seuraavat mahdollisuudet:

- liitettyjen laitteiden mahdollisen määrän lisääminen, väylän sähköisten eritelmien rajoitusten ylittäminen;

- PCI-laitteiden jakaminen segmentteihin - PCI-väylät - eri ominaisuuksilla: bittisyvyys (32/64 bittiä), kellotaajuus (33/66/100/133 MHz), protokolla (PCI, PC-X Mode 1, PCI-X Mode) 2, PCI Express). Jokaisella väylällä kaikki tilaajat ovat yhtä suuria kuin heikoin osallistuja; laitteiden oikea järjestely väylissä antaa sinun käyttää laitteiden ja emolevyn ominaisuuksia mahdollisimman tehokkaasti;

- segmenttien järjestäminen "kuumien" laitteiden liittämisellä/irrottamalla;

- tapahtumien samanaikainen rinnakkainen toteuttaminen eri väylillä sijaitsevilta aloittajilta.

Jokainen PCI-silta yhdistää vain kaksi väylää: ensisijaisen väylän, joka sijaitsee lähempänä hierarkian huippua, toisioväylän kanssa; Siltaliitäntöjä, joilla se on kytketty näihin väyliin, kutsutaan ensisijaiseksi ja toissijaiseksi. Vain puhtaasti puumainen konfiguraatio on sallittu, eli kaksi väylää on yhdistetty toisiinsa vain yhdellä sillalla, eikä siltoja ole "silmukoita". Tietyn sillan toissijaiseen rajapintaan muiden siltojen kautta kytkettyjä väyliä kutsutaan alisteisiksi väyliksi. PCI-sillat muodostavat PCI-väylien hierarkian, jonka yläosassa on isäntäväylä, numeroitu nolla, yhdistettynä isäntäsiltaan. Jos pääsiltoja on useita, niin niiden linja-autoista (samanarvoinen) pääsilta on se, jolle on annettu nollanumero.

Sillan on suoritettava useita pakollisia toimintoja:

- huoltaa sen toissijaiseen rajapintaan kytkettyä väylää:

- suorittaa sovittelun - vastaanottaa REQx#-pyyntösignaalit väyläisänniltä ja antaa heille oikeus ohjata väylää GNTx#-signaaleilla

- pysäköi väylä - lähetä GNTx#-signaali jollekin laitteelle, kun mikään isäntä ei vaadi väylän ohjausta;

- generoi tyypin 0 konfigurointijaksoja, joissa muodostetaan yksittäisiä IDSEL-signaaleja osoitettavalle PCI-laitteelle;

- "vetää" ohjaussignaalit korkealle tasolle;

- määrittää kytkettyjen laitteiden ominaisuudet ja valita niitä tyydyttävä väylän toimintatila (taajuus, bittisyvyys, protokolla);

- generoi laitteiston nollauksen (RST#) nollaamalla ensisijaisesta rajapinnasta ja komennolla raportoimalla valitusta tilasta erityisellä hälytyksellä.

- ylläpitää karttoja resursseista, jotka sijaitsevat sillan vastakkaisilla puolilla;

- vastata kohdelaitteen varjolla tapahtumiin, jotka isäntä on aloittanut yhdessä rajapinnassa ja osoitettu toisessa rajapinnassa sijaitsevalle resurssille; lähettää nämä tapahtumat toiseen käyttöliittymään, joka toimii isäntänä, ja lähettää niiden tulokset todelliselle aloittajalle.

Näitä toimintoja suorittavia siltoja kutsutaan läpinäkyviksi silloiksi; Tällaisten siltojen takana olevien laitteiden kanssa työskentelyyn ei tarvita ylimääräisiä siltaohjaimia. Juuri nämä sillat on kuvattu PCI Bridge 1.1 -spesifikaatiossa, ja niille PCI-laitteina on erityinen luokka (06). Tässä tapauksessa viitataan "tasaiseen" resurssien osoitemalliin (muisti ja I/O): jokaisella laitteella on omat osoitteensa, jotka ovat yksilöllisiä (ei risteä muiden kanssa) tietyssä järjestelmässä (tietokoneessa).

On myös läpinäkymättömiä siltoja (ei läpinäkyvä silta), joiden avulla voit järjestää erilliset segmentit omilla paikallisilla osoiteavaruuksilla. Läpinäkymätön silta suorittaa osoitteenmuunnoksen (muunnoksen) tapahtumille, joissa aloittaja ja kohdelaite sijaitsevat sillan vastakkaisilla puolilla. Kaikki vastapuolen resurssit (osoitealueet) eivät välttämättä ole tavoitettavissa tällaisen sillan kautta. Läpinäkyviä siltoja käytetään esimerkiksi silloin, kun tietokoneessa on "älykäs input/output" (I20) -alijärjestelmä, jossa on oma I/O-prosessori ja paikallinen osoiteavaruus.

Yleistä tietoa

PCI-väylä sisältää aluksi mahdollisuuden määrittää automaattisesti järjestelmäresurssit (muisti- ja I/O-tilat ja keskeytyspyyntörivit). Automaattinen laitekonfigurointi (osoitteiden ja keskeytysten valinta) on tuettu BIOS- ja OS-työkaluilla; se keskittyy PnP-tekniikkaan. PCI-standardi määrittelee kullekin toiminnolle enintään 256 rekisterin (8 bitin) konfigurointitilan, jota ei ole osoitettu muisti- tai I/O-tilaan. Niihin päästään käyttämällä erityisiä väyläkomentoja Configuration Read ja Configuration Write, jotka on luotu jollakin alla kuvatuista laitteisto- ja ohjelmistomekanismeista. Tässä tilassa on alueita, joita vaaditaan kaikille laitteille ja tietyille laitteille. Tietyllä laitteella ei välttämättä ole rekistereitä kaikissa osoitteissa, mutta sen on tuettava niille osoitettujen toimintojen normaalia suorittamista. Tässä tapauksessa olemattomien rekisterien lukemisen tulee palauttaa nollia ja kirjoittaminen tulee suorittaa tyhjäkäynnillä.

Toiminnon konfigurointiavaruus alkaa vakiootsikolla, joka sisältää valmistajan, laitteen ja sen luokan tunnisteet sekä kuvauksen tarvittavista ja varatuista järjestelmäresursseista. Otsikkorakenne on standardoitu perinteisille laitteille (tyyppi 0), PCI-PCI-silloille (tyyppi 1), PCI-CardBus-silloille (tyyppi 2). Otsikkotyyppi määrittää hyvin tunnettujen rekisterien sijainnin ja niiden bittien tarkoituksen. Otsikon jälkeen voi olla laitekohtaisia rekistereitä. Laitteiden standardoituja ominaisuuksia (kykyä) varten (esimerkiksi energianhallinta) konfiguraatiotilassa on lohkoja rekistereistä, joilla on tunnettu tarkoitus. Nämä lohkot on järjestetty ketjuiksi, ensimmäiseen tällaiseen lohkoon viitataan standardiotsikossa (CAP_PTR); lohkon ensimmäisessä rekisterissä on linkki seuraavaan lohkoon (tai 0, jos tämä lohko on viimeinen). Siten ketjua skannaamalla konfigurointiohjelmisto vastaanottaa listan kaikista saatavilla olevista laitteen ominaisuuksista ja niiden sijainnista toimintokonfiguraatiotilassa. PCI 2.3 määrittelee seuraavat CAP_ID:t, joista osan tarkastelemme:

- 01 - energianhallinta;

- 02 - AGP-portti;

- 03 - VPD (Vital Product Data), tiedot, jotka tarjoavat kattavan kuvauksen laitteiden laitteiston (mahdollisesti myös ohjelmiston) ominaisuuksista;

- 04 — aukkojen ja alustan numerointi;

- 05 - MSI-keskeytykset;

- 06 - Hot Swap, hot-liitäntä Compact PCI:lle;

- 07 - PCI-X-protokollalaajennukset;

- 08 - varattu AMD:lle;

- 09 - valmistajan harkinnan mukaan (Myyjäkohtainen);

- 0Ah — virheenkorjausportti (Debug Port);

- 0Bh - PCI Hot Plug, vakiovaruste "hot plug".

PCI-X for Mode 2 -laitteissa määritystila on laajennettu 4096 tavuun; laajennetussa tilassa voi olla laajennettuja kiinteistökuvauksia.

Kovan nollauksen (tai virran kytkemisen) jälkeen PCI-laitteet eivät reagoi muistin ja I/O-tilan käyttöön, ja ne ovat käytettävissä vain asetusten lukemiseen ja kirjoittamiseen. Näissä toiminnoissa laitteet valitaan yksittäisten IDSEL-signaalien avulla ja rekistereitä lukemalla konfigurointiohjelmisto oppii resurssivaatimuksista ja mahdollisista. Kun määritysohjelma on varannut resurssit (POST- tai käyttöjärjestelmän käynnistyksen aikana), konfigurointiparametrit (perusosoitteet) kirjoitetaan laitteen konfigurointirekistereihin. Vasta tämän jälkeen laitteet (tarkemmin sanottuna toiminnot) asetetaan biteille, joiden avulla ne voivat vastata komentoihin päästäkseen muistiin ja I/O-portteihin sekä ohjata itse väylää. Jotta aina löydettäisiin toimiva konfiguraatio, kaikkien korttien käyttämien resurssien on oltava siirrettävissä tiloissaan. Monitoimilaitteissa jokaisella toiminnolla on oltava oma konfigurointitila. Laite voi yhdistää samat rekisterit sekä muistiin että I/O-tilaan. Tässä tapauksessa molempien kuvaajien on oltava konfiguraatiorekistereissään, mutta kuljettajan on käytettävä vain yhtä pääsytapaa (mieluiten muistin kautta).

Määritystilan otsikko kuvaa kolmentyyppisten osoitteiden tarpeita:

- rekisterit I/O-tilassa);

- I/O-rekisterit on yhdistetty muistiin (Memory Mapped I/O). Tämä on muistialue, johon on päästävä tiukasti vaihdon aloittajan pyyntöjen mukaisesti. Näihin rekistereihin pääsy voi muuttaa oheislaitteiden sisäistä tilaa;

- muistia, joka mahdollistaa esihaettavan muistin. Tämä on muistialue, jossa "ylimääräinen" lukeminen (käyttämättömillä tuloksilla) ei johda sivuvaikutuksiin, kaikki tavut luetaan BE#-signaaleista riippumatta ja yksittäisten tavujen kirjoitus voidaan sillata (eli se on muistia puhtaimmassa muodossaan).

Osoitevaatimukset ilmoitetaan perusosoiterekistereissä - BAR (Base Address Register). Konfigurointiohjelma voi myös määrittää tarvittavien alueiden koon. Tätä varten sen on laitteiston nollauksen jälkeen luettava ja tallennettava perusosoitteiden arvot (nämä ovat oletusosoitteita), kirjoitettava FFFFFFFFh jokaiseen rekisteriin ja luettava niiden arvo uudelleen. Vastaanotetuissa sanoissa sinun on nollattava tyypin dekoodausbitit (bitit muistille ja bitit I/O:lle), käännettävä ja lisättävä tuloksena oleva 32-bittinen sana - tuloksena on alueen pituus (ohita porttien bitit ). Menetelmä olettaa, että alueen pituus ilmaistaan muodossa 2n ja alue on luonnollisesti kohdistettu. Vakiootsikko sisältää jopa 6 perusosoiterekisteriä, mutta 64-bittistä osoitusta käytettäessä kuvattujen lohkojen määrä vähenee. Käyttämättömien BAR-rekisterien tulee aina palauttaa nollia luettaessa.

PCI tukee vanhoja laitteita (VGA, IDE), jotka ilmoittavat olevansa sellaisiksi otsikossa olevan luokkakoodin avulla. Niiden perinteisiä (kiinteitä) porttiosoitteita ei ilmoiteta konfiguraatiotilassa, mutta heti kun portin pääsyn salliva bitti on asetettu, laitteet saavat vastata myös näihin osoitteisiin.

Intelin ja sen kumppaneiden kehittämä PCI Express -sarjaväylä on tarkoitettu korvaamaan rinnakkais-PCI-väylä ja sen laajennettu ja erikoistunut AGP-versio. Samanlaisista nimistään huolimatta PCI- ja PCI Express -väylillä on vain vähän yhteistä. PCI:ssä käytetty asettaa rajoituksia väylän kaistanleveydelle ja taajuudelle; PCI Expressissä käytetty sarjatiedonsiirto tarjoaa skaalautuvuuden (spesifikaatiot kuvaavat PCI Express 1x, 2x, 4x, 8x, 16x ja 32x toteutukset). Tällä hetkellä väylän nykyinen versio indeksillä 3.0

Intelin ja sen kumppaneiden kehittämä PCI Express -sarjaväylä on tarkoitettu korvaamaan rinnakkais-PCI-väylä ja sen laajennettu ja erikoistunut AGP-versio. Samanlaisista nimistään huolimatta PCI- ja PCI Express -väylillä on vain vähän yhteistä. PCI:ssä käytetty asettaa rajoituksia väylän kaistanleveydelle ja taajuudelle; PCI Expressissä käytetty sarjatiedonsiirto tarjoaa skaalautuvuuden (spesifikaatiot kuvaavat PCI Express 1x, 2x, 4x, 8x, 16x ja 32x toteutukset). Tällä hetkellä väylän nykyinen versio indeksillä 3.0

PCI-E 3.0

Marraskuussa 2010 PCI-SIG-organisaatio, joka standardoi PCI Express -teknologiaa, ilmoitti ottavansa käyttöön PCIe Base 3.0 -määrityksen.

Keskeistä eroa kahteen edelliseen PCIe-versioon voidaan pitää muunneltuna koodausmenetelmänä - nyt 8 bitin hyödyllisen tiedon sijasta 10 lähetetystä bitistä (8b/10b), 128 bittiä hyödyllistä tietoa voidaan lähettää lähetetystä 130 bitistä. bussin kautta, ts. Hyötykuormakerroin on lähes 100 %. Lisäksi tiedonsiirtonopeus on noussut 8 GT/s:iin. Muistakaamme, että tämä arvo PCIe 1.x:lle oli 2,5 GT/s ja PCIe 2.x - 5 GT/s.

Kaikki edellä mainitut muutokset johtivat väylän kaistanleveyden kaksinkertaistumiseen verrattuna PCI-E 2.x -väylään. Tämä tarkoittaa, että PCIe 3.0 -väylän kokonaiskaistanleveys 16x-kokoonpanossa saavuttaa 32 Gb/s. Ensimmäiset PCIe 3.0 -ohjaimella varustetut prosessorit olivat Ivy Bridge -mikroarkkitehtuuriin perustuvat Intel-prosessorit.

Huolimatta PCI-E 3.0:n yli kolminkertaisesta suorituskyvystä PCI-E 1.1:een verrattuna, samojen näytönohjainkorttien suorituskyky eri liitäntöjä käytettäessä ei eroa paljon. Alla oleva taulukko näyttää GeForce GTX 980:n testitulokset erilaisissa testeissä. Mittaukset tehtiin samoilla grafiikka-asetuksilla, samassa konfiguraatiossa PCI-E-väyläversio muutettiin BIOS-asetuksissa.

PCI Express 3.0 on edelleen taaksepäin yhteensopiva PCIe:n aiempien versioiden kanssa.

PCI-E 2.0

Vuonna 2007 otettiin käyttöön uusi PCI Express -väyläspesifikaatio, 2.0, jonka tärkein ero on kunkin siirtolinjan kaksinkertainen kaistanleveys kumpaankin suuntaan, ts. Näytönohjainkorteissa käytetyn PCI-E 16x suosituimman version tapauksessa nopeus on 8 Gb/s kumpaankin suuntaan. Ensimmäinen PCI-E 2.0:aa tukeva piirisarja oli Intel X38.

PCI-E 2.0 on täysin taaksepäin yhteensopiva PCI-E 1.0:n kanssa, ts. Kaikki olemassa olevat PCI-E 1.0 -laitteet voivat toimia PCI-E 2.0 -paikoissa ja päinvastoin.

PCI-E 1.1

Ensimmäinen versio PCI Express -liittymästä, joka ilmestyi vuonna 2002. Tarjosi 500 MB/s siirtonopeuden linjaa kohden.

PCI-E:n eri sukupolvien toimintanopeuksien vertailu

PCI-väylä toimii 33 tai 66 MHz taajuudella ja tarjoaa 133 tai 266 MB/s kaistanleveyttä, mutta tämä kaistanleveys jaetaan kaikkien PCI-laitteiden kesken. Taajuus, jolla PCI Express -väylä toimii, on 1,1 - 2,5 GHz, mikä antaa suorituskyvyn 2500 MHz / 10 * 8 = 250 * 8 Mbps = 250 Mbps (8 bitin datan lähettämisen redundantin koodauksen vuoksi 10 bittiä on itse asiassa lähetetyt tiedot) jokaiselle PCI Express 1.1 x1 -laitteelle yhteen suuntaan. Jos rivejä on useita, suorituskyvyn laskemiseksi arvo 250 Mb/s on kerrottava juovien lukumäärällä ja kahdella, koska PCI Express on kaksisuuntainen väylä.

| PCI Express 1.1 -kaistan määrä | Yksisuuntainen läpijuoksu | Kokonaiskapasiteetti |

| 1 | 250 Mt/s | 500 MB/s |

| 2 | 500 Mb/s | 1 Gt/s |

| 4 | 1 Gt/s | 2 Gt/s |

| 8 | 2 Gt/s | 4 Gt/s |

| 16 | 4 Gt/s | 8 Gt/s |

| 32 | 8 Gt/s | 16 Gt/s |

Huomio! Älä yritä asentaa PCI Express -korttia PCI-korttipaikkaan, ja päinvastoin, PCI-kortit eivät asennu PCI Express -aukkoon. Esimerkiksi PCI Express 1x -kortti voidaan kuitenkin asentaa ja se toimii todennäköisesti normaalisti PCI Express 8x- tai 16x -paikassa, mutta ei päinvastoin: PCI Express 16x -kortti ei sovi PCI Express 1x -paikkaan. .

PCI-väylä

32-bittinen PCI-liitin emolevyllä

64-bittinen PCI-paikka Power Macintosh G4:ssä

PCI-väylästandardi määrittelee:

- fyysiset parametrit (esimerkiksi liittimet ja signaalijohdot);

- sähköiset parametrit (esimerkiksi jännite);

- looginen malli (esim. väyläjaksotyypit, väyläosoitteet).

PCI-standardin on kehittänyt PCI Special Interest Group.

Luomisen historia

Katso mitä "PCI-väylä" on muissa sanakirjoissa:

PCI-X väylä- 64-bittinen väylä, taaksepäin yhteensopiva PCI-väylän kanssa. Aiheet tietotekniikka yleisesti FI PCI X ...

Teknisen kääntäjän opas

Kuvassa on 4 PCI Express -paikkaa: x4, x16, x1, x16, alla on tavallinen 32-bittinen PCI-paikka DFI LanParty nForce4 SLI DR PCI Express- tai PCIe- tai PCI E -emolevyllä (tunnetaan myös nimellä 3GIO 3. sukupolven I/O:lle ei pidä sekoittaa PCI:hen... Wikipedia

PCI E PCI Express PCI Express -logo Löytymisvuosi: 2002 (1.0) 15. tammikuuta 2007 (2.0) marraskuuta 2010 (Tekniset versio 3.0) Kehittäjä: Intel, PCI Special Interest Group Mitä tämä väylä korvasi: AGP, PCI X, PCI .. Wikipedia

PCI (Peripheral Component Interconnect) -tietokoneväylä. PCI DSS -standardi korttimaksujärjestelmien tietoturvaan (Payment Card Industry Data Security Standard), jota käytetään usein lyhenteenä lyhenteestä PCI. PCI... ... Wikipedia

Tällä termillä on muita merkityksiä, katso PCI (merkityksiä) ... Wikipedia

Tämä artikkeli on kirjoitettava kokonaan uudelleen. Keskustelusivulla saattaa olla selityksiä... Wikipedia PCI Express (oheiskomponenttien välinen yhteys express) - Kolmannen sukupolven järjestelmätulo-/lähtöväylä, aiemmin nimeltään 3GIO (3rd Generation I/O), joka korvasi tavallisen PCI-väylän ja josta tuli pääliitäntä tietokoneen sisällä olevien komponenttien liittämiseen. PCI Express -väylä tukee yhteensopivuutta...

Sanasto Samsungin kotitalous- ja tietokonelaitteille PCI - (IlmaistaSanasto Samsungin kotitalous- ja tietokonelaitteillePCIe E) – sarja, yleisväylä julkistettiin ensimmäisen kerran 22. heinäkuuta 2002

vuosi. Is, yleistä väylä emolevyn kaikille solmuille, jossa kaikki siihen liitetyt laitteet ovat rinnakkain. Tuli vaihtamaan vanhentunut rengas PCI ja sen muunnelmia AGP väylän suorituskyvyn kasvaneiden vaatimusten vuoksi ja kyvyttömyydestä parantaa jälkimmäisen nopeutta kohtuullisin kustannuksin.

Rengas toimii mm kytkin yksinkertaisesti lähettämällä signaalin pisteestä toiseen muuttamatta sitä. Tämä mahdollistaa ilman selvää nopeuden menetystä minimaalisilla muutoksilla ja virheillä lähettää ja vastaanottaa signaalia.

Tiedot bussista kulkevat yksinkertainen(full duplex), eli samanaikaisesti molempiin suuntiin samalla nopeudella ja signaali linjojen mukaan virtaa jatkuvasti, vaikka laite olisi pois päältä (tasavirtana tai nollien bittisignaalina).

Synkronointi rakennettu redundantilla menetelmällä. Eli sen sijaan 8-bittinen tiedot välitetään 10 bittiä, joista kaksi on virallinen (20% ) ja palvele tietyssä järjestyksessä majakat varten synkronointi kellogeneraattorit tai virheiden tunnistamisessa. Siksi ilmoitettu nopeus yhden rivin sisään 2,5 Gbps, on itse asiassa yhtä suuri kuin noin 2,0 Gbps todellinen.

Ravitsemus jokainen väylän laite valitaan erikseen ja säädellään tekniikalla ASPM (Active State Power Management). Se sallii, kun laite on käyttämättömänä (lähettämättä signaalia) laskea sen kellogeneraattoria ja laita bussi tilaan vähentynyt energiankulutus. Jos signaalia ei vastaanoteta muutamassa mikrosekunnissa, laite pidetään passiivisena ja vaihtaa tilaan odotuksia(aika riippuu laitetyypistä).

Nopeusominaisuudet kahteen suuntaan Sanasto Samsungin kotitalous- ja tietokonelaitteille Express 1.0 :*

1 x PCI-E~ 500 Mbps

4x PCI-E~ 2 Gbps

8 x PCI-E~ 4 Gbps

16x PCI-E~ 8 Gbps

32x PCI-E~ 16 Gbps

*Tiedonsiirtonopeus yhteen suuntaan on 2 kertaa pienempi kuin nämä ilmaisimet

15. tammikuuta 2007, PCI-SIG julkaisi päivitetyn spesifikaation nimeltä PCI-Express 2.0

Suurin parannus tapahtui 2 kertaa suurempi nopeus tiedonsiirto ( 5,0 GHz, vastaan 2,5 GHz vanhassa versiossa). Myös parantunut point-to-point-viestintäprotokolla(pisteestä pisteeseen), muokattu ohjelmistokomponentti ja lisätty järjestelmä ohjelmiston seuranta renkaan nopeuden mukaan. Samalla se säilytettiin yhteensopivuus protokollaversioiden kanssa PCI-E 1.x

Standardin uudessa versiossa ( Sanasto Samsungin kotitalous- ja tietokonelaitteilleExpress 3.0 ), tärkein innovaatio on muutettu koodausjärjestelmä Ja synkronointi. Sijasta 10 bittiä järjestelmät ( 8-bittinen tiedot, 2 bittiä virallinen), sovelletaan 130 bittiä (128 bittinen tiedot, 2 bittiä virallinen). Tämä vähentää tappioita nopeudessa 20 % - ~1,5 %. Suunnitellaan myös uudelleen synkronointialgoritmi lähetin ja vastaanotin, parannettu PLL(vaihelukittu silmukka).Tiedonsiirtonopeus odotetaan kasvavan 2 kertaa(verrattuna PCI-E 2.0), samalla yhteensopivuus säilyy aiempien versioiden kanssa PCI-Express.

Tällä hetkellä monimutkaisen elektroniikan alalla on käynnissä uusien teknologioiden aktiivinen ja nopea käyttöönotto, minkä seurauksena jotkut järjestelmäkomponentit voivat vanhentua, eikä niitä voida päivittää jne.

Tältä osin on tarpeen liittää niihin erilaisia lisäosia ja lisävarusteita, mikä vaatii usein tiettyjä sovittimia.

Tässä artikkelissa tarkastellaan pci-e pci -sovitinta, miten se toimii ja mitä ominaisuuksia sillä on.

Määritelmä

Mikä laite tämä on ja mihin se on tarkoitettu? Tarkkaan ottaen tämä on tulo- ja lähtöväylä, joka liitetään henkilökohtaiseen tietokoneeseen.

Itse tähän väylään, eli sovittimeen, voit liittää tietyn määrän ulkoisia oheislaitteita (joka vaihtelee kokoonpanon mukaan).

Nämä oheislaitteet liitetään tietokoneeseen sarjaliitännän avulla.

Tällaisen laitteen pääominaisuus on sen suorituskyky.

Juuri tämä luonnehtii (yleensä) työn laatua, sen nopeutta sekä tietokoneen ja tällä tavalla kytkettyjen elementtien suorituskykyä.

Suorituskyky on ilmaistu liitäntälinjojen lukumääränä (1 - 32).

Tästä pääominaisuudesta riippuen tämän laitteen hinta voi vaihdella merkittävästi. Eli mitä parempi tämä ominaisuus on (mitä korkeampi indikaattori), sitä korkeampi on tällaisen laitteen hinta. Lisäksi paljon riippuu valmistajan tilasta, laitteiden luotettavuudesta ja kestävyydestä. Keskimäärin hinta alkaa 250-500 ruplasta (aasialaisille tuotteille, joilla on pieni kaistanleveys), jopa 2000 ruplaan (eurooppalaisille ja japanilaisille laitteille, joilla on suuri kaistanleveys).

Tekniset tiedot

Tekniseltä kannalta tällainen laite sisältää kolme komponenttia:

Yllä kirjoitettiin laitteen suorituskyvyn poikkeuksellisesta merkityksestä sen normaalille toiminnalle.

Mikä on läpimenokyky? Vastataksesi tähän kysymykseen sinun on ymmärrettävä tällaisen sovittimen toimintaperiaate.

Se pystyy samanaikaiseen kaksisuuntaiseen (kortista oheislaitteeseen ja oheislaitteesta kortille) laiteliitäntään.

Tässä tapauksessa tiedonsiirto voi tapahtua yhden tai useamman rivin yli.

Mitä enemmän tällaisia linjoja, sitä vakaammin laite toimii, sitä suurempi on sen suorituskyky ja sitä nopeampi oheislaite.

Tärkeää! Linjojen lukumäärästä riippuen laitteella voi olla erilaisia kokoonpanoja: x1, x2, x4, x8, x12, x16, x32. Numero ilmaisee suoraan kahdensuuntaisen samanaikaisen tiedonsiirron kaistojen lukumäärän. Jokainen näistä nauhoista koostuu kahdesta parista johtoja (lähettämistä varten kahteen suuntaan).

Kuten kuvauksesta voidaan nähdä, tämä kokoonpano vaikuttaa merkittävästi laitteen hintaan.

Mutta mitä käytännön merkitystä sillä on, onko todella järkevää kuluttaa ylimääräistä laitetta?

Tämä riippuu suoraan siitä, kuinka monta aiot muodostaa yhteyden emolevyyn - mitä enemmän niitä on, sitä suuremman kaistanleveyden laite tarvitsee ylläpitääkseen tietokoneen vakaan toiminnan.

Salaus

Tällaisessa tiedonsiirtojärjestelmässä käytetään erityistä järjestelmää suojaamaan sitä vääristymiseltä ja katoamiselta.

Tämä suojausmenetelmä on merkitty 8V/10V.

Asia on siinä, että 8 bitin tarvittavan tiedon siirtämiseksi on käytettävä 2 lisäpalvelubittiä turvallisuuden ja vääristymisen estämiseksi.

Tällaisen sovittimen toimiessa 20 % huoltotiedoista siirtyy jatkuvasti tietokoneelle, joka ei kanna mitään kuormaa ja jota käyttäjä ei tarvitse. Mutta juuri tämä varmistaa väylän ja oheislaitteiden vakauden, vaikka se lataa (tosin hyvin vähän).

Tarina

2000-luvun alussa AGP-laajennuspaikkaa käytettiin aktiivisesti, ja sen avulla .

Mutta jossain vaiheessa saavutettiin teknisesti suurin mahdollinen suorituskyky ja tarve luoda uudenlainen sovitin.

Ja pian PCI-E ilmestyi - se oli 2002.

Välittömästi tarvittiin sovitin, joka mahdollistaisi uusien grafiikkaratkaisujen asentamisen vanhentuneeseen laajennuspaikkaan tai päinvastoin.

Siksi vuonna 2002 monet kehittäjät ja valmistajat alkoivat vakavasti luoda tällaista sovitinta.

Tuolloin laitteessa oli yksi tärkeä ominaisuus - kyky päivittää PC, kuluttamalla siihen minimaalisia summia, koska emolevyn vaihtamisen sijaan riitti suhteellisen edullinen sovitin.

Mutta kehitys ei onnistunut, koska ne maksoivat tuolloin melkein saman verran kuin ensimmäiset sovittimet, ja siksi oli tarpeen kehittää yksinkertaisempi sovitinkokoonpano.

Mielenkiintoista on, että valmistajat ovat myös jatkuvasti lisänneet tällaisten laitteiden suorituskykyä. Jos ensimmäisissä kokoonpanoissa se oli korkeintaan 8 Gb/s, niin toisessa se oli jo 16 Gb/s ja kolmannessa 64 Gb/s. Tämä vastasi oheislaitteiden modernisoinnista johtuvien lisääntyvien työkuormien vaatimuksiin.

Samanaikaisesti eri siirtonopeuksilla varustetut paikat ovat yhteensopivia kaikkien alemman "suuren nopeuden" tason laitteiden kanssa.

Eli jos liität toisen tai ensimmäisen sukupolven grafiikkaalustan kolmannen sukupolven korttipaikkaan, paikka vaihtaa automaattisesti eri nopeustilaan, joka vastaa yhdistettyä laitetta.

Erot PCI:n ja PCI-E:n välillä

Mitä erityisiä eroja näillä kahdella kokoonpanolla on?

Teknisiltä ja toiminnallisilta ominaisuuksiltaan PCI on samanlainen kuin AGP, kun taas PCI-E on pohjimmiltaan uusi kehitys.

PCI tarjoaa rinnakkaisen tiedonsiirron, kun taas PCI-E tarjoaa sarjamuotoisen tiedonsiirron, mikä saavuttaa huomattavasti suuremmat tiedonsiirtonopeudet ja -suorituskyky, jopa sovittimen käyttö huomioon ottaen.

Miksi sitä tarvitaan?

Miksi tarvitset tällaista sovitinta ja mihin sitä voidaan käyttää?

Sinun on ymmärrettävä, että useimmat käyttäjät tekevät ilman tätä laitetta, koska sitä ei tarvita edes vanhoissa tietokoneissa, jotka ovat alttiina huomattavalle kulumiselle.

Tämä on lisälaite, joka joissakin tapauksissa parantaa tietokoneesi toimivuutta, mutta jota tavallinen käyttäjä voi helposti tulla ilman.

Itse asiassa tällaisen sovittimen käyttö tarjoaa vain yhden pääedun - mahdollisuuden liittää muistikorttiin tietty määrä oheislaitteita, kun taas on mahdotonta kytkeä niin monia niistä suoraan. Esimerkiksi tällä tavalla voit liittää erillisen videon tai päävideon lisäksi.

Se on myös varsin kätevä vaihtoehto sammuttaa kaikki oheislaitteet nopeasti samanaikaisesti tarvittaessa.

Esimerkiksi siinä tapauksessa, että tietokoneen suorituskyky heikkenee tai muista syistä. Tässä tapauksessa käyttäjän ei tarvitse poistaa komponentteja ohjelmallisesti käytöstä pitkään aikaan.